**DAC7750, DAC8750** ZHCSC70D - DECEMBER 2013 - REVISED DECEMBER 2021

# DACx750 适用于 4-20mA 电流环路应用的单通道、 12 位和 16 位可编程电流输出数模转换器

# 1 特性

- 电流输出选项:

- 0mA 至 24mA

- 4mA 至 20mA

- 0mA 至 20mA

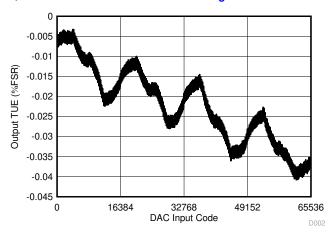

- ±0.1% FSR 典型总体未调误差 (TUE)

- DNL: ±1LSB 最大值

- 最大环路合规性电压: AVDD 2V

- 内部 5V 基准: 10ppm/°C(最大值)

- 4.6V 内部电源输出

- CRC 帧错误校验

- 看门狗计时器

- 热警报

- 开路警报

- 用于监控输出电流的引脚

- 片上故障警报

- 针对偏移和增益的用户校准

- 宽温度范围: 40°C 至 125°C

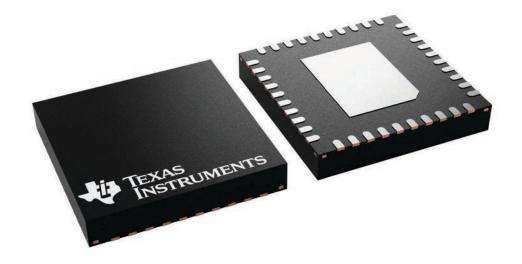

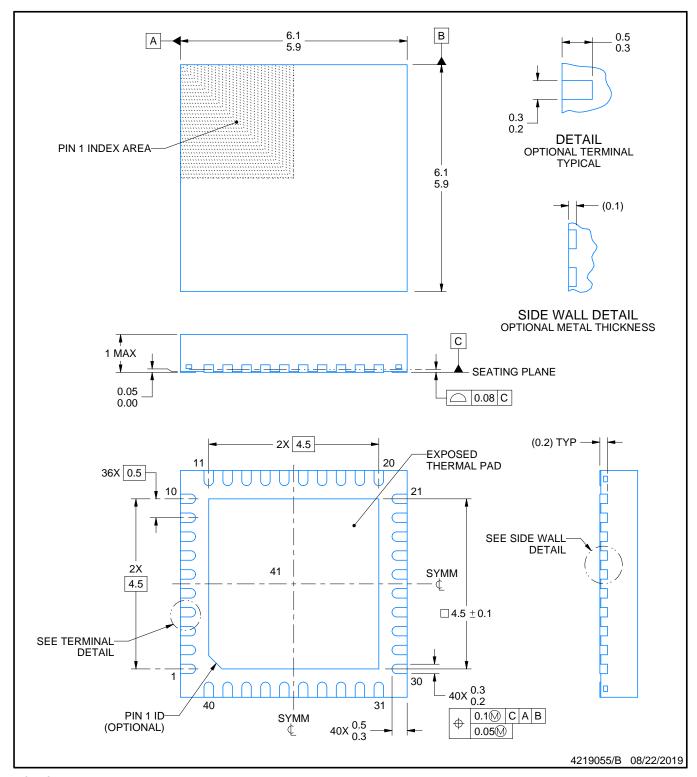

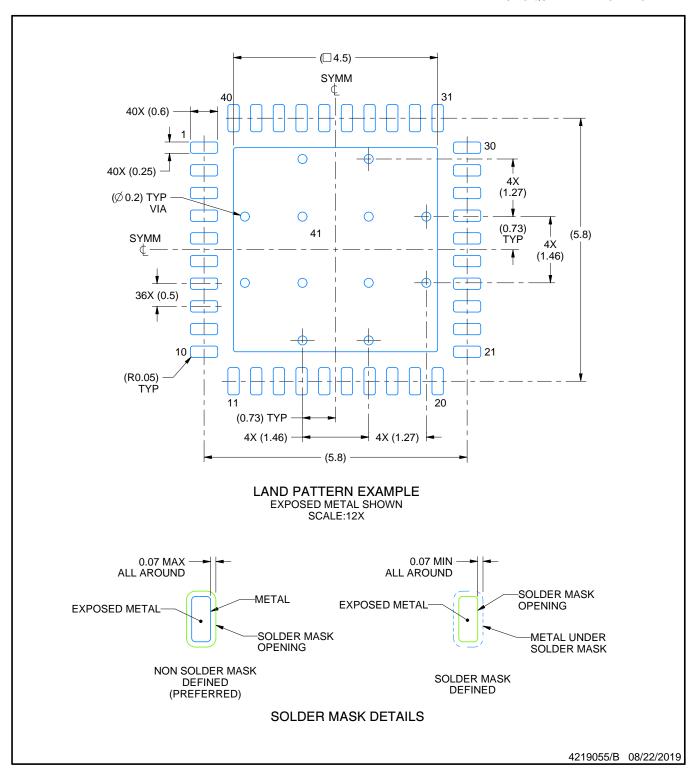

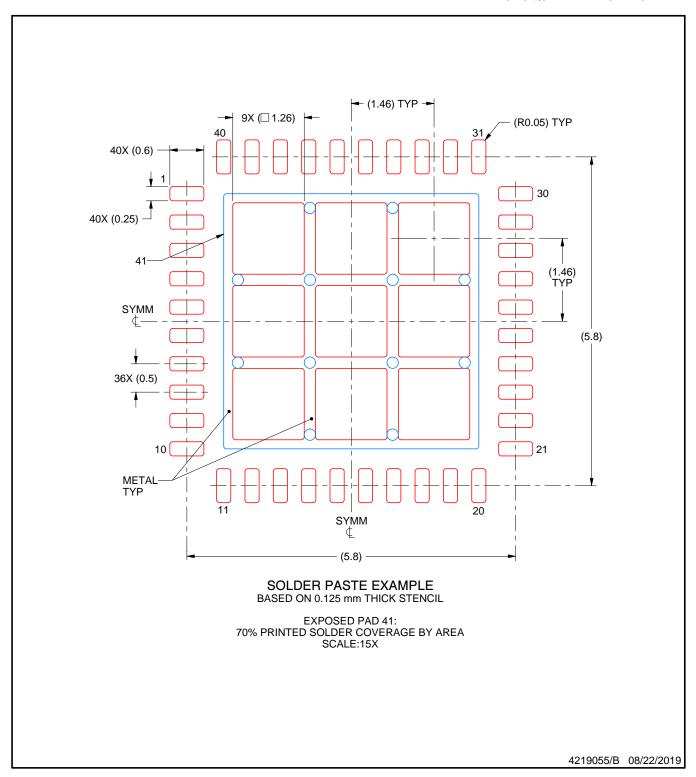

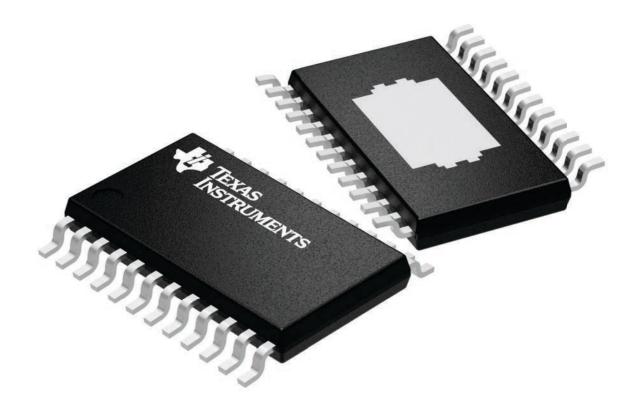

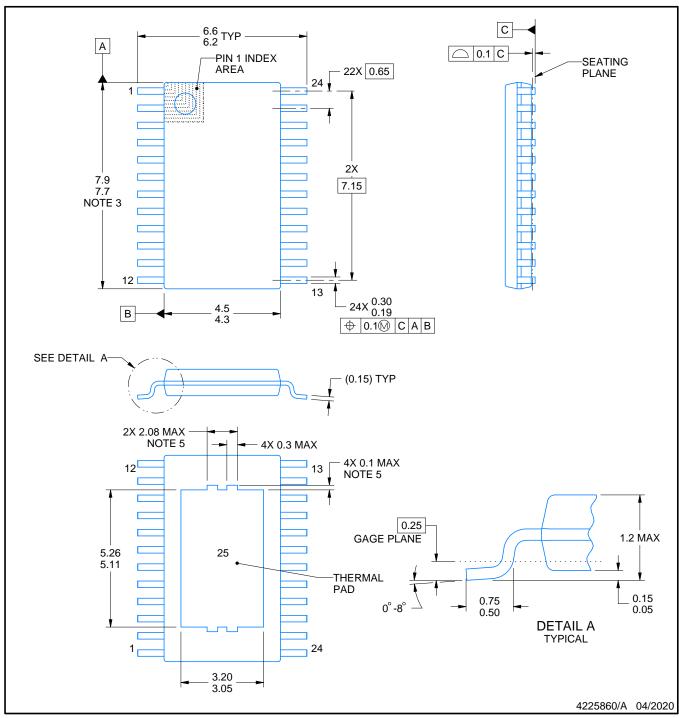

- 封装:6mm×6mm 40 引脚 VQFN 和 24 引脚 **HTSSOP**

## 2 应用

- 模拟输出模块

- CPU(PLC控制器)

- 流量变送器

- 其他传感器变送器

- 传动器

- 过程分析(pH、气体、浓度、力和湿度)

# 3 说明

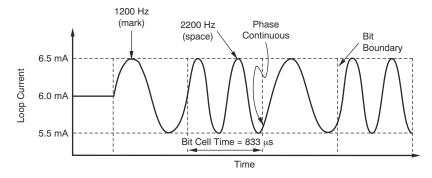

DAC7750 和 DAC8750 (DACx750) 是完全集成的低成 本、精密 12 位和 16 位数模转换器 (DAC),旨在满足 工业过程控制应用的要求。这些器件经编程可提供范围 介于 4-20mA、0-20mA 或 0-24mA 的电流输出。 DACx750 包括可靠性功能,例如 SPI 帧上的 CRC 错 误校验、看门狗计时器、开路、合规电压和热警报。此 外,可通过访问一个内部高精度电阻器来监控输出电 流。

这些器件包括一个上电复位功能,以确保器件在某个已 知状态(IOUT 被禁用并且处于高阻抗状态)上电。如 果输出被启用, CLR 引脚将电流输出设定为低电平。 对零和增益寄存器进行编程,以便对终端系统内的器件 进行数字校准。输出转换率也可通过寄存器进行编程。 这些器件可以在电流输出上叠加外部 HART® 信号,并 采用 10V 至 36V 电源供电。

### 器件信息

| 器件型号    | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |

|---------|-------------------|-----------------|

| DACx750 | HTSSOP (24)       | 7.80mm × 4.40mm |

| DACATOO | VQFN (40)         | 6.00mm × 6.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

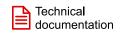

方框图

# **Table of Contents**

| 1 特性                                            | 1 | 8.3 Feature Description                 | 21              |

|-------------------------------------------------|---|-----------------------------------------|-----------------|

|                                                 |   | 8.4 Device Functional Modes             | <mark>28</mark> |

| - <del>,                                 </del> |   | 8.5 Programming                         |                 |

| 4 Revision History                              |   | 8.6 Register Maps                       |                 |

| 5 Device Comparison Table                       |   | 9 Application and Implementation        | 37              |

| 6 Pin Configuration and Functions               |   | 9.1 Application Information             | 37              |

| 7 Specifications                                |   | 9.2 Typical Application                 |                 |

| 7.1 Absolute Maximum Ratings                    |   | 10 Power Supply Recommendations         | 42              |

| 7.2 ESD Ratings                                 |   | 11 Layout                               |                 |

| 7.3 Recommended Operating Conditions            |   | 11.1 Layout Guidelines                  |                 |

| 7.4 Thermal Information                         |   | 11.2 Layout Example                     |                 |

| 7.5 Electrical Characteristics                  |   | 12 Device and Documentation Support     | 44              |

| 7.6 Electrical Characteristics: AC              |   | 12.1 Documentation Support              | 44              |

| 7.7 Timing Requirements: Write Mode             |   | 12.2 接收文档更新通知                           | 44              |

| 7.8 Timing Requirements: Readback Mode          |   | 12.3 支持资源                               | 44              |

| 7.9 Timing Diagrams                             |   | 12.4 Trademarks                         |                 |

| 7.10 Typical Characteristics                    |   | 12.5 Electrostatic Discharge Caution    | 44              |

| 8 Detailed Description                          |   | 12.6 术语表                                |                 |

| 8.1 Overview                                    |   | 13 Mechanical, Packaging, and Orderable |                 |

| 8.2 Functional Block Diagram                    |   | Information                             | 44              |

| ÷ := : = :: = : = : = : = : = : = : = :         |   |                                         |                 |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| C | hanges from Revision C (January 2018) to Revision D (December 2021)                                   | Page            |

|---|-------------------------------------------------------------------------------------------------------|-----------------|

| • | 更新了整个文档中的表格、图和交叉参考的编号格式                                                                               | 1               |

| • | Changed Loop compliance voltage to Reference input voltage, and Reference input voltage to External   | !               |

|   | reference current in Recommended Operating Conditions                                                 | 6               |

| • | Changed Digital input low voltage test condition upper limit from 2.6 V to 3.6 V in Recommended Opera | ating           |

|   | Conditions                                                                                            |                 |

| • | Deleted Timing Requirements: Daisy-Chain Mode section and Daisy-Chain Mode Timing figure              | 11              |

| • | Deleted Power-Supply Sequence section; content moved to Power Supply Recommendations section          | <mark>22</mark> |

| • | Deleted daisy-chain operation content from Watchdog Timer section                                     | 24              |

| • | Deleted The DACx750 Shares the SPI Bus With Other Devices subsection from Watchdog Timer section      | on 24           |

| • | Deleted daisy-chain operation from Frame Error Checking section                                       |                 |

| • | Added CRC fault reset command of 0x96 to Frame Error Checking section                                 | 24              |

| • | Deleted The DACx750 Shares the SPI Bus With Other Devices subsection                                  |                 |

| • | Changed duplicated 010 step-size from 0.125 to 0.25 in Table 8-3, Slew Rate Step-Size Options         |                 |

| • | Added CRC fault reset command to Table 8-8, Write Address Functions                                   |                 |

| • | Deleted Daisy-Chain Operation section                                                                 |                 |

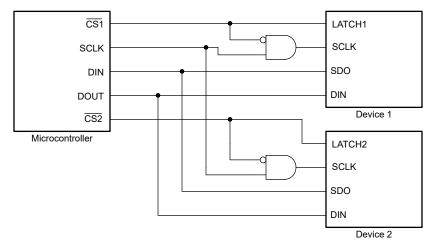

| • | Added Multiple Devices on the Bus section                                                             |                 |

| • | Changed Table 8-11 to delete daisy-chain operation and add CRC fault reset                            |                 |

| • | Changed DCEN to Reserved for DB3 in Control Register table                                            |                 |

| • | Deleted text stating CAP2 pin is only available for the 40-pin VQFN package                           |                 |

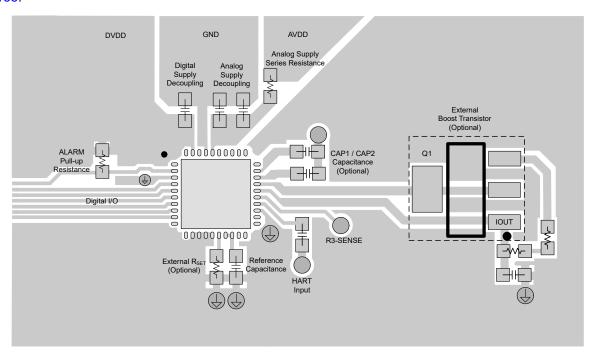

| • | Added series resistance for supply and corrected HART-IN capacitance for Figure 9-3                   |                 |

| • | Added content from deleted Power-Supply Sequence section to Power Supply Recommendations section      |                 |

| • | Added fast supply ramp and series resistance content to Power-Supply Recommendations                  |                 |

|   | Added power supply series resistance to Figure 11-1, Layout Example                                   |                 |

| C | hanges from Revision B (June 2016) to Revision C (January 2018)                                       | Page            |

| • | Added last paragraph to User Calibration section                                                      | 25              |

DAC7750, DAC8750 ZHCSC70D - DECEMBER 2013 - REVISED DECEMBER 2021

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

# **5 Device Comparison Table**

| PRODUCT | RESOLUTION | TUE (FSR) | DIFFERENTIAL<br>NONLINEARITY (LSB) |  |

|---------|------------|-----------|------------------------------------|--|

| DAC8750 | 16         | 0.2%      | ±1                                 |  |

| DAC7750 | 12         | 0.2%      | ±1                                 |  |

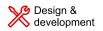

# **6 Pin Configuration and Functions**

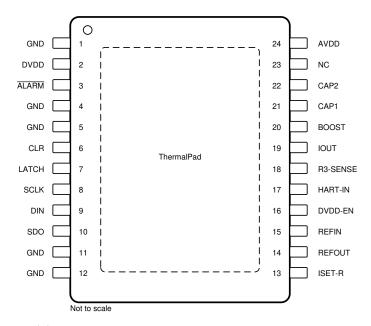

图 6-1. RHA Package, 40-Pin VQFN, Top View

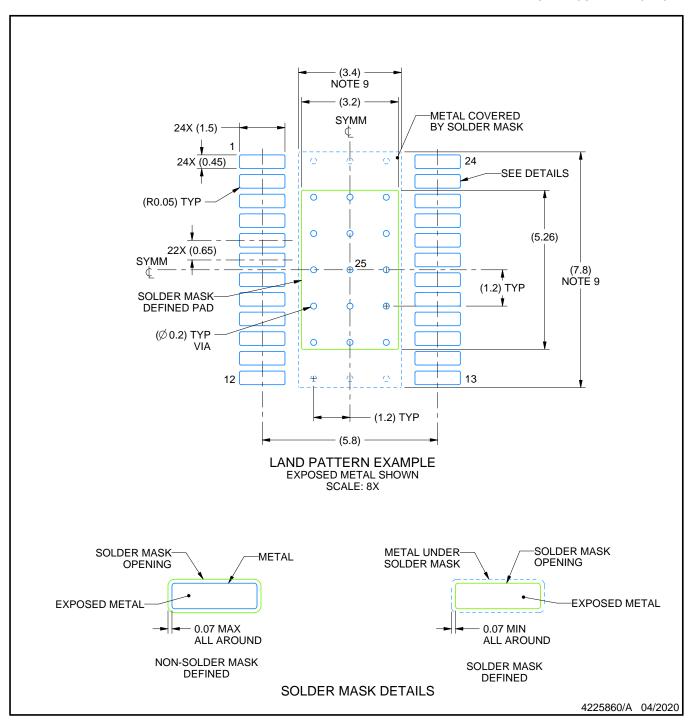

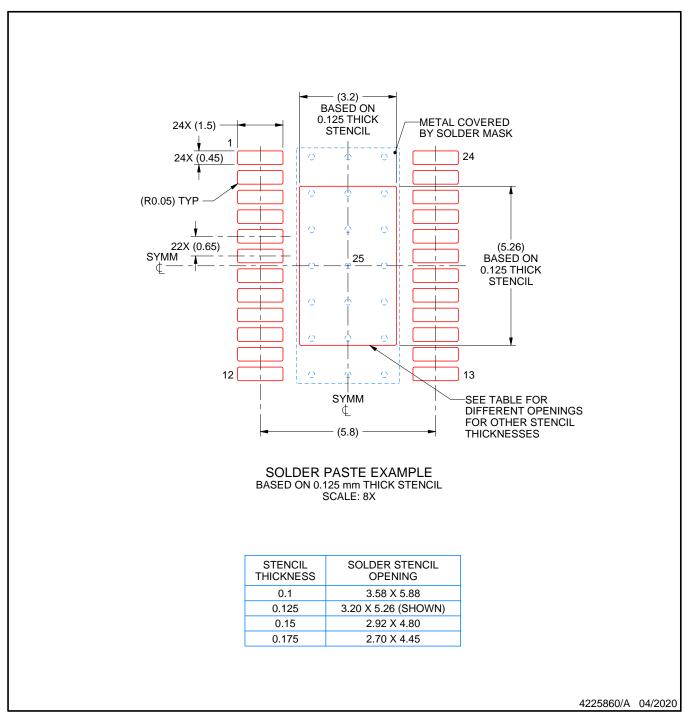

图 6-2. PWP Package, 24-Pin HTSSOP, Top View

Submit Document Feedback

# 表 6-1. Pin Functions

|             | 表 6-1. Pin Functions                                                  |                 |                        |                                                                                                                                                                                                                                                                                                 |  |  |  |

|-------------|-----------------------------------------------------------------------|-----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | RHA<br>(VQFN)                                                         | PWP<br>(HTSSOP) | TYPE                   | DESCRIPTION                                                                                                                                                                                                                                                                                     |  |  |  |

| ALARM       | 2                                                                     | 3               | Digital output         | Alarm pin. Open drain output. External pullup resistor required (10 k $\Omega$ ). The pin goes low (active) when the $\overline{\text{ALARM}}$ condition is detected (open circuit, over temperature, timeout, and so on).                                                                      |  |  |  |

| AVDD        | 36                                                                    | 24              | Supply input           | Positive analog power supply.                                                                                                                                                                                                                                                                   |  |  |  |

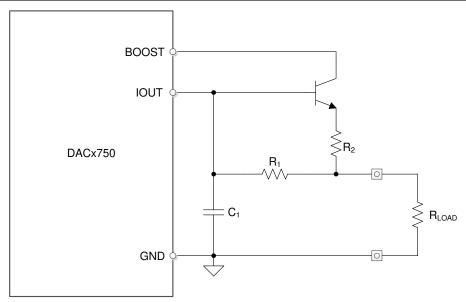

| BOOST       | 27                                                                    | 20              | Analog output          | Boost pin. External transistor connection (optional).                                                                                                                                                                                                                                           |  |  |  |

| CAP1        | 28                                                                    | 21              | Analog input           | Connection for output filtering capacitor (optional).                                                                                                                                                                                                                                           |  |  |  |

| CAP2        | 29                                                                    | 22              | Analog input           | Connection for output filtering capacitor (optional).                                                                                                                                                                                                                                           |  |  |  |

| CLR         | 5                                                                     | 6               | Digital input          | Clear input. Logic high on this pin causes the part to enter CLEAR state. Active high.                                                                                                                                                                                                          |  |  |  |

| DIN         | 8                                                                     | 9               | Digital input          | Serial data input. Data are clocked into the 24-bit input shift register on the rising edge of the serial clock input. Schmitt-Trigger logic input.                                                                                                                                             |  |  |  |

| DVDD        | 39                                                                    | 2               | Supply input or output | Digital power supply. Can be input or output, depending on DVDD-EN pin.                                                                                                                                                                                                                         |  |  |  |

| DVDD-EN     | 23                                                                    | 16              | Digital input          | Internal power-supply enable pin. Connect this pin to GND to disable the internal supply, or leave this pin unconnected to enable the internal supply When this pin is connected to GND, an external supply must be connected to the DVDD pin.                                                  |  |  |  |

| GND         | 12, 13, 14,<br>15, 37                                                 | 1, 11, 12       | Supply input           | Ground reference point for all analog circuitry of the device.                                                                                                                                                                                                                                  |  |  |  |

| GND         | 3, 4                                                                  | 4, 5            | Supply input           | Ground reference point for all digital circuitry of the device.                                                                                                                                                                                                                                 |  |  |  |

| HART-IN     | 24                                                                    | 17              | Analog input           | Input pin for HART modulation.                                                                                                                                                                                                                                                                  |  |  |  |

| IOUT        | 26                                                                    | 19              | Analog output          | Current output pin                                                                                                                                                                                                                                                                              |  |  |  |

| ISET-R      | 16                                                                    | 13              | Analog input           | Connection pin for external precision resistor (15 k $\Omega$ ). See #8 of this data sheet.                                                                                                                                                                                                     |  |  |  |

| LATCH       | 6                                                                     | 7               | Digital input          | Load DAC registers input. A rising edge on this pin loads the input shift register data into the DAC data and control registers and updates the DAC output.                                                                                                                                     |  |  |  |

| NC          | 1, 10, 11,<br>19, 20, 21,<br>22, 30, 31,<br>32, 33, 34,<br>35, 38, 40 | 23              | _                      | No connection.                                                                                                                                                                                                                                                                                  |  |  |  |

| R3-SENSE    | 25                                                                    | 18              | Analog output          | This pin is used as a monitoring feature for the output current. The voltage measured between the R3-SENSE pin and the BOOST pin is directly proportional to the output current.                                                                                                                |  |  |  |

| REFOUT      | 17                                                                    | 14              | Analog output          | Internal reference output. Connects to REFIN when using internal reference.                                                                                                                                                                                                                     |  |  |  |

| REFIN       | 18                                                                    | 15              | Analog input           | Reference input                                                                                                                                                                                                                                                                                 |  |  |  |

| SCLK        | 7                                                                     | 8               | Digital input          | Serial clock input of the SPI. Data can be transferred at rates up to 30 MHz. Schmitt-Trigger logic input.                                                                                                                                                                                      |  |  |  |

| SDO         | 9                                                                     | 10              | Digital output         | Serial data output. Data are valid on the rising edge of SCLK.                                                                                                                                                                                                                                  |  |  |  |

| Thermal Pad | -                                                                     | _               | Supply input           | The thermal pad is internally connected to GND. For enhanced thermal performance, thermally connect the pad to a copper plane. The pad can be electrically connected to the same potential as the GND pin or left electrically unconnected provided a supply connection is made at the GND pin. |  |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                              | MIN   | MAX        | UNIT |

|------------------|------------------------------|-------|------------|------|

|                  | AVDD to GND                  | - 0.3 | 40         | V    |

|                  | DVDD to GND                  | - 0.3 | 6          | V    |

|                  | IOUT to GND                  | - 0.3 | AVDD       | V    |

|                  | REFIN to GND                 | - 0.3 | 6          | V    |

|                  | REFOUT to GND                | - 0.3 | 6          | V    |

|                  | ALARM to GND                 | - 0.3 | 6          | V    |

|                  | Digital input voltage to GND | - 0.3 | DVDD + 0.3 | V    |

|                  | SDO to GND                   | - 0.3 | DVDD + 0.3 | V    |

|                  | Current into REFOUT          |       | 10         | mA   |

|                  | Operating temperature        | - 40  | 125        | °C   |

| TJ               | Junction temperature         |       | 150        | °C   |

| T <sub>stg</sub> | Storage temperature          | - 65  | 150        | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 7.2 ESD Ratings

|                  |                                        |                                                              | VALUE | UNIT |

|------------------|----------------------------------------|--------------------------------------------------------------|-------|------|

| \/               | Electrostatic discharge <sup>(1)</sup> | Human body model (HBM) ESD stress voltage <sup>(2)</sup>     | ±3000 | \/   |

| V <sub>ESD</sub> | Liectrostatic discriarge               | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> | ±1000 | v    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

# 7.3 Recommended Operating Conditions

|                                                         |                               |                            | MIN  | NOM MAX  | UNIT |

|---------------------------------------------------------|-------------------------------|----------------------------|------|----------|------|

| AVDD                                                    | Analog supply voltage         |                            | 10   | 36       | V    |

| DVDD                                                    | Digital supply voltage        |                            | 2.7  | 5.5      | V    |

|                                                         | Reference input voltage       |                            | 4.95 | 5.05     | V    |

|                                                         | External reference current    |                            | 30   | μA       |      |

| Loop compliance voltage (output = 24 mA) <sup>(1)</sup> |                               | ut = 24 mA) <sup>(1)</sup> |      | AVDD - 2 | V    |

| VIH                                                     | Digital input high voltage    |                            | 2    |          | V    |

| \( ///                                                  | Digital lagrat lagrander as   | 3.6 V < AVDD < 5.5 V       |      | 0.8      | V    |

| VIL                                                     | Digital Input low voltage     | 2.7 V < AVDD < 3.6 V       |      | 0.6      | V    |

|                                                         | Specified performance tempera | ture                       | - 40 | 125      | °C   |

(1) Loop compliance voltage is defined as the voltage at the IOUT pin

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

<sup>(3)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 7.4 Thermal Information

|                        |                                              | DAC7750    | DAC8750      |      |

|------------------------|----------------------------------------------|------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHA (VQFN) | PWP (HTSSOP) | UNIT |

|                        |                                              | 40 PINS    | 24 PINS      |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 32.9       | 32.3         | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17.2       | 14.1         | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 7.5        | 12.2         | °C/W |

| ψ ЈТ                   | Junction-to-top characterization parameter   | 0.2        | 0.3          | °C/W |

| ψ ЈВ                   | Junction-to-board characterization parameter | 7.5        | 12           | °C/W |

| R <sub>θ</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.4        | 0.63         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

at AVDD = 10 V to 36 V, GND = 0 V, REFIN = 5 V external, DVDD = 2.7 V to 5.5 V, and all specifications are from  $-40^{\circ}$ C to +125°C (unless otherwise noted); for IOUT,  $R_L = 300^{\circ}$  Ω; typical specifications are at 25°C

| PARAMETER                                | TEST                                                 | CONDITIONS                                           | MIN     | TYP     | MAX    | UNIT       |  |

|------------------------------------------|------------------------------------------------------|------------------------------------------------------|---------|---------|--------|------------|--|

| CURRENT OUTPUT                           |                                                      |                                                      |         |         |        |            |  |

|                                          | RANGE bits = 111                                     |                                                      | 0       |         | 24     |            |  |

| Current output                           | RANGE bits = 110                                     |                                                      | 0       |         | 20     | mA         |  |

|                                          | RANGE bits = 101                                     | RANGE bits = 101                                     |         |         | 20     |            |  |

| Resolution                               | DAC8750                                              |                                                      | 16      |         |        | Bits       |  |

| Resolution                               | DAC7750                                              |                                                      | 12      |         |        | DIIS       |  |

| CURRENT OUTPUT ACCURACY (0 mA            | TO 20 mA AND 0 mA TO                                 | 24 mA) <sup>(1)</sup>                                |         |         |        |            |  |

|                                          | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                                                      | - 0.2%  |         | 0.2%   |            |  |

| Total unadjusted error, TUE              | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$        |                                                      | - 0.16% |         | 0.16%  | FSR        |  |

|                                          | T <sub>A</sub> = 25°C                                |                                                      | - 0.08% | ±0.02%  | 0.08%  |            |  |

| Differential nonlinearity, DNL           | Monotonic                                            |                                                      |         |         | ±1     | LSB        |  |

| D. I. (2)                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                                                      |         |         | ±0.08% |            |  |

| Relative accuracy, INL <sup>(3)</sup>    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$        |                                                      |         | ±0.024% | FSR    |            |  |

| Offset error                             | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                                                      | - 0.17% |         | 0.17%  |            |  |

|                                          | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  | - 0.1%                                               |         | 0.1%    | FSR    |            |  |

|                                          | T <sub>A</sub> = 25°C                                | - 0.07%                                              | ±0.01%  | 0.07%   |        |            |  |

| Offset error temperature coefficient     |                                                      |                                                      |         | ±5      |        | ppm FSR/°C |  |

|                                          | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |         |         | 0.2%   |            |  |

| Full-scale error                         | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  |                                                      |         |         | 0.16%  | FSR        |  |

|                                          | T <sub>A</sub> = 25°C                                |                                                      |         |         | 0.08%  |            |  |

|                                          | Internal R <sub>SET</sub>                            |                                                      |         | ±5      |        |            |  |

| Full-scale error temperature coefficient | External R <sub>SET</sub>                            |                                                      |         | ±10     |        | ppm FSR/°C |  |

|                                          |                                                      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | - 0.2%  |         | 0.2%   |            |  |

|                                          | Internal R <sub>SET</sub>                            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$        | - 0.15% |         | 0.15%  |            |  |

|                                          |                                                      | T <sub>A</sub> = 25°C                                | - 0.08% | ±0.01%  | 0.08%  |            |  |

| Gain error                               |                                                      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | - 0.17% |         | 0.17%  | FSR        |  |

|                                          | External R <sub>SET</sub>                            | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  | - 0.12% |         | 0.12%  |            |  |

|                                          |                                                      | T <sub>A</sub> = 25°C                                | - 0.05% | ±0.01%  | 0.05%  |            |  |

|                                          | Internal R <sub>SET</sub>                            |                                                      |         | ±3      |        |            |  |

| Gain error temperature coefficient       | External R <sub>SET</sub>                            |                                                      |         |         |        | ppm FSR/°C |  |

|                                          |                                                      | Internal R <sub>SET</sub>                            |         | ±50     |        |            |  |

| Output current drift vs time             | T <sub>A</sub> = 125°C, 1000 hrs                     | External R <sub>SET</sub>                            |         | ±25     |        | ppm FSR    |  |

# 7.5 Electrical Characteristics (continued)

at AVDD = 10 V to 36 V, GND = 0 V, REFIN = 5 V external, DVDD = 2.7 V to 5.5 V, and all specifications are from  $-40^{\circ}$ C to +125°C (unless otherwise noted); for IOUT,  $R_1 = 300^{\circ}$  Ω; typical specifications are at 25°C

| PARAMETER                                | TEST C                                         | ONDITIONS                                            | MIN      | TYP     | MAX        | UNIT         |

|------------------------------------------|------------------------------------------------|------------------------------------------------------|----------|---------|------------|--------------|

| CURRENT OUTPUT ACCURACY (4 m.            | A TO 20 mA) <sup>(1)</sup>                     |                                                      |          |         |            |              |

|                                          | Internal D                                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | - 0.25%  |         | 0.25%      |              |

|                                          | Internal R <sub>SET</sub>                      | T <sub>A</sub> = 25°C                                | - 0.08%  | ±0.02%  | 0.08%      |              |

| Total unadjusted error, TUE              |                                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | - 0.29%  |         | 0.29%      | FSR          |

|                                          | External R <sub>SET</sub>                      | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$        | - 0.25%  |         | 0.25%      |              |

|                                          |                                                | T <sub>A</sub> = 25°C                                | - 0.1%   | ±0.02%  | 0.1%       |              |

| Differential nonlinearity, DNL           | Monotonic                                      |                                                      |          |         | ±1         | LSB          |

| D. I. (3)                                | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                                                      |          |         | ±0.08%     | F0D          |

| Relative accuracy, INL <sup>(3)</sup>    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  |                                                      |          |         | ±0.024%    | FSR          |

|                                          |                                                | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       | - 0.22%  |         | 0.22%      |              |

|                                          | Internal R <sub>SET</sub>                      | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$        | - 0.2%   |         | 0.2%       |              |

| Offset error                             |                                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | - 0.2%   |         | 0.2%       | FSR          |

|                                          | External R <sub>SET</sub>                      | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$        | - 0.18%  |         | 0.18%      |              |

|                                          | Internal and external R <sub>SE</sub>          |                                                      | - 0.07%  | ±0.01%  | 0.07%      |              |

| Offset error temperature coefficient     |                                                |                                                      |          | ±3      |            | ppm FSR/°C   |

|                                          |                                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | - 0.25%  |         | 0.25%      |              |

| Full-scale error                         | Internal R <sub>SET</sub>                      | T <sub>A</sub> = 25°C                                | - 0 .08% | ±0.015% | 0.08%      | FSR          |

|                                          | External R <sub>SET</sub>                      | T <sub>A</sub> = -40°C to +125°C                     | - 0.29%  |         | 0.29%      |              |

|                                          |                                                | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  | - 0.25%  |         | 0.25%      |              |

|                                          |                                                | T <sub>A</sub> = 25°C                                | - 0 .1%  | ±0.015% | 0.1%       |              |

|                                          | Internal R <sub>SET</sub>                      |                                                      |          | ±5      |            |              |

| Full-scale error temperature coefficient | External R <sub>SET</sub>                      |                                                      | ±10      |         | ppm FSR/°C |              |

|                                          | Internal R <sub>SET</sub>                      | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       | - 0.2%   |         | 0.2%       | FSR          |

|                                          |                                                | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  | - 0.15%  |         | 0.15%      |              |

|                                          |                                                | T <sub>A</sub> = 25°C                                | - 0.08%  | ±0.01%  | 0.08%      |              |

| Gain error                               |                                                | T <sub>A</sub> = -40°C to +125°C                     | - 0.16%  |         | 0.16%      |              |

|                                          | External R <sub>SET</sub>                      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  | - 0.12%  |         | 0.12%      |              |

|                                          | OE1                                            | T <sub>A</sub> = 25°C                                | - 0.05%  | ±0.01%  | 0.05%      |              |

|                                          | Internal R <sub>SET</sub>                      |                                                      |          | ±3      |            |              |

| Gain error temperature coefficient       | External R <sub>SET</sub>                      |                                                      |          | ±8      |            | ppm FSR/°C   |

|                                          |                                                | Internal R <sub>SET</sub>                            |          | ±50     |            |              |

| Output current drift vs time             | T <sub>A</sub> = 125°C, 1000 hrs               | External R <sub>SET</sub>                            |          | ±75     |            | ppm FSR      |

| CURRENT OUTPUT STAGE <sup>(2)</sup>      |                                                |                                                      |          |         |            |              |

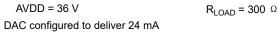

| _oop compliance voltage <sup>(4)</sup>   | Output = 24 mA                                 |                                                      |          |         | AVDD - 2   | V            |

| nductive load <sup>(5)</sup>             |                                                |                                                      |          | 50      |            | mH           |

| DC PSRR                                  |                                                |                                                      |          |         | 1          | μ <b>Α/V</b> |

| Output impedance                         | Code = 0x8000                                  |                                                      |          | 50      |            | ΜΩ           |

| R3 RESISTOR                              | l                                              |                                                      | I        |         | l          |              |

| R3 resistor value                        |                                                |                                                      | 36       | 40      | 44         | Ω            |

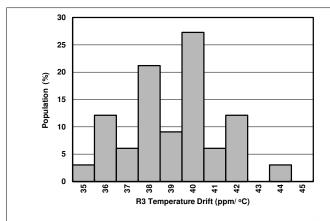

| R3 resistor temperature coefficient      |                                                |                                                      |          | 40      |            | ppm/°C       |

| EXTERNAL REFERENCE INPUT                 | ·                                              |                                                      |          |         |            |              |

| Reference input voltage                  |                                                |                                                      | 4.95     | 5       | 5.05       | V            |

| External reference current               | REFIN = 5.0 V                                  |                                                      |          | 30      |            | μ <b>A</b>   |

| Reference input capacitance              |                                                |                                                      |          | 10      |            | pF           |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 7.5 Electrical Characteristics (continued)

at AVDD = 10 V to 36 V, GND = 0 V, REFIN = 5 V external, DVDD = 2.7 V to 5.5 V, and all specifications are from  $-40^{\circ}$ C to +125°C (unless otherwise noted); for IOUT,  $R_1 = 300^{\circ}$  Ω; typical specifications are at 25°C

| +125°C (unless otherwise noted<br>PARAMETER      | TEST COI                                |                                                               | MIN        | TYP  | MAX   | UNIT               |

|--------------------------------------------------|-----------------------------------------|---------------------------------------------------------------|------------|------|-------|--------------------|

| INTERNAL REFERENCE OUTPUT                        |                                         |                                                               |            |      |       |                    |

| Reference output                                 | T <sub>A</sub> = 25°C                   |                                                               | 4.995      |      | 5.005 | V                  |

| Reference temperature coefficient <sup>(2)</sup> | T <sub>A</sub> = -40°C to +85°C         |                                                               |            |      | ±10   | ppm/°C             |

| Output noise (0.1 Hz to 10 Hz)                   | T <sub>A</sub> = 25°C                   |                                                               |            | 14   |       | μ V <sub>PP</sub>  |

| Noise spectral density                           | T <sub>A</sub> = 25°C, 10 kHz           |                                                               |            | 185  |       | nV/√ <del>Hz</del> |

| Capacitive load                                  |                                         |                                                               |            | 600  |       | nF                 |

| Load current                                     |                                         |                                                               |            | ±5   |       | mA                 |

| Short-circuit current                            | REFOUT shorted to GND                   |                                                               |            | 25   |       | mA                 |

|                                                  | AVDD = 24 V, T <sub>A</sub> = 25°C, so  | purcing                                                       |            | 55   |       |                    |

| Load regulation                                  | AVDD = 24 V, T <sub>A</sub> = 25°C, sir |                                                               |            | 120  |       | μ V/mA             |

| Line regulation                                  |                                         |                                                               |            | ±1.2 |       | μ <b>V/V</b>       |

| DVDD INTERNAL REGULATOR                          |                                         |                                                               | 1          |      |       |                    |

| Output voltage                                   | AVDD = 24 V                             |                                                               |            | 4.6  |       | V                  |

| Output load current <sup>(2)</sup>               |                                         |                                                               |            |      | 10    | mA                 |

| Load regulation                                  |                                         |                                                               |            | 3.5  |       | mV/mA              |

| Line regulation                                  |                                         |                                                               |            | 1    |       | mV/V               |

| Short-circuit current                            | AVDD = 24 V, to GND                     | AVDD = 24 V, to GND                                           |            | 35   |       | mA                 |

| Capacitive load stability <sup>(2)</sup>         |                                         |                                                               |            |      | 2.5   | μF                 |

| DIGITAL INPUTS                                   |                                         |                                                               |            |      |       |                    |

| High-level input voltage, V <sub>IH</sub>        |                                         |                                                               | 2          |      |       | V                  |

|                                                  | 3.6 V < AVDD < 5.5 V                    |                                                               |            |      | 0.8   |                    |

| Low-level input voltage, V <sub>IL</sub>         | 2.7 V < AVDD < 3.6 V                    | 2.7 V < AVDD < 3.6 V                                          |            |      | 0.6   | V                  |

| Hysteresis voltage                               |                                         |                                                               |            | 0.4  |       | V                  |

| , ,                                              | DVDD-EN, V <sub>IN</sub> ≤ 5 V          |                                                               | - 2.7      |      |       |                    |

| Input current                                    | All pins other than DVDD-EN             | N                                                             |            |      | ±1    | $\mu$ A            |

| Pin capacitance                                  | Per pin                                 |                                                               |            | 10   |       | pF                 |

| DIGITAL OUTPUTS                                  | · · · · · · · · · · · · · · · · · · ·   |                                                               |            |      |       | F*                 |

|                                                  | Low-level output voltage, Vo            | sinking 200 µA                                                |            |      | 0.4   |                    |

| SDO                                              | Hligh-level output voltage, V           | -                                                             | DVDD - 0.5 |      |       | V                  |

|                                                  | High-impedance leakage                  | OH, Sourcing 200 PA                                           | 0.5        |      | ±1    | 11 <b>A</b>        |

|                                                  | підп-ітірецапсе теакаде                 | 10 k O pullus resistes to                                     |            |      | ±1    | μ <b>А</b>         |

|                                                  | Low-level output voltage,               | 10-k Ω pullup resistor to DVDD                                |            |      | 0.4   | V                  |

| ALARM                                            | V <sub>OL</sub>                         | 2.5 mA                                                        |            |      | 0.6   | •                  |

|                                                  | High-impedance leakage                  |                                                               |            |      | ±1    | μ <b>A</b>         |

| High-impedance output capacitance                |                                         |                                                               |            | 10   |       | pF                 |

| POWER SUPPLY                                     |                                         |                                                               | 1          |      |       | <u> </u>           |

| AVDD                                             |                                         |                                                               | 10         |      | 36    | V                  |

| DVDD                                             | Internal regulator disabled             |                                                               | 2.7        |      | 5.5   | V                  |

|                                                  | Outputs disabled, external D            | OVDD                                                          |            |      | 3     |                    |

| AIDD                                             | Outputs disabled, internal D            | VDD                                                           |            |      | 4     | mA                 |

|                                                  | Code = 0x0000, IOUT enabled             |                                                               |            |      | 3     |                    |

| DIDD                                             |                                         | V <sub>IH</sub> = DVDD, V <sub>IL</sub> = GND, interface idle |            |      | 1     | mA                 |

| Power dissipation                                | AVDD = 36 V, IOUT = 0 mA,               |                                                               |            | 95   | 115   | mW                 |

| TEMPERATURE                                      | <u> </u>                                |                                                               | 1          |      |       |                    |

| Thermal alarm                                    |                                         |                                                               |            | 142  |       | °C                 |

| Thermal alarm hysteresis                         |                                         |                                                               |            | 18   |       | °C                 |

<sup>(1)</sup> DAC8750 and DAC7750 current output range is set by writing to RANGE bits in control register at address 0x55.

- (2) Specified by design and characterization; not production tested.

- (3) For 0-mA to 20-mA and 0-mA to 24-mA ranges, INL is calculated beginning from code 0x0100 for DAC8750 and from code 0x0010 for DAC7750.

- (4) Loop compliance voltage is defined as the voltage at the IOUT pin.

- (5) For stability, use slew rate limit feature or add a capacitor between IOUT and GND

## 7.6 Electrical Characteristics: AC

At AVDD = 10 V to 36 V, GND = 0 V, REFIN= 5 V external and DVDD = 2.7 V to 5.5 V. For IOUT,  $R_L$  = 300  $\Omega$ . All specifications  $-40^{\circ}$ C to 125 $^{\circ}$ C (unless otherwise noted). Typical specifications are at 25 $^{\circ}$ C.

| opeomeation 10 0 to 120 0 (timese strict vice 1). Typical opeomeations are at 20 0. |                                                                       |     |      |     |      |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|------|-----|------|

| PARAMETER <sup>(1)</sup>                                                            | TEST CONDITIONS                                                       | MIN | TYP  | MAX | UNIT |

| DYNAMIC PERFORMANCE                                                                 |                                                                       |     |      |     |      |

| Output current settling time                                                        | 16-mA step, to 0.1% FSR, no L (inductance)                            |     | 10   |     | μS   |

| Output current setting time                                                         | 16-mA step, to 0.1% FSR, L < 1 mH                                     |     | 25   |     | μ \$ |

| AC PSRR                                                                             | 200-mV, 50-Hz or 60-Hz sine wave superimposed on power-supply voltage |     | - 75 |     | dB   |

(1) Specified by characterization, not production tested.

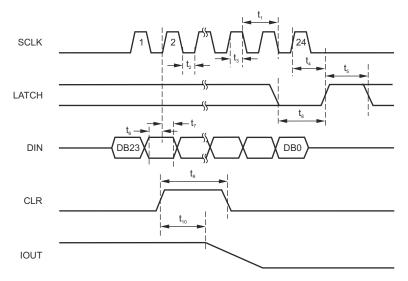

# 7.7 Timing Requirements: Write Mode

at  $T_A = -40$ °C to 125°C and DVDD = 2.7 V to 5.5 V (unless otherwise noted)<sup>(1)</sup>

|                 |                                | MIN M | AX | UNIT |

|-----------------|--------------------------------|-------|----|------|

| t <sub>1</sub>  | SCLK cycle time                | 33    |    | ns   |

| t <sub>2</sub>  | SCLK low time                  | 13    |    | ns   |

| t <sub>3</sub>  | SCLK high time                 | 13    |    | ns   |

| t <sub>4</sub>  | LATCH delay time               | 13    |    | ns   |

| t <sub>5</sub>  | LATCH high time <sup>(2)</sup> | 40    |    | ns   |

| t <sub>6</sub>  | Data setup time                | 5     |    | ns   |

| t <sub>7</sub>  | Data hold time                 | 7     |    | ns   |

| t <sub>8</sub>  | LATCH low time                 | 40    |    | ns   |

| t <sub>9</sub>  | CLR pulse duration             | 20    |    | ns   |

| t <sub>10</sub> | CLR activation time            |       | 5  | μs   |

- (1) Specified by design, not production tested.

- (2) Based on digital interface circuitry only. When writing to DAC control and configuration registers, consider the analog output specifications in #7.6.

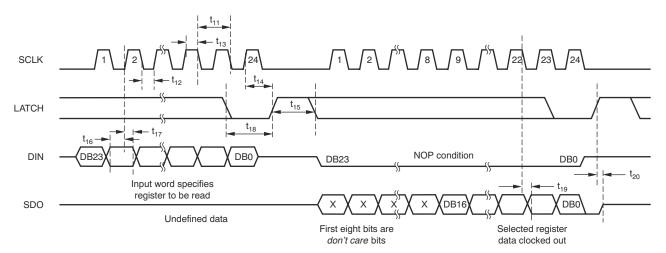

## 7.8 Timing Requirements: Readback Mode

at  $T_A = -40$ °C to 125°C and DVDD = 2.7 V to 5.5 V (unless otherwise noted)(1)

|                 |                                                                | MIN | MAX | UNIT |

|-----------------|----------------------------------------------------------------|-----|-----|------|

| t <sub>11</sub> | SCLK cycle time                                                | 60  |     | ns   |

| t <sub>12</sub> | SCLK low time                                                  | 25  |     | ns   |

| t <sub>13</sub> | SCLK high time                                                 | 25  |     | ns   |

| t <sub>14</sub> | LATCH delay time                                               | 13  |     | ns   |

| t <sub>15</sub> | LATCH high time                                                | 40  |     | ns   |

| t <sub>16</sub> | Data setup time                                                | 5   |     | ns   |

| t <sub>17</sub> | Data hold time                                                 | 7   |     | ns   |

| t <sub>18</sub> | LATCH low time                                                 | 40  |     | ns   |

| t <sub>19</sub> | Serial output delay time (C <sub>L, SDO</sub> = 15 pF)         |     | 35  | ns   |

| t <sub>20</sub> | LATCH rising edge to SDO 3-state (C <sub>L, SDO</sub> = 15 pF) |     | 35  | ns   |

(1) Specified by design, not production tested.

# 7.9 Timing Diagrams

图 7-1. Write Mode Timing

图 7-2. Readback Mode Timing

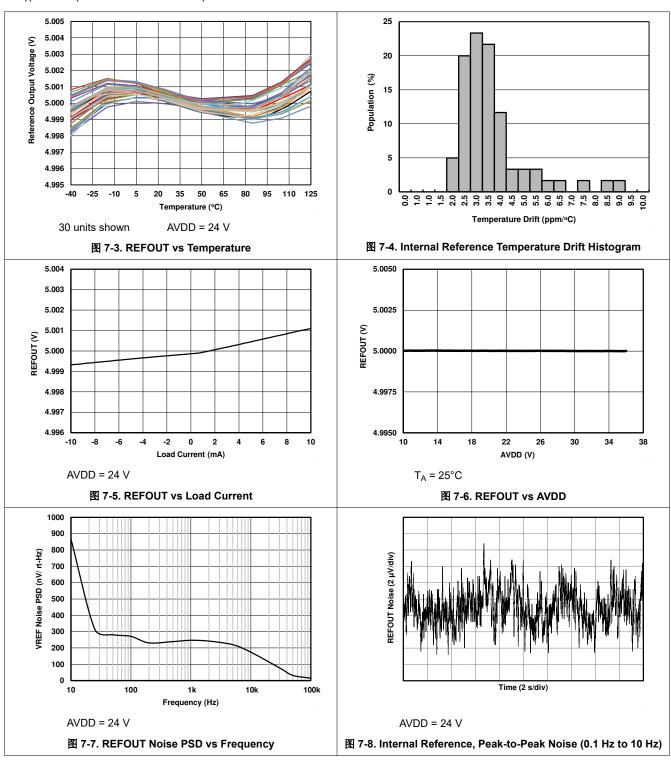

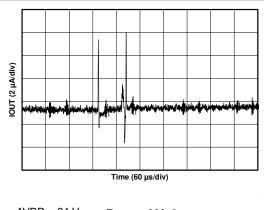

# 7.10 Typical Characteristics

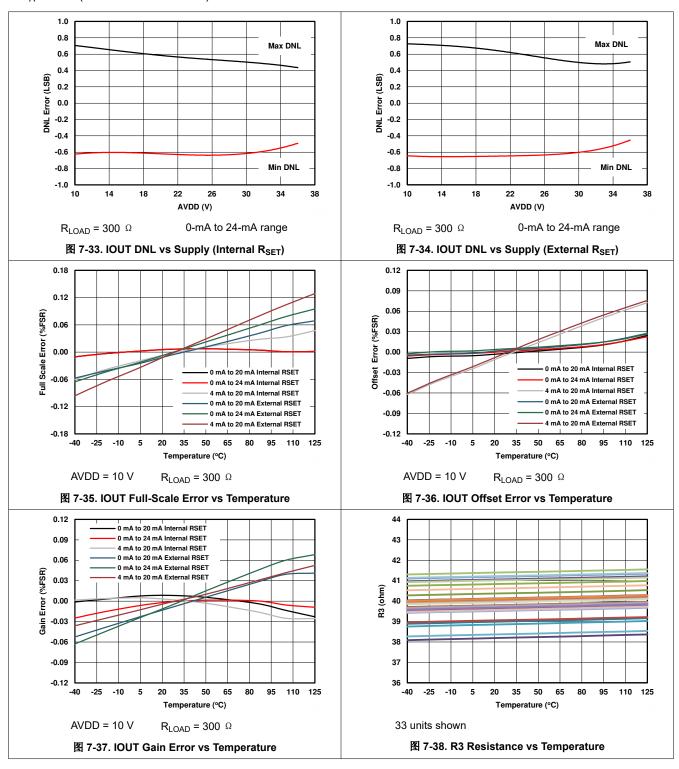

at T<sub>A</sub> = 25°C (unless otherwise noted)

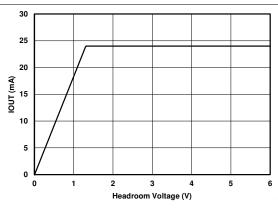

0.00 Temperature (°C) AVDD = 36 V IOUT = 24 mA

from the AVDD pin to the IOUT pin.

2.00

1.50

1.25

1.00 0.75

0.50

0.25

3 1.75

Compliance Headroom Voltage

$R_{LOAD} = 300 \Omega$ NOTE: Compliance voltage headroom is defined as the drop

图 7-39. R3 Resistance Temperature Drift Histogram

图 7-40. Compliance Headroom Voltage vs Temperature

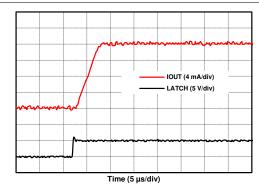

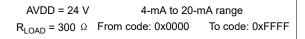

### 图 7-41. IOUT vs Compliance Headroom Voltage

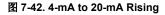

AVDD = 24 V  $R_{LOAD} = 300 \Omega$

图 7-44. IOUT Power-On Glitch

# 8 Detailed Description

## 8.1 Overview

The DAC8750 and DAC7750 are low-cost, precision, fully-integrated, 16-bit and 12-bit digital-to-analog converters (DACs) designed to meet the requirements of industrial process control applications. These devices can be programmed as a current output with a range of 4 mA to 20 mA, 0 mA to 20 mA, or 0 mA to 24 mA. The DAC8750 and DAC7750 include reliability features such as CRC error checking on the serial peripheral interface (SPI) frame, a watchdog timer, an open circuit, compliance voltage, and thermal alarm. In addition the output current can be monitored by accessing an internal precision resistor.

These devices include a power-on-reset function to ensure powering up in a known state (both IOUT is disabled and in a high-impedance state). The CLR pin sets the current output to the low-end of the range if the output is enabled. Zero code error and gain error calibration registers can be programmed to digitally calibrate the device in the end system. The output slew rate is also programmable. These devices can AC couple an external HART signal on the current output and can operate with either a 10-V to 36-V supply.

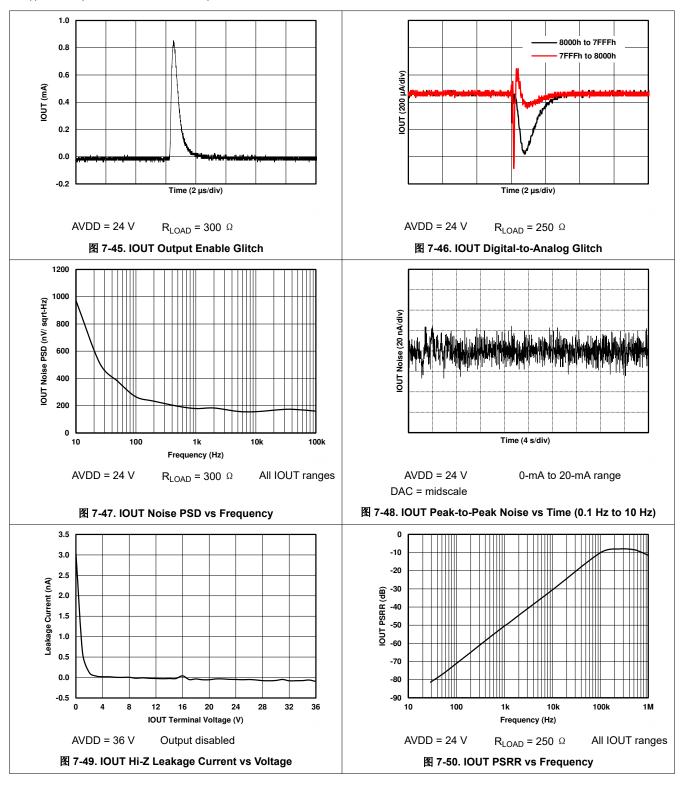

# 8.2 Functional Block Diagram

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 8.3 Feature Description

### 8.3.1 DAC Architecture

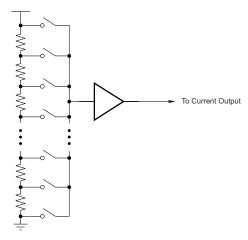

The resistor-string section is simply a string of resistors, each with the same value, from REFIN to GND, as 8-1 shows. This type of architecture makes sure the DAC is monotonic. The 16-bit (DAC8750) or 12-bit (DAC7750) binary digital code loaded to the DAC register determines at which node on the string the voltage is tapped off before it is fed into the voltage-to-current conversion stage. The current-output stage converts the voltage output from the string to current. When the output is disabled, it is in a high-impedance (Hi-Z) state. After power-on, the output is disabled.

图 8-1. DAC Structure: Resistor String

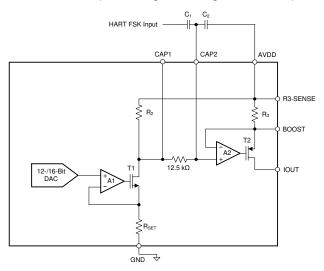

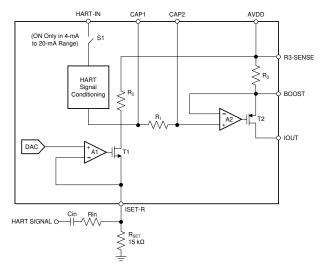

### 8.3.2 Current Output Stage

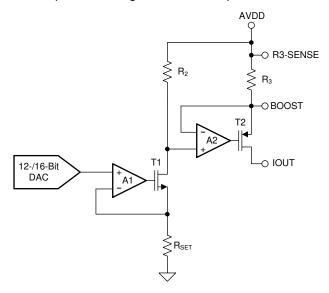

The current output stage consists of a preconditioner and a current source, as shown in 🛭 8-2. This stage provides a current output according to the DAC code. The output range can be programmed as 0 mA to 20 mA, 0 mA to 24 mA, or 4 mA to 20 mA. Use an external transistor to reduce the power dissipation of the device. The maximum compliance voltage on IOUT equals (AVDD - 2 V). In single power-supply mode, the maximum AVDD is 36 V, and the maximum compliance voltage is 34 V. After power on, the IOUT pin is in a Hi-Z state.

图 8-2. Current Output

For a 5-V reference, the output can be expressed as shown in 方程式 1 through 方程式 3.

For a 0-mA to 20-mA output range, use 方程式 1.

$$IOUT = 20mA \cdot \frac{CODE}{2^N}$$

(1)

For a 0-mA to 24-mA output range, use 方程式 2.

$$IOUT = 24mA \cdot \frac{CODE}{2^N}$$

(2)

For a 4-mA to 20-mA output range, use 方程式 3.

$$IOUT = 16mA \cdot \frac{CODE}{2^N} + 4mA$$

(3)

where

- CODE is the decimal equivalent of the code loaded to the DAC

- N is the bits of resolution; 16 for DAC8750, and 12 for DAC7750

The current-output range is normally set according to the value of the RANGE bits in the *Control Register* (see # 8.4.1 for more details).

#### 8.3.3 Internal Reference

The DACx750 includes an integrated 5-V reference with a buffered output (REFOUT) capable of driving up to 5 mA (source or sink) with an initial accuracy of ±5 mV maximum and a temperature drift coefficient of 10 ppm/°C maximum.

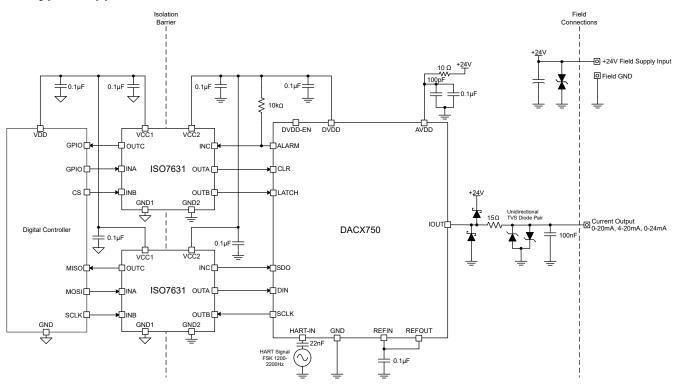

# 8.3.4 Digital Power Supply

An internally generated 4.6-V supply capable of driving up to 10 mA can be output on DVDD by leaving the DVDD-EN pin unconnected. This configuration simplifies the system power-supply design when an isolation barrier is required to generate the digital supply. The internally generated supply can be used to drive isolation components used for the digital data lines and other miscellaneous components, such as references and temperature sensors; see 39-3 for an example application.

If an external supply is preferred, the DVDD pin (which can be driven up to 5.5 V in this case) can become an input by tying DVDD-EN to GND. See #7.5 for detailed specifications.

### 8.3.5 DAC Clear

The DAC has an asynchronous clear function through the CLR pin that is active-high and allows the current output to be cleared to zero-scale code. When the CLR signal returns to low, the output remains at the cleared value. The preclear value can be restored by pulsing the LATCH signal without clocking any data. A new value cannot be programmed until the CLR pin returns to low. To avoid glitches on the output, disable the output by writing a 0 to the OUTEN bit of the *Control Register* before changing the current range.

### 8.3.6 Power-On Reset

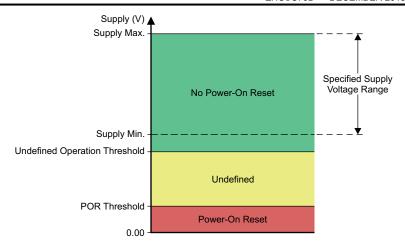

The DACx750 incorporates two internal POR circuits for the DVDD and AVDD supplies. The DVDD and AVDD POR signals are ANDed together so that both supplies must be at their minimal specified values for the device to not be in a reset condition. These POR circuits initialize internal logic and registers, as well as set the analog outputs to a known state while the device supplies are ramping. All registers are reset to their default values. Typically the POR function can be ignored, as long as the device supplies power-up and maintains the specified minimum voltage levels. However, in the case of a supply drop or brownout, the DACx750 can have an internal POR reset event or lose digital memory integrity. 8-3 represents the threshold levels for the internal POR for both the DVDD and AVDD supplies.

图 8-3. Relevant Voltage Levels for POR Circuit

For the DVDD supply, no internal POR occurs for nominal supply operation from 2.7 V (supply min) to 5.5 V (supply max). For the DVDD supply region between 2.4 V (undefined operation threshold) and 0.8 V (POR threshold), the internal POR circuit may or may not provide a reset over all temperature conditions. For the DVDD supply below 0.8 V (POR threshold), the internal POR resets if the supply voltage remains less than 0.8 V for approximately 1 ms.

For the AVDD supply, no internal POR occurs for nominal supply operation from 10 V (supply min) to 36 V (supply max). For AVDD supply voltages between 8 V (undefined operation threshold) and 1 V (POR threshold), the internal POR circuit may or may not provide a reset over all temperature conditions. For the AVDD supply below 1 V (POR threshold), the internal POR resets if the supply voltage remains less than 1 V for approximately 1 ms. In case the DVDD or AVDD supply drops to a level where the internal POR signal is indeterminate, either power cycle the device, or toggle the LATCH pin and then perform a software reset. Both options initialize the internal circuitry to a known state and provide proper operation.

#### 8.3.7 Alarm Detection

These devices also provide an alarm detection feature. When one or more of following events occur, the ALARM pin goes low:

- The current output load is in open circuit,

- The voltage at IOUT reaches a level where accuracy of the output current is compromised. This condition is

detected by monitoring internal voltage levels of the IOUT circuitry and is typically below the specified

compliance voltage headroom (defined as the voltage drop between the AVDD and IOUT pins) minimum of 2

V,

- The die temperature exceeds 142°C.

- The SPI watchdog timer exceeds the timeout period (if enabled), or

- The SPI frame error CRC check encounters an error (if enabled).

When the ALARM pins of multiple DACx750 devices are connected together to form a wired-AND function, the host processor must read the status register of each device to know all the fault conditions that are present. Note that the thermal alarm has hysteresis of approximately 18°C. After being set, the alarm only resets when the die temperature drops below 124°C.

### 8.3.8 Watchdog Timer

This feature is useful to make sure that communication between the host processor and the DACx750 has not been lost. The feature can be enabled by setting the WDEN bit of the *Configuration Register* to 1. The watchdog timeout period can be set using the WDPD bits of the configuration register, as shown in 表 8-1. The timer period is based off an internal oscillator with a typical value of 8 MHz.

表 8-1. Watchdog Timeout Period

| WATCHDOG TIMEOUT PERIOD (Typical) |

|-----------------------------------|

| 10 ms                             |

| 51 ms                             |

| 102 ms                            |

| 204 ms                            |

|                                   |

If the watchdog timer is enabled, these devices must have an SPI frame with 0x95 as the write address byte written to the device within the programmed timeout period. Otherwise, the  $\overline{\text{ALARM}}$  pin asserts low and the WD-FLT bit of the status register is set to 1. The  $\overline{\text{ALARM}}$  pin can be asserted low for any of the different conditions explained in #8.3.7. To reset the WD-FLT bit to 0, use a software reset, disable the watchdog timer, or power down the device.

### 8.3.9 Frame Error Checking

表 8-2. SPI Frame with Frame Error Checking Enabled

| BIT 31:BIT 8          | BIT 7:BIT 0          |  |  |  |

|-----------------------|----------------------|--|--|--|

| Normal SPI frame data | 8-bit CRC polynomial |  |  |  |

When in CRC mode, the DACx750 calculates CRC words every 32 clocks, unconditional of when the LATCH pin toggles. The DACx750 decodes the 32-bit input frame data to compute the CRC remainder. If no error exists in the frame, the CRC remainder is zero. When the remainder is non-zero (that is, the input frame has single- or multiple-bit errors), the  $\overline{\text{ALARM}}$  pin asserts low and the CRC-FLT bit of the status register is set to 1. The  $\overline{\text{ALARM}}$  pin can be asserted low for any of the different conditions explained in #8.3.7. To reset the CRC-FLT bit to 0, either issue software reset command of 0x96, disable the frame error checking, or power down the device. In the case of a CRC error, the specific SPI frame is blocked from writing to the device.

If CRC mode is enabled on the first frame issued to the device after power up, issue a no operation, or NOOP, command to the device in order to reset the SPI clock and SPI frame alignment in the event that any transients on the SCLK line are interpreted as SCLK periods. A NOOP command can be issued to the device by simply toggling the LATCH pin without any SCLK periods.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

#### 8.3.10 User Calibration

The device implements a user-calibration function (enabled by the CALEN bit in the *Configuration Register*) to trim system gain and zero errors. The DAC output is calibrated according to the value of the gain calibration and zero calibration registers. The range of gain adjustment is typically ±50% of full-scale with 1 LSB per step. The gain register must be programmed to 0x8000 to achieve the default gain of 1 because the power-on value of the register is 0x0000, equivalent to a gain of 0.5. The zero code adjustment is typically ±32,768 LSBs with 1 LSB per step. The input data format of the gain register is unsigned straight binary, and the input data format of the zero register is 2's complement. The gain and offset calibration is described by  $\pi$ 2.

$$CODE\_OUT = CODE \cdot \frac{User\_GAIN + 2^{15}}{2^{16}} + User\_ZERO$$

(4)

#### where

- CODE is the decimal equivalent of the code loaded to the DAC data register at address 0x01

- N is the bits of resolution (16 for DAC8750 and 12 for DAC7750)

- User\_ZERO is the signed 16-bit code in the zero register

- User\_GAIN is the unsigned 16-bit code in the gain register

- CODE\_OUT is the decimal equivalent of the code loaded to the DAC (limited between 0x0000 to 0xFFFF for DAC8750 and 0x000 to 0xFFF for DAC7750)

This is a purely digital implementation and the output is still limited by the programmed value at both ends of the current output range (set by the RANGE bits, as described in #8.4.1). In addition, the correction only makes sense for endpoints inside of the true device end points. To correct more than just the actual device error (for example, a system offset), the valid range for the adjustment changes accordingly and must be taken into account.

New calibration codes are only applied to subsequent writes to the DAC data register. Updating the calibration codes does not automatically update the DAC output. Additionally, before applying new DAC data, configure the calibration codes along with the slew rate control.

Copyright © 2022 Texas Instruments Incorporated

### 8.3.11 Programmable Slew Rate

The slew rate control feature controls the rate at which the output current changes. With the slew rate control feature disabled, the output changes smoothly at a rate limited by the output drive circuitry and the attached load.

To reduce the slew rate, enable the slew rate control feature through bit 4 of the *Control Register*. With this feature enabled, the output does not slew directly between the two values. Instead, the output steps digitally at a rate defined by bits [7:5] (SRSTEP) and bits [11:8] (SRCLK) of the *Control Register*. SRCLK defines the rate at which the digital slew updates, and SRSTEP defines the amount by which the output value changes at each update. If the DAC data register is read while the DAC output is still changing, the instantaneous value is read. 表 8-3 lists the slew rate step-size options. 表 8-4 summarizes the slew rate update clock options.

表 8-3. Slew Rate Step-Size (SRSTEP) Options

|        | STEP SIZE (LSB) |         |  |

|--------|-----------------|---------|--|

| SRSTEP | DAC7750         | DAC8750 |  |

| 000    | 0.0625          | 1       |  |

| 001    | 0.125           | 2       |  |

| 010    | 0.25            | 4       |  |

| 011    | 0.5             | 8       |  |

| 100    | 1               | 16      |  |

| 101    | 2               | 32      |  |

| 110    | 4               | 64      |  |

| 111    | 8               | 128     |  |

表 8-4. Slew Rate Update Clock (SRCLK) Options

| SRCLK | DAC UPDATE FREQUENCY (Hz) |

|-------|---------------------------|

| 0000  | 258,065                   |

| 0001  | 200,000                   |

| 0010  | 153,845                   |

| 0011  | 131,145                   |

| 0100  | 115,940                   |

| 0101  | 69,565                    |

| 0110  | 37,560                    |

| 0111  | 25,805                    |

| 1000  | 20,150                    |

| 1001  | 16,030                    |

| 1010  | 10,295                    |

| 1011  | 8,280                     |

| 1100  | 6,900                     |

| 1101  | 5,530                     |

| 1110  | 4,240                     |

| 1111  | 3,300                     |

Product Folder Links: DAC7750 DAC8750

The time required for the output to slew over a given range is expressed as 方程式 5.

Slew Time =

$$\frac{\text{Output Change}}{\text{Step Size} \cdot \text{Update Clock Frequency} \cdot \text{LSB Size}}$$

(5)

#### where

- · Slew Time is expressed in seconds

- · Output Change is expressed in amps (A) for IOUT or volts (V) for VOUT

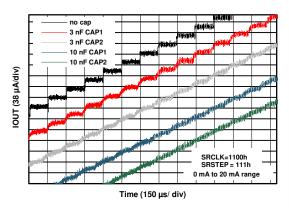

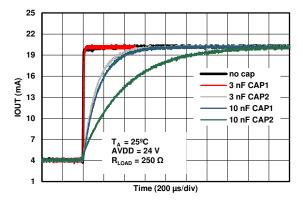

When the slew rate control feature is enabled, all output changes happen at the programmed slew rate. This configuration results in a staircase formation at the output. If the CLR pin is asserted, the output slews to the zero-scale value at the programmed slew rate. Read bit 1 (SR-ON) of the *Status Register* to verify that the slew operation has completed. The update clock frequency for any given value is the same for all output ranges. The step size, however, varies across output ranges for a given value of step size because the LSB size is different for each output range. 图 8-4 shows an example of IOUT slewing at a rate set by the previously described parameters. In this example for the DAC8750 (LSB size of 305 nA for the 0-mA to 20-mA range), the settings correspond to an update clock frequency of 6.9 kHz and a step size of 128 LSB. As shown in the case with no capacitors on CAP1 or CAP2, the steps occur at the update clock frequency (6.9 kHz corresponds to a period close to 150  $\mu$ s), and the size of each step is approximately 38  $\mu$ A (128 × 305 nA). Calculate the slew time for a specific code change by using  $\mathcal{F}$  $\mathcal{H}$ 3.

图 8-4. IOUT vs Time With Digital Slew Rate Control

Apply the desired programmable slew rate control setting before updating the DAC data register because updates to the DAC data register in tandem with updates to the slew rate control registers can create race conditions that may result in unexpected DAC data.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

## 8.4 Device Functional Modes

### 8.4.1 Setting Current-Output Ranges

The current output range is set according to  $\frac{1}{8}$  8-5.

表 8-5. RANGE Bits vs Output Range

| RANGE | OUTPUT RANGE  |

|-------|---------------|

| 101   | 4 mA to 20 mA |

| 110   | 0 mA to 20 mA |

| 111   | 0 mA to 24 mA |

Note that changing the RANGE bits at any time causes the DAC data register to be cleared.

# 8.4.2 Current-Setting Resistor

Resistor  $R_{SET}$  (used to convert the DAC voltage to current) illustrated in  $\boxtimes$  8-2 determines the stability of the output current over temperature. If desired, an external, low-drift, precision 15-k  $\Omega$  resistor can be connected to the ISET-R pin and used instead of the internal  $R_{SET}$  resistor.

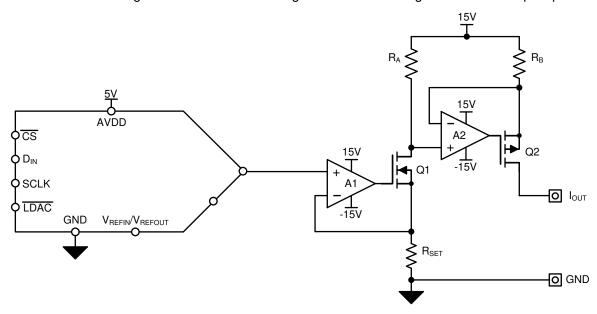

## 8.4.3 BOOST Configuration for IOUT

🛮 8-5 illustrates an external NPN transistor used to reduce power dissipation on the die. Most of the load current flows through the NPN transistor with a small amount flowing through the on-chip PMOS transistor based on the gain of the NPN transistor. This configuration reduces the temperature induced drift on the die and internal reference and is an option for use cases at the extreme end of the supply, load current, and ambient temperature ranges.

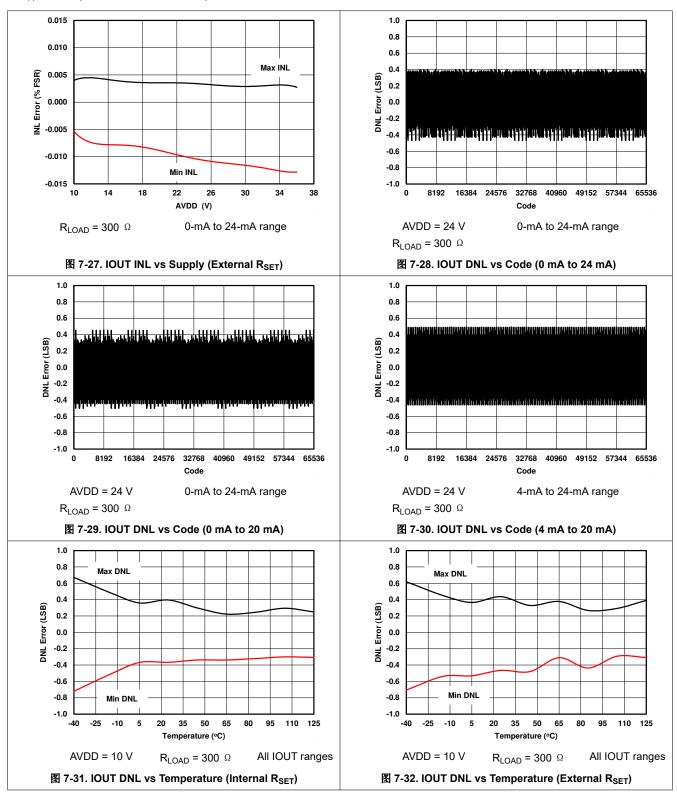

The inclusion of the bipolar junction transistor (BJT) adds an additional open loop gain to internal amplifier A2 (see  $\boxtimes$  8-2) and thus, can cause possible instability. Adding series emitter resistor R2 decreases the gain of the stage created by the BJT and internal R3 resistor (see  $\boxtimes$  8-2) especially for cases where R<sub>LOAD</sub> is a short or a very small load, such as a multimeter. Recommended values for R<sub>1</sub>, R<sub>2</sub>, and C<sub>1</sub> in this circuit are 1 k $\Omega$ , 30  $\Omega$  and 22 nF, respectively. An equivalent solution is to place R<sub>2</sub> (with a recommended value of 3 k $\Omega$  instead of 30  $\Omega$ ) in series with the base of the transistor instead of the configuration provided in  $\boxtimes$  8-5. Note that there is some gain error introduced by this configuration; see  $\boxtimes$  7-14,  $\boxtimes$  7-15 and  $\boxtimes$  7-16. Use the internal transistor in most cases because the values in # 7.5 are based on the configuration with the internal on-chip PMOS transistor.

Submit Document Feedback

Copyright © 2016, Texas Instruments Incorporated

图 8-5. Boost Mode Configuration

# 8.4.4 Filtering The Current Output

The DACx750 provides access to internal nodes of the circuit; see \$\inserpset\$ 9-2. Place capacitors on these pins and AVDD to form a filter on the output current, reducing bandwidth and the slew rate of the output, especially useful for driving inductive loads. However, to achieve large reductions in slew rate, use the programmable slew rate to avoid having to use large capacitors. Even in that case, use the capacitors on CAP1 and CAP2 to smooth out the stairsteps caused by the digital code changes as shown in \$\inserpset\$ 8-6. However, note that power supply ripple also couples into the devices through these capacitors.

图 8-6. IOUT vs Time for Different Cap Values on CAP1 and CAP2

# 8.4.5 Output Current Monitoring