Order

Now

ZHCSK33G-JULY 2008-REVISED JULY 2019

# 用于恒流 LED 驱动器的 LM342x N 沟道控制器

Technical

Documents

### 1 特性

- V<sub>IN</sub> 范围从 4.5V 至 75V

- 高侧可调节电流感应

- 2Ω、1A 峰值 MOSFET 栅极驱动器

- 输入欠压和输出过压保护

- PWM 和模拟调光

- 逐周期电流限制

- 可编程开关频率

- 零电流关断和热关断

- LED 输出状态标志(仅 LM3423 和 LM3423-Q0)

- 故障状态标志和计时器(仅LM3423和LM3423-Q0)

### 2 应用

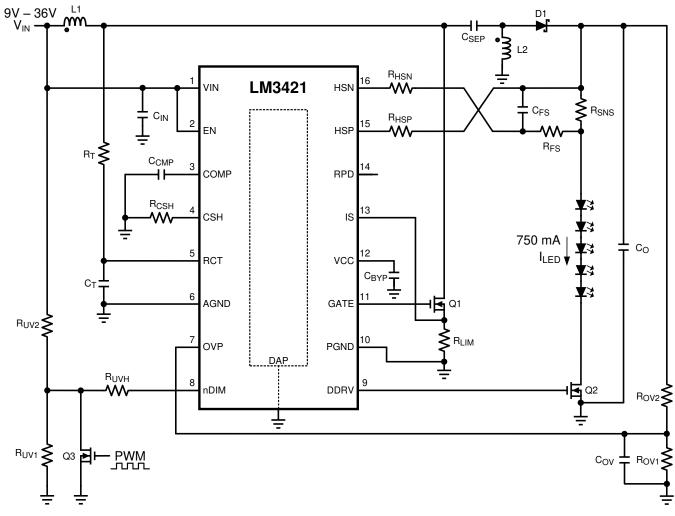

- LED 驱动器:降压、升压、降压/升压和 SEPIC

- 室内外空地 SSL

- 汽车

ÆΑ

- 通用照明

- 恒流稳压器

## 3 说明

🥭 Tools &

Software

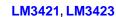

LM3421 和 LM3423 系列器件是适用于 LED 驱动器的 多功能高压 N 沟道 MOSFET 控制器。可以轻松为降 压、升压、降压/升压和 SEPIC 拓扑配置这些器件。这 一灵活性以及 75V 的输入电压额定值使得这些控制器 非常适合在多种应用中 点亮 LED。

Support &

Community

22

可调节高侧电流感应电压允许以尽可能高的效率对 LED 电流进行严格稳压。LM3421 和 LM3423 器件采 用预测性关闭时间 (PRO) 控制,此控制集成了峰值电 流模式控制和预测性关闭计时器。这种控制方法简化了 环路补偿设计,并提供了固有的输入电压前馈补偿。

LM3421 和 LM3423 器件包含一个高电压启动稳压器,此稳压器能够在 4.5V 至 75V 的宽输入范围内工作。PWM 控制器专为高达 2MHz 的可调节开关频率而设计,因此可实现紧凑的解决方案。

#### 器件信息<sup>(1)</sup>

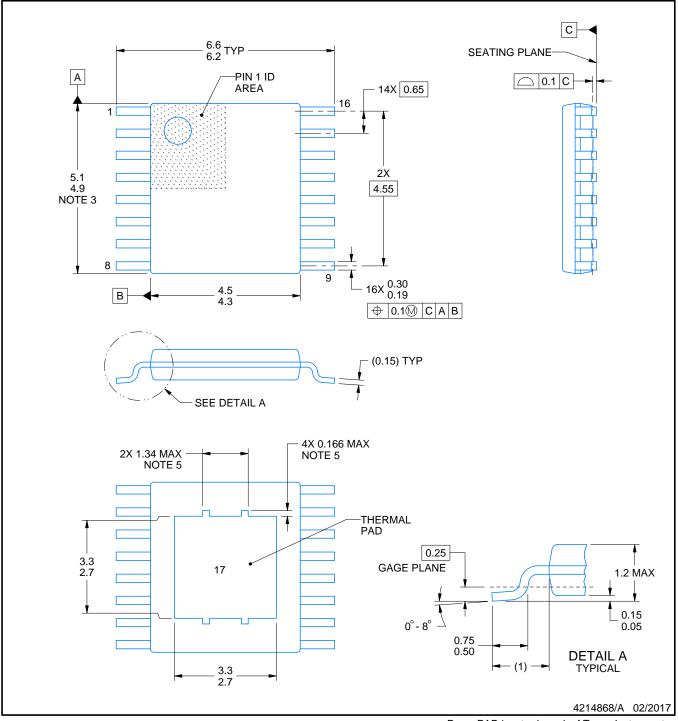

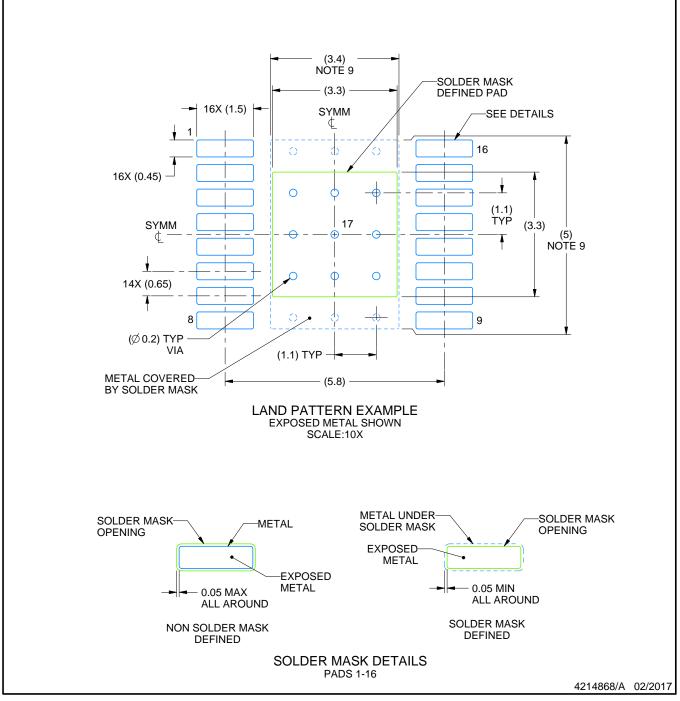

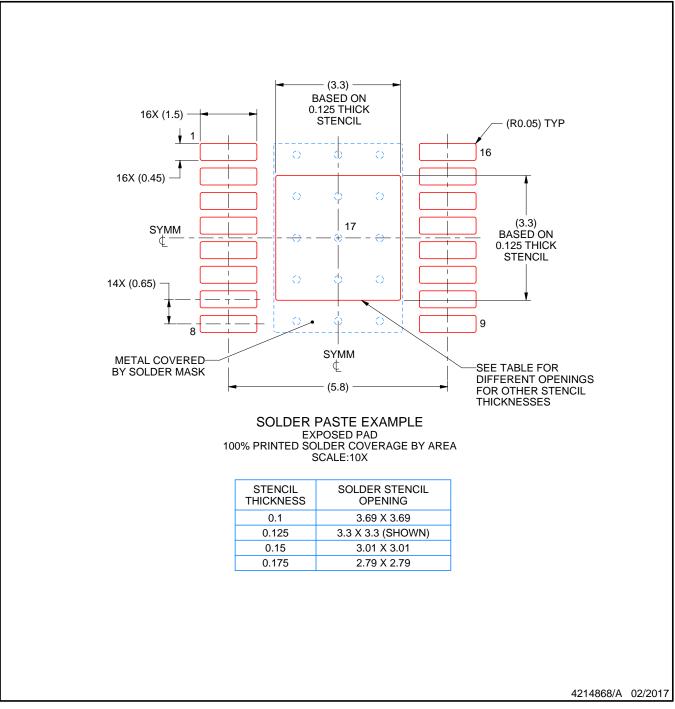

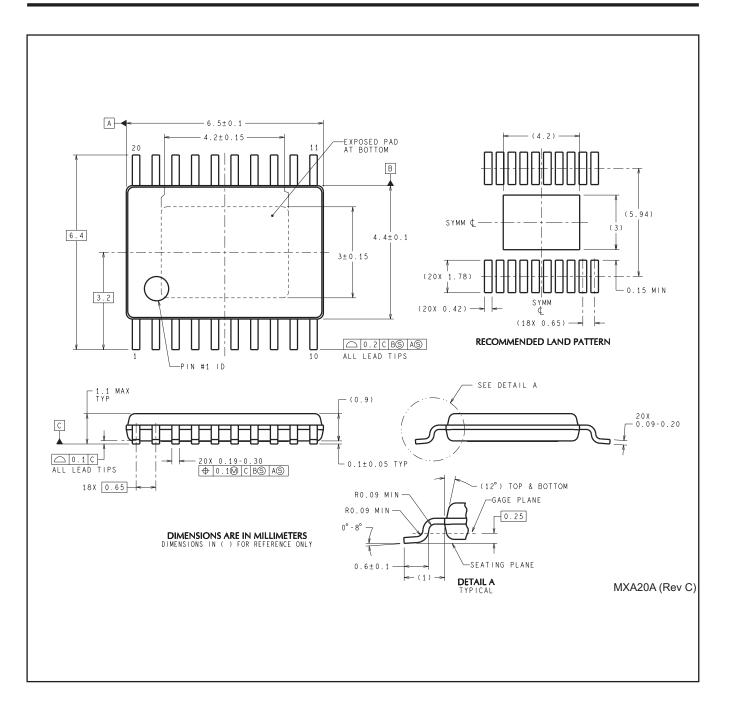

| 器件型号   | 封装          | 封装尺寸(标称值)       |  |  |  |  |

|--------|-------------|-----------------|--|--|--|--|

| LM3421 | HTSSOP (16) | 5.00mm × 4.40mm |  |  |  |  |

| LM3423 | HTSSOP (20) | 6.50mm × 4.40mm |  |  |  |  |

|        |             |                 |  |  |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

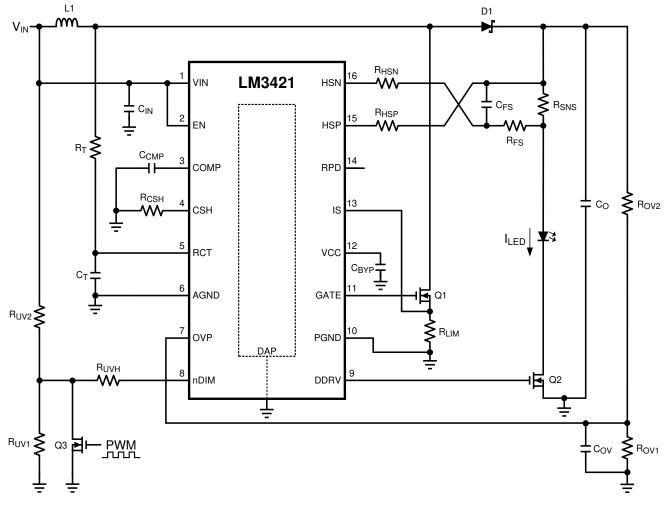

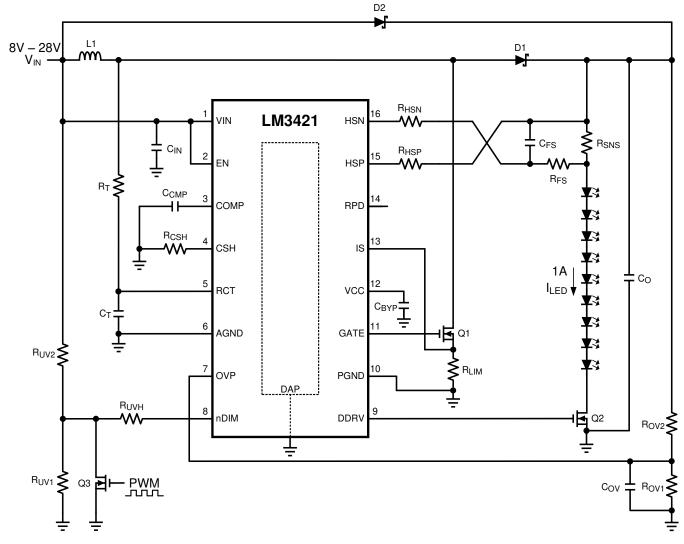

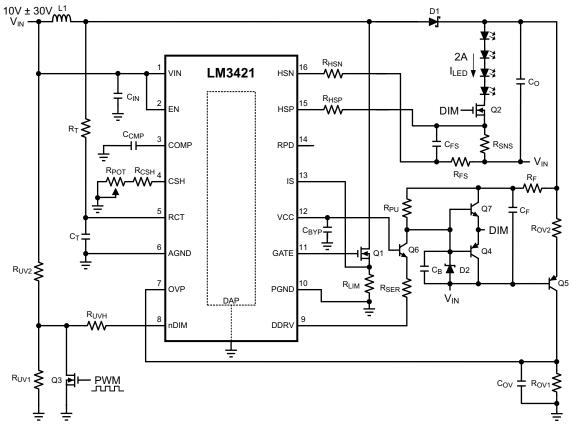

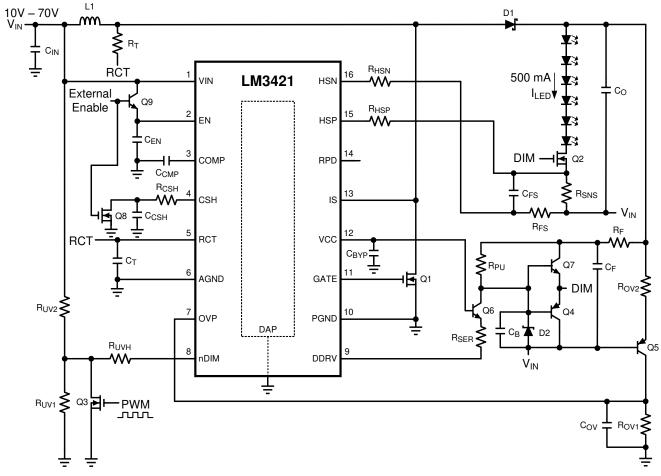

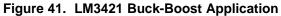

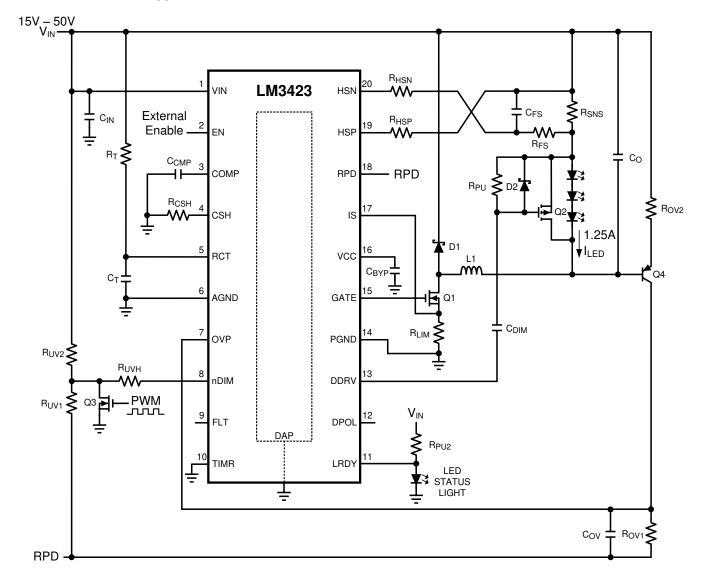

### 典型升压应用

# 目录

9

11

12.1

12.2

12.3

12.4

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   |                                    |

| 3 | 说明   |                                    |

| 4 | 修订   | 历史记录                               |

| 5 | Dev  | ice Comparison 3                   |

| 6 | Pin  | Configuration and Functions 4      |

| 7 | Spe  | cifications5                       |

|   | 7.1  | Absolute Maximum Ratings5          |

|   | 7.2  | ESD Ratings 6                      |

|   | 7.3  | Recommended Operating Conditions 6 |

|   | 7.4  | Thermal Information 6              |

|   | 7.5  | Electrical Characteristics 7       |

|   | 7.6  | Typical Characteristics 11         |

| 8 | Deta | ailed Description 13               |

|   | 8.1  | Overview 13                        |

|   | 8.2  | Functional Block Diagram 13        |

|   | 8.3  | Feature Description 14             |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Cł | hanges from Revision F (July 2015) to Revision G                                                                                         | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | 己删除 删除了对汽车级(LM342x-Q1 和 LM342x-Q0)器件的引用,现在在数据表 SNVSB95 中提供                                                                               | 1    |

| •  | Corrected typographic error in Table 1                                                                                                   | 3    |

| •  | Changed EN pulldown resistance specification minimum value from: 0.45 M $\Omega$ to: 0.245 M $\Omega$ Electrical Characteristics table.  | 7    |

| •  | Changed EN pulldown resistance specification maximum value from: 1.3 M $\Omega$ to: 2.85 M $\Omega$ in Electrical Characteristics table. | 7    |

# Changes from Revision E (April 2013) to Revision F

已添加 ESD 额定值表, 特性 说明 部分、器件功能模式、应用和实施 部分、电源建议 部分、布局 部分、器件和文档 支持 部分以及机械、封装和可订购信息 部分 .......1

# Changes from Revision D (May 2013) to Revision E

Application and Implementation ...... 28 9.2 Typical Applications ...... 32 10.1 General Recommendations ...... 65 10.2 Input Supply Current Limit ...... 65

11.1 Layout Guidelines ...... 65 11.2 Layout Example ..... 66 12 器件和文档支持 ...... 67

器件支持......67

相关链接......67

社区资源...... 67

商标......67

12.5 静电放电警告...... 67 13 机械、封装和可订购信息...... 67

### www.ti.com.cn

| P | a | g | e |

|---|---|---|---|

|   |   |   |   |

Page

# 5 Device Comparison

|           | FLAG FE    | ATURES |                  | TEMPERATURE           |  |

|-----------|------------|--------|------------------|-----------------------|--|

| DEVICE    | LED OUTPUT |        |                  | RANGE, T <sub>A</sub> |  |

| LM3421-Q0 | No         | No     | AEC-Q100 Grade 0 | -40°C to +150°C       |  |

| LM3421-Q1 | No         | No     | AEC-Q100 Grade 1 | –40°C to +125°C       |  |

| LM3423-Q0 | Yes        | Yes    | AEC-Q100 Grade 0 | –40°C to +150°C       |  |

| LM3423-Q1 | Yes        | Yes    | AEC-Q100 Grade 1 | –40°C to +125°C       |  |

| LM3421    | No         | No     | Commercial Grade | –40°C to +125°C       |  |

| LM3423    | Yes        | Yes    | Commercial Grade | –40°C to +125°C       |  |

### Table 1. Device Comparison

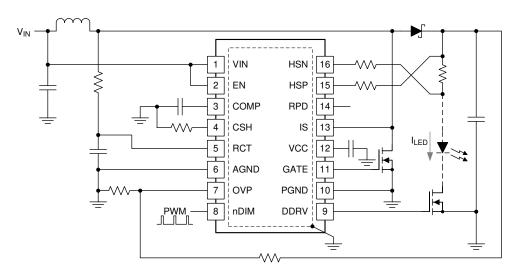

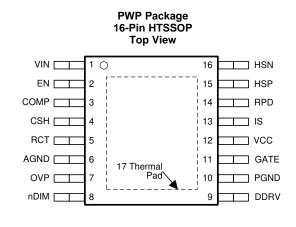

# 6 Pin Configuration and Functions

#### Pin Functions

| PIN  |        |        | I/O <sup>(1)</sup> | EUNICTION                                                                                                                                                                                                                                                                                                    |  |  |

|------|--------|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | LM3423 | LM3421 |                    | FUNCTION                                                                                                                                                                                                                                                                                                     |  |  |

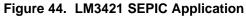

| AGND | 6      | 6      | G                  | Analog ground. Connect to PGND through the DAP copper pad to provide ground retur for CSH, COMP, RCT, and TIMR.                                                                                                                                                                                              |  |  |

| COMP | 3      | 3      | I                  | Compensation. Connect a capacitor to AGND to set the compensation.                                                                                                                                                                                                                                           |  |  |

| CSH  | 4      | 4      | I                  | Current sense high. Connect a resistor to AGND to set the signal current. For analog dimming, connect a controlled current source or a potentiometer to AGND as detailed in the <i>Analog Dimming</i> section.                                                                                               |  |  |

| DDRV | 13     | 9      | 0                  | Dim gate drive output. Connect to the gate of the dimming MOSFET.                                                                                                                                                                                                                                            |  |  |

| DPOL | 12     | _      | I                  | Dim polarity. Connect to AGND if dimming with a series P-channel MOSFET or leave open when dimming with series N-channel MOSFET.                                                                                                                                                                             |  |  |

| EN   | 2      | 2      | I                  | Enable. Connect to AGND for zero current shutdown or apply more than 2.4 V to enable device.                                                                                                                                                                                                                 |  |  |

| FLT  | 9      | _      | I                  | Fault flag. Connect to pullup resistor from VIN and N-channel MOSFET open-drain output is high when a fault condition is latched by the timer.                                                                                                                                                               |  |  |

| GATE | 15     | 11     | 0                  | Main gate drive output. Connect to the gate of the main switching MOSFET.                                                                                                                                                                                                                                    |  |  |

| HSN  | 20     | 16     | I                  | LED current sense negative. Connect through a series resistor to the negative side of the LED current sense resistor.                                                                                                                                                                                        |  |  |

| HSP  | 19     | 15     | I                  | LED current sense positive. Connect through a series resistor to the positive side of the LED current sense resistor.                                                                                                                                                                                        |  |  |

| IS   | 17     | 13     | I                  | Main switch current sense. Connect to the drain of the main N-channel MOSFET switch for R <sub>DS-ON</sub> sensing or to a sense resistor installed in the source of the same device.                                                                                                                        |  |  |

| LRDY | 11     | _      | 0                  | LED ready flag. Connect to pullup resistor from VIN and N-channel MOSFET open-drain output pulls down when the LED current is not in regulation.                                                                                                                                                             |  |  |

| nDIM | 8      | 8      | I                  | Dimming input and undervoltage protection. Connect a PWM signal for dimming as detailed in the <i>PWM Dimming</i> section and/or a resistor divider from $V_{IN}$ to program input undervoltage lockout (UVLO). Turnon threshold is 1.24 V and hysteresis for turnoff is provided by a 23-µA current source. |  |  |

| OVP  | 7      | 7      | I                  | Overvoltage protection. Connect to a resistor divider from V <sub>O</sub> to program output overvoltage lockout (OVLO). Turnoff threshold is 1.24 V and hysteresis for turnon is provided by 23-µA current source.                                                                                           |  |  |

| PGND | 14     | 10     | G                  | Power ground. Connect to AGND through the DAP copper pad to provide ground return for GATE and DDRV.                                                                                                                                                                                                         |  |  |

| RCT  | 5      | 5      | I                  | Resistor capacitor timing. External RC network sets the predictive off-time and thus the switching frequency.                                                                                                                                                                                                |  |  |

### **Pin Functions (continued)**

|                 | PIN                 |          | 1/O <sup>(1)</sup>                                                                                                                  | FUNCTION                                                                                                                    |  |

|-----------------|---------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | LM3423              | LM3421   | 100                                                                                                                                 | FUNCTION                                                                                                                    |  |

|                 |                     | I        | Resistor pulldown. Connect the low side of all external resistor dividers ( $V_{IN}$ UVLO, OVP) to implement zero-current shutdown. |                                                                                                                             |  |

| TIMR            | 10                  | _        | I                                                                                                                                   | Fault timer. Connect a capacitor to AGND to set the time delay before a sensed fault condition is latched.                  |  |

| V <sub>IN</sub> | V <sub>IN</sub> 1 1 |          | I                                                                                                                                   | Input voltage. Bypass with 100-nF capacitor to AGND as close to the device as possible in the printed-circuit-board layout. |  |

| V <sub>CC</sub> | 16                  | 12       | I                                                                                                                                   | Internal regulator output. Bypass with 2.2-µF to 3.3-µF ceramic capacitor to PGND.                                          |  |

| Thermal PAD     |                     | G        | Thermal PAD on bottom of IC. Star ground, connecting AGND and PGND.                                                                 |                                                                                                                             |  |

| DAP             | DAP (21)            | DAP (17) | G                                                                                                                                   | Star ground, connecting AGND and PGND.                                                                                      |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                  | MIN             | MAX                              | UNIT |

|--------------------------------------------------|-----------------|----------------------------------|------|

|                                                  | -0.3            | 76                               | V    |

| V <sub>IN</sub> , EN, RPD, nDIM                  | -1 continuous   |                                  | mA   |

|                                                  | -0.3            | 76                               | V    |

| OVP, HSP, HSN, LRDY, FLT, DPOL                   | -100 continuous |                                  | μA   |

| DOT                                              | -0.3            | 76                               | V    |

| RCT                                              | -1 continuous   | 5 continuous                     | mA   |

|                                                  | -0.3            | 76                               |      |

| IS                                               | -2 for 100 ns   |                                  | V    |

|                                                  | -1 continuous   |                                  | mA   |

| V <sub>cc</sub>                                  | -0.3            | 8                                | V    |

| THE                                              | -0.3            | 7                                | V    |

| TIMR                                             | -100 continuous | 100 continuous                   | μA   |

|                                                  | -0.3            | 6                                | V    |

| COMP, CSH                                        | -200 continuous | 200 continuous                   | μA   |

|                                                  | -0.3            | V <sub>CC</sub>                  |      |

| GATE, DDRV                                       | -2.5 for 100 ns | V <sub>CC</sub> + 2.5 for 100 ns | V    |

|                                                  | -1 continuous   | 1 continuous                     | mA   |

| POND                                             | -0.3            | 0.3                              |      |

| PGND                                             | –2.5 for 100 ns | 2.5 for 100 ns                   | V    |

| Continuous power dissipation                     | Internall       | y Limited                        |      |

| Maximum junction temperature                     | Internall       | y Limited                        |      |

| Maximum lead temperature (solder and reflow) (3) |                 | 260                              | °C   |

| Storage temperature                              | -65             | 150                              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) Refer to http://www.ti.com/packaging for more detailed information and mounting techniques.

ZHCSK33G – JULY 2008 – REVISED JULY 2019

www.ti.com.cn

ISTRUMENTS

EXAS

### 7.2 ESD Ratings

|        |                         |                                                                          | VALUE | UNIT |

|--------|-------------------------|--------------------------------------------------------------------------|-------|------|

| N/     | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 $^{\left( 1\right) }$ | ±2000 | V    |

| V(ESD) | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101          | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

|                                       |                | MIN | MAX | UNIT |

|---------------------------------------|----------------|-----|-----|------|

| Operating junction temperature, $T_J$ | LM3421, LM3423 | -40 | 125 | °C   |

| Input voltage, V <sub>IN</sub>        |                | 4.5 | 75  | V    |

### 7.4 Thermal Information

|                       |                                              | LM3421       | LM3423       |      |

|-----------------------|----------------------------------------------|--------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | PWP (HTSSOP) | UNIT |

|                       |                                              | 16 PINS      | 20 PINS      |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 38.9         | 36.7         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 23.1         | 21.5         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 16.8         | 18           | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.6          | 0.5          | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 16.6         | 17.8         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.7          | 1.9          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.5 Electrical Characteristics

$V_{IN} = 14$ ,  $-40^{\circ}C \le T_J \le 125^{\circ}C$  unless otherwise specified. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$ , and are provided for reference purposes only.

|                      | PARAMETER                        | TEST CONDITIONS                              | MIN   | TYP  | MAX   | UNIT |

|----------------------|----------------------------------|----------------------------------------------|-------|------|-------|------|

| START-UP             | REGULATOR                        |                                              |       |      |       |      |

| V                    | V regulation                     | $I_{CC} = 0 \text{ mA}$                      | 6.3   |      | 7.35  | V    |

| V <sub>CCREG</sub>   | V <sub>CC</sub> regulation       | $I_{CC} = 0$ mA, $T_A = 25^{\circ}C$         |       | 6.9  |       | v    |

|                      |                                  | $V_{CC} = 0 V$                               | 20    |      |       |      |

| ICCLIM               | V <sub>CC</sub> current limit    | V <sub>CC</sub> = 0 V, T <sub>A</sub> = 25°C |       | 25   |       | mA   |

|                      |                                  | V <sub>EN</sub> = 3 V, Static                |       |      | 3     |      |

| l <sub>Q</sub>       | Quiescent Current                | $V_{EN} = 3 V$ , Static, $T_A = 25^{\circ}C$ |       | 2    |       | mA   |

|                      | Chutdaura aumant                 | V <sub>EN</sub> = 0 V                        |       |      | 1     | ۵    |

| I <sub>SD</sub>      | Shutdown current                 | V <sub>EN</sub> = 0 V, T <sub>A</sub> = 25°C |       | 0.1  |       | μA   |

| V <sub>CC</sub> SUPP | LY                               |                                              |       |      |       |      |

|                      |                                  | V <sub>CC</sub> Increasing                   |       |      | 4.5   |      |

| V                    |                                  | $V_{CC}$ Increasing, $T_A = 25^{\circ}C$     |       | 4.17 |       | V    |

| V <sub>CCUV</sub>    | V <sub>CC</sub> UVLO Threshold   | V <sub>CC</sub> Decreasing                   | 3.7   |      |       | V    |

|                      |                                  | $V_{CC}$ Decreasing, $T_A = 25^{\circ}C$     |       | 4.08 |       |      |

| V <sub>CCHYS</sub>   | V <sub>CC</sub> UVLO Hysteresis  | $T_A = 25^{\circ}C$                          |       | 0.1  |       | V    |

| ENABLE T             | HRESHOLDS                        |                                              |       |      |       |      |

|                      |                                  | V <sub>EN</sub> Increasing                   |       |      | 2.4   | V    |

| EN <sub>ST</sub>     | EN start-up threshold            | $V_{EN}$ Increasing, $T_A = 25^{\circ}C$     |       | 1.75 |       |      |

|                      |                                  | V <sub>EN</sub> Decreasing                   | 0.8   |      |       |      |

| EN <sub>ST</sub>     | EN start-up threshold            | $V_{EN}$ Decreasing, $T_A = 25^{\circ}C$     |       | 1.63 |       | V    |

| EN <sub>STHYS</sub>  | EN start-up hysteresis           | $T_A = 25^{\circ}C$                          |       | 0.1  |       | V    |

| D                    |                                  | V <sub>EN</sub> = 1 V                        | 0.245 |      | 2.85  |      |

| R <sub>EN</sub>      | EN pulldown resistance           | V <sub>EN</sub> = 1 V, T <sub>A</sub> = 25°C |       | 0.82 |       | MΩ   |

| CSH THRE             | SHOLDS                           |                                              |       |      |       |      |

|                      | CSH high fault                   | CSH Increasing, $T_A = 25^{\circ}C$          |       | 1.6  |       | V    |

|                      | CSH low condition on LRDY<br>Pin | CSH increasing, $T_A = 25^{\circ}C$ LM342    | 3     | 1    |       | V    |

| OV THRES             | HOLDS                            | · ·                                          |       |      | 1     |      |

|                      |                                  | OVP Increasing                               | 1.185 |      | 1.285 |      |

| OVP <sub>CB</sub>    | OVP OVLO threshold               | OVP Increasing, $T_A = 25^{\circ}C$          |       | 1.24 |       | V    |

|                      |                                  | OVP Active (high)                            | 20    |      | 25    |      |

| OVP <sub>HYS</sub>   | OVP hysteresis source current    | OVP Active (high), $T_A = 25^{\circ}C$       |       | 23   |       | μA   |

### **Electrical Characteristics (continued)**

$V_{IN} = 14$ ,  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$  unless otherwise specified. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_{J} = 25^{\circ}C$ , and are provided for reference purposes only.

|                       | PARAMETER                                    | TEST CONDITIONS                                                      | MIN   | ТҮР                   | MAX  | UNIT |  |

|-----------------------|----------------------------------------------|----------------------------------------------------------------------|-------|-----------------------|------|------|--|

| DPOL THRE             | SHOLDS                                       |                                                                      |       |                       |      |      |  |

|                       |                                              | DPOL Increasing                                                      | 2     |                       | 2.6  |      |  |

| DPOL <sub>THRSH</sub> | DPOL logic threshold                         | DPOL Increasing, $T_A = 25^{\circ}C$                                 |       | 2.3                   |      | V    |  |

|                       |                                              |                                                                      |       |                       | 1200 | 1.0  |  |

| R <sub>DPOL</sub>     | DPOL pullup resistance                       | T <sub>A</sub> = 25°C                                                |       | 500                   |      | kΩ   |  |

|                       | ER                                           |                                                                      |       |                       |      |      |  |

|                       | Fault threshold                              |                                                                      | 1.185 |                       | 1.29 |      |  |

| V <sub>FLTTH</sub>    |                                              | $T_A = 25^{\circ}C$                                                  |       | 1.24                  |      | V    |  |

|                       |                                              |                                                                      | 10    |                       | 13   |      |  |

| FLT                   | FAULT pin source current                     | T <sub>A</sub> = 25°C                                                |       | 11.5                  |      | μA   |  |

| ERROR AMI             | PLIFIER                                      |                                                                      |       |                       |      |      |  |

|                       |                                              | w/r/t to AGND                                                        | 1.21  |                       | 1.26 |      |  |

| V <sub>REF</sub>      | CSH reference voltage                        | w/r/t to AGND, $T_J = 25^{\circ}C$                                   |       | 1.235                 |      | V    |  |

|                       | Error amplifier input bias                   |                                                                      |       |                       |      |      |  |

|                       | current                                      | $T_J = 25^{\circ}C$                                                  | -0.6  | 0                     | 0.6  | μA   |  |

|                       |                                              |                                                                      | 22    |                       | 35   |      |  |

|                       | COMP sink or source current                  | $T_J = 25^{\circ}C$                                                  |       | 30                    |      | μA   |  |

|                       | Transconductance                             | T <sub>J</sub> = 25°C                                                |       | 100                   |      | μA/\ |  |

|                       | Linear input range                           | <sup>(1)</sup> , T <sub>J</sub> = 25°C                               |       | ±125                  |      | mV   |  |

|                       | Transconductance bandwidth                   | -6dB Unloaded Response <sup>(1)</sup> ,<br>MIN = $T_J = 25^{\circ}C$ | 0.5   | 1                     |      | MHz  |  |

| OFF TIMER             |                                              | •                                                                    |       |                       |      |      |  |

|                       | Minimum OFF-time                             | RCT = 1 V through 1 k $\Omega$                                       |       |                       | 75   |      |  |

| t <sub>OFF(min)</sub> |                                              | RCT = 1 V through 1 k $\Omega$ , T <sub>J</sub> = 25°C               |       | 35                    |      | ns   |  |

| _                     | RCT reset pulldown resistance                |                                                                      |       |                       | 120  | -    |  |

| R <sub>RCT</sub>      |                                              | T <sub>J</sub> = 25°C                                                |       | 36                    |      | Ω    |  |

| V <sub>RCT</sub>      | V <sub>IN</sub> /25 reference voltage        | V <sub>IN</sub> = 14 V                                               | 540   |                       | 585  | mV   |  |

|                       |                                              | V <sub>IN</sub> = 14 V, T <sub>J</sub> = 25°C                        |       | 565                   |      |      |  |

| :                     | Continuous conduction<br>switching frequency | 2.2 nF > C <sub>T</sub> > 470 pF, T <sub>J</sub> = 25°C              |       | (See <sup>(2)</sup> ) |      | Hz   |  |

|                       | ARATOR                                       |                                                                      | l     |                       |      |      |  |

|                       |                                              |                                                                      | 700   |                       | 900  |      |  |

|                       | COMP-to-PWM offset voltage                   | $T_J = 25^{\circ}C$                                                  |       | 800                   |      | mV   |  |

| CURRENT L             | .IMIT (IS)                                   | · ·                                                                  |       |                       |      |      |  |

|                       |                                              |                                                                      | 215   |                       | 275  |      |  |

| LIM                   | Current limit threshold                      | $T_{J} = 25^{\circ}C$                                                |       | 245                   |      | mV   |  |

|                       |                                              |                                                                      |       |                       | 75   |      |  |

|                       | Current limit delay-to-output                | T <sub>J</sub> = 25°C                                                |       | 35                    |      | ns   |  |

| t <sub>LEB</sub>      | Leading edge blanking (LEB) time             |                                                                      | 115   |                       | 325  | ns   |  |

|                       |                                              | $T_{J} = 25^{\circ}C$                                                |       | 210                   |      |      |  |

| HIGH SIDE 1           | TRANSCONDUCTANCE AMPLIF                      |                                                                      |       | 2.0                   |      |      |  |

|                       | Input bias current                           | $T_J = 25^{\circ}C$                                                  |       | 11.5                  |      | μA   |  |

|                       |                                              | · J = 20 0                                                           | 20    | 11.5                  |      | μЧ   |  |

| Ям                    | Transconductance                             | T 25%C                                                               | 20    | 140                   |      | mA/∖ |  |

|                       |                                              | $T_J = 25^{\circ}C$                                                  |       | 119                   |      |      |  |

(1) Specified by design. Not production tested.

(2)  $f = 25/(C_T \times R_T)$

# **Electrical Characteristics (continued)**

$V_{IN} = 14$ ,  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$  unless otherwise specified. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_{J} = 25^{\circ}C$ , and are provided for reference purposes only.

|                                | PARAMETER                  | TEST CONDITIONS                                      | MIN   | TYP  | MAX   | UNIT |

|--------------------------------|----------------------------|------------------------------------------------------|-------|------|-------|------|

|                                | land offerst summert       |                                                      | -1.5  |      | 1.5   | μA   |

|                                | Input offset current       | $T_J = 25^{\circ}C$                                  |       | 0    |       |      |

|                                | Input offset voltage       |                                                      | -7    |      | 7     |      |

|                                |                            | $T_J = 25^{\circ}C$                                  |       | 0    |       | mV   |

| 9м(вw)                         | Transconductance bandwidth | $I_{CSH} = 100 \ \mu A^{(1)}, \ T_{J} = 25^{\circ}C$ | 250   | 500  |       | kHz  |

| GATE DRIV                      | ER (GATE)                  |                                                      |       |      | ·     |      |

| D                              | GATE sourcing resistance   | GATE = High                                          |       |      | 6     | Ω    |

| R <sub>SRC(GATE)</sub>         |                            | $GATE = High, T_J = 25^{\circ}C$                     |       | 2    |       |      |

| R <sub>SNK(GATE)</sub>         | GATE sinking resistance    | GATE = Low                                           |       |      | 4.5   | Ω    |

|                                |                            | $GATE = Low, T_J = 25^{\circ}C$                      |       | 1.3  |       |      |

| DIM DRIVER                     | R (DIM, DDRV)              |                                                      |       |      | i     |      |

| $\mathrm{nDIM}_{\mathrm{VTH}}$ | nDIM / UVLO threshold      |                                                      | 1.185 |      | 1.285 | V    |

|                                |                            | $T_J = 25^{\circ}C$                                  |       | 1.24 |       | V    |

| nDIM <sub>HYS</sub>            | nDIM hysteresis current    |                                                      | 20    |      | 25    | μA   |

|                                |                            | $T_J = 25^{\circ}C$                                  |       | 23   |       |      |

| R <sub>SRC(DDRV)</sub>         | DDRV sourcing resistance   | DDRV = High                                          |       |      | 30    | Ω    |

|                                |                            | DDRV = High, $T_J = 25^{\circ}C$                     |       | 13.5 |       |      |

| R <sub>SNK(DDRV)</sub>         | DDRV sinking resistance    | DDRV = Low                                           |       |      | 10    | Ω    |

|                                |                            | $DDRV = Low, T_J = 25^{\circ}C$                      |       | 3.5  |       |      |

| -                              |                            |                                                      | 1     |      |       |      |

### **Electrical Characteristics (continued)**

$V_{IN} = 14$ ,  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$  unless otherwise specified. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_{J} = 25^{\circ}C$ , and are provided for reference purposes only.

|                            | PARAMETER                                     | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |

|----------------------------|-----------------------------------------------|---------------------------------|-----|-----|-----|------|

| PULLDOWN N-CHANNEL MOSFETS |                                               |                                 |     |     |     |      |

| R <sub>RPD</sub>           | RPD pulldown resistance                       |                                 |     |     | 300 | 0    |

|                            |                                               | $T_{\rm J} = 25^{\circ}{\rm C}$ |     | 145 |     | Ω    |

| R <sub>FLT</sub>           | FLT pulldown resistance                       |                                 |     |     | 300 | Ω    |

|                            |                                               | $T_J = 25^{\circ}C$             |     | 145 |     |      |

| R <sub>LRDY</sub>          | LRDY pulldown resistance                      |                                 |     |     | 300 | 0    |

|                            |                                               | $T_{\rm J} = 25^{\circ}{\rm C}$ |     | 135 |     | Ω    |

| THERMAL SHUTDOWN           |                                               |                                 |     |     |     |      |

| T <sub>SD</sub>            | Thermal shutdown threshold <sup>(1)</sup>     | $T_J = 25^{\circ}C$             |     | 165 |     | °C   |

| T <sub>HYS</sub>           | Thermal shutdown<br>hysteresis <sup>(1)</sup> | $T_J = 25^{\circ}C$             |     | 25  |     | °C   |

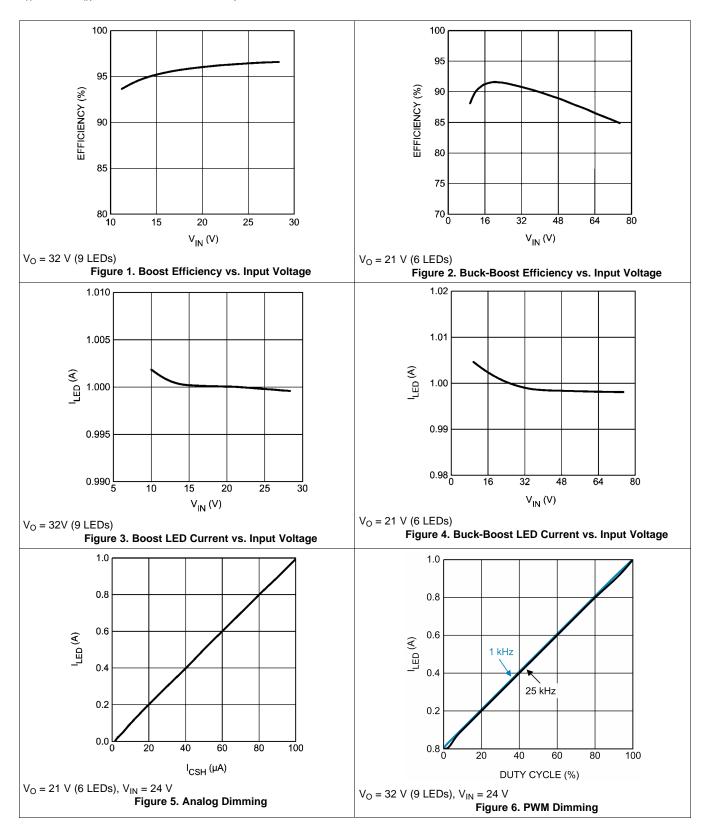

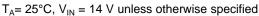

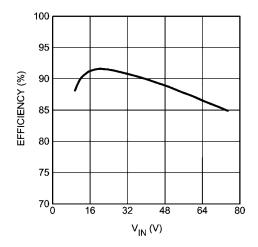

# 7.6 Typical Characteristics

$T_A$ = 25°C,  $V_{IN}$  = 14 V unless otherwise specified

# **Typical Characteristics (continued)**

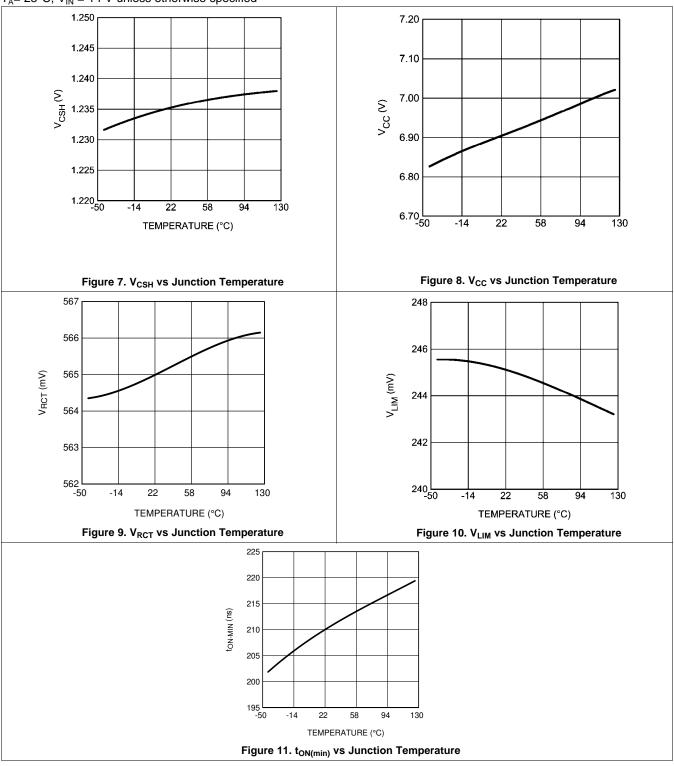

### 8 Detailed Description

### 8.1 Overview

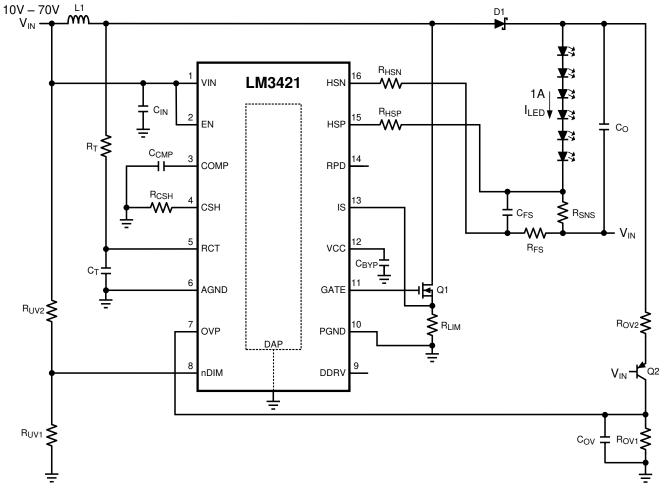

The LM3421 and LM3423 are N-channel MOSFET (N-channel FET) controllers for buck, boost and buck-boost current regulators which are ideal for driving LED loads. The controller has wide input voltage range allowing for regulation of a variety of LED loads. The high-side differential current sense, with low adjustable threshold voltage, provides an excellent method for regulating output current while maintaining high system efficiency.

The devices use a Predictive Off-time (PRO) control architecture that allows the regulator to be operated using minimal external control loop compensation, while providing an inherent cycle-by-cycle current limit. The adjustable current sense threshold provides the capability to amplitude (analog) dim the LED current and the output enable and disable function with external dimming FET driver allows for fast PWM dimming of the LED load. The maximum attainable LED current is not internally limited because the device is a controller. Instead, current is a function of the system operating point, component choices, and switching frequency that allows the device to easily provide constant currents up to 5 A. This controller contains all the features necessary to implement a high-efficiency versatile LED driver.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Current Regulators

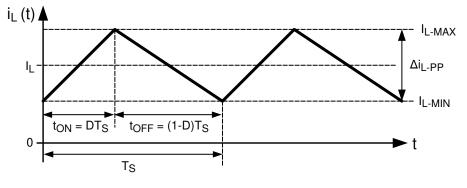

Figure 12. Ideal CCM Regulator Inductor Current i<sub>L</sub>(t)

Current regulators can create three basic topologies: buck, boost, or buck-boost. All three topologies in their most basic form contain a main switching MOSFET, a recirculating diode, an inductor and capacitors. The controller is designed to drive a ground referenced N-channel FET which is perfect for a standard boost regulator. However, buck and buck-boost regulators usually have a high-side switch. When driving an LED load, a ground referenced load is often not necessary, therefore a ground referenced switch drives a floating load instead. The controller can then be used to drive all three basic topologies as shown in the *Basic Topology Schematics* section. Other topologies such as the SEPIC and flyback converter (both derivatives of the buckboost) can be implemented as well.

Looking at the buck-boost design, the basic operation of a current regulator can be analyzed. During the time that the N-channel FET (Q1) is turned on  $(t_{ON})$ , the input voltage source stores energy in the inductor (L1) while the output capacitor (C<sub>O</sub>) provides energy to the LED load. When Q1 is turned off ( $t_{OFF}$ ), the re-circulating diode (D1) becomes forward biased and L1 provides energy to both C<sub>O</sub> and the LED load. Figure 12 shows the inductor current ( $i_L(t)$ ) waveform for a regulator operating in CCM.

The average output LED current ( $I_{LED}$ ) is proportional to the average inductor current ( $I_L$ ), therefore if  $I_L$  is tightly controlled,  $I_{LED}$  is well regulated. As the system changes input voltage or output voltage, the ideal duty cycle (D) is varied to regulate  $I_L$  and ultimately  $I_{LED}$ . For any current regulator, D is a function of the conversion ratio:

Buck

$$D = \frac{V_{O}}{V_{IN}}$$

(1)

Boost

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{O}} - \mathsf{V}_{\mathsf{IN}}}{\mathsf{V}_{\mathsf{O}}}$$

**Buck-boost**

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{O}}}{\mathsf{V}_{\mathsf{O}} + \mathsf{V}_{\mathsf{IN}}}$$

(3)

(2)

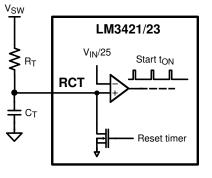

### 8.3.2 Predictive Off-Time (PRO) Control

PRO control is used by the device to control  $I_{LED}$ . It is a combination of average peak current control and a oneshot off-timer that varies with input voltage. The LM3421 and LM3423 use peak current control to regulate the average LED current through an array of HBLEDs. This method of control uses a series resistor in the LED path to sense LED current and can use either a series resistor in the MOSFET path or the MOSFET R<sub>DS-ON</sub> for both cycle-by-cycle current limit and input voltage feed forward. D is indirectly controlled by changes in both t<sub>OFF</sub> and t<sub>ON</sub>, which vary depending on the operating point.

#### Feature Description (continued)

Even though the off-time control is quasi-hysteretic, the input voltage proportionality in the off-timer creates an essentially constant switching frequency over the entire operating range for boost and buck-boost topologies. The buck topology can be designed to give constant ripple over either input voltage or output voltage, however switching frequency is only constant at a specific operating point.

This type of control minimizes the control loop compensation necessary in many switching regulators, simplifying the design process. The averaging mechanism in the peak detection control loop provides extremely accurate LED current regulation over the entire operating range.

PRO control was designed to mitigate *current mode instability* (also called *sub-harmonic oscillation*) found in standard peak current mode control when operating near or above 50% duty cycles. When using standard peak current mode control with a fixed switching frequency, this condition is present, regardless of the topology. However, using a constant off-time approach, current mode instability cannot occur, enabling easier design and control.

Predictive off-time advantages:

- There is no current mode instability at any duty cycle.

- Higher duty cycles or voltage transformation ratios are possible, especially in the boost regulator.

The only disadvantage is that synchronization to an external reference frequency is generally not available.

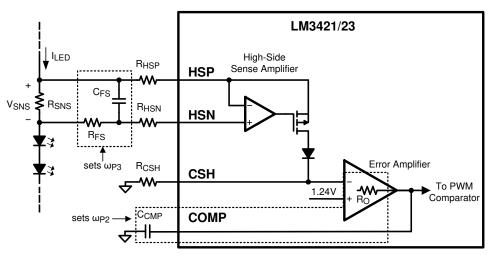

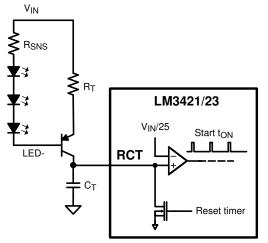

### 8.3.3 Average LED Current

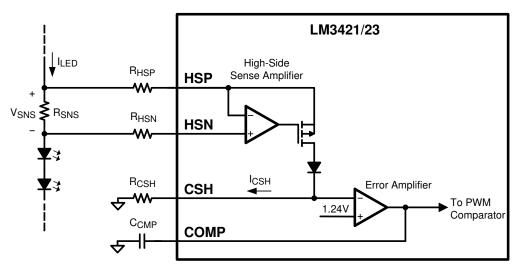

The LM3421 and LM3423 use an external current sense resistor ( $R_{SNS}$ ) placed in series with the LED load to convert the LED current ( $I_{LED}$ ) into a voltage ( $V_{SNS}$ ) as shown in Figure 13. The HSP and HSN pins are the inputs to the high-side sense amplifier which are forced to be equal potential ( $V_{HSP}=V_{HSN}$ ) through negative feedback. Because of this, the  $V_{SNS}$  voltage is forced across  $R_{HSP}$  to generate the signal current ( $I_{CSH}$ ) which flows out of the CSH pin and through the  $R_{CSH}$  resistor. The error amplifier regulates the CSH pin to 1.24 V, therefore  $I_{CSH}$  can be calculated using Equation 4.

$$I_{CSH} = \frac{V_{SNS}}{R_{HSP}}$$

(4)

This application regulates  $V_{SNS}$  as described in Equation 5.

$$V_{SNS} = 1.24V \text{ x} \frac{R_{HSP}}{R_{CSH}}$$

Calculate I<sub>LED</sub> using Equation 6.

(5)

#### Feature Description (continued)

$$I_{LED} = \frac{V_{SNS}}{R_{SNS}} = \frac{1.24V}{R_{SNS}} \times \frac{R_{HSP}}{R_{CSH}}$$

The selection of the three resistors ( $R_{SNS}$ ,  $R_{CSH}$ , and  $R_{HSP}$ ) is not arbitrary. For matching and noise performance, the suggested signal current  $I_{CSH}$  is approximately 100 µA. This current does not flow in the LEDs and does not affect either the off-state LED current or the regulated LED current.  $I_{CSH}$  can be above or below this value, but the high-side amplifier offset characteristics may be affected slightly. In addition, to minimize the effect of the high-side amplifier voltage offset on LED current accuracy, the minimum  $V_{SNS}$  is suggested to be 50 mV. Place a resistor ( $R_{HSN} = R_{HSP}$ ) in series with the HSN pin to cancel out the effects of the input bias current (approximately 10 µA) of both inputs of the high-side sense amplifier.

The sense resistor ( $R_{SNS}$ ) can be placed anywhere in the series string of LEDs as long as the voltage at the HSN and HSP pins ( $V_{HSP}$  and  $V_{HSN}$ ) satisfies the following conditions.

$$V_{HSP} < 76V$$

$$V_{HSN} > 3.5V$$

(7)

Typically, for a buck-boost configuration,  $R_{SNS}$  is placed at the bottom of the string (LED-) which allows for greater flexibility of input and output voltage. However, if there is substantial input voltage ripple allowed, it can help to place  $R_{SNS}$  at the top of the string (LED+) which limits the output voltage of the string to:

(8) The CSH pin can also be used as a low-side current sense input regulated to 1.24 V. The high-side sense amplifier is disabled if HSP and HSN are tied to AGND (or  $V_{HSN} > V_{HSP}$ ).

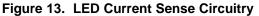

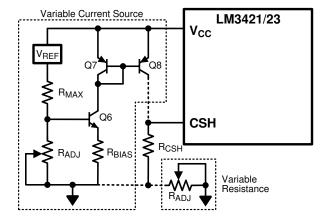

#### 8.3.4 Analog Dimming

$V_{O} = 76V - V_{IN}$

The CSH pin can be used to analog dim the LED current by adjusting the current sense voltage ( $V_{SNS}$ ). There are several different methods to adjust  $V_{SNS}$  using the CSH pin:

- 1. External variable resistance: Adjust a potentiometer placed in series with R<sub>CSH</sub> to vary V<sub>SNS</sub>.

- 2. External variable current source: Source current (0 µA to I<sub>CSH</sub>) into the CSH pin to adjust V<sub>SNS</sub>.

In general, analog dimming applications require a lower switching frequency to minimize the effect of the leading edge blanking circuit. As the LED current is reduced, the output voltage and the duty cycle decreases. Eventually, the minimum on-time is reached. The lower the switching frequency, the wider the linear dimming range. Figure 14 shows how both CSH methods are physically implemented.

Method 1 uses an external potentiometer in the CSH path which is a simple addition to the existing circuitry. However, the LEDs cannot dim completely because there is always some resistance causing signal current to flow. This method is also susceptible to noise coupling at the CSH pin because the potentiometer increases the size of the signal current loop.

(6)

www.ti.com.cn

16

#### Feature Description (continued)

Method 2 provides a complete dimming range and better noise performance, though it is more complex. It consists of a PNP current mirror and a bias network consisting of an NPN, 2 resistors and a potentiometer ( $R_{ADJ}$ ), where  $R_{ADJ}$  controls the amount of current sourced into the CSH pin. A higher resistance value sources more current into the CSH pin, causing less regulated signal current through  $R_{HSP}$ , effectively dimming the LEDs.  $V_{REF}$  should be a precise external voltage reference, while Q7 and Q8 should be a dual pair PNP for best matching and performance. The additional current ( $I_{ADD}$ ) sourced into the CSH pin can be calculated using Equation 9.

$$I_{ADD} = \frac{\left(\frac{R_{ADJ} \times V_{REF}}{R_{ADJ} + R_{MAX}}\right) - V_{BE-Q6}}{R_{BIAS}}$$

(9)

The corresponding LED current ( $I_{LED}$ ) for a specific  $I_{ADD}$  is:

$$I_{LED} = (I_{CSH} - I_{ADD}) \times \left(\frac{R_{HSP}}{R_{SNS}}\right)$$

# (10)

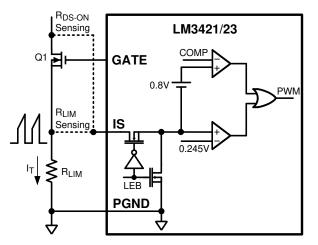

#### 8.3.5 Current Sense and Current Limit

The LM3421 and LM3423 achieve peak current mode control using a comparator that monitors the main MOSFET (Q1) transistor current, comparing it with the COMP pin voltage as shown in Figure 15. The controller incorporates a cycle-by-cycle overcurrent protection function. Aredundant internal current sense comparator provides the current limit functionality. If the voltage at the current sense comparator input (IS pin) exceeds 245 mV (typical), the on cycle is immediately terminated. The IS input pin has an internal N-channel MOSFET which pulls it down at the conclusion of every cycle. The discharge device remains on for an additional 210 ns (typical) after the beginning of a new cycle to blank the leading edge spike on the current sense signal. The leading edge blanking (LEB) determines the minimum achievable on-time (t<sub>ON-MIN</sub>).

Figure 15. Current Sense / Current Limit Circuitry

There are two possible methods to sense the transistor current. The  $R_{DS-ON}$  of the main power MOSFET can be used as the current sense resistance because the IS pin was designed to withstand the high voltages present on the drain when the MOSFET is in the off state. Alternatively, a sense resistor located in the source of the MOSFET may be used for current sensing; however, TI suggests a low inductance (ESL) type. The cycle-by-cycle current limit ( $I_{LIM}$ ) can be calculated using either method as the limiting resistance ( $R_{LIM}$ ):

$$I_{\text{LIM}} = \frac{245 \text{ mV}}{R_{\text{LIM}}}$$

(11)

#### Feature Description (continued)

#### 8.3.6 Overcurrent Protection

The LM3421 and LM3423 controllers have a secondary method of overcurrent protection. Switching action is disabled whenever the current in the LEDs is more than 30% above the regulation set point. The dimming MOSFET switch driver (DDRV) is not disabled however as this would immediately remove the fault condition and cause oscillatory behavior.

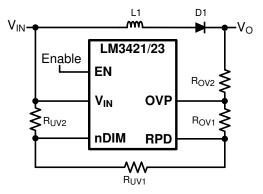

#### 8.3.7 Zero Current Shutdown

The LM3421 and LM3423 controllers implement zero current shutdown through the EN and RPD pins. When pulled low, the EN pin places the devices into near-zero current state, where only the leakage currents occurs at the pins (typical 0.1  $\mu$ A). The applications circuits frequently have resistor dividers to set UVLO, OVLO, or other similar functions. The RPD pin is an open-drain N-channel MOSFET that is enabled only when the device is enabled. Tying the bottom of all resistor dividers to the RPD pin as shown in Figure 16 allows them to float during shutdown, thus removing their current paths and providing true application-wide zero current shutdown.

Figure 16. Zero Current Shutdown Circuit

#### 8.3.8 Control Loop Compensation

The control loop is modeled as most typical current mode controllers. Using a first order approximation, the uncompensated loop can be modeled as a single pole created by the output capacitor and, in the boost and buck-boost topologies, a right half plane zero created by the inductor, where both have a dependence on the LED string dynamic resistance. There is also a high-frequency pole in the model; however, it is near the switching frequency and plays no part in the compensation design process. Therefore, it is neglected. Because ceramic capacitance is recommended for use with LED drivers, due to long lifetimes and high ripple current rating, the ESR of the output capacitor can also be neglected in the loop analysis. The DC gain of the uncompensated loop depends on internal controller gains and the external sensing network.

This section describes a buck-boost regulator as an example case.

Use Equation 12 to calculate the uncompensated loop gain for a buck-boost regulator.

$$T_{U} = T_{U0} \times \frac{\left(1 - \frac{s}{\omega_{Z1}}\right)}{\left(1 + \frac{s}{\omega_{P1}}\right)}$$

(12)

Where the uncompensated DC loop gain of the system is calculated using Equation 13.

$$T_{U0} = \frac{D' \times 500V \times R_{CSH} \times R_{SNS}}{(1+D) \times R_{HSP} \times R_{LIM}} = \frac{D' \times 620V}{(1+D) \times I_{LED} \times R_{LIM}}$$

(13)

And the output pole ( $\omega_{P1}$ ) is approximated using Equation 14.

$$\omega_{\rm P1} = \frac{1+D}{r_{\rm D} \, {\rm x} \, {\rm C}_{\rm O}} \tag{14}$$

(15)

### Feature Description (continued)

And the right half plane zero  $(\omega_{Z1})$  is:

$$\omega_{Z1} = \frac{r_D \, x \, D'^2}{D \, x \, L1}$$

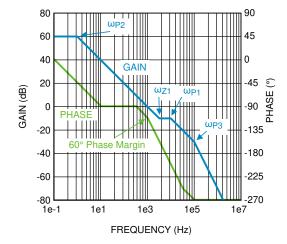

100 135  $\omega_{P1}$ ω7 80 90 GAIN 45 60 40 n 0 GAIN (dB) PHASE ( PHASE 45 20 0° Phase Margir -90 0 -135 -20 -180 -40 -225 -60 1e-1 1e1 1e3 1e5 1e7 FREQUENCY (Hz)

Figure 17. Uncompensated Loop Gain Frequency Response

Figure 17 shows the uncompensated loop gain in a worst-case scenario when the RHP zero is below the output pole. This occurs at high duty cycles when the regulator is trying to boost the output voltage significantly. The RHP zero adds 20dB/decade of gain while losing 45°/decade of phase, which places the crossover frequency (when the gain is zero dB) extremely high because the gain only starts falling again due to the high-frequency pole (not shown in Figure 17). The phase is below –180° at the crossover frequency, which means there is no phase margin (180° + phase at crossover frequency) causing system instability. Even if the output pole is below the RHP zero, the phase reaches –180° before the crossover frequency in most cases yielding instability.

Figure 18. Compensation Circuitry

#### Feature Description (continued)

To mitigate this problem, a compensator should be designed to give adequate phase margin (above 45°) at the crossover frequency. A simple compensator using a single capacitor at the COMP pin (C<sub>CMP</sub>) adds a dominant pole to the system, which ensures adequate phase margin if placed low enough. At high duty cycles (as shown in Figure 17), the RHP zero places extreme limits on the achievable bandwidth with this type of compensation. However, because an LED driver is essentially free of output transients (except catastrophic failures open or short), the dominant pole approach, even with reduced bandwidth, is usually the best approach. The dominant compensation pole ( $\omega_{P2}$ ) is determined by C<sub>CMP</sub> and the output resistance ( $R_0$ ) of the error amplifier (typically 5 M $\Omega$ ) as demonstrated in Equation 16.

$$\omega_{P2} = \frac{1}{5 \times 10^6 \times C_{CMP}} \tag{16}$$

It may also be necessary to add one final pole at least one decade above the crossover frequency to attenuate switching noise and, in some cases, provide better gain margin. This pole can be placed across R<sub>SNS</sub> to filter the ESL of the sense resistor at the same time. Figure 18 shows how the compensation is physically implemented in the system.

The high-frequency pole ( $\omega_{P3}$ ) can be calculated using Equation 17.

$$\omega_{\rm P3} = \frac{1}{\rm R_{\rm FS} \, x \, C_{\rm FS}} \tag{17}$$

The total system transfer function becomes:

1-<u>s</u>

$$T = T_{U0} x \frac{(-\omega_{Z1})}{\left(1 + \frac{s}{\omega_{P1}}\right) x \left(1 + \frac{s}{\omega_{P2}}\right) x \left(1 + \frac{s}{\omega_{P3}}\right)}$$

(18)

The resulting compensated loop gain frequency response shown in Figure 19 indicates that the system has

adequate phase margin (above 45°) if the dominant compensation pole is placed low enough, ensuring stability.

Figure 19. Compensated Loop Gain Frequency Response

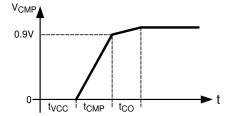

#### 8.3.9 Start-Up Regulator

The controller includes a high voltage, low dropout bias regulator. When power is applied, the regulator is enabled and sources current into an external capacitor (CBYP) connected to the V<sub>CC</sub> pin. The recommended bypass capacitance for the V<sub>CC</sub> regulator is 2.2 µF to 3.3 µF. The output of the V<sub>CC</sub> regulator is monitored by an internal UVLO circuit that protects the device from attempting to operate with insufficient supply voltage and the supply is also internally current limited. Figure 20 shows the typical start-up waveforms.

www.ti.com.cn

#### Feature Description (continued)

Figure 20. Start-Up Waveforms

First,  $C_{BYP}$  is charged to be above  $V_{CC}$  UVLO threshold (approximately 4.2 V). The  $C_{VCC}$  charging time ( $t_{VCC}$ ) can be estimated using Equation 19.

$$t_{VCC} = \frac{4.2V}{25 \text{ mA}} \times C_{BYP} = 168\Omega \times C_{BYP}$$

(19)

$C_{CMP}$  is then charged to 0.9 V over the charging time ( $t_{CMP}$ ), which can be estimated using Equation 20.

$$t_{CMP} = \frac{0.9V}{25\,\mu A} \times C_{CMP} = 36\,k\Omega \times C_{CMP}$$

(20)

Once  $C_{CMP} = 0.9$  V, the part starts switching to charge  $C_0$  until the LED current is in regulation. The  $C_0$  charging time (t<sub>C0</sub>) can be roughly estimated using Equation 21.

$$t_{CO} = C_O \times \frac{V_O}{I_{LED}}$$

(21)

The system start-up time  $(t_{SU})$  is defined using Equation 22.

$$t_{SU} = t_{VCC} + t_{CMP} + t_{CO}$$

<sup>(22)</sup>

In some configurations, the start-up waveform overshoots the steady state COMP pin voltage. In this case, the LED current and output voltage overshoots also, which can trip the overvoltage or protection, causing a race condition. The easiest way to prevent this is to use a larger compensation capacitor ( $C_{CMP}$ ), thereby slowing down the control loop.

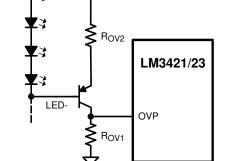

#### 8.3.10 Overvoltage Lockout (OVLO)

The LM3421 and LM3423 can be configured to detect an output (or input) overvoltage condition through the OVP pin. The pin features a precision 1.24-V threshold with 23  $\mu$ A (typical) of hysteresis current as shown in Figure 21. When the OVLO threshold is exceeded, the GATE pin is immediately pulled low and a 23- $\mu$ A current source provides hysteresis to the lower threshold of the OVLO hysteretic band.

If the LEDs are referenced to a potential other than ground (floating), as in the buck-boost and buck configuration, the output voltage ( $V_O$ ) should be sensed and translated to ground by using a single PNP as shown in Figure 22.

The overvoltage turnoff threshold (V<sub>TURN-OFF</sub>) is defined:

#### **Ground Referenced**

$$V_{\text{TURN-OFF}} = 1.24 \text{V} \text{x} \left( \frac{\text{R}_{\text{OV1}} + \text{R}_{\text{OV2}}}{\text{R}_{\text{OV1}}} \right)$$

Floating

$$V_{\text{TURN-OFF}} = 1.24 \text{V} \times \left( \frac{0.5 \times \text{R}_{\text{OV1}} + \text{R}_{\text{OV2}}}{\text{R}_{\text{OV1}}} \right)$$

(24)

21

(23)

In the ground referenced configuration, the voltage across  $R_{OV2}$  is  $V_O - 1.24$  V whereas in the floating configuration it is  $V_O - 620$  mV where 620 mV approximates  $V_{BE}$  of the PNP.

The overvoltage hysteresis (V<sub>HYSO</sub>) is defined using Equation 25.

R<sub>OV2</sub>

OVP

LED+

$V_{HYSO} = 23 \,\mu A \, x \, R_{OV2}$

OVI O 1.24 Rov

LM3421/23

23 uA

Figure 21. Overvoltage Protection Circuitry

Figure 22. Floating Output OVP Circuitry

The OVLO feature can cause some interesting results if the OVLO trip-point is set too close to V<sub>O</sub>. At turnon, the converter has a modest amount of voltage overshoot before the control loop gains control of ILED. If the overshoot exceeds the OVLO threshold, the controller shuts down, opening the dimming MOSFET. This isolates the LED load from the converter and the output capacitance. The voltage then discharges very slowly through the HSP and HSN pins until Vo drops below the lower threshold, where the process repeats. This looks like the LEDs are blinking at around 2 Hz. This mode can be escaped if the input voltage is reduced.

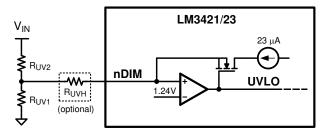

### 8.3.11 Input Undervoltage Lockout (UVLO)

22

The nDIM pin is a dual-function input that features an accurate 1.24-V threshold with programmable hysteresis as shown in Figure 23. This pin functions as both the PWM dimming input for the LEDs and as a V<sub>IN</sub> UVLO. When the pin voltage rises and exceeds the 1.24-V threshold, 23 µA (typical) of current is driven out of the nDIM pin into the resistor divider providing programmable hysteresis.

www.ti.com.cn

(25)

### Feature Description (continued)

Figure 23. UVLO Circuit

When using the nDIM pin for UVLO and PWM dimming concurrently, the UVLO circuit can have an extra series resistor to set the hysteresis. This allows the standard resistor divider to have smaller resistor values minimizing PWM delays due to a pulldown MOSFET at the nDIM pin (see *PWM Dimming* section). In general, at least 3 V of hysteresis is preferable when PWM dimming, if operating near the UVLO threshold.

The turnon threshold ( $V_{TURN-ON}$ ) is defined using Equation 26.

$$V_{\text{TURN ON}} = 1.24 \text{Vx} \left( \frac{\text{R}_{\text{UV1}} + \text{R}_{\text{UV2}}}{\text{R}_{\text{UV1}}} \right)$$

The hysteresis (V<sub>HYS</sub>) is defined as follows:

#### 8.3.11.1 UVLO Only

١

$$V_{HYS} = 23 \,\mu A \,x \,R_{UV2}$$

#### 8.3.11.2 PWM Dimming and UVLO

$$V_{HYS} = 23 \,\mu A \, x \left( R_{UV2} + \frac{R_{UVH} \, x \left( R_{UV1} + R_{UV2} \right)}{R_{UV1}} \right)$$

(28)

When zero current shutdown and UVLO are implemented together, the EN pin can be used to escape UVLO. The nDIM pin pulls up to  $V_{IN}$  when EN is pulled low. Therefore, if  $V_{IN}$  is within the UVLO hysteretic window when EN is pulled high again, the controller starts-up even though  $V_{TURN-ON}$  is not exceeded.

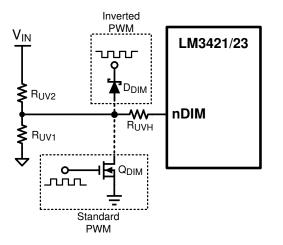

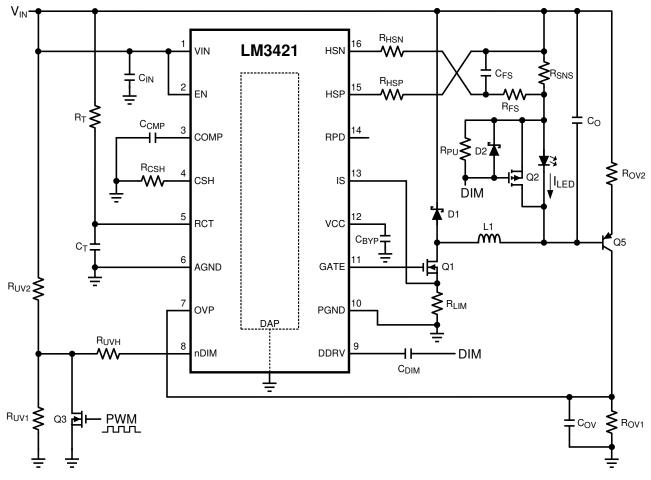

#### 8.3.12 PWM Dimming

The active low nDIM pin can be driven with a PWM signal which controls the main N-channel FET and the dimming FET (dimFET). The brightness of the LEDs can be varied by modulating the duty cycle of this signal. LED brightness is approximately proportional to the PWM signal duty cycle, (that is, 30% duty cycle equals approximately 30% LED brightness). This function can be ignored if PWM dimming is not required by using nDIM solely as a V<sub>IN</sub> UVLO input as described in *Input Undervoltage Lockout (UVLO)* or by tying it directly to V<sub>CC</sub> or V<sub>IN</sub>.

(26)

(27)

### **Feature Description (continued)**

Figure 24. PWM Dimming Circuit

### STOPPED DD EDITING HERELM3421 and LM3423

Figure 24 shows how the PWM signal is applied to nDIM:

- 1. Connect the dimming MOSFET (Q<sub>DIM</sub>) with the drain to the nDIM pin and the source to AGND. Apply an external logic-level PWM signal to the gate of Q<sub>DIM</sub>.

- 2. Connect the anode of a Schottky diode (D<sub>DIM</sub>) to the nDIM pin. Apply an inverted external logic-level PWM signal to the cathode of the same diode.

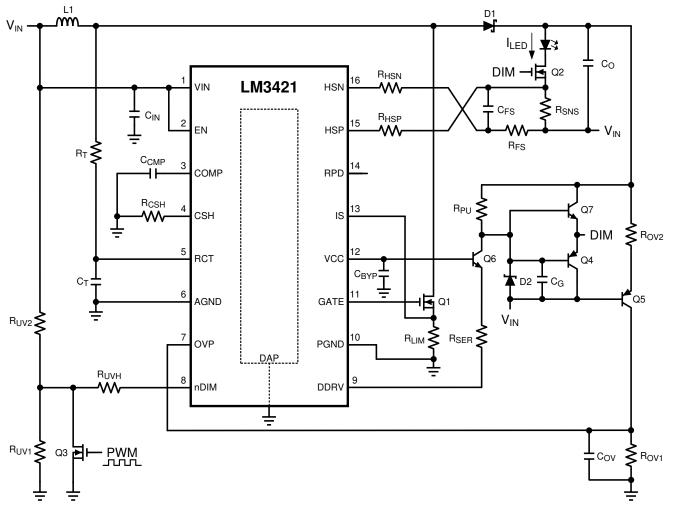

The DDRV pin is a PWM output that follows the nDIM PWM input signal. When the nDIM pin rises, the DDRV pin rises and the PWM latch reset signal is removed allowing the main MOSFET Q1 to turn on at the beginning of the next clock set pulse. In boost and buck-boost topologies, the DDRV pin is used to control a N-channel MOSFET placed in series with the LED load, while it would control a P-channel MOSFET in parallel with the load for a buck topology.

The series dimFET opens the LED load, when nDIM is low, effectively speeding up the rise and fall times of the LED current. Without any dimFET, the rise and fall times are limited by the inductor slew rate and dimming frequencies above 1 kHz are impractical. Using the series dimFET, dimming frequencies up to 30 kHz are achievable. With a parallel dimFET (buck topology), even higher dimming frequencies are achievable.

When using the PWM functionality in a boost regulator, the PWM signal can drive a ground referenced FET. However, with buck-boost and buck topologies, level shifting circuitry is necessary to translate the PWM dim signal to the floating dimFET as shown in Figure 25 and Figure 26. If high side dimming is necessary in a boost regulator using the LM3423, level shifting can be added providing the polarity inverting DPOL pin is pulled low (see *LM3423 Only: DPOL, FLT, TIMR, and LRDY* section) as shown in Figure 27.

When using a series dimFET to PWM dim the LED current, more output capacitance is always better. Typical applications use a minimum of 40  $\mu$ F for PWM dimming. For most applications, a capacitance of 40  $\mu$ F provides adequate energy storage at the output when the dimFET turns off and opens the LED load. Then when the dimFET is turned back on, the capacitance helps source current into the load, improving the LED current rise time.

A minimum on-time must be maintained in order for PWM dimming to operate in the linear region of its transfer function. Because the controller is disabled during dimming, the PWM pulse must be long enough such that the energy intercepted from the input is greater than or equal to the energy being put into the LEDs. For boost and buck-boost regulators, the minimum dimming pulse length in seconds (t<sub>PULSE</sub>) is:

$$t_{\text{PULSE}} = \frac{2 \times I_{\text{LED}} \times V_{\text{O}} \times L1}{V_{\text{IN}}^2}$$

(29)

Even maintaining a dimming pulse greater than t<sub>PULSE</sub>, preserving linearity at low dimming duty cycles is difficult.

#### Feature Description (continued)

The second helpful modification is to remove the  $C_{FS}$  capacitor and  $R_{FS}$  resistor, eliminating the high-frequency compensation pole. Typically, this does not affect stability, but it speeds up the response of the CSH pin, specifically at the rising edge of the LED current when PWM dimming, thus improving the achievable linearity at low dimming duty cycles.

Figure 25. Buck-boost Level-Shifted PWM Circuit

Figure 26. Buck Level-Shifted PWM Circuit

Figure 27. Boost Level-Shifted PWM Circuit

### Feature Description (continued)

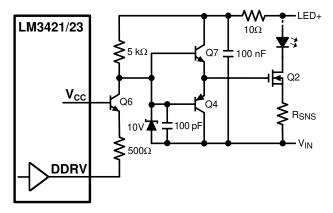

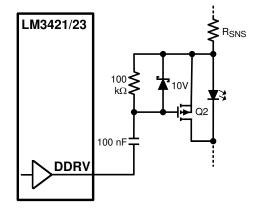

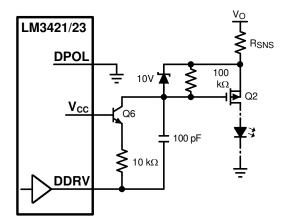

#### 8.3.13 LM3423 Only: DPOL, FLT, TIMR, and LRDY

The LM3423 has four additional pins: DPOL, FLT, TIMR, and LRDY. The DPOL pin is simply used to invert the DDRV polarity . If DPOL is left open, then it is internally pulled high and the polarity is correct for driving a series N-channel dimFET. If DPOL is pulled low then the polarity is correct for using a series P-channel dimFET in high-side dimming applications. For a parallel P-channel dimFET, as used in the buck topology, leave DPOL open for proper polarity.

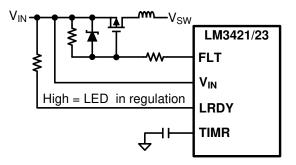

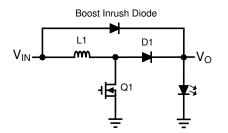

The additional TIMR and FLT pins can be used in conjunction with an input disconnect MOSFET switch as shown in Figure 28 to protect the module from various fault conditions.

A fault is detected and an 11.5  $\mu$ A (typical) current is sourced from the TIMR pin whenever any one of the following conditions exists.

- LED current is above regulation by more than 30%.

- OVLO has engaged.

- Thermal shutdown has engaged.

An external capacitor ( $C_{TMR}$ ) from TIMR to AGND programs the fault filter time as follows:

$$C_{\text{TMR}} = \frac{t_{\text{FLT}} \times 11.5 \,\mu\text{A}}{1.24 \text{V}}$$

When the voltage on the TIMR pin reaches 1.24 V, the device is latched off and the N-channel MOSFET opendrain FLT pin transitions to a high impedance state. The controller immediatly pulls the TIMR pin to ground (resets) if the fault condition is removed at any point during the filter period. Otherwise, if the timer expires, the fault remains latched until one of these situations occurs:

- The EN pin is pulled low long enough for the V<sub>CC</sub> pin to drop below 4.1 V (approximately 200 ms) or

- the TIMR pin is pulled to ground or

- a complete power cycle occurs

When using the EN and OVP pins in conjunction with the RPD pulldown pin, a race condition exists when exiting the disabled (EN low) state. When disabled, controller pulls up the OVP pin to the output voltage because the RPD pulldown is disabled, and this appears as if it is a real OVLO condition. The timer pin immediately rises and latches the controller to the fault state. To protect against this behavior, a minimum timer capacitor ( $C_{TMR} = 220$  pF) should be used. If fault latching is not required, short the TMR pin to AGND, which disables the FLT flag function.

The LM3423 also includes an LED Ready (LRDY) flag to notify the system that the LEDs are in proper regulation. The N-channel MOSFET open-drain LRDY pin is pulled low whenever any of the following conditions are met:

- 1. V<sub>CC</sub> UVLO has engaged.

- 2. LED current is below regulation by more than 20%.

- 3. LED current is above regulation by more than 30%.

- 4. Overvoltage protection has engaged

- 5. Thermal shutdown has engaged.

- 6. A fault has latched the device off.

The LRDY pin is pulled low during start-up of the device and remains low until the LED current is in regulation.

(30)

# Feature Description (continued)

Figure 28. Fault Detection and LED Status Circuit

TEXAS INSTRUMENTS

www.ti.com.cn

### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

#### 9.1.1 Inductor

The inductor (L1) is the main energy storage device in a switching regulator. Depending on the topology, energy is stored in the inductor and transfered to the load in different ways (as an example, buck-boost operation is detailed in the *Current Regulators* section). The size of the inductor, the voltage across it, and the length of the switching subinterval ( $t_{ON}$  or  $t_{OFF}$ ) determines the inductor current ripple ( $\Delta i_{L-PP}$ ). In the design process, L1 is chosen to provide a desired  $\Delta i_{L-PP}$ . For a buck regulator the inductor has a direct connection to the load, which is good for a current regulator. This requires little to no output capacitance therefore  $\Delta i_{L-PP}$  is basically equal to the LED ripple current  $\Delta i_{LED-PP}$ . However, for boost and buck-boost regulators, there is always an output capacitor which reduces  $\Delta i_{LED-PP}$ ; therefore, the inductor ripple can be larger than in the buck regulator case where output capacitance is minimal or completely absent.

In general,  $\Delta i_{LED-PP}$  is recommended by manufacturers to be less than 40% of the average LED current (I<sub>LED</sub>). Therefore, for the buck regulator with no output capacitance,  $\Delta i_{L-PP}$  should also be less than 40% of I<sub>LED</sub>. For the boost and buck-boost topologies,  $\Delta i_{L-PP}$  can be much higher depending on the output capacitance value. However,  $\Delta i_{L-PP}$  is suggested to be less than 100% of the average inductor current (I<sub>L</sub>) to limit the RMS inductor current.

L1 is also suggested to have an RMS current rating at least 25% higher than the calculated minimum allowable RMS inductor current (I<sub>L-RMS</sub>).

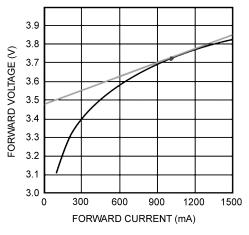

#### 9.1.2 LED Dynamic Resistance

When the load is a string of LEDs, the output load resistance is the LED string dynamic resistance plus  $R_{SNS}$ . LEDs are PN junction diodes, and their dynamic resistance shifts as their forward current changes. Dividing the forward voltage of a single LED ( $V_{LED}$ ) by the forward current ( $I_{LED}$ ) leads to an incorrect calculation of the dynamic resistance of a single LED ( $r_{LED}$ ). The result can be 5 to 10 times higher than the true  $r_{LED}$  value.

Figure 29. Dynamic Resistance

Obtaining  $r_{LED}$  is accomplished by referring to the manufacturer's LED I-V characteristic. It can be calculated as the slope at the nominal operating point as shown in Figure 29. For any application with more than 2 series LEDs,  $R_{SNS}$  can be neglected allowing  $r_D$  to be approximated as the number of LEDs multiplied by  $r_{LED}$ .

### **Application Information (continued)**

### 9.1.3 Output Capacitor

For boost and buck-boost regulators, the output capacitor ( $C_O$ ) provides energy to the load when the recirculating diode (D1) is reverse biased during the first switching subinterval. An output capacitor in a buck topology simplys reduce the LED current ripple ( $\Delta i_{LED-PP}$ ) below the inductor current ripple ( $\Delta i_{L-PP}$ ). In all cases,  $C_O$  is sized to provide a desired  $\Delta i_{LED-PP}$ . As mentioned in the *Inductor* section,  $\Delta i_{LED-PP}$  is recommended by manufacturers to be less than 40% of the average LED current ( $I_{LED}$ ).

$C_O$  should be carefully chosen to account for derating due to temperature and operating voltage. It must also have the necessary RMS current rating. Ceramic capacitors are the best choice due to their high ripple current rating, long lifetime, and good temperature performance. An X7R dieletric rating is suggested.

#### 9.1.4 Input Capacitors

The input capacitance (C<sub>IN</sub>) provides energy during the discontinuous portions of the switching period. For buck and buck-boost regulators, C<sub>IN</sub> provides energy during t<sub>ON</sub> and during t<sub>OFF</sub>, the input voltage source charges up C<sub>IN</sub> with the average input current (I<sub>IN</sub>). For boost regulators, C<sub>IN</sub> only needs to provide the ripple current due to the direct connection to the inductor. C<sub>IN</sub> is selected given the maximum input voltage ripple ( $\Delta v_{IN-PP}$ ) which can be tolerated.  $\Delta v_{IN-PP}$  is suggested to be less than 10% of the input voltage (V<sub>IN</sub>).

An input capacitance at least 100% greater than the calculated  $C_{IN}$  value is recommended to account for derating due to temperature and operating voltage. When PWM dimming, even more capacitance can be helpful to minimize the large current draw from the input voltage source during the rising transition of the LED current waveform.

The chosen input capacitors must also have the necessary RMS current rating. Ceramic capacitors are again the best choice due to their high ripple current rating, long lifetime, and good temperature performance. An X7R dielectric rating is suggested.

For most applications, TI recommends bypassing the  $V_{IN}$  pin with an 0.1  $\mu$ F ceramic capacitor placed as close as possible to the pin. In situations where the bulk input capacitance may be far from the controller, a 10- $\Omega$  series resistor can be placed between the bulk input capacitance and the bypass capacitor, creating a 150-kHz filter to eliminate undesired high-frequency noise.

#### 9.1.5 Main MOSFET / Dimming MOSFET