Application Note 1084 Parallel Application of High Speed Link

Literature Number: SNLA001

# Parallel Application of High Speed Link

National Semiconductor Application Note 1084 Susan Poniatowski June 1998

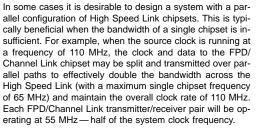

flip-flops. An inverted clock signal (either CK1 or CK2) serves to latch all data into a second flip-flop stage. The data is then available to the timing controller, preserving the overall clock frequency of 110 MHz. (See *Figure 1.*)

The primary issue with a parallel configuration is the skew between the data paths and it's impact on the reconstruction of the parallel word. Data from each path must be available at the register inputs in time to be latched on the correct clock cycle. If the skew between parallel paths is too large, data will be misaligned and corrupted at the timing controller. The total skew between the two paths must be less than the time between adjacent clock edges (43% of clock period) to guarantee that data from both paths is at the register inputs *before* the inverted clock latches the data.

The skew between the two paths consists of chip-to-chip skew of the FPD Link transmitter- and receivers, skew of the cable, and system skew to the register inputs. Additional FIFO's before the register may be used to compensate for the skew. All parallel data will be available when the register clock arrives.

It is important that the clock signal to each of the transmitters be routed to reduce skew. Each clock signal should travel the same distance across the PCB from the output of the GUI (or splitter device) before reaching the clock input pins of the odd and even transmitters.

Take the Flat Panel Display Link application for dual pixel SXGA as an example. The clock and data from the graphic controller are "split" into odd and even pixels (data). The splitter function generates two clocks-CK1 and CK2-at half of the graphic controller clock frequency (55 MHz). The splitter also separates the odd and even RGB data. This data splitting function is typically internal to the graphic controller, but may also be implemented as an ASIC external to the GUI. The odd data and CK1 are supplied to the data and clock inputs of one FPD Link transmitter: the even data and CK2 are supplied to the data and clock inputs of the second FPD Link transmitter. Data and clock of both FPD Link transmitters are sent across a cable, in parallel, to two FPD Link receivers. Timing and control signals are sent through only one of the transmitter/receiver pairs. At the output of the FPD Link receivers odd and even pixel data is sent to two parallel

www.national.com

AN-1084

#### Definition of Skew Components:

- 1. Odd/even clock skew at input of FPD Tx. Dependent on dual/single clock source and electrical delay differences in signal layout to each transmitter.

- 2. Chip-to-chip clock skew at FPD Tx outputs. Defined as  $T_{CCDmax} T_{CCDmin}$  at single temperature and  $V_{CC}$  (per FPD Link datasheet).

- Cable skew within a single cable (single cable interface is used—recommended) and defined as ps/unit length—or between two cables (if dual cable interface is used).

- Chip-to-chip clock skew at the FPD Rx outputs. Defined as R<sub>CCDmax</sub> – R<sub>CCDmin</sub> at single temperature and V<sub>CC</sub> (per FPD Link datasheet).

Total budget for skew is the time between clock edges (falling and rising) in one clock cycle. Data is latched at the flipflops on a falling edge; output of the flip-flop is then latched on the inverted rising edge.

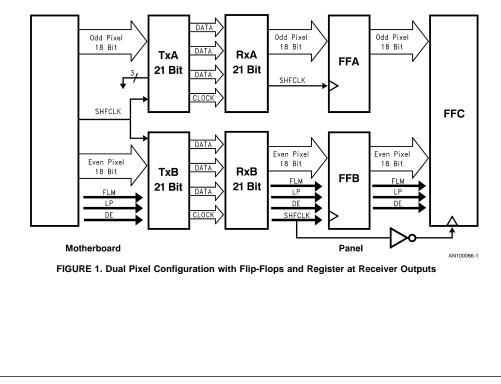

- For example, clock skew budget for SXGA:

- GUI clock = 110 MHz

- Shift clock frequency = 55 MHz

- T (shift clock period) = 18.2ns

T \* 0.43 = 7.8 ns (period multiplied by factor of 0.43 because RxCLKOUT duty cycle is 4:3 ratio)

Therefore, 1 + 2 + 3 + 4 should be less than 7.8 ns Assume:

- #1 (clock layout skew) = 50 ps

- #2 ( $T_{CCD}$  window) = 2.5 ns (Note 1)

- #3 (cable skew) = 50 ps

- #4 ( $R_{CCD}$  window) = 4 ns (Note 1)

Note 1: Based on T<sub>CCD</sub> and R<sub>CCD</sub> specification for 3.3V FPD Link Note 2: The flip flops should be integrated in the timing controller ASIC to minimize any additional delays and setup times.

#### Total skew = 6.6 ns

This value is less than 7.8 ns, therefore, the parallel word will be reconstructed correctly at the register.

FIGURE 2. Data Correctly Reconstructed at 55 MHz

www.national.com

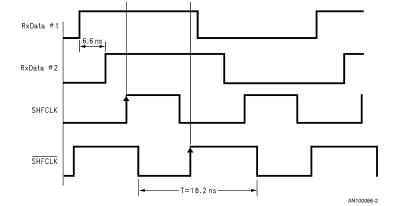

A maximum clock rate of 130MHz can be supported with a parallel configuration of the 65MHz FPD Link chipset. Due to the short clock period, FIFO's (or another method of aligning the parallel data paths) will be needed to guarantee correct reconstruction of the parallel word. For example:

GUI clock = 130 MHz

### T (shift clock period) = 15.4 ns T \* 0.43 = 6.6 ns

Using values for skew as in previous example, total skew is 6.6 ns. This is equal to the budget of 6.6 ns, therefore it may be necessary to align the data of the parallel paths (i.e., using FIFO's) to provide additional margin.

FIGURE 3. Data Incorrectly Reconstructed at 130 MHz

One way to align the data of parallel paths may be through the use of FIFO's. A FIFO may be added at the output of each receiver, before the inputs to the register. Logic would be included to monitor the "output register not empty" ( $\overline{ORE}$ ) flags of each FIFO.  $\overline{ORE}$  assertion indicates that the first parallel data word from the receiver outputs is available. When  $\overline{ORE}$  of both FIFO's is asserted, the FIFO outputs are enabled and data from both paths are transmitted to the register inputs. This method would allow for up to one clock cycle of skew between the parallel paths.

There are several reasons for using a parallel configuration of high speed links. The most common is simply to gain bandwidth—two links deliver twice the bandwidth. Using two links also allows the interface to operate at half the data rate while maintaining the bandwidth of a single link running at full speed. Lowering the data rate allows the LVDS signals to be driven a longer distance — maximum cable length increases as data rate decreases. In addition, emissions are reduced at lower speeds and electromagnetic compliance is easier to achieve.

National's LDI (LVDS Display Interface) chipset provides an optimized solution for the dual pixel interface and high bandwidth requirement of emerging technologies. A single chipset includes a dual pixel interface, eliminating the need to address device-to-device clock skew and data alignment issues. The LDI chipset operates across a large frequency range (32.5MHz to 112MHz), with the flexibility to transmit data in either dual or single pixel mode. LDI also includes features to address the requirements of high speed data transmission over a long cable interface.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| $\mathbf{\Lambda}$ | National Semiconductor | National Semiconductor               | National Semiconductor     | National Semiconductor |

|--------------------|------------------------|--------------------------------------|----------------------------|------------------------|

| N                  | Corporation            | Europe                               | Asia Pacific Customer      | Japan Ltd.             |

|                    | Americas               | Fax: +49 (0) 1 80-530 85 86          | Response Group             | Tel: 81-3-5620-6175    |

|                    | Tel: 1-800-272-9959    | Email: europe.support@nsc.com        | Tel: 65-2544466            | Fax: 81-3-5620-6179    |

|                    | Fax: 1-800-737-7018    | Deutsch Tel: +49 (0) 1 80-530 85 85  | Fax: 65-2504466            |                        |

|                    | Email: support@nsc.com | English Tel: +49 (0) 1 80-532 78 32  | Email: sea.support@nsc.com |                        |

|                    |                        | Français Tel: +49 (0) 1 80-532 93 58 |                            |                        |

| www.national.com   |                        | Italiano Tel: +49 (0) 1 80-534 16 80 |                            |                        |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

## **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|  | Products               |                                 | Applications                  |                                   |

|--|------------------------|---------------------------------|-------------------------------|-----------------------------------|

|  | Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

|  | Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

|  | Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

|  | DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

|  | DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

|  | Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

|  | Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

|  | Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

|  | Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

|  | Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

|  | RFID                   | www.ti-rfid.com                 |                               |                                   |

|  | OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

|  | Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|  |                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated