**DRV8329** SLVSGX4A - JUNE 2022 - REVISED OCTOBER 2022

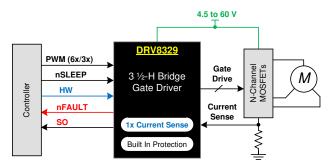

# DRV8329 4.5 to 60 V Three-phase BLDC Gate Driver

## 1 Features

- 65-V Three Phase Half-Bridge Gate Driver

- Drives 3 High-Side and 3 Low-Side N-Channel MOSFETs (NMOS)

- 4.5 to 60-V Operating Voltage Range

- Supports 100% PWM Duty Cycle with Trickle Charge pump

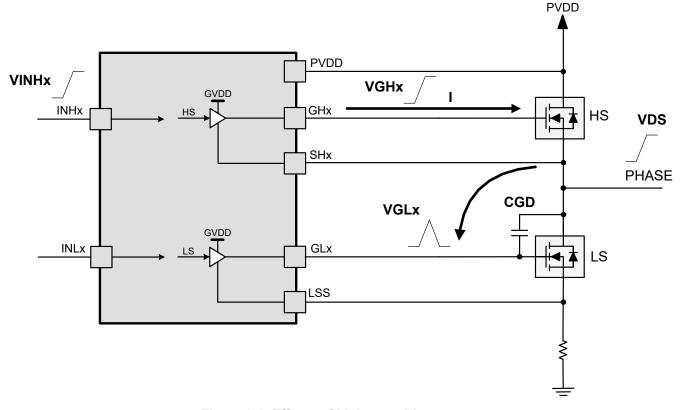

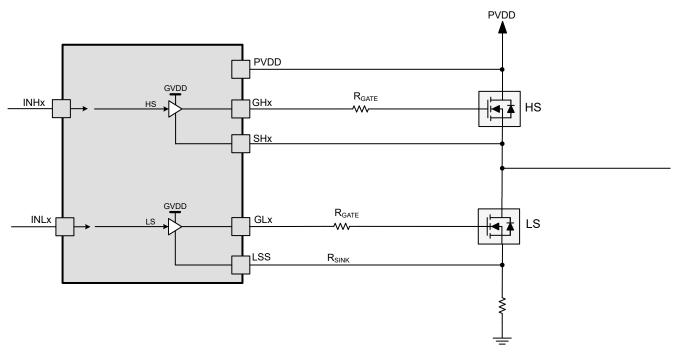

- Bootstrap based Gate Driver Architecture

- 1000-mA Maximum Peak Source Current

- 2000-mA Maximum Peak Sink Current

- Integrated Current Sense Amplifier with low input offset (optimized for 1 shunt)

- Adjustable Gain (5, 10, 20, 40 V/V)

- Hardware interface provides simple configuration

- Ultra-low power sleep mode <1 uA at 25 ℃

- 4-ns (typ) propagation delay matching between phases

- Independent driver shutdown path (DRVOFF)

- 65-V tolerant wake pin (nSLEEP)

- Supports negative transients upto -10V on SHx

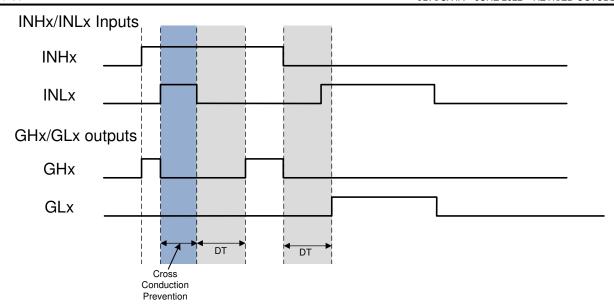

- 6x and 3x PWM Modes

- Supports 3.3-V, and 5-V Logic Inputs

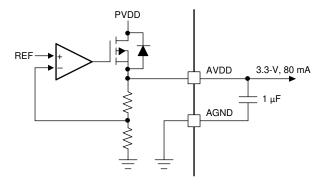

- Accurate LDO (AVDD), 3.3 V ±3%, 80 mA

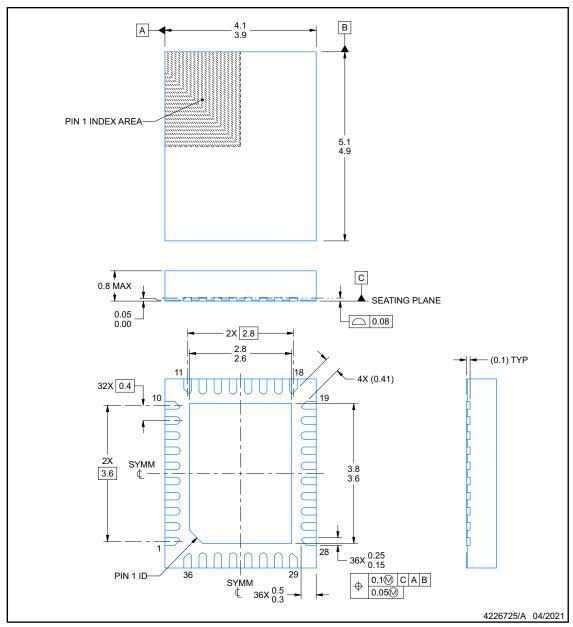

- Compact QFN Packages and Footprints

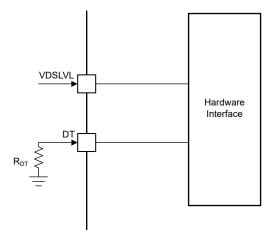

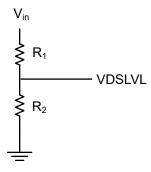

- Adjustable VDS overcurrent threshold through VDSLVL pin

- Adjustable deadtime through DT pin

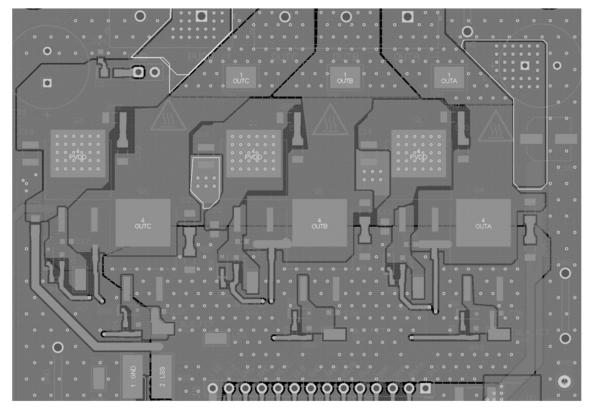

- Efficient System Design With Power Blocks

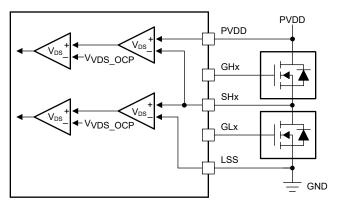

- **Integrated Protection Features**

- PVDD Undervoltage Lockout (PVDDUV)

- GVDD Undervoltage (GVDDUV)

- Bootstrap Undervoltage (BST\_UV)

- Overcurrent Protection (VDS\_OCP, SEN\_OCP)

- Thermal Shutdown (OTSD)

- Fault Condition Indicator (nFAULT)

# 2 Applications

- Brushless-DC (BLDC) Motor Modules and PMSM

- Cordless Garden and Power Tools, Lawnmowers

- **Appliances Fans and Pumps**

- Servo Drives

- E-Bikes, E-Scooters, and E-Mobility

- **Cordless Vacuum Cleaners**

- **Drones**

- Industrial & Logistics Robots, and RC Toys

# 3 Description

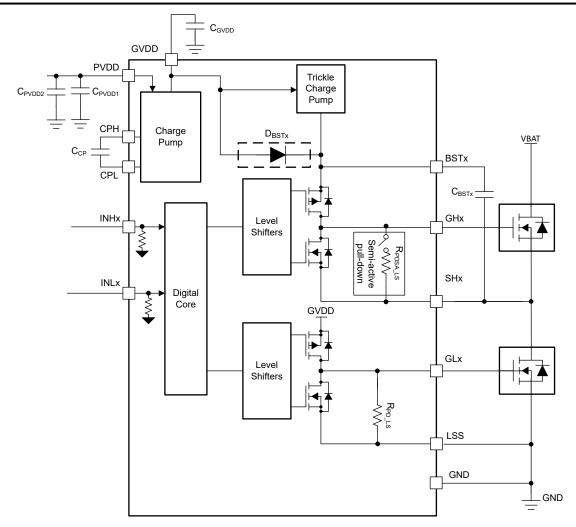

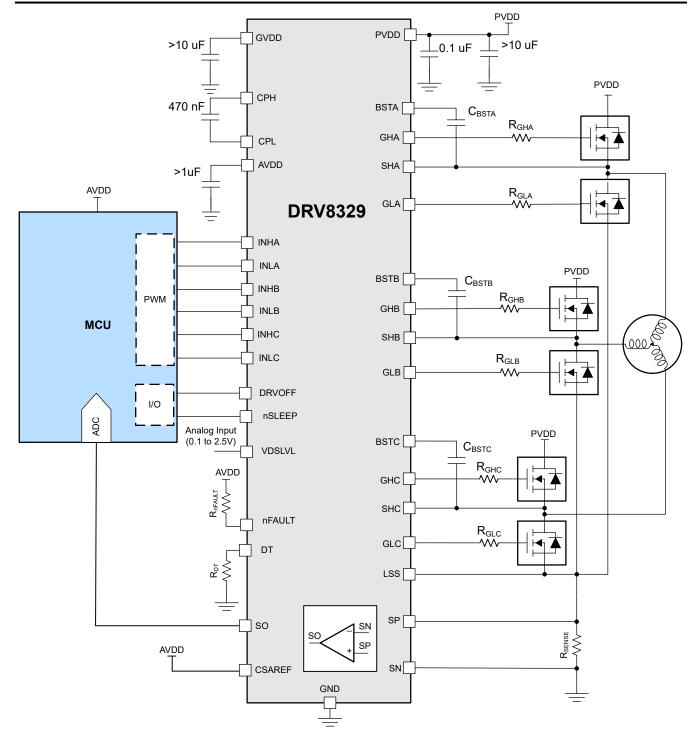

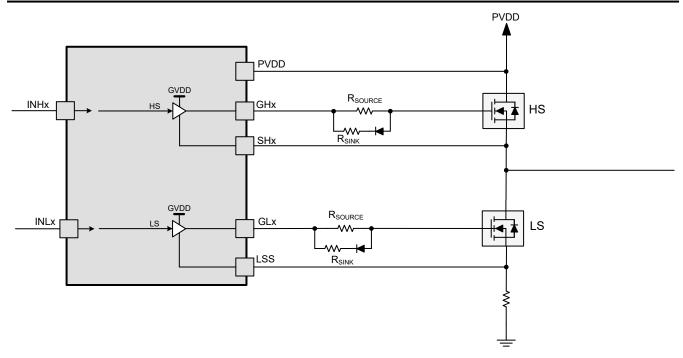

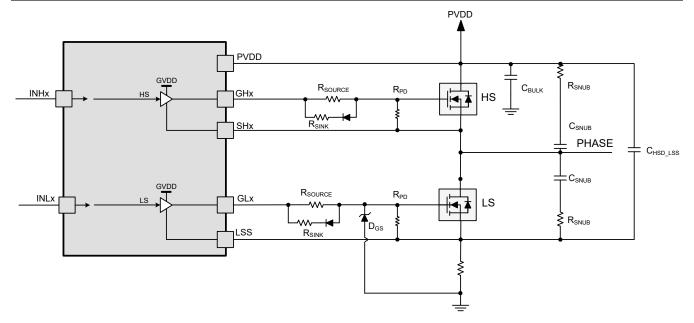

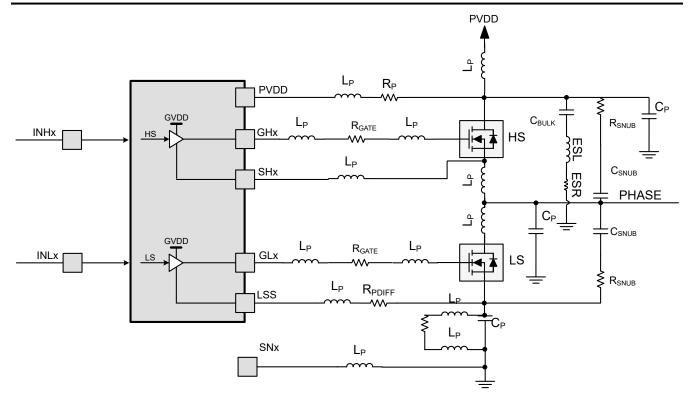

The DRV8329 family of devices is an integrated gate driver for three-phase applications. The devices provide three half-bridge gate drivers, each capable of driving high-side and low-side N-channel power MOSFETs. The device generates the correct gate drive voltages using an internal charge pump and enhances the high-side MOSFETs using a bootstrap circuit. A trickle charge pump is included to support 100% duty cycle. The Gate Drive architecture supports peak gate drive currents up to 1-A source and 2-A sink. The DRV8329 can operate from a single power supply and supports a wide input supply range of 4.5 to 60 V.

The 6x and 3x PWM modes allow for simple interfacing to controller circuits. The device has integrated accurate 3.3-V LDO that can be used to power external controller and can be used as reference for CSA. The configuration settings for the device are configurable through hardware (H/W) pins.

The DRV8329 devices integrate low-side current sense amplifier that allow current sensing for sum of current from all three phases of the drive stage.

A low-power sleep mode is provided to achieve low quiescent current by shutting down most of the internal circuitry. Internal protection functions are provided for undervoltage lockout, GVDD fault, MOSFET overcurrent, MOSFET short circuit, and overtemperature. Fault conditions are indicated on nFAULT pin.

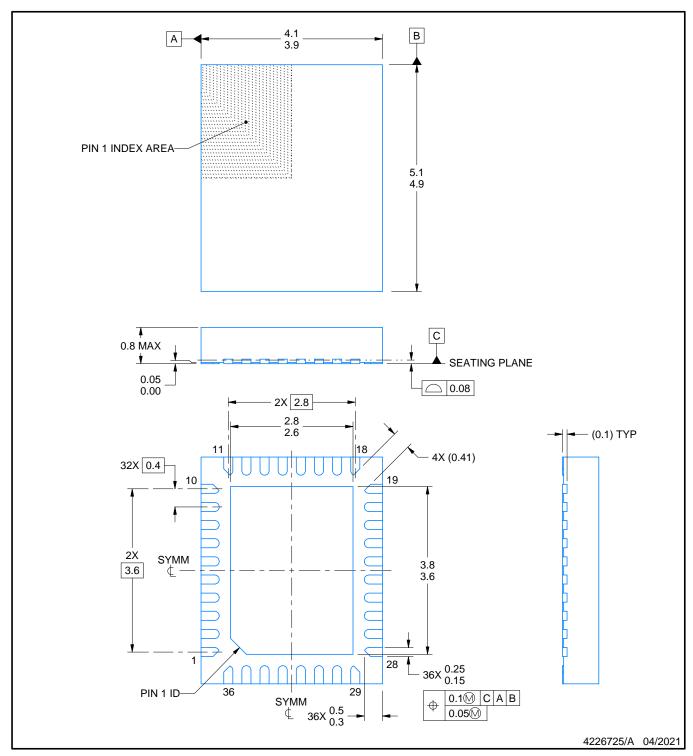

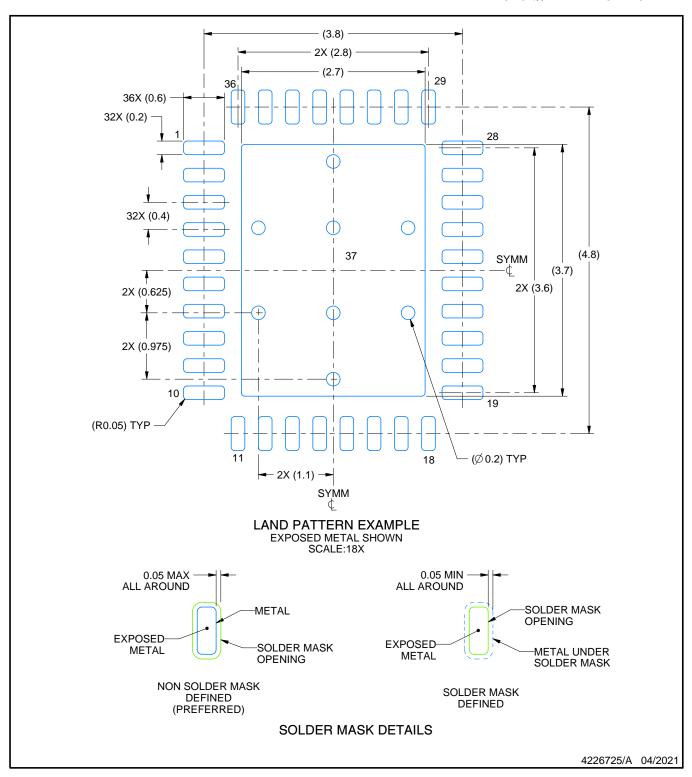

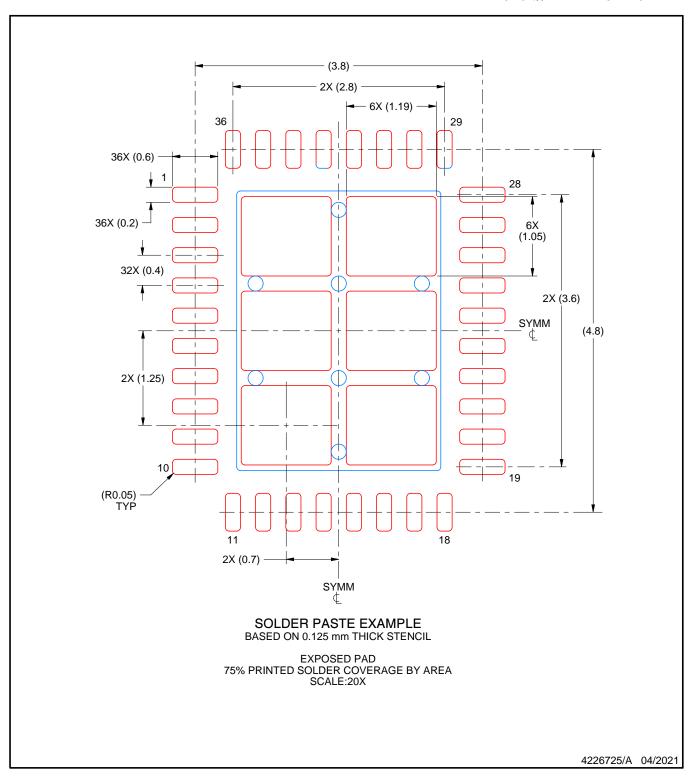

## Device Information<sup>(1)</sup>

| PART NUMBER                | PACKAGE   | BODY SIZE (NOM)   |  |  |

|----------------------------|-----------|-------------------|--|--|

| DRV8329AREE                | VQFN (36) | 5.00 mm × 4.00 mm |  |  |

| DRV8329BREE <sup>(2)</sup> | VQFN (36) | 5.00 mm × 4.00 mm |  |  |

- For all available packages, see the orderable addendum at the end of the data sheet.

- Device available for preview only

**DRV8329 Simplified Schematic**

# **Table of Contents**

| 1 Features1                           | 9.1 Application Information29                          |

|---------------------------------------|--------------------------------------------------------|

| 2 Applications 1                      | 9.2 Typical Application29                              |

| 3 Description1                        | 10 Power Supply Recommendations44                      |

| 4 Revision History2                   | 10.1 Bulk Capacitance Sizing44                         |

| 5 Device Comparison Table3            | 11 Layout45                                            |

| 6 Pin Configuration and Functions4    | 11.1 Layout Guidelines45                               |

| 7 Specification6                      | 11.2 Layout Example47                                  |

| 7.1 Absolute Maximum Ratings6         | 11.3 Thermal Considerations48                          |

| 7.2 ESD Ratings Comm6                 | 12 Device and Documentation Support49                  |

| 7.3 Recommended Operating Conditions7 | 12.1 Device Support                                    |

| 7.4 Thermal Information 1pkg7         | 12.2 Documentation Support49                           |

| 7.5 Electrical Characteristics8       | 12.3 Related Links49                                   |

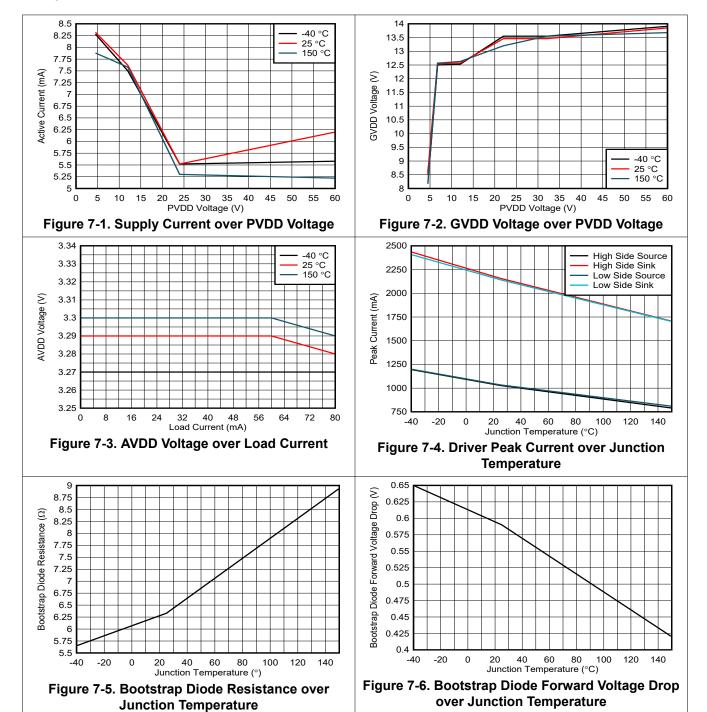

| 7.6 Typical Characteristics15         | 12.4 Receiving Notification of Documentation Updates49 |

| 8 Detailed Description16              | 12.5 Community Resources49                             |

| 8.1 Overview                          | 12.6 Trademarks49                                      |

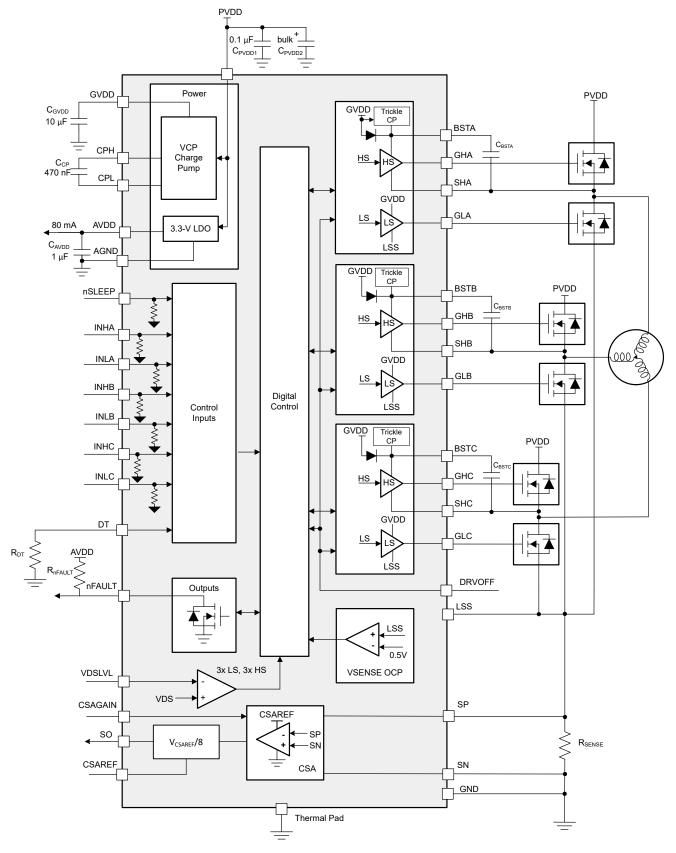

| 8.2 Functional Block Diagram17        | 13 Mechanical, Packaging, and Orderable                |

| 8.3 Feature Description               | Information49                                          |

| 8.4 Device Functional Modes28         | 13.1 Tape and Reel Information53                       |

| 9 Application and Implementation29    | ·                                                      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Revision * (June 2022) to Revision A (October 2022) | Page |

|---|------------------------------------------------------------------|------|

| • | Updated device status to Production Data                         | 1    |

# **5 Device Comparison Table**

# **Table 5-1. Different Device Variants**

| DEVICE   | DEVICE VARIANT | Package             | LDO output | DT pin and VDSLVL | PWM_MODE |

|----------|----------------|---------------------|------------|-------------------|----------|

| DD\/8320 | DRV8329A       | 36-pin QFN          | 3.3 V      | Available         | 6x       |

| DRV8329  | DRV8329B       | (5.00 mm x 4.00 mm) | 3.5 V      | Available         | 3x       |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

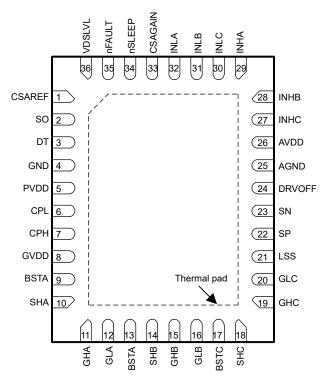

# **6 Pin Configuration and Functions**

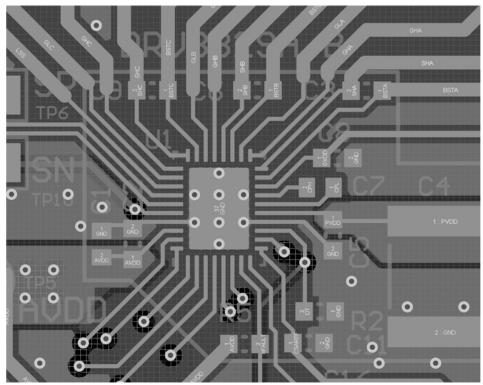

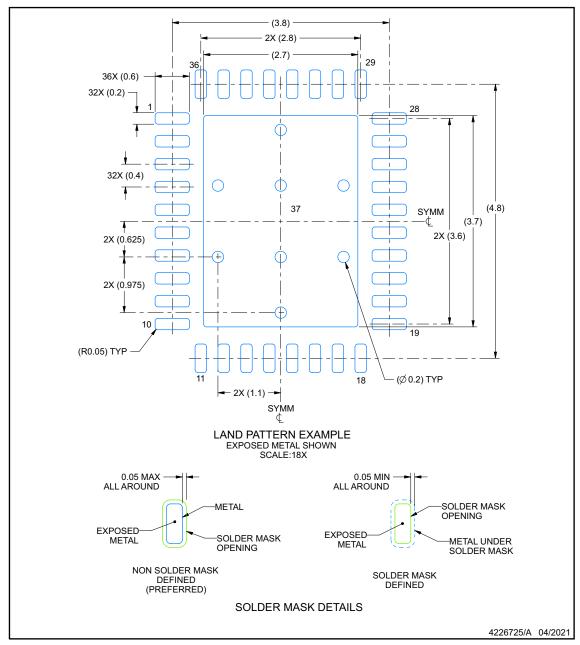

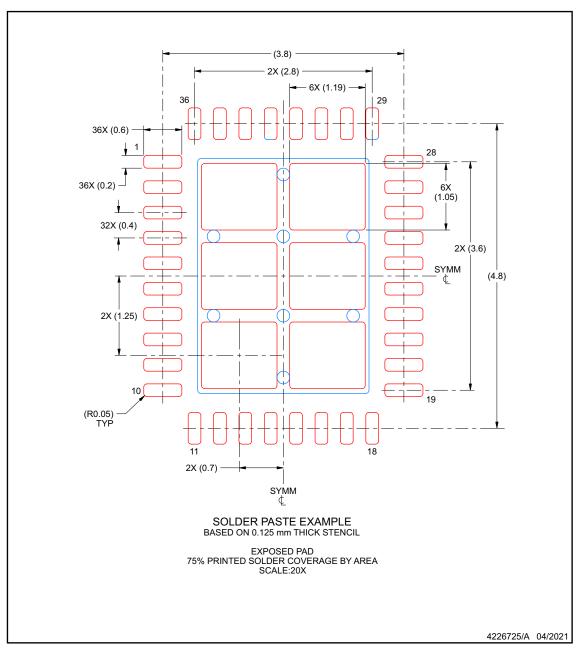

Figure 6-1. DRV8329 REE Package 36-pin VQFN With Exposed Thermal Pad Top View

Table 6-1. Pin Functions—36-Pin DRV8329 Devices

| NAME    | PIN NO. | TVDE  | DECORIDATION                                                                                                                                                                                                                                                   |

|---------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | DRV8329 | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                    |

| AGND    | 25      | PWR   | Device analog ground. Refer Layout Guidelines for the recommendation on connection.                                                                                                                                                                            |

| AVDD    | 26      | PWR-O | 3.3-V regulator output. Connect a X5R or X7R, 1-µF, >6.3-V ceramic capacitor between the AVDD and GND pins. This regulator can source up to 80 mA externally. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin. |

| BSTA    | 9       | 0     | Bootstrap output pin. Connect a X5R or X7R, 1-µF, 25-V ceramic capacitor between BSTA and SHA                                                                                                                                                                  |

| BSTB    | 13      | 0     | Bootstrap output pin. Connect a X5R or X7R, 1-µF, 25-V ceramic capacitor between BSTB and SHB                                                                                                                                                                  |

| BSTC    | 17      | 0     | Bootstrap output pin. Connect a X5R or X7R, 1-µF, 25-V ceramic capacitor between BSTC and SHC                                                                                                                                                                  |

| CSAGAIN | 33      | I     | Gain settings for Current sense amplifier. The pin is a 4 level input pin set by an external resistor. See Low-Side Current Sense Amplifiers for more information.                                                                                             |

| CSAREF  | 1       | 1     | Current sense amplifier reference. Connect a X5R or X7R, 0.1-µF, 6.3-V ceramic capacitor between the CSAREF and AGND pins.                                                                                                                                     |

| СРН     | 7       | PWR   | Charge pump switching node. Connect a X5R or X7R, PVDD-rated ceramic capacitor between the                                                                                                                                                                     |

| CPL     | 6       | PWR   | CPH and CPL pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin.                                                                                                                                             |

| DRVOFF  | 24      | I     | Independent driver shutdown path. Pulling DRVOFF high turns off all external MOSFETs by putting the gate drivers into the pull-down state. This signal bypasses and overrides the digital core of DRV8329.                                                     |

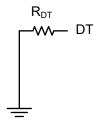

| DT      | 3       | I     | Gate drive deadtime setting. Connect a resistor of value between 10 k $\Omega$ to 390 k $\Omega$ between DT and GND to adjust deadtime between 100 ns to 2000 ns. If pin is left floating or connected to GND fixed value of 55 ns deadtime is inserted.       |

| GHA     | 11      | 0     | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                               |

| GHB     | 15      | 0     | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                               |

| GHC     | 19      | 0     | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                               |

| GLA     | 12      | 0     | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                 |

| GLB     | 16      | 0     | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                 |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# Table 6-1. Pin Functions—36-Pin DRV8329 Devices (continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIN NO. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DRV8329 | TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DESCRIPTION                                                                                                                                                                                                                                                             |

| GLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                          |

| GVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8       | PWR-O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Gate driver power supply output. Connect a X5R or X7R, 30-V rated ceramic ≥ 10-uF local capacitance between the GVDD and GND pins. TI recommends a capacitor value of >10x C <sub>BSTx</sub> and voltage rating at least twice the normal operating voltage of the pin. |

| GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4       | PWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Device ground. Refer Layout Guidelines for the recommendation on connection.                                                                                                                                                                                            |

| INHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | High-side gate driver control input for Phase A. This pin controls the output of the high-side FET.                                                                                                                                                                     |

| INHB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | High-side gate driver control input for Phase B. This pin controls the output of the high-side FET.                                                                                                                                                                     |

| INHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | High-side gate driver control input for Phase C. This pin controls the output of the high-side FET.                                                                                                                                                                     |

| INLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Low-side gate driver control input for Phase A. This pin controls the output of the low-side FET.                                                                                                                                                                       |

| and voltage rating at least twice the normal operating voltage of the pin.  GND 4 PWR Device ground. Refer Layout Guidelines for the recommendation on connection.  INHA 29 I High-side gate driver control input for Phase A. This pin controls the output of the high-side FET.  INHB 28 I High-side gate driver control input for Phase B. This pin controls the output of the high-side FET.  INHC 27 I High-side gate driver control input for Phase C. This pin controls the output of the high-side FET.  INLA 32 I Low-side gate driver control input for Phase A. This pin controls the output of the low-side FET.  INLB 31 I Low-side gate driver control input for Phase B. This pin controls the output of the low-side FET.  INLC 30 I Low-side gate driver control input for Phase C. This pin controls the output of the low-side FET.  Low side source pin, connect all sources of the external low-side MOSFETs here. This pin is the s path for the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS vo and VSEN_OCP voltage.  INFAULT 35 OD Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to 3.3V to 5.0V.  INSLEEP 34 I Sleep mode entry pin. When this pin is pulled logic low the device goes to a low-power sleep mode.  Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1-  µF, >2x PVDD-rated ceramic and >10-uF local capacitance between the PVDD and GND pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin.  SHA 10 I/O High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side power MOSFET source. This pin is an input for the                                                                                                                                                                                                                                                                  |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                         |

| INLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30      | I Low-side gate driver control input for Phase A. This pin controls the output of the low-side FET.  I Low-side gate driver control input for Phase B. This pin controls the output of the low-side FET.  I Low-side gate driver control input for Phase C. This pin controls the output of the low-side FET.  Low-side gate driver control input for Phase C. This pin controls the output of the low-side FET.  Low-side gate driver control input for Phase C. This pin controls the output of the low-side FET.  Low side source pin, connect all sources of the external low-side MOSFETs here. This pin is the sir path for the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS volts and VSEN_OCP voltage.  Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to 3.3V to 5.0V.  Sleep mode entry pin. When this pin is pulled logic low the device goes to a low-power sleep mode 1 to 1.2-μs low pulse can be used to reset fault conditions without entering sleep mode. |                                                                                                                                                                                                                                                                         |

| INLC 30 I Low-side gate driver control input for Phase C. This pin controls the output of the low-side FET.  Low side source pin, connect all sources of the external low-side MOSFETs here. This pin is the path for the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS viand VSEN_OCP voltage.  nFAULT 35 OD Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to 3.3V to 5.0V.  Sleep mode entry pin. When this pin is pulled logic low the device goes to a low-power sleep mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                         |

| Fault indicator output. This pin is pulled logic low during a fault condition and requires an extension of the second sec |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                         |

| nSLEEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sleep mode entry pin. When this pin is pulled logic low the device goes to a low-power sleep mode. An 1 to 1.2-µs low pulse can be used to reset fault conditions without entering sleep mode.                                                                          |

| Description of the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS votand VSEN_OCP voltage.  Description of the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS votand VSEN_OCP voltage.  Description of the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS votand VSEN_OCP voltage.  Description of the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS votand VSEN_VDS voltage.  Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to 3.3V to 5.0V.  Sleep mode entry pin. When this pin is pulled logic low the device goes to a low-power sleep mode of the pin to 1.2-μs low pulse can be used to reset fault conditions without entering sleep mode.  Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1-μF, >2x PVDD-rated ceramic and >10-μF local capacitance between the PVDD and GND pins. The recommends a capacitor voltage rating at least twice the normal operating voltage of the pin.  SHA  10  High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the high-side gate driver sink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                         |

| SHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                         |

| SHB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                         |

| SHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                         |

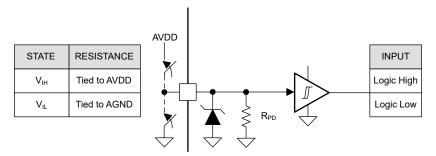

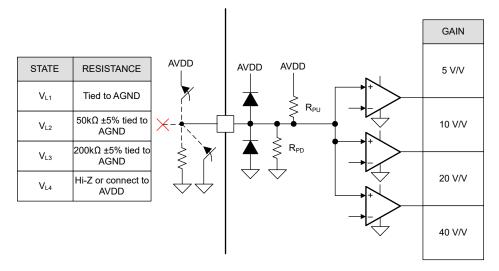

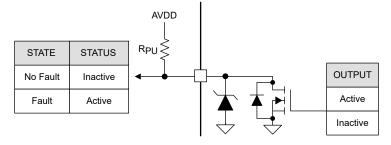

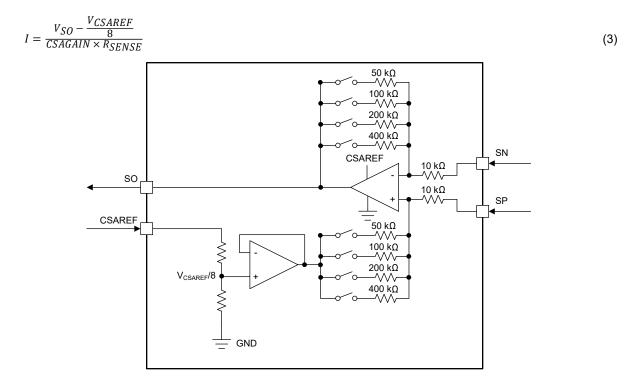

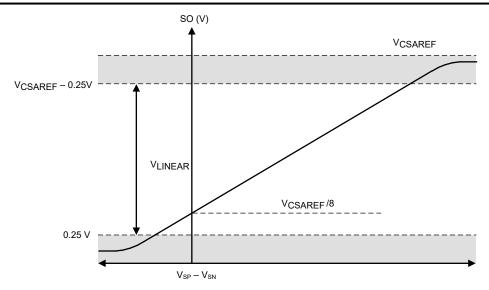

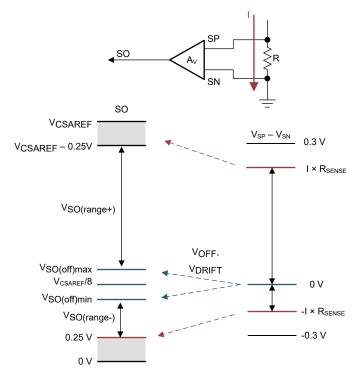

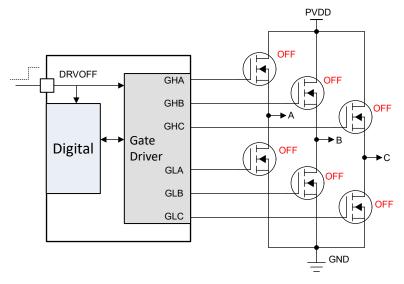

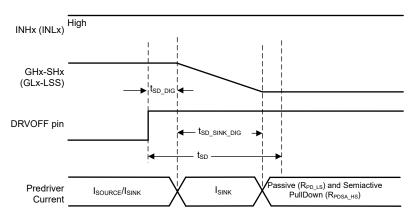

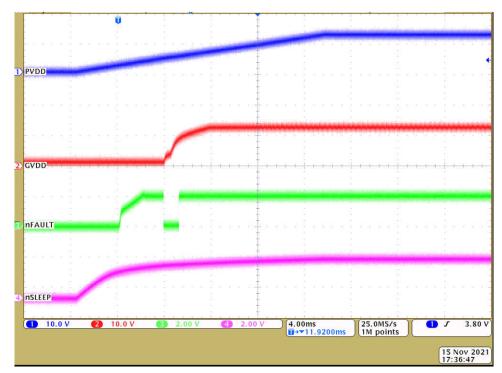

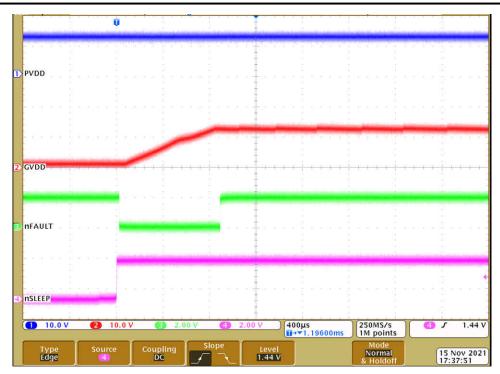

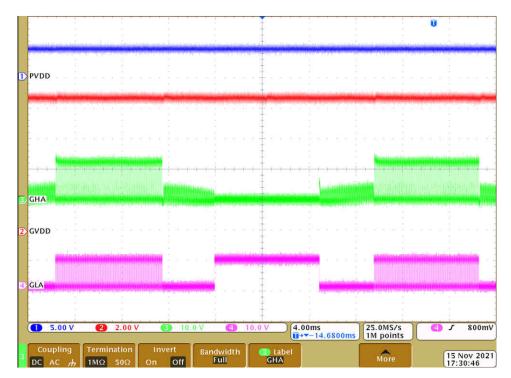

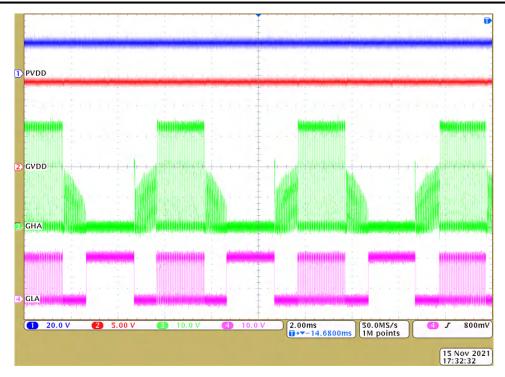

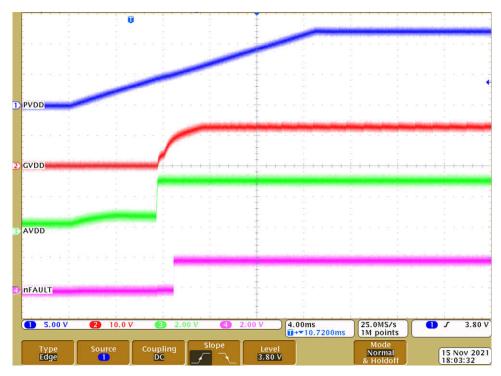

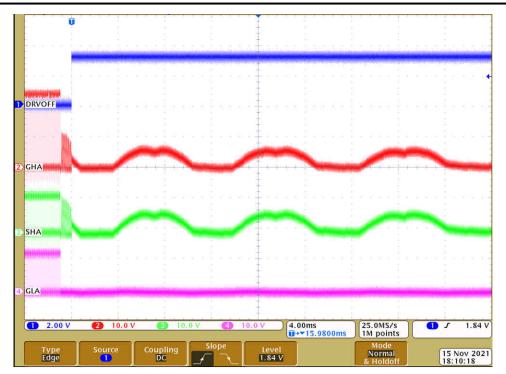

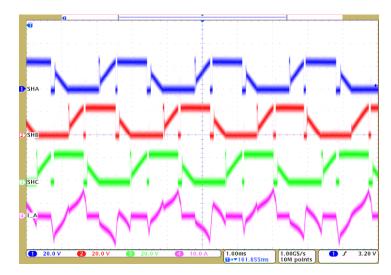

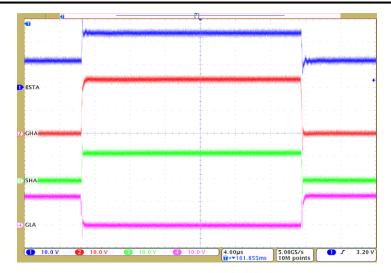

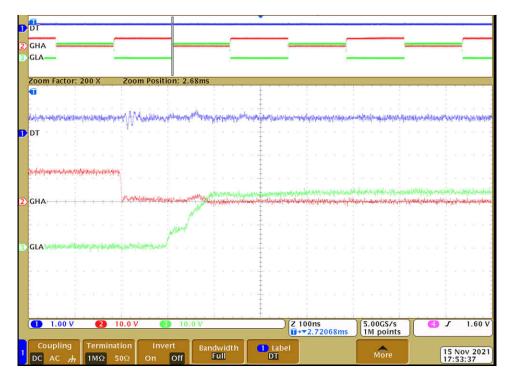

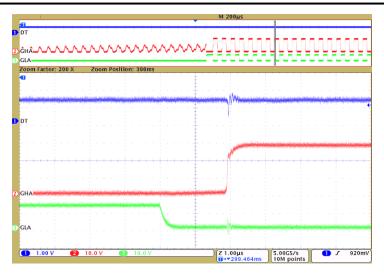

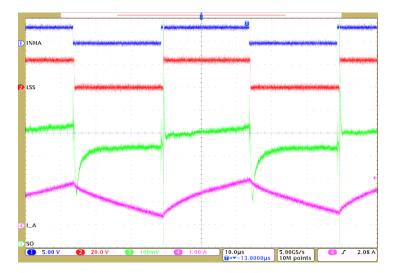

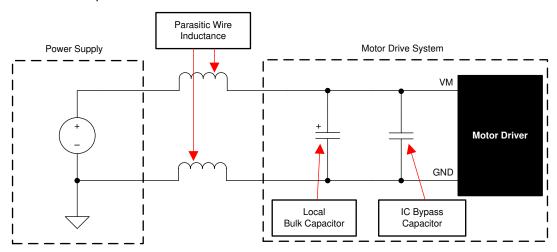

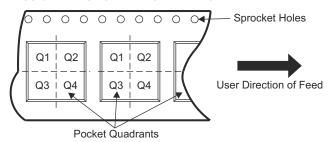

| so                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Current sense amplifier output. Supports capacitive load or low pass filter (resistor in series and capacitor to GND)                                                                                                                                                   |