# Chapter Excerpt from SLAU208

# Chapter 1 SLAU391F-August 2012-Revised March 2018

# **CPUX**

NOTE: This chapter is an excerpt from the MSP430x5xx and MSP430x6xx Family User's Guide.

The most recent version of the full user's guide is available at

http://www.ti.com/lit/pdf/slau208.

This chapter describes the extended MSP430X 16-bit RISC CPU (CPUX) with 1MB memory access, its addressing modes, and instruction set.

NOTE: The MSP430X CPUX implemented on this device family, formally called CPUXV2, has in some cases, slightly different cycle counts from the MSP430X CPUX implemented on the 2xx and 4xx families.

**Topic Page**

| 1.1 | MSP430X CPU (CPUX) Introduction2 |

|-----|----------------------------------|

| 1.2 | Interrupts 4                     |

| 1.3 | CPU Registers 5                  |

| 1.4 | Addressing Modes 11              |

| 1.5 | MSP430 and MSP430X Instructions  |

| 1.6 | Instruction Set Description 44   |

# 1.1 MSP430X CPU (CPUX) Introduction

The MSP430X CPU incorporates features specifically designed for modern programming techniques, such as calculated branching, table processing, and the use of high-level languages such as C. The MSP430X CPU can address a 1MB address range without paging. The MSP430X CPU is completely backward compatible with the MSP430 CPU.

The MSP430X CPU features include:

- RISC architecture

- Orthogonal architecture

- Full register access including program counter (PC), status register (SR), and stack pointer (SP)

- Single-cycle register operations

- Large register file reduces fetches to memory.

- 20-bit address bus allows direct access and branching throughout the entire memory range without paging.

- 16-bit data bus allows direct manipulation of word-wide arguments.

- Constant generator provides the six most often used immediate values and reduces code size.

- · Direct memory-to-memory transfers without intermediate register holding

- Byte, word, and 20-bit address-word addressing

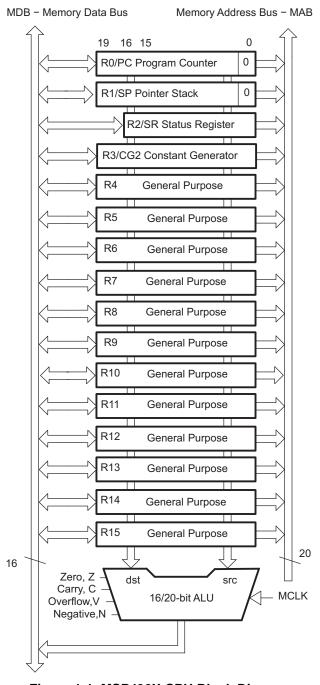

The block diagram of the MSP430X CPU is shown in Figure 1-1.

Figure 1-1. MSP430X CPU Block Diagram

CPUX

Interrupts www.ti.com

# 1.2 Interrupts

The MSP430X has the following interrupt structure:

- Vectored interrupts with no polling necessary

- Interrupt vectors are located downward from address 0FFFEh.

The interrupt vectors contain 16-bit addresses that point into the lower 64KB memory. This means all interrupt handlers must start in the lower 64KB memory.

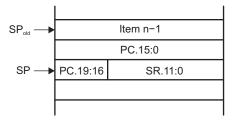

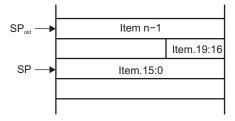

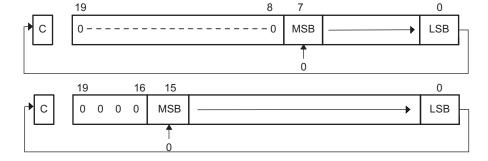

During an interrupt, the program counter (PC) and the status register (SR) are pushed onto the stack as shown in Figure 1-2. The MSP430X architecture stores the complete 20-bit PC value efficiently by appending the PC bits 19:16 to the stored SR value automatically on the stack. When the RETI instruction is executed, the full 20-bit PC is restored making return from interrupt to any address in the memory range possible.

Figure 1-2. PC Storage on the Stack for Interrupts

**CPU Registers** www.ti.com

### 1.3 **CPU Registers**

The CPU incorporates 16 registers (R0 through R15). Registers R0, R1, R2, and R3 have dedicated functions. Registers R4 through R15 are working registers for general use.

# 1.3.1 Program Counter (PC)

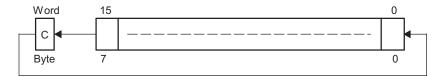

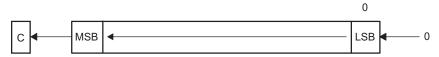

The 20-bit Program Counter (PC, also called R0) points to the next instruction to be executed. Each instruction uses an even number of bytes (2, 4, 6, or 8 bytes), and the PC is incremented accordingly. Instruction accesses are performed on word boundaries, and the PC is aligned to even addresses. Figure 1-3 shows the PC.

Figure 1-3. Program Counter

The PC can be addressed with all instructions and addressing modes. A few examples:

```

#LABEL, PC ; Branch to address LABEL (lower 64KB)

MOV.W

MOVA

#LABEL, PC ; Branch to address LABEL (1MB memory)

MOV.W

LABEL, PC

; Branch to address in word LABEL

; (lower 64KB)

MOV.W

@R14,PC

; Branch indirect to address in

; R14 (lower 64KB)

; Skip two words (1MB memory)

ADDA

#4,PC

```

The BR and CALL instructions reset the upper four PC bits to 0. Only addresses in the lower 64KB address range can be reached with the BR or CALL instruction. When branching or calling, addresses beyond the lower 64KB range can only be reached using the BRA or CALLA instructions. Also, any instruction to directly modify the PC does so according to the used addressing mode. For example, MOV.W #value, PC clears the upper four bits of the PC, because it is a .W instruction.

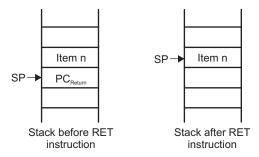

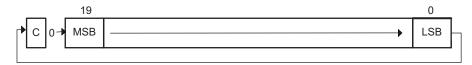

The PC is automatically stored on the stack with CALL (or CALLA) instructions and during an interrupt service routine. Figure 1-4 shows the storage of the PC with the return address after a CALLA instruction. A CALL instruction stores only bits 15:0 of the PC.

Figure 1-4. PC Storage on the Stack for CALLA

The RETA instruction restores bits 19:0 of the PC and adds 4 to the stack pointer (SP). The RET instruction restores bits 15:0 to the PC and adds 2 to the SP.

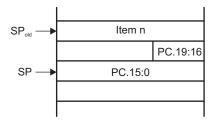

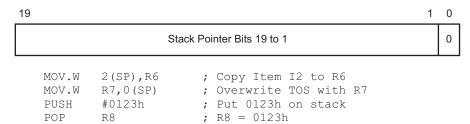

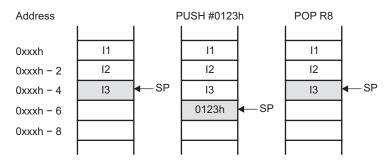

# 1.3.2 Stack Pointer (SP)

The 20-bit Stack Pointer (SP, also called R1) is used by the CPU to store the return addresses of subroutine calls and interrupts. It uses a predecrement, postincrement scheme. In addition, the SP can be used by software with all instructions and addressing modes. Figure 1-5 shows the SP. The SP is initialized into RAM by the user, and is always aligned to even addresses.

CPU Registers www.ti.com

Figure 1-6 shows the stack usage. Figure 1-7 shows the stack usage when 20-bit address words are pushed.

Figure 1-5. Stack Pointer

Figure 1-6. Stack Usage

Figure 1-7. PUSHX.A Format on the Stack

The special cases of using the SP as an argument to the PUSH and POP instructions are described and shown in Figure 1-8.

The stack pointer is changed after a PUSH SP instruction.

The stack pointer is not changed after a POP SP instruction. The POP SP instruction places SP1 into the stack pointer SP (SP2 = SP1)

Figure 1-8. PUSH SP, POP SP Sequence

CPU Registers www.ti.com

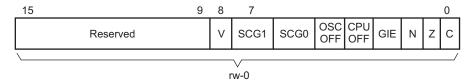

# 1.3.3 Status Register (SR)

The 16-bit Status Register (SR, also called R2), used as a source or destination register, can only be used in register mode addressed with word instructions. The remaining combinations of addressing modes are used to support the constant generator. Figure 1-9 shows the SR bits. Do not write 20-bit values to the SR. Unpredictable operation can result.

Figure 1-9. SR Bits

Table 1-1 describes the SR bits.

Table 1-1. SR Bit Description

| Bit      | Description                                                                                                                                                                |                                                                                         |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Reserved | Reserved                                                                                                                                                                   |                                                                                         |  |  |  |

| V        | Overflow. This bit is set when the result of an arithmetic operation                                                                                                       | on overflows the signed-variable range.                                                 |  |  |  |

|          | ADD(.B), ADDX(.B,.A),<br>ADDC(.B), ADDCX(.B.A),<br>ADDA                                                                                                                    | Set when: positive + positive = negative negative + negative = positive otherwise reset |  |  |  |

|          | SUB(.B), SUBX(.B,.A),<br>SUBC(.B), SUBCX(.B,.A),<br>SUBA, CMP(.B),<br>CMPX(.B,.A), CMPA                                                                                    | Set when: positive – negative = negative negative – positive = positive otherwise reset |  |  |  |

| SCG1     | System clock generator 1. This bit may be used to enable or disable functions in the clock system depending on the device family; for example, DCO bias enable or disable. |                                                                                         |  |  |  |

| SCG0     | System clock generator 0. This bit may be used to enable or disdevice family; for example, FLL enable or disable.                                                          | sable functions in the clock system depending on the                                    |  |  |  |

| OSCOFF   | Oscillator off. When this bit is set, it turns off the LFXT1 crystal SMCLK.                                                                                                | oscillator when LFXT1CLK is not used for MCLK or                                        |  |  |  |

| CPUOFF   | CPU off. When this bit is set, it turns off the CPU.                                                                                                                       |                                                                                         |  |  |  |

| GIE      | General interrupt enable. When this bit is set, it enables maskable interrupts. When it is reset, all maskable interrupts are disabled.                                    |                                                                                         |  |  |  |

| N        | Negative. This bit is set when the result of an operation is negative.                                                                                                     | tive and cleared when the result is positive.                                           |  |  |  |

| Z        | Zero. This bit is set when the result of an operation is 0 and cleared when the result is not 0.                                                                           |                                                                                         |  |  |  |

| С        | Carry. This bit is set when the result of an operation produced a                                                                                                          | a carry and cleared when no carry occurred.                                             |  |  |  |

NOTE: Bit manipulations of the SR should be done by the following instructions: MOV, BIS, and BIC.

**CPU Registers** www.ti.com

# 1.3.4 Constant Generator Registers (CG1 and CG2)

Six commonly-used constants are generated with the constant generator registers R2 (CG1) and R3 (CG2), without requiring an additional 16-bit word of program code. The constants are selected with the source register addressing modes (As), as described in Table 1-2.

Table 1-2. Values of Constant Generators CG1, CG2

| Register | As | Constant Remarks   |                       |

|----------|----|--------------------|-----------------------|

| R2       | 00 | _                  | Register mode         |

| R2       | 01 | (0)                | Absolute address mode |

| R2       | 10 | 00004h             | +4, bit processing    |

| R2       | 11 | 00008h             | +8, bit processing    |

| R3       | 00 | 00000h             | 0, word processing    |

| R3       | 01 | 00001h             | +1                    |

| R3       | 10 | 00002h             | +2, bit processing    |

| R3       | 11 | FFh, FFFFh, FFFFFh | -1, word processing   |

The constant generator advantages are:

- No special instructions required

- No additional code word for the six constants

- No code memory access required to retrieve the constant

The assembler uses the constant generator automatically if one of the six constants is used as an immediate source operand. Registers R2 and R3, used in the constant mode, cannot be addressed explicitly; they act as source-only registers.

# 1.3.4.1 Constant Generator – Expanded Instruction Set

The RISC instruction set of the MSP430 has only 27 instructions. However, the constant generator allows the MSP430 assembler to support 24 additional emulated instructions. For example, the single-operand instruction:

CLR dst

is emulated by the double-operand instruction with the same length:

where the #0 is replaced by the assembler, and R3 is used with As = 00.

INC dst

is replaced by:

ADD #1,dst

R

www.ti.com CPU Registers

# 1.3.5 General-Purpose Registers (R4 to R15)

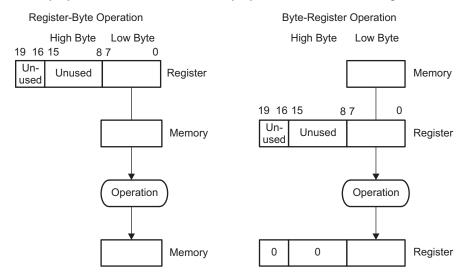

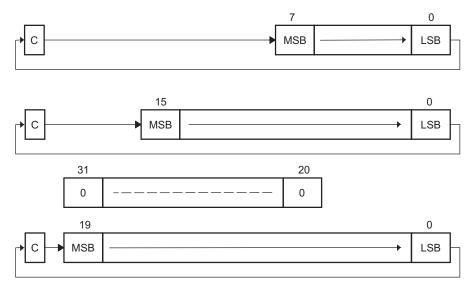

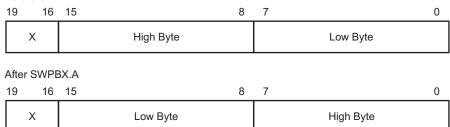

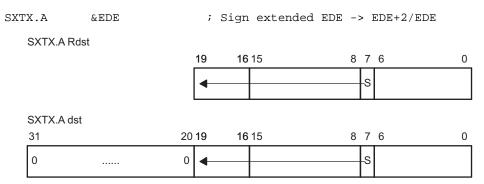

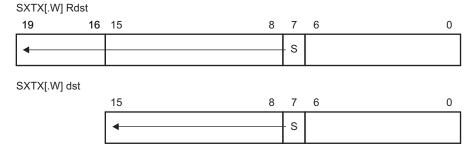

The 12 CPU registers (R4 to R15) contain 8-bit, 16-bit, or 20-bit values. Any byte-write to a CPU register clears bits 19:8. Any word-write to a register clears bits 19:16. The only exception is the SXT instruction. The SXT instruction extends the sign through the complete 20-bit register.

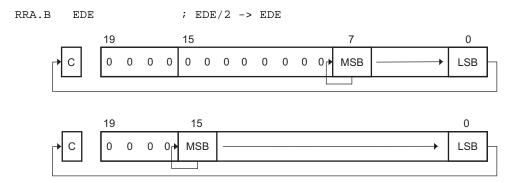

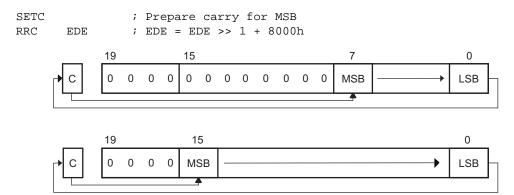

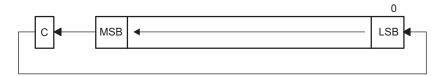

Figure 1-10 through Figure 1-14 show the handling of byte, word, and address-word data. Note the reset of the leading most significant bits (MSBs) if a register is the destination of a byte or word instruction.

Figure 1-10 shows byte handling (8-bit data, .B suffix). The handling is shown for a source register and a destination memory byte and for a source memory byte and a destination register.

Figure 1-10. Register-Byte and Byte-Register Operation

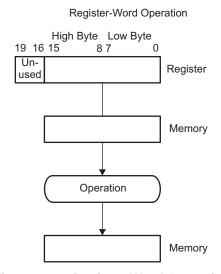

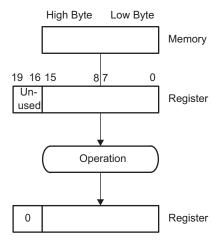

Figure 1-11 and Figure 1-12 show 16-bit word handling (.W suffix). The handling is shown for a source register and a destination memory word and for a source memory word and a destination register.

Figure 1-11. Register-Word Operation

TEXAS INSTRUMENTS

CPU Registers www.ti.com

Word Register Operation

Figure 1-12. Word-Register Operation

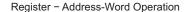

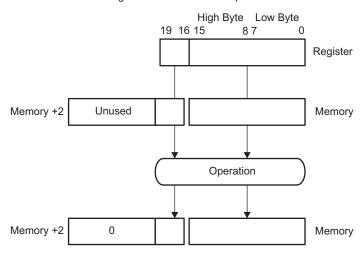

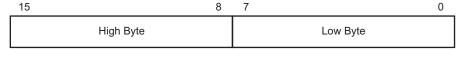

Figure 1-13 and Figure 1-14 show 20-bit address-word handling (.A suffix). The handling is shown for a source register and a destination memory address-word and for a source memory address-word and a destination register.

Figure 1-13. Register - Address-Word Operation

# Address-Word – Register Operation High Byte Low Byte 19 16 15 8 7 0 Memory +2 Unused Memory Register Operation Register

Figure 1-14. Address-Word – Register Operation

# 1.4 Addressing Modes

Seven addressing modes for the source operand and four addressing modes for the destination operand use 16-bit or 20-bit addresses (see Table 1-3). The MSP430 and MSP430X instructions are usable throughout the entire 1MB memory range.

Table 1-3. Source and Destination Addressing

| As, Ad | Addressing Mode           | Syntax | Description                                                                                                                                                                                             |

|--------|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00, 0  | Register                  | Rn     | Register contents are operand.                                                                                                                                                                          |

| 01, 1  | Indexed                   | X(Rn)  | (Rn + X) points to the operand. X is stored in the next word, or stored in combination of the preceding extension word and the next word.                                                               |

| 01, 1  | Symbolic                  | ADDR   | (PC + X) points to the operand. X is stored in the next word, or stored in combination of the preceding extension word and the next word. Indexed mode $X(PC)$ is used.                                 |

| 01, 1  | Absolute                  | &ADDR  | The word following the instruction contains the absolute address. X is stored in the next word, or stored in combination of the preceding extension word and the next word. Indexed mode X(SR) is used. |

| 10, –  | Indirect Register         | @Rn    | Rn is used as a pointer to the operand.                                                                                                                                                                 |

| 11, –  | Indirect<br>Autoincrement | @Rn+   | Rn is used as a pointer to the operand. Rn is incremented afterwards by 1 for .B instructions, by 2 for .W instructions, and by 4 for .A instructions.                                                  |

| 11, –  | Immediate                 | #N     | N is stored in the next word, or stored in combination of the preceding extension word and the next word. Indirect autoincrement mode @PC+ is used.                                                     |

The seven addressing modes are explained in detail in the following sections. Most of the examples show the same addressing mode for the source and destination, but any valid combination of source and destination addressing modes is possible in an instruction.

### NOTE: Use of Labels EDE, TONI, TOM, and LEO

Throughout MSP430 documentation, EDE, TONI, TOM, and LEO are used as generic labels. They are only labels and have no special meaning.

Addressing Modes www.ti.com

### 1.4.1 Register Mode

Operation: The operand is the 8-, 16-, or 20-bit content of the used CPU register.

Length: One, two, or three words

Comment: Valid for source and destination

Byte operation reads only the eight least significant bits (LSBs) of the source Byte operation:

register Rsrc and writes the result to the eight LSBs of the destination register Rdst.

The bits Rdst.19:8 are cleared. The register Rsrc is not modified.

Word operation: Word operation reads the 16 LSBs of the source register Rsrc and writes the result

to the 16 LSBs of the destination register Rdst. The bits Rdst.19:16 are cleared.

The register Rsrc is not modified.

Address-word operation:

Address-word operation reads the 20 bits of the source register Rsrc and writes the

result to the 20 bits of the destination register Rdst. The register Rsrc is not

modified

The SXT instruction is the only exception for register operation. The sign of the low SXT exception:

byte in bit 7 is extended to the bits Rdst.19:8.

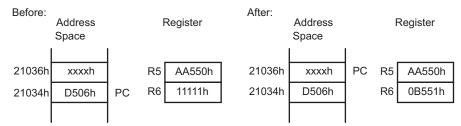

BIS.W R5,R6 ; Example:

This instruction logically ORs the 16-bit data contained in R5 with the 16-bit

contents of R6. R6.19:16 is cleared.

A550h.or.1111h = B551h

Example: BISX.A R5,R6 ;

> This instruction logically ORs the 20-bit data contained in R5 with the 20-bit contents of R6.

The extension word contains the A/L bit for 20-bit data. The instruction word uses byte mode with bits A/L:B/W = 01. The result of the instruction is:

AA550h.or.11111h = BB551h

### 1.4.2 Indexed Mode

The Indexed mode calculates the address of the operand by adding the signed index to a CPU register. The Indexed mode has four addressing possibilities:

- MSP430 instruction with Indexed mode in lower 64KB memory (see Section 1.4.2.1)

- MSP430 instruction with Indexed mode addressing memory above the lower 64KB memory (see Section 1.4.2.2)

- MSP430X instruction with Indexed mode (see Section 1.4.2.3)

- MSP430X address instructions with Indexed mode (see Section 1.4.2.4)

# 1.4.2.1 MSP430 Instruction With Indexed Mode in Lower 64KB Memory

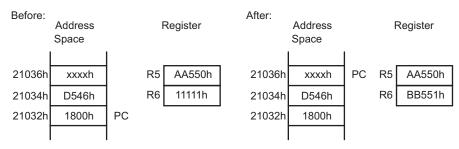

If the CPU register Rn points to an address in the lower 64KB of the memory range, the calculated memory address bits 19:16 are cleared after the addition of the CPU register Rn and the signed 16-bit index. This means the calculated memory address is always located in the lower 64KB and does not overflow or underflow out of the lower 64KB memory space. The RAM and the peripheral registers can be accessed this way and existing MSP430 software is usable without modifications as shown in Figure 1-15.

Figure 1-15. Indexed Mode in Lower 64KB

Length: Two or three words

Operation: The signed 16-bit index is located in the next word after the instruction and is added to

the CPU register Rn. The resulting bits 19:16 are cleared giving a truncated 16-bit memory address, which points to an operand address in the range 00000h to 0FFFFh.

The operand is the content of the addressed memory location.

Comment: Valid for source and destination. The assembler calculates the register index and inserts

it.

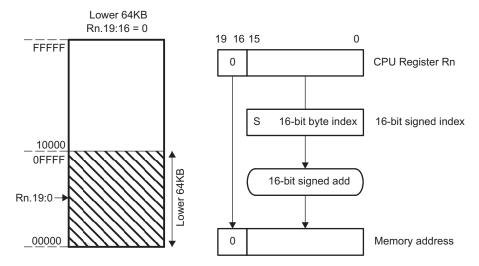

Example: ADD.B 1000h(R5),0F000h(R6);

This instruction adds the 8-bit data contained in source byte 1000h(R5) and the destination byte 0F000h(R6) and places the result into the destination byte. Source and destination bytes are both located in the lower 64KB due to the cleared bits 19:16 of

registers R5 and R6.

Source: The byte pointed to by R5 + 1000h results in address 0479Ch + 1000h = 0579Ch after

truncation to a 16-bit address.

Destination: The byte pointed to by R6 + F000h results in address 01778h + F000h = 00778h after

truncation to a 16-bit address.

**STRUMENTS**

Addressing Modes www.ti.com

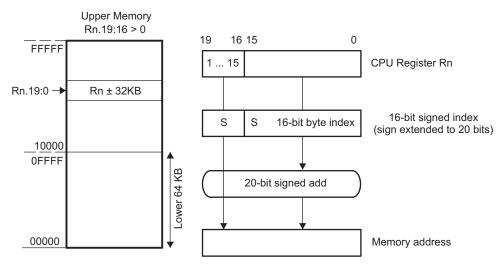

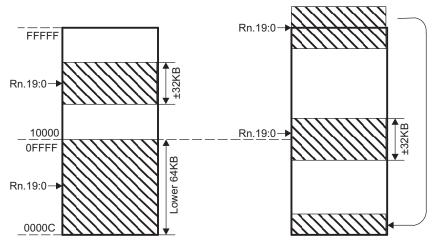

# 1.4.2.2 MSP430 Instruction With Indexed Mode in Upper Memory

If the CPU register Rn points to an address above the lower 64KB memory, the Rn bits 19:16 are used for the address calculation of the operand. The operand may be located in memory in the range Rn ±32KB, because the index, X, is a signed 16-bit value. In this case, the address of the operand can overflow or underflow into the lower 64KB memory space (see Figure 1-16 and Figure 1-17).

Figure 1-16. Indexed Mode in Upper Memory

Figure 1-17. Overflow and Underflow for Indexed Mode

Length: Two or three words

Operation: The sign-extended 16-bit index in the next word after the instruction is added to the

20 bits of the CPU register Rn. This delivers a 20-bit address, which points to an address in the range 0 to FFFFFh. The operand is the content of the addressed

memory location.

Comment: Valid for source and destination. The assembler calculates the register index and

inserts it.

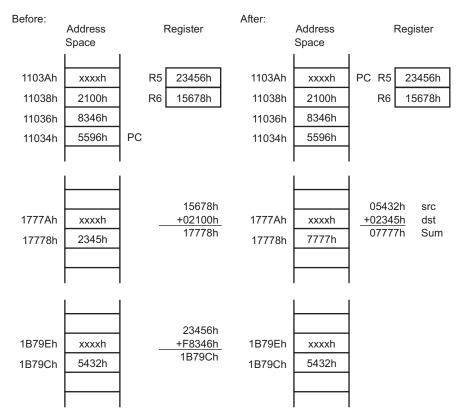

Example: ADD.W 8346h(R5),2100h(R6);

This instruction adds the 16-bit data contained in the source and the destination addresses and places the 16-bit result into the destination. Source and destination

operand can be located in the entire address range.

Source: The word pointed to by R5 + 8346h. The negative index 8346h is sign extended,

which results in address 23456h + F8346h = 1B79Ch.

Destination: The word pointed to by R6 + 2100h results in address 15678h + 2100h = 17778h.

TEXAS INSTRUMENTS

Addressing Modes www.ti.com

Figure 1-18. Example for Indexed Mode

### 1.4.2.3 MSP430X Instruction With Indexed Mode

When using an MSP430X instruction with Indexed mode, the operand can be located anywhere in the range of Rn + 19 bits.

Length: Three or four words

Operation: The operand address is the sum of the 20-bit CPU register content and the 20-bit

index. The 4 MSBs of the index are contained in the extension word; the 16 LSBs are contained in the word following the instruction. The CPU register is not modified

Comment: Valid for source and destination. The assembler calculates the register index and

inserts it.

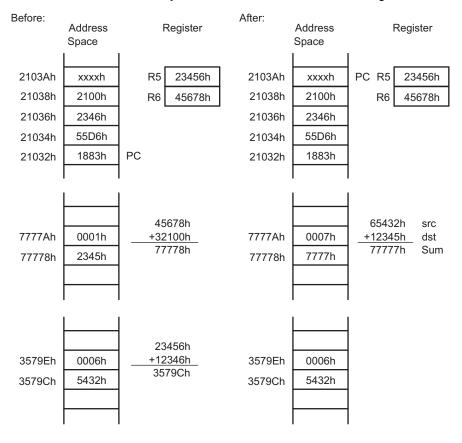

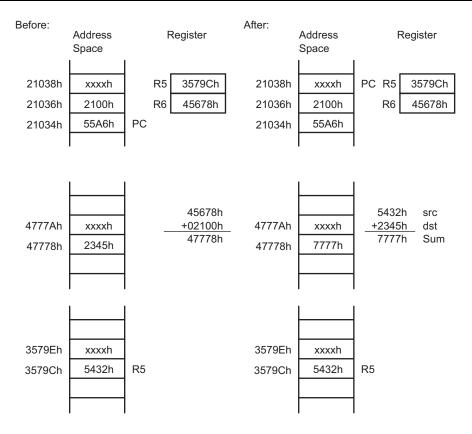

Example: ADDX.A 12346h(R5),32100h(R6);

This instruction adds the 20-bit data contained in the source and the destination

addresses and places the result into the destination.

Source: Two words pointed to by R5 + 12346h which results in address 23456h + 12346h =

3579Ch.

Destination: Two words pointed to by R6 + 32100h which results in address 45678h + 32100h =

77778h.

The extension word contains the MSBs of the source index and of the destination index and the A/L bit for 20-bit data. The instruction word uses byte mode due to the 20-bit data length with bits A/L:B/W = 01.

# 1.4.2.4 MSP430X Address Instructions With Indexed Mode

When using an MSP430X Address Instruction with Indexed mode, the operand is located in memory in the range Rn ±32KB, because the index, X, is a signed 16-bit value.

Length: Two words

Operation: The sign-extended 16-bit index in the next word after the instruction is added to the 20

bits of the CPU register Rn. This delivers a 20-bit address, which points to an address in the range 0 to FFFFh. The operand is the content of the addressed memory location.

Comment: Valid for source and destination. The assembler calculates the register index and inserts

it.

Example: MOVA 8002h(R5),R6 ; // R5 = 0x100

This instruction loads the 20-bit data contained in the source address into destination

register.

Source: Two words pointed to by R5 + 8002h and R5 + 8002h + 2h which results in address

00100h + F8002h (+2h) = F8102h and F8104h.

Destination: Register R6

Addressing Modes www.ti.com

# 1.4.3 Symbolic Mode

The Symbolic mode calculates the address of the operand by adding the signed index to the PC. The Symbolic mode has three addressing possibilities:

- Symbolic mode in lower 64KB of memory

- MSP430 instruction with Symbolic mode addressing memory above the lower 64KB of memory.

- MSP430X instruction with Symbolic mode

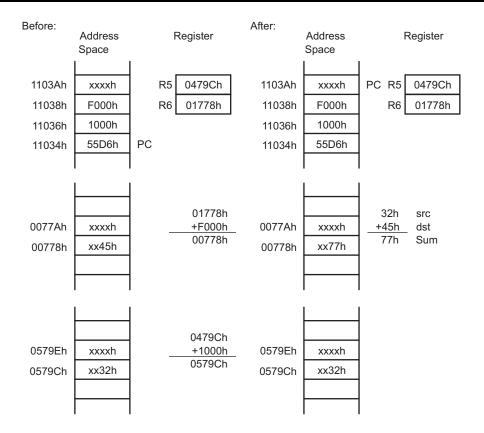

### 1.4.3.1 Symbolic Mode in Lower 64KB

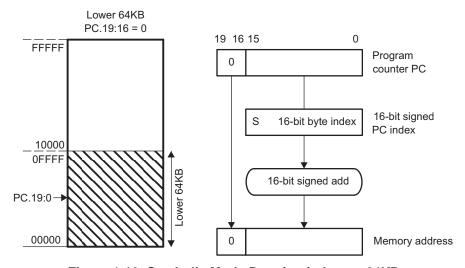

If the PC points to an address in the lower 64KB of the memory range, the calculated memory address bits 19:16 are cleared after the addition of the PC and the signed 16-bit index. This means the calculated memory address is always located in the lower 64KB and does not overflow or underflow out of the lower 64KB memory space. The RAM and the peripheral registers can be accessed this way and existing MSP430 software is usable without modifications as shown in Figure 1-19.

Figure 1-19. Symbolic Mode Running in Lower 64KB

Operation: The signed 16-bit index in the next word after the instruction is added temporarily to

> the PC. The resulting bits 19:16 are cleared giving a truncated 16-bit memory address, which points to an operand address in the range 00000h to 0FFFFh. The

operand is the content of the addressed memory location.

Length: Two or three words

Comment: Valid for source and destination. The assembler calculates the PC index and

inserts it.

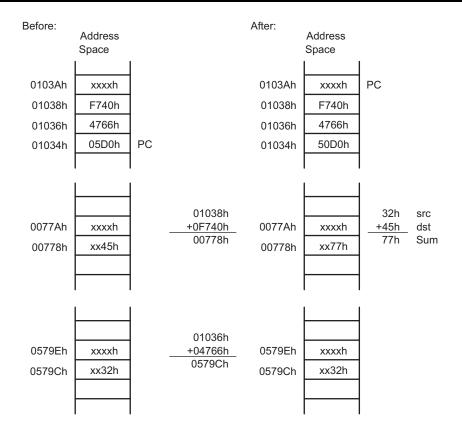

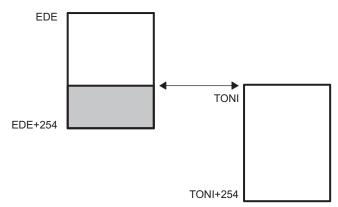

ADD.B EDE, TONI ; Example:

> This instruction adds the 8-bit data contained in source byte EDE and destination byte TONI and places the result into the destination byte TONI. Bytes EDE and

TONI and the program are located in the lower 64KB.

Source: Byte EDE located at address 0579Ch, pointed to by PC + 4766h, where the PC

index 4766h is the result of 0579Ch - 01036h = 04766h. Address 01036h is the

location of the index for this example.

Byte TONI located at address 00778h, pointed to by PC + F740h, is the truncated Destination:

16-bit result of 00778h - 1038h = FF740h. Address 01038h is the location of the

index for this example.

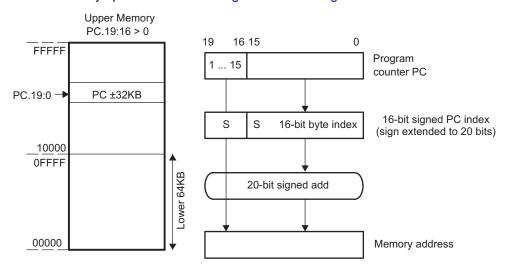

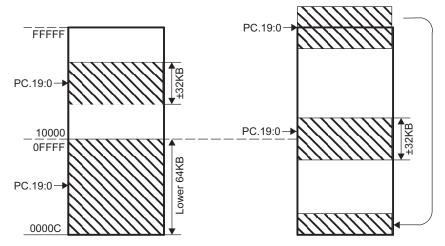

# 1.4.3.2 MSP430 Instruction With Symbolic Mode in Upper Memory

If the PC points to an address above the lower 64KB memory, the PC bits 19:16 are used for the address calculation of the operand. The operand may be located in memory in the range PC  $\pm$  32KB, because the index, X, is a signed 16-bit value. In this case, the address of the operand can overflow or underflow into the lower 64KB memory space as shown in Figure 1-20 and Figure 1-21.

Figure 1-20. Symbolic Mode Running in Upper Memory

TEXAS INSTRUMENTS

Addressing Modes www.ti.com

Figure 1-21. Overflow and Underflow for Symbolic Mode

Length: Two or three words

Operation: The sign-extended 16-bit index in the next word after the instruction is added to the

20 bits of the PC. This delivers a 20-bit address, which points to an address in the range 0 to FFFFFh. The operand is the content of the addressed memory location.

Comment: Valid for source and destination. The assembler calculates the PC index and

inserts it

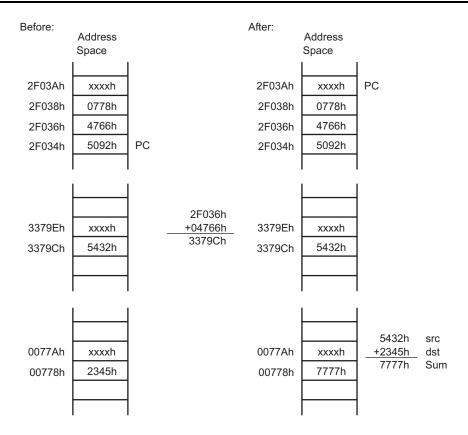

Example: ADD.W EDE,&TONI ;

This instruction adds the 16-bit data contained in source word EDE and destination

word TONI and places the 16-bit result into the destination word TONI. For this

example, the instruction is located at address 2F034h.

Source: Word EDE at address 3379Ch, pointed to by PC + 4766h, which is the 16-bit result

of 3379Ch – 2F036h = 04766h. Address 2F036h is the location of the index for this

example.

Destination: Word TONI located at address 00778h pointed to by the absolute address 00778h

# 1.4.3.3 MSP430X Instruction With Symbolic Mode

When using an MSP430X instruction with Symbolic mode, the operand can be located anywhere in the range of PC + 19 bits.

Length: Three or four words

Operation: The operand address is the sum of the 20-bit PC and the 20-bit index. The 4 MSBs

of the index are contained in the extension word; the 16 LSBs are contained in the

word following the instruction.

Comment: Valid for source and destination. The assembler calculates the register index and

inserts it.

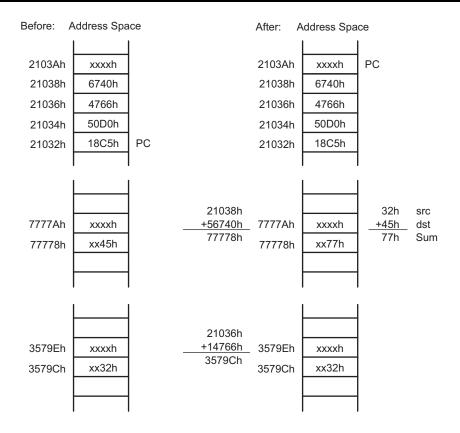

Example: ADDX.B EDE, TONI ;

This instruction adds the 8-bit data contained in source byte EDE and destination

byte TONI and places the result into the destination byte TONI.

Source: Byte EDE located at address 3579Ch, pointed to by PC + 14766h, is the 20-bit

result of 3579Ch - 21036h = 14766h. Address 21036h is the address of the index

in this example.

Destination: Byte TONI located at address 77778h, pointed to by PC + 56740h, is the 20-bit

result of 77778h - 21038h = 56740h. Address 21038h is the address of the index in

this example.

Addressing Modes www.ti.com

### 1.4.4 Absolute Mode

The Absolute mode uses the contents of the word following the instruction as the address of the operand. The Absolute mode has two addressing possibilities:

- Absolute mode in lower 64KB memory

- MSP430X instruction with Absolute mode

### 1.4.4.1 Absolute Mode in Lower 64KB

If an MSP430 instruction is used with Absolute addressing mode, the absolute address is a 16-bit value and, therefore, points to an address in the lower 64KB of the memory range. The address is calculated as an index from 0 and is stored in the word following the instruction The RAM and the peripheral registers can be accessed this way and existing MSP430 software is usable without modifications.

Length: Two or three words

Operation: The operand is the content of the addressed memory location.

Comment: Valid for source and destination. The assembler calculates the index from 0 and

inserts it.

Example: ADD.W &EDE,&TONI;

This instruction adds the 16-bit data contained in the absolute source and

destination addresses and places the result into the destination.

Source: Word at address EDE

Destination: Word at address TONI

### 1.4.4.2 MSP430X Instruction With Absolute Mode

If an MSP430X instruction is used with Absolute addressing mode, the absolute address is a 20-bit value and, therefore, points to any address in the memory range. The address value is calculated as an index from 0. The 4 MSBs of the index are contained in the extension word, and the 16 LSBs are contained in the word following the instruction.

Length: Three or four words

Operation: The operand is the content of the addressed memory location.

Comment: Valid for source and destination. The assembler calculates the index from 0 and

inserts it.

Example: ADDX.A &EDE,&TONI;

This instruction adds the 20-bit data contained in the absolute source and

destination addresses and places the result into the destination.

Source: Two words beginning with address EDE

Destination: Two words beginning with address TONI

**TRUMENTS**

Addressing Modes www.ti.com

| Before:                                        | Address<br>Space              |    | After:                                         | Address<br>Space              |                             |                   |

|------------------------------------------------|-------------------------------|----|------------------------------------------------|-------------------------------|-----------------------------|-------------------|

| 2103Ah<br>21038h<br>21036h<br>21034h<br>21032h | xxxxh 7778h 579Ch 52D2h 1987h | PC | 2103Ah<br>21038h<br>21036h<br>21034h<br>21032h | xxxxh 7778h 579Ch 52D2h 1987h | PC                          |                   |

| 7777Ah<br>77778h                               | 0001h<br>2345h                |    | 7777Ah<br>77778h                               | 0007h<br>7777h                | 65432h<br>+12345h<br>77777h | src<br>dst<br>Sum |

| 3579Eh<br>3579Ch                               | 0006h<br>5432h                |    | 3579Eh<br>3579Ch                               | 0006h<br>5432h                |                             |                   |

# 1.4.5 Indirect Register Mode

The Indirect Register mode uses the contents of the CPU register Rsrc as the source operand. The Indirect Register mode always uses a 20-bit address.

Length: One, two, or three words

The operand is the content the addressed memory location. The source register Operation:

Rsrc is not modified.

Comment: Valid only for the source operand. The substitute for the destination operand is

0(Rdst).

Example: ADDX.W @R5,2100h(R6)

This instruction adds the two 16-bit operands contained in the source and the

destination addresses and places the result into the destination.

Source: Word pointed to by R5. R5 contains address 3579Ch for this example.

Destination: Word pointed to by R6 + 2100h, which results in address 45678h + 2100h = 7778h

# 1.4.6 Indirect Autoincrement Mode

The Indirect Autoincrement mode uses the contents of the CPU register Rsrc as the source operand. Rsrc is then automatically incremented by 1 for byte instructions, by 2 for word instructions, and by 4 for address-word instructions immediately after accessing the source operand. If the same register is used for source and destination, it contains the incremented address for the destination access. Indirect Autoincrement mode always uses 20-bit addresses.

Length: One, two, or three words

Operation: The operand is the content of the addressed memory location.

Comment: Valid only for the source operand

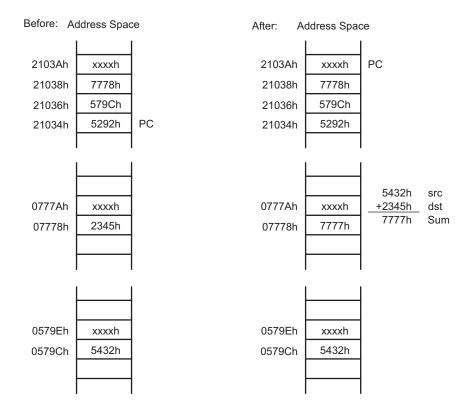

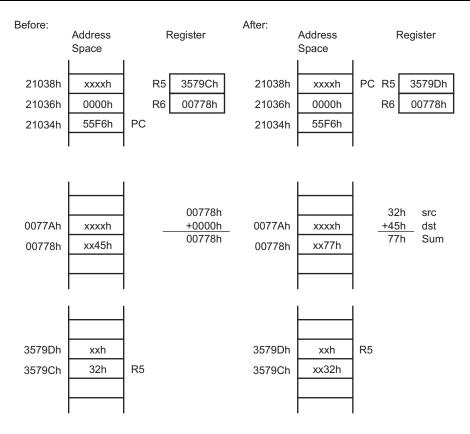

Example: ADD.B @R5+,0(R6)

This instruction adds the 8-bit data contained in the source and the destination

addresses and places the result into the destination.

Source: Byte pointed to by R5. R5 contains address 3579Ch for this example.

Destination: Byte pointed to by R6 + 0h, which results in address 0778h for this example

TEXAS INSTRUMENTS

Addressing Modes www.ti.com

# 1.4.7 Immediate Mode

The Immediate mode allows accessing constants as operands by including the constant in the memory location following the instruction. The PC is used with the Indirect Autoincrement mode. The PC points to the immediate value contained in the next word. After the fetching of the immediate operand, the PC is incremented by 2 for byte, word, or address-word instructions. The Immediate mode has two addressing possibilities:

- 8-bit or 16-bit constants with MSP430 instructions

- 20-bit constants with MSP430X instruction

### 1.4.7.1 MSP430 Instructions With Immediate Mode

If an MSP430 instruction is used with Immediate addressing mode, the constant is an 8- or 16-bit value and is stored in the word following the instruction.

Length: Two or three words. One word less if a constant of the constant generator can be

used for the immediate operand.

Operation: The 16-bit immediate source operand is used together with the 16-bit destination

operand.

Comment: Valid only for the source operand

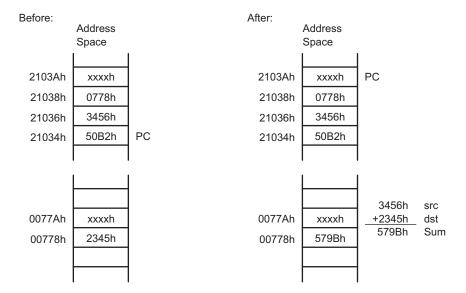

Example: ADD #3456h,&TONI

This instruction adds the 16-bit immediate operand 3456h to the data in the

destination address TONI.

Source: 16-bit immediate value 3456h

Destination: Word at address TONI

### 1.4.7.2 MSP430X Instructions With Immediate Mode

If an MSP430X instruction is used with Immediate addressing mode, the constant is a 20-bit value. The 4 MSBs of the constant are stored in the extension word, and the 16 LSBs of the constant are stored in the word following the instruction.

Length: Three or four words. One word less if a constant of the constant generator can be

used for the immediate operand.

Operation: The 20-bit immediate source operand is used together with the 20-bit destination

operand.

Comment: Valid only for the source operand

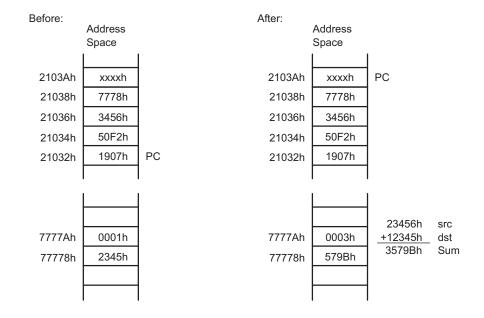

Example: ADDX.A #23456h,&TONI ;

This instruction adds the 20-bit immediate operand 23456h to the data in the

destination address TONI.

Source: 20-bit immediate value 23456h

Destination: Two words beginning with address TONI

### 1.5 MSP430 and MSP430X Instructions

MSP430 instructions are the 27 implemented instructions of the MSP430 CPU. These instructions are used throughout the 1MB memory range unless their 16-bit capability is exceeded. The MSP430X instructions are used when the addressing of the operands or the data length exceeds the 16-bit capability of the MSP430 instructions.

There are three possibilities when choosing between an MSP430 and MSP430X instruction:

- To use only the MSP430 instructions The only exceptions are the CALLA and the RETA instruction. This can be done if a few, simple rules are met:

- Place all constants, variables, arrays, tables, and data in the lower 64KB. This allows the use of MSP430 instructions with 16-bit addressing for all data accesses. No pointers with 20-bit addresses are needed.

- Place subroutine constants immediately after the subroutine code. This allows the use of the symbolic addressing mode with its 16-bit index to reach addresses within the range of PC + 32KB.

- To use only MSP430X instructions The disadvantages of this method are the reduced speed due to the additional CPU cycles and the increased program space due to the necessary extension word for any double-operand instruction.

- Use the best fitting instruction where needed.

Section 1.5.1 lists and describes the MSP430 instructions, and Section 1.5.2 lists and describes the MSP430X instructions.

### 1.5.1 MSP430 Instructions

The MSP430 instructions can be used, regardless if the program resides in the lower 64KB or beyond it. The only exceptions are the instructions CALL and RET, which are limited to the lower 64KB address range. CALLA and RETA instructions have been added to the MSP430X CPU to handle subroutines in the entire address range with no code size overhead.

# 1.5.1.1 MSP430 Double-Operand (Format I) Instructions

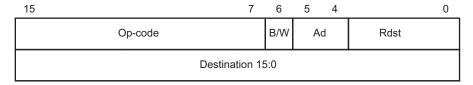

Figure 1-22 shows the format of the MSP430 double-operand instructions. Source and destination words are appended for the Indexed, Symbolic, Absolute, and Immediate modes. Table 1-4 lists the 12 MSP430 double-operand instructions.

Figure 1-22. MSP430 Double-Operand Instruction Format

www.ti.com

Table 1-4. MSP430 Double-Operand Instructions

| Mnemonic  | S-Reg,  | Omeration                                                              |   | Status Bits <sup>(1)</sup> |   |   |  |  |

|-----------|---------|------------------------------------------------------------------------|---|----------------------------|---|---|--|--|

| winemonic | D-Reg   | Operation                                                              | V | N                          | Z | С |  |  |

| MOV(.B)   | src,dst | $src \rightarrow dst$                                                  | _ | _                          | _ | _ |  |  |

| ADD(.B)   | src,dst | $\operatorname{src} + \operatorname{dst} \to \operatorname{dst}$       | * | *                          | * | * |  |  |

| ADDC(.B)  | src,dst | $src + dst + C \rightarrow dst$                                        | * | *                          | * | * |  |  |

| SUB(.B)   | src,dst | $dst + .not.src + 1 \rightarrow dst$                                   | * | *                          | * | * |  |  |

| SUBC(.B)  | src,dst | $dst + .not.src + C \rightarrow dst$                                   | * | *                          | * | * |  |  |

| CMP(.B)   | src,dst | dst - src                                                              | * | *                          | * | * |  |  |

| DADD(.B)  | src,dst | $src + dst + C \rightarrow dst (decimally)$                            | * | *                          | * | * |  |  |

| BIT(.B)   | src,dst | src .and. dst                                                          | 0 | *                          | * | Z |  |  |

| BIC(.B)   | src,dst | .not.src .and. $dst \rightarrow dst$                                   | _ | _                          | _ | _ |  |  |

| BIS(.B)   | src,dst | $src.or. dst \rightarrow dst$                                          |   | _                          | _ | _ |  |  |

| XOR(.B)   | src,dst | $src.xor. dst \rightarrow dst$                                         | * | *                          | * | Z |  |  |

| AND(.B)   | src,dst | $\operatorname{src}$ .and. $\operatorname{dst} \to \operatorname{dst}$ | 0 | *                          | * | Z |  |  |

<sup>(1) \* =</sup> Status bit is affected.

# 1.5.1.2 MSP430 Single-Operand (Format II) Instructions

Figure 1-23 shows the format for MSP430 single-operand instructions, except RETI. The destination word is appended for the Indexed, Symbolic, Absolute, and Immediate modes. Table 1-5 lists the seven single-operand instructions.

Figure 1-23. MSP430 Single-Operand Instructions

Table 1-5. MSP430 Single-Operand Instructions

| Mnemonic   | S-Reg, Operation Statu |                                                                                                |   |   |   |   |

|------------|------------------------|------------------------------------------------------------------------------------------------|---|---|---|---|

| Willemonic | D-Reg                  | Operation                                                                                      | ٧ | N | Z | С |

| RRC(.B)    | dst                    | $C \to MSB \to \!\! \dots \!\! \dots \!\! LSB \to C$                                           | 0 | * | * | * |

| RRA(.B)    | dst                    | $MSB \to MSB \to LSB \to C$                                                                    | 0 | * | * | * |

| PUSH(.B)   | src                    | SP - 2 $\rightarrow$ SP, src $\rightarrow$ SP                                                  | - | - | - | - |

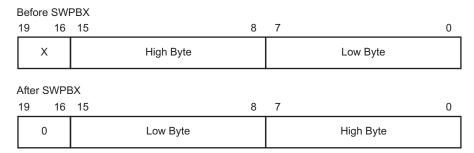

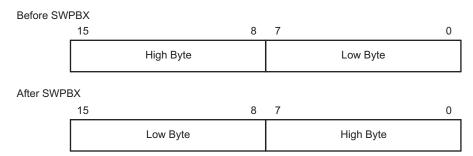

| SWPB       | dst                    | bit 15bit 8 ↔ bit 7bit 0                                                                       | - | - | - | - |

| CALL       | dst                    | Call subroutine in lower 64KB                                                                  | - | - | - | - |

| RETI       |                        | $TOS \to SR, SP + 2 \to SP$                                                                    | * | * | * | * |

|            |                        | $TOS \to PC, SP + 2 \to SP$                                                                    |   |   |   |   |

| SXT        | dst                    | Register mode: bit $7 \rightarrow$ bit 8bit 19<br>Other modes: bit $7 \rightarrow$ bit 8bit 15 | 0 | * | * | Z |

<sup>(1) \* =</sup> Status bit is affected.

<sup>- =</sup> Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

<sup>-</sup> = Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

## 1.5.1.3 Jump Instructions

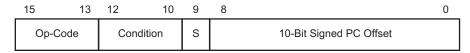

Figure 1-24 shows the format for MSP430 and MSP430X jump instructions. The signed 10-bit word offset of the jump instruction is multiplied by two, sign-extended to a 20-bit address, and added to the 20-bit PC. This allows jumps in a range of –511 to +512 words relative to the PC in the full 20-bit address space. Jumps do not affect the status bits. Table 1-6 lists and describes the eight jump instructions.

Figure 1-24. Format of Conditional Jump Instructions

**Table 1-6. Conditional Jump Instructions**

| Mnemonic | S-Reg,<br>D-Reg | Operation                            |

|----------|-----------------|--------------------------------------|

| JEQ, JZ  | Label           | Jump to label if zero bit is set     |

| JNE, JNZ | Label           | Jump to label if zero bit is reset   |

| JC       | Label           | Jump to label if carry bit is set    |

| JNC      | Label           | Jump to label if carry bit is reset  |

| JN       | Label           | Jump to label if negative bit is set |

| JGE      | Label           | Jump to label if (N .XOR. V) = 0     |

| JL       | Label           | Jump to label if (N .XOR. V) = 1     |

| JMP      | Label           | Jump to label unconditionally        |

### 1.5.1.4 Emulated Instructions

In addition to the MSP430 and MSP430X instructions, emulated instructions are instructions that make code easier to write and read, but do not have op-codes themselves. Instead, they are replaced automatically by the assembler with a core instruction. There is no code or performance penalty for using emulated instructions. The emulated instructions are listed in Table 1-7.

Table 1-7. Emulated Instructions

| Instruction  | Explanation                | Emulation -     | Status Bits <sup>(1)</sup> |   |   |   |

|--------------|----------------------------|-----------------|----------------------------|---|---|---|

| mstruction   | Explanation                | Emulation       | V                          | N | Z | С |

| ADC(.B) dst  | Add Carry to dst           | ADDC(.B) #0,dst | *                          | * | * | * |

| BR dst       | Branch indirectly dst      | MOV dst,PC      | _                          | - | _ | - |

| CLR(.B) dst  | Clear dst                  | MOV(.B) #0,dst  | _                          | - | _ | - |

| CLRC         | Clear Carry bit            | BIC #1,SR       | -                          | - | - | 0 |

| CLRN         | Clear Negative bit         | BIC #4,SR       | -                          | 0 | - | - |

| CLRZ         | Clear Zero bit             | BIC #2,SR       | -                          | - | 0 | - |

| DADC(.B) dst | Add Carry to dst decimally | DADD(.B) #0,dst | *                          | * | * | * |

| DEC(.B) dst  | Decrement dst by 1         | SUB(.B) #1,dst  | *                          | * | * | * |

| DECD(.B) dst | Decrement dst by 2         | SUB(.B) #2,dst  | *                          | * | * | * |

| DINT         | Disable interrupt          | BIC #8,SR       | -                          | - | - | - |

| EINT         | Enable interrupt           | BIS #8,SR       | -                          | - | - | - |

| INC(.B) dst  | Increment dst by 1         | ADD(.B) #1,dst  | *                          | * | * | * |

| INCD(.B) dst | Increment dst by 2         | ADD(.B) #2,dst  | *                          | * | * | * |

<sup>(1) \* =</sup> Status bit is affected.

<sup>-=</sup> Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

Table 1-7. Emulated Instructions (continued)

| Instruction | Explanation                            | Emulation —      | Status Bits <sup>(1)</sup> |   |   |   |

|-------------|----------------------------------------|------------------|----------------------------|---|---|---|

| mstruction  | Explanation                            | Emulation —      | ٧                          | N | Z | С |

| INV(.B) dst | Invert dst                             | XOR(.B) #-1,dst  | *                          | * | * | * |

| NOP         | No operation                           | MOV R3,R3        | -                          | - | _ | _ |

| POP dst     | Pop operand from stack                 | MOV @SP+,dst     | -                          | - | - | - |

| RET         | Return from subroutine                 | MOV @SP+,PC      | -                          | - | _ | - |

| RLA(.B) dst | Shift left dst arithmetically          | ADD(.B) dst,dst  | *                          | * | * | * |

| RLC(.B) dst | Shift left dst logically through Carry | ADDC(.B) dst,dst | *                          | * | * | * |

| SBC(.B) dst | Subtract Carry from dst                | SUBC(.B) #0,dst  | *                          | * | * | * |

| SETC        | Set Carry bit                          | BIS #1,SR        | -                          | - | _ | 1 |

| SETN        | Set Negative bit                       | BIS #4,SR        | -                          | 1 | _ | - |

| SETZ        | Set Zero bit                           | BIS #2,SR        | -                          | _ | 1 | - |

| TST(.B) dst | Test dst (compare with 0)              | CMP(.B) #0,dst   | 0                          | * | * | 1 |

### 1.5.1.5 MSP430 Instruction Execution

The number of CPU clock cycles required for an instruction depends on the instruction format and the addressing modes used – not the instruction itself. The number of clock cycles refers to MCLK.

# 1.5.1.5.1 Instruction Cycles and Length for Interrupt, Reset, and Subroutines

Table 1-8 lists the length and the CPU cycles for reset, interrupts, and subroutines.

Table 1-8. Interrupt, Return, and Reset Cycles and Length

| Action                                                             | Execution Time (MCLK Cycles) | Length of Instruction (Words) |

|--------------------------------------------------------------------|------------------------------|-------------------------------|

| Return from interrupt RETI                                         | 5                            | 1                             |

| Return from subroutine RET                                         | 4                            | 1                             |

| Interrupt request service (cycles needed before first instruction) | 6                            | -                             |

| WDT reset                                                          | 4                            | -                             |

| Reset (RST/NMI)                                                    | 4                            | -                             |

# 1.5.1.5.2 Format II (Single-Operand) Instruction Cycles and Lengths

Table 1-9 lists the length and the CPU cycles for all addressing modes of the MSP430 single-operand instructions.

Table 1-9. MSP430 Format II Instruction Cycles and Length

|                 | No. of Cycles         |      |               | Length of |             |  |

|-----------------|-----------------------|------|---------------|-----------|-------------|--|

| Addressing Mode | RRA, RRC<br>SWPB, SXT | PUSH | CALL Instruct |           | Example     |  |

| Rn              | 1                     | 3    | 4             | 1         | SWPB R5     |  |

| @Rn             | 3                     | 3    | 4             | 1         | RRC @R9     |  |

| @Rn+            | 3                     | 3    | 4             | 1         | SWPB @R10+  |  |

| #N              | N/A                   | 3    | 4             | 2         | CALL #LABEL |  |

| X(Rn)           | 4                     | 4    | 5             | 2         | CALL 2(R7)  |  |

| EDE             | 4                     | 4    | 5             | 2         | PUSH EDE    |  |

| &EDE            | 4                     | 4    | 6             | 2         | SXT &EDE    |  |

# 1.5.1.5.3 Jump Instructions Cycles and Lengths

All jump instructions require one code word and take two CPU cycles to execute, regardless of whether the jump is taken or not.

# 1.5.1.5.4 Format I (Double-Operand) Instruction Cycles and Lengths

Table 1-10 lists the length and CPU cycles for all addressing modes of the MSP430 Format I instructions.

Table 1-10. MSP430 Format I Instructions Cycles and Length

| Add    | ressing Mode | No. of Cooler    | Length of   | Evenuele         |  |  |

|--------|--------------|------------------|-------------|------------------|--|--|

| Source | Destination  | — No. of Cycles  | Instruction | Example          |  |  |

| Rn     | Rm           | 1                | 1           | MOV R5,R8        |  |  |

|        | PC           | 3                | 1           | BR R9            |  |  |

|        | x(Rm)        | 4 <sup>(1)</sup> | 2           | ADD R5,4(R6)     |  |  |

|        | EDE          | 4 <sup>(1)</sup> | 2           | XOR R8,EDE       |  |  |

|        | &EDE         | 4 <sup>(1)</sup> | 2           | MOV R5, & EDE    |  |  |

| @Rn    | Rm           | 2                | 1           | AND @R4,R5       |  |  |

|        | PC           | 4                | 1           | BR @R8           |  |  |

|        | x(Rm)        | 5 <sup>(1)</sup> | 2           | XOR @R5,8(R6)    |  |  |

|        | EDE          | 5 <sup>(1)</sup> | 2           | MOV @R5,EDE      |  |  |

|        | &EDE         | 5 <sup>(1)</sup> | 2           | XOR @R5,&EDE     |  |  |

| @Rn+   | Rm           | 2                | 1           | ADD @R5+,R6      |  |  |

|        | PC           | 4                | 1           | BR @R9+          |  |  |

|        | x(Rm)        | 5 <sup>(1)</sup> | 2           | XOR @R5,8(R6)    |  |  |

|        | EDE          | 5 <sup>(1)</sup> | 2           | MOV @R9+,EDE     |  |  |

|        | &EDE         | 5 <sup>(1)</sup> | 2           | MOV @R9+,&EDE    |  |  |

| #N     | Rm           | 2                | 2           | MOV #20,R9       |  |  |

|        | PC           | 3                | 2           | BR #2AEh         |  |  |

|        | x(Rm)        | 5 <sup>(1)</sup> | 3           | MOV #0300h,0(SP) |  |  |

|        | EDE          | 5 <sup>(1)</sup> | 3           | ADD #33,EDE      |  |  |

|        | &EDE         | 5 <sup>(1)</sup> | 3           | ADD #33,&EDE     |  |  |

| x(Rn)  | Rm           | 3                | 2           | MOV 2(R5),R7     |  |  |

|        | PC           | 5                | 2           | BR 2(R6)         |  |  |

|        | TONI         | 6 <sup>(1)</sup> | 3           | MOV 4(R7),TONI   |  |  |

|        | x(Rm)        | 6 <sup>(1)</sup> | 3           | ADD 4(R4),6(R9)  |  |  |

|        | &TONI        | 6 <sup>(1)</sup> | 3           | MOV 2(R4),&TONI  |  |  |

| EDE    | Rm           | 3                | 2           | AND EDE,R6       |  |  |

|        | PC           | 5                | 2           | BR EDE           |  |  |

|        | TONI         | 6 <sup>(1)</sup> | 3           | CMP EDE, TONI    |  |  |

|        | x(Rm)        | 6 <sup>(1)</sup> | 3           | MOV EDE, 0(SP)   |  |  |

|        | &TONI        | 6 <sup>(1)</sup> | 3           | MOV EDE,&TONI    |  |  |

| &EDE   | Rm           | 3                | 2           | MOV &EDE,R8      |  |  |

|        | PC           | 5                | 2           | BR &EDE          |  |  |

|        | TONI         | 6 <sup>(1)</sup> | 3           | MOV &EDE,TONI    |  |  |

|        | x(Rm)        | 6 <sup>(1)</sup> | 3           | MOV &EDE,0(SP)   |  |  |

|        | &TONI        | 6 <sup>(1)</sup> | 3           | MOV &EDE,&TONI   |  |  |

$<sup>\,^{\</sup>rm (1)}\,\,$  MOV, BIT, and CMP instructions execute in one fewer cycle.

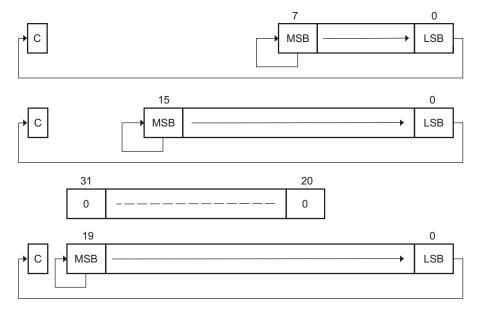

### 1.5.2 MSP430X Extended Instructions

The extended MSP430X instructions give the MSP430X CPU full access to its 20-bit address space. Most MSP430X instructions require an additional word of op-code called the extension word. Some extended instructions do not require an additional word and are noted in the instruction description. All addresses, indexes, and immediate numbers have 20-bit values when preceded by the extension word.

There are two types of extension words:

- Register or register mode for Format I instructions and register mode for Format II instructions

- · Extension word for all other address mode combinations

# 1.5.2.1 Register Mode Extension Word

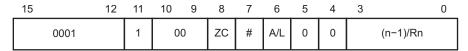

The register mode extension word is shown in Figure 1-25 and described in Table 1-11. An example is shown in Figure 1-27.

Figure 1-25. Extension Word for Register Modes

Table 1-11. Description of the Extension Word Bits for Register Mode

| Bit   | Description                                                                                                                                        |                                                                                                                                              |                     |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|

| 15:11 | Extension word op-code. Op-codes 1800h to 1FFFh are extension words.                                                                               |                                                                                                                                              |                     |  |  |  |

| 10:9  | Reserv                                                                                                                                             | Reserved                                                                                                                                     |                     |  |  |  |

| ZC    | Zero c                                                                                                                                             | Zero carry                                                                                                                                   |                     |  |  |  |

|       | 0                                                                                                                                                  | The executed instruction uses the status of the carry bit C.                                                                                 |                     |  |  |  |

|       | 1                                                                                                                                                  | The executed instruction uses the carry bit as 0. The carry bit is defined by the result of the final operation after instruction execution. |                     |  |  |  |

| #     | Repeti                                                                                                                                             | Repetition                                                                                                                                   |                     |  |  |  |

|       | 0                                                                                                                                                  | The number of instruction repetitions is set by extension word bits 3:0.                                                                     |                     |  |  |  |

|       | 1                                                                                                                                                  | 1 The number of instruction repetitions is defined by the value of the four LSBs of Rn. See description for bits 3:0.                        |                     |  |  |  |

| A/L   | Data length extension. Together with the B/W bits of the following MSP430 instruction, the AL bit defines the used data length of the instruction. |                                                                                                                                              |                     |  |  |  |

|       | A/L                                                                                                                                                | B/W                                                                                                                                          | Comment             |  |  |  |

|       | 0                                                                                                                                                  | 0                                                                                                                                            | Reserved            |  |  |  |

|       | 0                                                                                                                                                  | 1                                                                                                                                            | 20-bit address word |  |  |  |

|       | 1                                                                                                                                                  | 0                                                                                                                                            | 16-bit word         |  |  |  |

|       | 1                                                                                                                                                  | 1                                                                                                                                            | 8-bit byte          |  |  |  |

| 5:4   | Reserved                                                                                                                                           |                                                                                                                                              |                     |  |  |  |

| 3:0   | Repetition count                                                                                                                                   |                                                                                                                                              |                     |  |  |  |

|       | #=0 These four bits set the repetition count n. These bits contain $n-1$ .                                                                         |                                                                                                                                              |                     |  |  |  |

|       | # = 1                                                                                                                                              | #=1 These four bits define the CPU register whose bits 3:0 set the number of repetitions. Rn.3:0 contain $n-1$ .                             |                     |  |  |  |

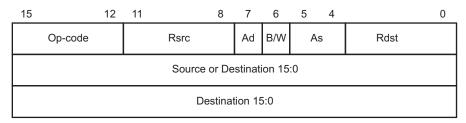

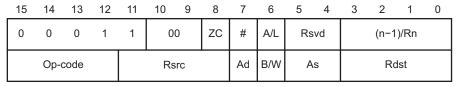

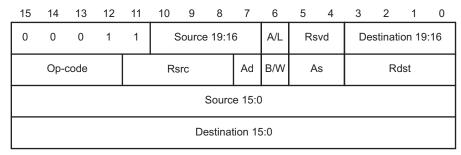

# 1.5.2.2 Non-Register Mode Extension Word

The extension word for non-register modes is shown in Figure 1-26 and described in Table 1-12. An example is shown in Figure 1-28.

Figure 1-26. Extension Word for Non-Register Modes

# Table 1-12. Description of Extension Word Bits for Non-Register Modes

| Bit                       | Desc                                                                                                                                                                  | ription |                     |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|--|

| 15:11                     | Extension word op-code. Op-codes 1800h to 1FFFh are extension words.                                                                                                  |         |                     |  |

| Source Bits<br>19:16      | The four MSBs of the 20-bit source. Depending on the source addressing mode, these four MSBs may belong to an immediate operand, an index, or to an absolute address. |         |                     |  |

| A/L                       | Data length extension. Together with the B/W bits of the following MSP430 instruction, the AL bit defines the used data length of the instruction.                    |         |                     |  |

|                           | A/L                                                                                                                                                                   | B/W     | Comment             |  |

|                           | 0                                                                                                                                                                     | 0       | Reserved            |  |

|                           | 0                                                                                                                                                                     | 1       | 20-bit address word |  |

|                           | 1                                                                                                                                                                     | 0       | 16-bit word         |  |

|                           | 1                                                                                                                                                                     | 1       | 8-bit byte          |  |

| 5:4                       | Reserved                                                                                                                                                              |         |                     |  |

| Destination<br>Bits 19:16 | The four MSBs of the 20-bit destination. Depending on the destination addressing mode, these four MSBs may belong to an index or to an absolute address.              |         |                     |  |

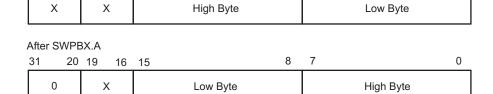

# NOTE: B/W and A/L bit settings for SWPBX and SXTX

| A/L | B/W |                 |

|-----|-----|-----------------|

| 0   | 0   | SWPBX.A, SXTX.A |

| 0   | 1   | N/A             |

| 1   | 0   | SWPB.W, SXTX.W  |

| 1   | 1   | N/A             |

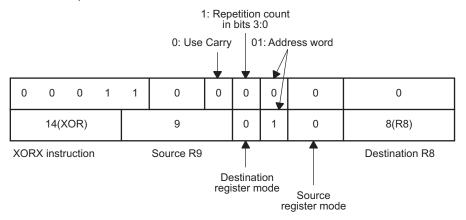

XORX.A R9, R8

Figure 1-27. Example for Extended Register or Register Instruction

www.ti.com

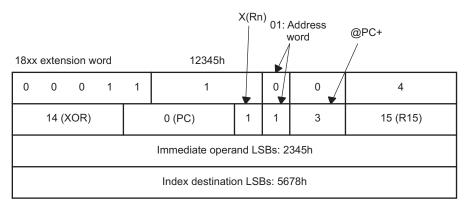

XORX.A #12345h, 45678h(R15)

Figure 1-28. Example for Extended Immediate or Indexed Instruction

# 1.5.2.3 Extended Double-Operand (Format I) Instructions

All 12 double-operand instructions have extended versions as listed in Table 1-13.

Table 1-13. Extended Double-Operand Instructions

| Mnemonic     | Operands | Operation -                                                           | Status Bits <sup>(1)</sup> |   |   |   |  |

|--------------|----------|-----------------------------------------------------------------------|----------------------------|---|---|---|--|

| Willemonic   |          |                                                                       | ٧                          | N | Z | С |  |

| MOVX(.B,.A)  | src,dst  | $src \rightarrow dst$                                                 | _                          | - | - | - |  |

| ADDX(.B,.A)  | src,dst  | $src + dst \rightarrow dst$                                           | *                          | * | * | * |  |

| ADDCX(.B,.A) | src,dst  | $src + dst + C \rightarrow dst$                                       | *                          | * | * | * |  |

| SUBX(.B,.A)  | src,dst  | $dst + .not.src + 1 \rightarrow dst$                                  | *                          | * | * | * |  |

| SUBCX(.B,.A) | src,dst  | $dst + .not.src + C \rightarrow dst$                                  | *                          | * | * | * |  |

| CMPX(.B,.A)  | src,dst  | dst - src                                                             | *                          | * | * | * |  |

| DADDX(.B,.A) | src,dst  | $\text{src} + \text{dst} + \text{C} \rightarrow \text{dst (decimal)}$ | *                          | * | * | * |  |

| BITX(.B,.A)  | src,dst  | src .and. dst                                                         | 0                          | * | * | Z |  |

| BICX(.B,.A)  | src,dst  | .not.src .and. $dst \rightarrow dst$                                  | -                          | - | - | - |  |

| BISX(.B,.A)  | src,dst  | $\text{src .or. dst} \to \text{dst}$                                  | -                          | - | - | - |  |

| XORX(.B,.A)  | src,dst  | $\text{src .xor. dst} \to \text{dst}$                                 | *                          | * | * | Z |  |

| ANDX(.B,.A)  | src,dst  | src .and. $dst \rightarrow dst$                                       | 0                          | * | * | Z |  |

<sup>\* =</sup> Status bit is affected.

<sup>-=</sup> Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

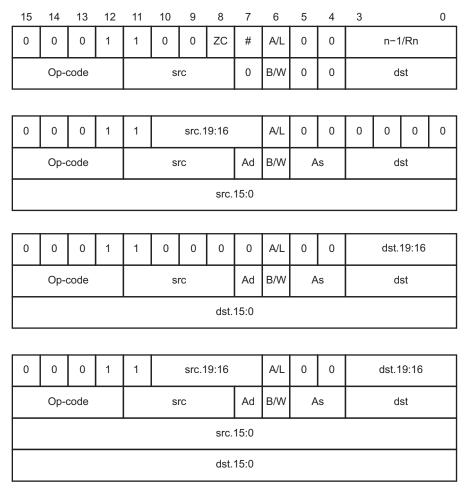

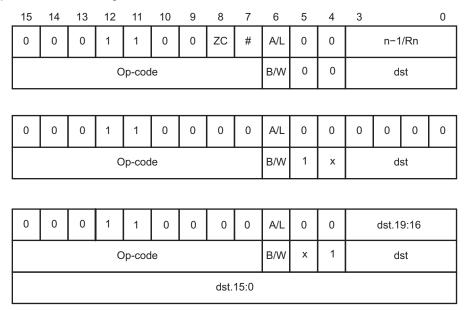

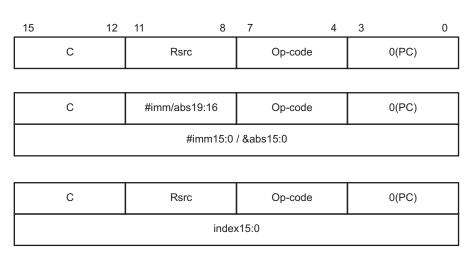

The four possible addressing combinations for the extension word for Format I instructions are shown in Figure 1-29.

Figure 1-29. Extended Format I Instruction Formats

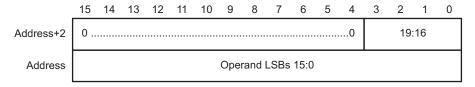

If the 20-bit address of a source or destination operand is located in memory, not in a CPU register, then two words are used for this operand as shown in Figure 1-30.

Figure 1-30. 20-Bit Addresses in Memory

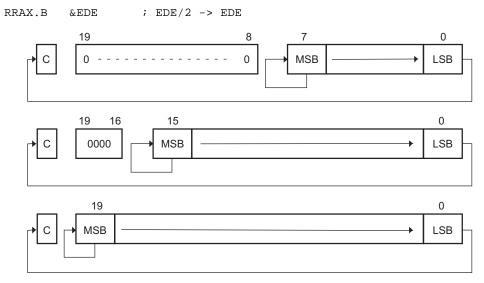

# 1.5.2.4 Extended Single-Operand (Format II) Instructions

Extended MSP430X Format II instructions are listed in Table 1-14.

**Table 1-14. Extended Single-Operand Instructions**

| Mnomonio     | Onerende | Operation                                                      |         |   | Status | Bits <sup>(1)</sup> |   |

|--------------|----------|----------------------------------------------------------------|---------|---|--------|---------------------|---|

| Mnemonic     | Operands | Operation                                                      | n       | ٧ | N      | Z                   | С |

| CALLA        | dst      | Call indirect to subroutine (20-bit address)                   |         | - | -      | -                   | - |

| POPM.A       | #n,Rdst  | Pop n 20-bit registers from stack                              | 1 to 16 | - | -      | -                   | - |

| POPM.W       | #n,Rdst  | Pop n 16-bit registers from stack                              | 1 to 16 | - | -      | -                   | - |

| PUSHM.A      | #n,Rsrc  | Push n 20-bit registers to stack                               | 1 to 16 | - | -      | -                   | - |

| PUSHM.W      | #n,Rsrc  | Push n 16-bit registers to stack                               | 1 to 16 | - | -      | -                   | - |

| PUSHX(.B,.A) | src      | Push 8-, 16-, or 20-bit source to stack                        |         | - | -      | -                   | - |

| RRCM(.A)     | #n,Rdst  | Rotate right Rdst n bits through carry (16-, 20-bit register)  | 1 to 4  | 0 | *      | *                   | * |

| RRUM(.A)     | #n,Rdst  | Rotate right Rdst n bits unsigned (16-, 20-bit register)       | 1 to 4  | 0 | *      | *                   | * |

| RRAM(.A)     | #n,Rdst  | Rotate right Rdst n bits arithmetically (16-, 20-bit register) | 1 to 4  | 0 | *      | *                   | * |

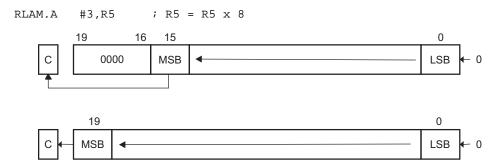

| RLAM(.A)     | #n,Rdst  | Rotate left Rdst n bits arithmetically (16-, 20-bit register)  | 1 to 4  | * | *      | *                   | * |

| RRCX(.B,.A)  | dst      | Rotate right dst through carry (8-, 16-, 20-bit data)          | 1       | 0 | *      | *                   | * |

| RRUX(.B,.A)  | Rdst     | Rotate right dst unsigned (8-, 16-, 20-bit)                    | 1       | 0 | *      | *                   | * |

| RRAX(.B,.A)  | dst      | Rotate right dst arithmetically                                | 1       | 0 | *      | *                   | * |

| SWPBX(.A)    | dst      | Exchange low byte with high byte                               | 1       | _ | _      | _                   | _ |

| SXTX(.A)     | Rdst     | Bit7 → bit8 bit19                                              | 1       | 0 | *      | *                   | Z |

| SXTX(.A)     | dst      | Bit7 $\rightarrow$ bit8 MSB                                    | 1       | 0 | *      | *                   | Z |

<sup>(1) \* =</sup> Status bit is affected.

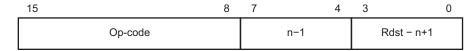

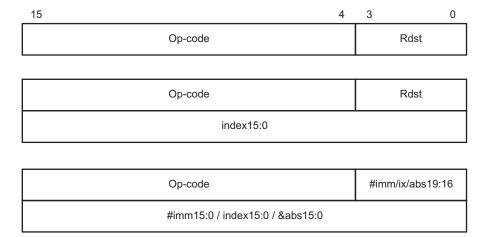

The three possible addressing mode combinations for Format II instructions are shown in Figure 1-31.

Figure 1-31. Extended Format II Instruction Format

<sup>-=</sup> Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

# 1.5.2.4.1 Extended Format II Instruction Format Exceptions

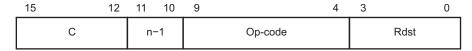

Exceptions for the Format II instruction formats are shown in Figure 1-32 through Figure 1-35.

Figure 1-32. PUSHM and POPM Instruction Format

Figure 1-33. RRCM, RRAM, RRUM, and RLAM Instruction Format

Figure 1-34. BRA Instruction Format

Figure 1-35. CALLA Instruction Format

### 1.5.2.5 Extended Emulated Instructions

The extended instructions together with the constant generator form the extended emulated instructions. Table 1-15 lists the emulated instructions.

**Table 1-15. Extended Emulated Instructions**

| Instruction                 | Explanation                            | Emulation             |

|-----------------------------|----------------------------------------|-----------------------|

| ADCX(.B,.A) dst             | Add carry to dst                       | ADDCX(.B,.A) #0,dst   |

| BRA dst                     | Branch indirect dst                    | MOVA dst,PC           |

| RETA                        | Return from subroutine                 | MOVA @SP+,PC          |

| CLRA Rdst                   | Clear Rdst                             | MOV #0,Rdst           |

| CLRX(.B,.A) dst             | Clear dst                              | MOVX(.B,.A) #0,dst    |

| DADCX(.B,.A) dst            | Add carry to dst decimally             | DADDX(.B,.A) #0,dst   |

| DECX(.B,.A) dst             | Decrement dst by 1                     | SUBX(.B,.A) #1,dst    |

| DECDA Rdst                  | Decrement Rdst by 2                    | SUBA #2,Rdst          |

| DECDX(.B,.A) dst            | Decrement dst by 2                     | SUBX(.B,.A) #2,dst    |

| <pre>INCX(.B,.A) dst</pre>  | Increment dst by 1                     | ADDX(.B,.A) #1,dst    |

| INCDA Rdst                  | Increment Rdst by 2                    | ADDA #2,Rdst          |

| <pre>INCDX(.B,.A) dst</pre> | Increment dst by 2                     | ADDX(.B,.A) #2,dst    |

| INVX(.B,.A) dst             | Invert dst                             | XORX(.B,.A) #-1,dst   |

| RLAX(.B,.A) dst             | Shift left dst arithmetically          | ADDX(.B,.A) dst,dst   |

| RLCX(.B,.A) dst             | Shift left dst logically through carry | ADDCX(.B,.A) dst,dst  |

| SBCX(.B,.A) dst             | Subtract carry from dst                | SUBCX(.B,.A) #0,dst   |

| TSTA Rdst                   | Test Rdst (compare with 0)             | CMPA #0,Rdst          |

| TSTX(.B,.A) dst             | Test dst (compare with 0)              | CMPX(.B,.A) #0,dst    |

| POPX dst                    | Pop to dst                             | MOVX(.B, .A) @SP+,dst |

### 1.5.2.6 MSP430X Address Instructions

MSP430X address instructions are instructions that support 20-bit operands but have restricted addressing modes. The addressing modes are restricted to the Register mode and the Immediate mode, except for the MOVA instruction as listed in Table 1-16. Restricting the addressing modes removes the need for the additional extension-word op-code improving code density and execution time. Address instructions should be used any time an MSP430X instruction is needed with the corresponding restricted addressing mode.

Table 1-16. Address Instructions, Operate on 20-Bit Register Data

| Mnomonio | Onerende       | Operation                                 | S | tatus | Bits | (1) |

|----------|----------------|-------------------------------------------|---|-------|------|-----|

| Mnemonic | Operands       | Operation                                 | ٧ | N     | Z    | С   |

| ADDA     | Rsrc,Rdst      | Add source to destination register        | * | *     | *    | *   |

|          | #imm20,Rdst    |                                           |   |       |      |     |

| MOVA     | Rsrc,Rdst      | Move source to destination                | - | -     | -    | -   |

|          | #imm20,Rdst    |                                           |   |       |      |     |

|          | z16(Rsrc),Rdst |                                           |   |       |      |     |

|          | EDE,Rdst       |                                           |   |       |      |     |

|          | &abs20,Rdst    |                                           |   |       |      |     |

|          | @Rsrc,Rdst     |                                           |   |       |      |     |

|          | @Rsrc+,Rdst    |                                           |   |       |      |     |

|          | Rsrc,z16(Rdst) |                                           |   |       |      |     |

|          | Rsrc,&abs20    |                                           |   |       |      |     |

| CMPA     | Rsrc,Rdst      | Compare source to destination register    | * | *     | *    | *   |