Chapter Excerpt from SLAU208

Chapter 1 SLAU408F–August 2012–Revised March 2018

# Comparator B (Comp\_B)

**NOTE:** This chapter is an excerpt from the *MSP430x5xx and MSP430x6xx Family User's Guide*. The latest version of the full user's guide is available from http://www.ti.com/lit/pdf/slau208.

Comp\_B is an analog voltage comparator. This chapter describes the Comp\_B. Comp\_B supports general comparator functionality for up to 16 channels.

#### Topic

Page

| 1.1 | Comp_B Introduction | 2 |

|-----|---------------------|---|

| 1.2 | Comp_B Operation    | 3 |

| 1.3 | Comp_B Registers    | 9 |

#### Comp\_B Introduction

## 1.1 Comp\_B Introduction

The Comp\_B module supports precision slope analog-to-digital conversions, supply voltage supervision, and monitoring of external analog signals.

Features of Comp\_B include:

- Inverting and noninverting terminal input multiplexer

- Software-selectable RC filter for the comparator output

- Output provided to Timer\_A capture input

- Software control of the port input buffer

- Interrupt capability

- Selectable reference voltage generator, voltage hysteresis generator

- Reference voltage input from shared reference

- Ultra-low-power comparator mode

- · Interrupt driven measurement system low-power operation support

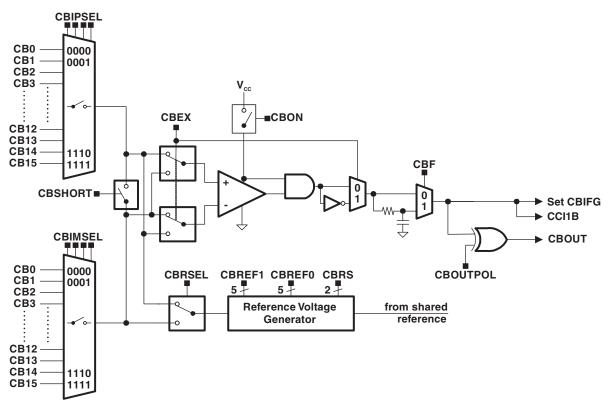

Figure 1-1 shows the Comp\_B block diagram.

Figure 1-1. Comp\_B Block Diagram

## 1.2 Comp\_B Operation

The Comp\_B module is configured by user software. The following sections describe the setup and operation of Comp\_B.

#### 1.2.1 Comparator

The comparator compares the analog voltages at the + and – input terminals. If the + terminal is more positive than the – terminal, the comparator output CBOUT is high. The comparator can be switched on or off using control bit CBON. The comparator should be switched off when not in use to reduce current consumption. When the comparator is off, CBOUT is low when CBOUTPOL bit is set to 0, and CBOUT is high when CBOUTPOL bit is set to 1.

To optimize current consumption for the application, the lowest power mode that meets the comparator speed requirements (see the device-specific data sheet for the comparator propagation delay and response time) should be selected with the CBPWRMD bits. The CBPWRMD bits default to 0x0, which is the highest power and fastest speed. CBPWRMD = 0x2 is the lowest power and slowest speed option.

## 1.2.2 Analog Input Switches

The analog input switches connect or disconnect the two comparator input terminals to associated port pins using the CBIPSELx and CBIMSELx bits. The comparator terminal inputs can be controlled individually. The CBIPSELx and CBIMSELx bits allow:

- Application of an external signal to the + and terminals of the comparator

- Application of an external current source (for example, a resistor) to the + or terminal of the comparator

- The mapping of both terminals of the internal multiplexer to the outside

Internally, the input switch is constructed as a T-switch to suppress distortion in the signal path.

#### NOTE: Comparator input connection

When the comparator is on, the input terminals should be connected to a signal, power, or ground. Otherwise, floating levels may cause unexpected interrupts and increased current consumption.

The CBEX bit controls the input multiplexer, permuting the input signals of the comparator's + and – terminals. Additionally, when the comparator terminals are permuted, the output signal from the comparator is inverted too. This allows the user to determine or compensate for the comparator input offset voltage.

## 1.2.3 Port Logic

The Px.y pins associated with a comparator channel are enabled by the CBIPSELx or CBIMSELx bits to disable its digital components while used as comparator input. Only one of the comparator input pins is selected as input to the comparator by the input multiplexer at a time.

## 1.2.4 Input Short Switch

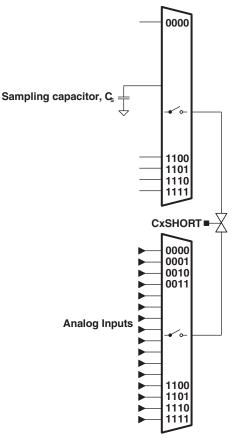

The CBSHORT bit shorts the Comp\_B inputs. This can be used to build a simple sample-and-hold for the comparator as shown in Figure 1-2.

Figure 1-2. Comp\_B Sample-And-Hold

The required sampling time is proportional to the size of the sampling capacitor ( $C_s$ ), the resistance of the input switches in series with the short switch ( $R_i$ ), and the resistance of the external source ( $R_s$ ). The total internal resistance ( $R_i$ ) is typically in the range of 1 k $\Omega$ . The sampling capacitor  $C_s$  should be greater than 100 pF. The time constant, Tau, to charge the sampling capacitor  $C_s$  can be calculated with the following equation:

$$Tau = (R_1 + R_s) \times C_s$$

Depending on the required accuracy, 3 to 10 Tau should be used as a sampling time. With 3 Tau the sampling capacitor is charged to approximately 95% of the input signal voltage level, with 5 Tau it is charged to more than 99%, and with 10 Tau the sampled voltage is sufficient for 12-bit accuracy.

#### 1.2.5 Output Filter

The output of the comparator can be used with or without internal filtering. When control bit CBF is set, the output is filtered with an on-chip RC filter. The delay of the filter can be adjusted in four different steps.

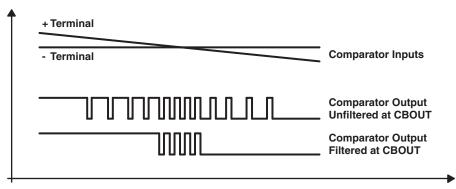

All comparator outputs oscillate if the voltage difference across the input terminals is small (see Figure 1-3). Internal and external parasitic effects and cross coupling on and between signal lines, power supply lines, and other parts of the system are responsible for this behavior. The comparator output oscillation reduces the accuracy and resolution of the comparison result. Selecting the output filter can reduce errors associated with comparator oscillation.

Figure 1-3. RC-Filter Response at the Output of the Comparator

## 1.2.6 Reference Voltage Generator

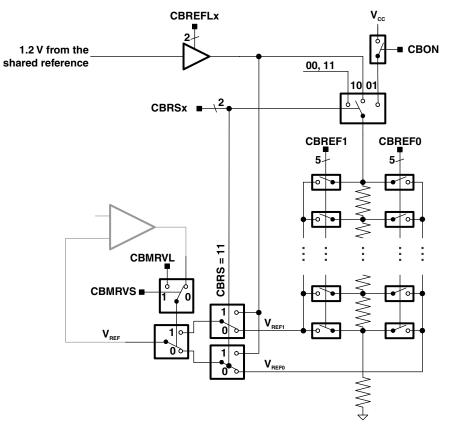

Figure 1-4 shows the Comp\_B reference block diagram.

Figure 1-4. Reference Generator Block Diagram

The voltage reference generator is used to generate VREF, which can be applied to either comparator input terminal. The CBREF1x (VREF1) and CBREF0x (VREF0) bits control the output of the voltage generator. The CBRSEL bit selects the comparator terminal to which VREF is applied. If external signals are applied to both comparator input terminals, the internal reference generator should be turned off to reduce current consumption. The voltage reference generator can generate a fraction of the device's  $V_{cc}$  or of the voltage reference of the integrated precision voltage reference source. Vref1 is used while CBOUT is 1 and Vref0 is used while CBOUT is 0. This allows the generation of a hysteresis without using external components.

#### Comp\_B Operation

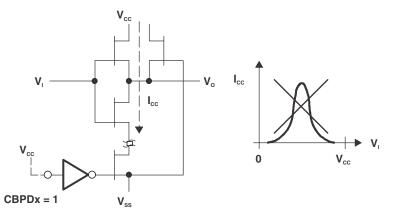

#### 1.2.7 Comp\_B Port Disable Register CBCTL3

The comparator input and output functions are multiplexed with the associated I/O port pins, which are digital CMOS gates. When analog signals are applied to digital CMOS gates, parasitic current can flow from  $V_{cc}$  to GND. This parasitic current occurs if the input voltage is near the transition level of the gate. Disabling the port pin buffer eliminates the parasitic current flow and therefore reduces overall current consumption.

The CBPDx bits in the CBCTL3 register, when set, disable the corresponding Px.y input buffer (see Figure 1-5). When current consumption is critical, any Px.y pin connected to analog signals should be disabled with the associated CBPDx bits.

Selecting an input pin to the comparator multiplexer with the CBIPSEL or CBIMSEL bits automatically disables the input buffer for that pin, regardless of the state of the associated CBPDx bit.

Figure 1-5. Transfer Characteristic and Power Dissipation in a CMOS Inverter/Buffer

#### 1.2.8 Comp\_B Interrupts

One interrupt flag and one interrupt vector is associated with the Comp\_B.

The interrupt flag CBIFG is set on either the rising or falling edge of the comparator output, selected by the CBIES bit. If both the CBIE and the GIE bits are set, the CBIFG interrupt flag generates an interrupt request.

**NOTE:** Changing the value of the CBIES bit might set the comparator interrupt flag CBIFG. This can happen even when the comparator is disabled (CBON = 0). TI recommends clearing CBIFG after configuring the comparator for proper interrupt behavior during operation.

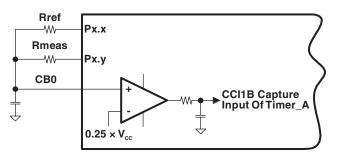

## 1.2.9 Comp\_B Used to Measure Resistive Elements

The Comp\_B can be optimized to precisely measure resistive elements using single slope analog-todigital conversion. For example, temperature can be converted into digital data using a thermistor, by comparing the thermistor's capacitor discharge time to that of a reference resistor (see Figure 1-6). Reference resister Rref is compared to Rmeas.

Figure 1-6. Temperature Measurement System

The resources used to calculate the temperature sensed by Rmeas are:

- Two digital I/O pins charge and discharge the capacitor.

- I/O is set to output high (V<sub>cc</sub>) to charge capacitor, reset to discharge.

- I/O is switched to high-impedance input with CBPDx set when not in use.

- One output charges and discharges the capacitor through Rref.

- One output discharges capacitor through Rmeas.

- The + terminal is connected to the positive terminal of the capacitor.

- The terminal is connected to a reference level, for example 0.25 × V<sub>cc</sub>.

- The output filter should be used to minimize switching noise.

- CBOUT is used to gate Timer\_A CCI1B, capturing capacitor discharge time.

More than one resistive element can be measured. Additional elements are connected to CB0 with available I/O pins and switched to high impedance when not being measured.

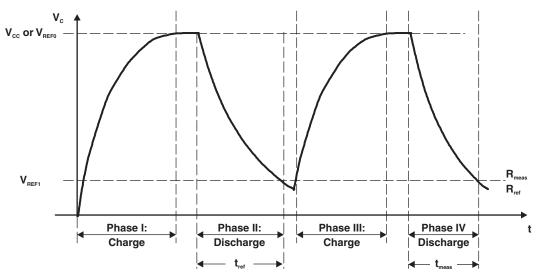

The thermistor measurement is based on a ratiometric conversion principle. The ratio of two capacitor discharge times is calculated as shown in Figure 1-7.

Figure 1-7. Timing for Temperature Measurement Systems

The  $V_{cc}$  voltage and the capacitor value should remain constant during the conversion but are not critical, because they cancel in the ratio:

Comp\_B Operation

www.ti.com

$$\frac{N_{meas}}{N_{ref}} = \frac{-R_{meas} \times C \times \ln \frac{V_{ref1}}{V_{CC}}}{-R_{ref} \times C \times \ln \frac{V_{ref1}}{V_{CC}}}$$

$$\frac{N_{meas}}{N_{ref}} = \frac{R_{meas}}{R_{ref}}$$

$$R_{meas} = R_{ref} \times \frac{N_{meas}}{N_{ref}}$$

## 1.3 Comp\_B Registers

The Comp\_B registers are listed in Table 1-1. The base address of the Comp\_B module can be found in the device-specific data sheet.

| Offset | Acronym | Register Name                | Туре       | Access | Reset | Section       |

|--------|---------|------------------------------|------------|--------|-------|---------------|

| 00h    | CBCTL0  | Comp_B control register 0    | Read/write | Word   | 0000h | Section 1.3.1 |

| 02h    | CBCTL1  | Comp_B control register 1    | Read/write | Word   | 0000h | Section 1.3.2 |

| 04h    | CBCTL2  | Comp_B control register 2    | Read/write | Word   | 0000h | Section 1.3.3 |

| 06h    | CBCTL3  | Comp_B control register 3    | Read/write | Word   | 0000h | Section 1.3.4 |

| 0Ch    | CBINT   | Comp_B interrupt register    | Read/write | Word   | 0000h | Section 1.3.5 |

| 0Eh    | CBIV    | Comp_B interrupt vector word | Read       | Word   | 0000h | Section 1.3.6 |

## Table 1-1. Comp\_B Registers

# 1.3.1 CBCTL0 Register

Comp\_B Control Register 0

|        |          |          | -   | -    |      |      |      |

|--------|----------|----------|-----|------|------|------|------|

| 15     | 14       | 13       | 12  | 11   | 10   | 9    | 8    |

| CBIMEN |          | Reserved |     |      | CBIN | ISEL |      |

| rw-0   | r-0      | r-0      | r-0 | rw-0 | rw-0 | rw-0 | rw-0 |

| 7      | 6        | 5        | 4   | 3    | 2    | 1    | 0    |

| CBIPEN | Reserved |          |     |      | CBIF | SEL  |      |

| rw-0   | r-0      | r-0      | r-0 | rw-0 | rw-0 | rw-0 | rw-0 |

#### Table 1-2. CBCTL0 Register Description

| Bit   | Field    | Туре | Reset | Description                                                                                                                                                                                      |

|-------|----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | CBIMEN   | RW   | Oh    | Channel input enable for the V– terminal of the comparator.<br>0b = Selected analog input channel for V– terminal is disabled.<br>1b = Selected analog input channel for V– terminal is enabled. |

| 14-12 | Reserved | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                                                     |

| 11-8  | CBIMSEL  | RW   | 0h    | Channel input selected for the V- terminal of the comparator if CBIMEN is set to 1.                                                                                                              |

| 7     | CBIPEN   | RW   | Oh    | Channel input enable for the V+ terminal of the comparator.<br>0b = Selected analog input channel for V+ terminal is disabled.<br>1b = Selected analog input channel for V+ terminal is enabled. |

| 6-4   | Reserved | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                                                     |

| 3-0   | CBIPSEL  | RW   | 0h    | Channel input selected for the V+ terminal of the comparator if CBIPEN is set to 1.                                                                                                              |

## 1.3.2 CBCTL1 Register

Comp\_B Control Register 1

| Figure 1-9. CBCTL1 Register |      |      |         |        |      |          |       |  |

|-----------------------------|------|------|---------|--------|------|----------|-------|--|

| 15                          | 14   | 13   | 12      | 11     | 10   | 9        | 8     |  |

| Reserved                    |      |      | CBMRVS  | CBMRVL | CBON | CBPW     | /RMD  |  |

| r-0                         | r-0  | r-0  | rw-0    | rw-0   | rw-0 | rw-0     | rw-0  |  |

| 7                           | 6    | 5    | 4       | 3      | 2    | 1        | 0     |  |

| CBFDLY                      |      | CBEX | CBSHORT | CBIES  | CBF  | CBOUTPOL | CBOUT |  |

| rw-0                        | rw-0 | rw-0 | rw-0    | rw-0   | rw-0 | rw-0     | r-0   |  |

## Table 1-3. CBCTL1 Register Description

| Bit   | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                  |

|-------|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13 | Reserved | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                                                                                                                                 |

| 12    | CBMRVS   | RW   | Oh    | This bit defines if the comparator output selects between VREF0 or VREF1 if CBRS = 00, 01, or 10.<br>0b = Comparator output state selects between VREF0 or VREF1.<br>1b = CBMRVL selects between VREF0 or VREF1.                                                             |

| 11    | CBMRVL   | RW   | Oh    | This bit is valid of CBMRVS is set to 1.<br>0b = VREF0 is selected if CBRS = 00, 01, or 10.<br>1b = VREF1 is selected if CBRS = 00, 01, or 10.                                                                                                                               |

| 10    | CBON     | RW   | Oh    | On. This bit turns the comparator on. When the comparator is turned off the Comp_B consumes no power.<br>Ob = Off<br>1b = On                                                                                                                                                 |

| 9-8   | CBPWRMD  | RW   | Oh    | Power mode. Not all modes are supported in all products. See devices specific data sheet for details.<br>00b = High-speed mode (optional)<br>01b = Normal mode (optional)<br>10b = Ultra-low-power mode (optional)<br>11b = Reserved                                         |

| 7-6   | CBFDLY   | RW   | Oh    | Filter delay. The filter delay can be selected in 4 steps. See the device-specific data sheet for details.<br>00b = Typical filter delay of 450 ns<br>01b = Typical filter delay of 900 ns<br>10b = Typical filter delay of 1800 ns<br>11b = Typical filter delay of 3600 ns |

| 5     | CBEX     | RW   | 0h    | Exchange. This bit permutes the comparator 0 inputs and inverts the comparator 0 output.                                                                                                                                                                                     |

| 4     | CBSHORT  | RW   | Oh    | Input short. This bit shorts the + and – input terminals.<br>0b = Inputs not shorted<br>1b = Inputs shorted                                                                                                                                                                  |

| 3     | CBIES    | RW   | Oh    | Interrupt edge select for CBIIFG and CBIFG<br>0b = Rising edge for CBIFG, falling edge for CBIIFG<br>1b = Falling edge for CBIFG, rising edge for CBIIFG                                                                                                                     |

| 2     | CBF      | RW   | 0h    | Output filter<br>0b = Comp_B output is not filtered<br>1b = Comp_B output is filtered                                                                                                                                                                                        |

| 1     | CBOUTPOL | RW   | 0h    | Output polarity. This bit defines the CBOUT polarity.<br>0b = Noninverted<br>1b = Inverted                                                                                                                                                                                   |

| 0     | CBOUT    | R    | 0h    | Output value. This bit reflects the value of the Comp_B output. Writing this bit has no effect on the comparator output.                                                                                                                                                     |

# 1.3.3 CBCTL2 Register

Comp\_B Control Register 2

| Figure 1-10. | CBCTL2 Register |

|--------------|-----------------|

|--------------|-----------------|

| 15       | 14     | 13     | 12   | 11   | 10     | 9    | 8    |

|----------|--------|--------|------|------|--------|------|------|

| CBREFACC | CBREFL |        |      |      | CBREF1 |      |      |

| rw-0     | rw-0   | rw-0   | rw-0 | rw-0 | rw-0   | rw-0 | rw-0 |

| 7        | 6      | 5      | 4    | 3    | 2      | 1    | 0    |

| CBRS C   |        | CBRSEL |      |      | CBREF0 |      |      |

| rw-0     | rw-0   | rw-0   | rw-0 | rw-0 | rw-0   | rw-0 | rw-0 |

#### Table 1-4. CBCTL2 Register Description

| Bit   | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                              |

|-------|----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | CBREFACC | RW   | Oh    | Reference accuracy. A reference voltage is requested only if CBREFL > 0.<br>0b = Static mode<br>1b = Clocked (low-power, low-accuracy) mode                                                                                                                                                                                                                              |

| 14-13 | CBREFL   | RW   | Oh    | Reference voltage level<br>00b = Reference voltage is disabled. No reference voltage is requested.<br>01b = 1.5 V<br>10b = 2.0 V<br>11b = 2.5 V                                                                                                                                                                                                                          |

| 12-8  | CBREF1   | RW   | 0h    | Reference resistor tap 1. This register defines the tap of the resistor string while CBOUT = 1.                                                                                                                                                                                                                                                                          |

| 7-6   | CBRS     | RW   | 0h    | Reference source. This bit define if the reference voltage is derived from VCC or<br>from the precise shared reference.00b = No current is drawn by the reference circuitry.01b = VCC applied to the resistor ladder10b = Shared reference voltage applied to the resistor ladder.11b = Shared reference voltage supplied to V <sub>CREF</sub> . Resistor ladder is off. |

| 5     | CBRSEL   | RW   | Oh    | Reference select. This bit selects which terminal the $V_{CCREF}$ is applied to.<br>0b = When CBEX = 0: $V_{REF}$ is applied to the + terminal; When CBEX = 1: $V_{REF}$ is applied to the - terminal<br>1b = When CBEX = 0: $V_{REF}$ is applied to the - terminal; When CBEX = 1: $V_{REF}$ is applied to the + terminal                                               |

| 4-0   | CBREF0   | RW   | 0h    | Reference resistor tap 0. This register defines the tap of the resistor string while $CBOUT = 0$ .                                                                                                                                                                                                                                                                       |

# 1.3.4 CBCTL3 Register

Comp\_B Control Register 3

| Figure 1-11. CBCTL3 Register |        |        |        |        |        |        |        |

|------------------------------|--------|--------|--------|--------|--------|--------|--------|

| 15                           | 14     | 13     | 12     | 11     | 10     | 9      | 8      |

| CBPD15                       | CBPD14 | CBPD13 | CBPD14 | CBPD11 | CBPD10 | CBPD9  | CBPD8  |

| rw-(0)                       | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) |

| 7                            | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| CBPD7                        | CBPD6  | CBPD5  | CBPD4  | CBPD3  | CBPD2  | CBPD1  | CBPD0  |

| rw-(0)                       | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) | rw-(0) |

## Table 1-5. CBCTL3 Register Description

| Bit | Field  | Туре | Reset | Description                                                                                                                                                                                                                                    |  |  |  |

|-----|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15  | CBPD15 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD15 disables the port of the comparator<br>channel 15.<br>0b = Input buffer enabled<br>1b = Input buffer disabled |  |  |  |

| 14  | CBPD14 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD14 disables the port of the comparator<br>channel 14.<br>0b = Input buffer enabled<br>1b = Input buffer disabled |  |  |  |

| 13  | CBPD13 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the pins associated with Comp_B. The bit CBPD13 disables the port of the comparator channel 13.<br>Ob = Input buffer enabled<br>1b = Input buffer disabled       |  |  |  |

| 12  | CBPD12 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD12 disables the port of the comparator<br>channel 12.<br>0b = Input buffer enabled<br>1b = Input buffer disabled |  |  |  |

| 11  | CBPD11 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port associated with Comp_B. The bit CBPD11 disables the port of the comparator channel 11.<br>0b = Input buffer enabled<br>1b = Input buffer disabled       |  |  |  |

| 10  | CBPD10 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD10 disables the port of the comparator<br>channel 10.<br>0b = Input buffer enabled<br>1b = Input buffer disabled |  |  |  |

| 9   | CBPD9  | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD9 disables the port of the comparator<br>channel 9.<br>0b = Input buffer enabled<br>1b = Input buffer disabled   |  |  |  |

| 8   | CBPD8  | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD8 disables the port of the comparator<br>channel 8.<br>Ob = Input buffer enabled<br>1b = Input buffer disabled   |  |  |  |

www.ti.com

| Table 1-5. CBCTL3 Register | <sup>•</sup> Description | (continued) |

|----------------------------|--------------------------|-------------|

|----------------------------|--------------------------|-------------|

| Bit | Field | Туре | Reset | Description                                                                                                                                                                                                                                                            |  |  |  |

|-----|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | CBPD7 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port associated with Comp_B. The bit CBPD7 disables the port of the comparator channel 7.                                                                                            |  |  |  |

|     |       |      |       | 0b = Input buffer enabled<br>1b = Input buffer disabled                                                                                                                                                                                                                |  |  |  |

| 6   | CBPD6 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD6 disables the port of the comparator<br>channel 6.<br>0b = Input buffer enabled<br>1b = Input buffer disabled                           |  |  |  |

| 5   | CBPD5 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD5 disables the port of the comparator<br>channel 5.<br>Ob = Input buffer enabled<br>1b = Input buffer disabled                           |  |  |  |

| 4   | CBPD4 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD4 disables the port of the comparator<br>channel 4.<br>Ob = Input buffer enabled<br>1b = Input buffer disabled                           |  |  |  |

| 3   | CBPD3 | RW   | Oh    | <ul> <li>Port disable. This bit individually disables the input buffer for the pins of the port associated with Comp_B. The bit CBPD3 disables the port of the comparator channel 3.</li> <li>Ob = Input buffer enabled</li> <li>1b = Input buffer disabled</li> </ul> |  |  |  |

| 2   | CBPD2 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD2 disables the port of the comparator<br>channel 2.<br>0b = Input buffer enabled<br>1b = Input buffer disabled                           |  |  |  |

| 1   | CBPD1 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD1 disables the port of the comparator<br>channel 1.<br>0b = Input buffer enabled<br>1b = Input buffer disabled                           |  |  |  |

| 0   | CBPD0 | RW   | Oh    | Port disable. This bit individually disables the input buffer for the pins of the port<br>associated with Comp_B. The bit CBPD0 disables the port of the comparator<br>channel 0.<br>0b = Input buffer enabled<br>1b = Input buffer disabled                           |  |  |  |

# 1.3.5 CBINT Register

Comp\_B Interrupt Control Register

|     | Figure 1-12. CBINT Register |      |       |     |     |        |       |

|-----|-----------------------------|------|-------|-----|-----|--------|-------|

| 15  | 14                          | 13   | 12    | 11  | 10  | 9      | 8     |

|     |                             | Rese | erved |     |     | CBIIE  | CBIE  |

| r-0 | r-0                         | r-0  | r-0   | r-0 | r-0 | rw-0   | rw-0  |

| 7   | 6                           | 5    | 4     | 3   | 2   | 1      | 0     |

|     |                             | Rese | erved |     |     | CBIIFG | CBIFG |

| r-0 | r-0                         | r-0  | r-0   | r-0 | r-0 | rw-0   | rw-0  |

## Table 1-6. CBINT Register Description

| Bit   | Field    | Туре | Reset | Description                                                                                                                                                               |

|-------|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-10 | Reserved | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                              |

| 9     | CBIIE    | RW   | 0h    | Comp_B output interrupt enable inverted polarity<br>0b = Interrupt is disabled<br>1b = Interrupt is enabled                                                               |

| 8     | CBIE     | RW   | 0h    | Comp_B output interrupt enable<br>0b = Interrupt is disabled<br>1b = Interrupt is enabled                                                                                 |

| 7-2   | Reserved | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                              |

| 1     | CBIIFG   | RW   | Oh    | Comp_B output inverted interrupt flag. The bit CBIES defines the transition of the output setting this bit.<br>0b = No interrupt pending<br>1b = Output interrupt pending |

| 0     | CBIFG    | RW   | Oh    | Comp_B output interrupt flag. The bit CBIES defines the transition of the output<br>setting this bit.<br>0b = No interrupt pending<br>1b = Output interrupt pending       |

www.ti.com

# 1.3.6 CBIV Register

Comp\_B Interrupt Vector Word Register

| Figure 1-13. CBIV Register |    |    |    |    |     |     |    |

|----------------------------|----|----|----|----|-----|-----|----|

| 15                         | 14 | 13 | 12 | 11 | 10  | 9   | 8  |

| CBIV                       |    |    |    |    |     |     |    |

| rO                         | rO | rO | rO | rO | rO  | rO  | rO |

| 7                          | 6  | 5  | 4  | 3  | 2   | 1   | 0  |

| CBIV                       |    |    |    |    |     |     |    |

| rO                         | rO | rO | rO | rO | r-0 | r-0 | rO |

#### Table 1-7. CBIV Register Description

| Bit  | Field | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | CBIV  | R    | Oh    | Comp_B interrupt vector word register. The interrupt vector register reflects only<br>interrupt flags whose interrupt enable bit are set. Reading the CBIV register<br>clears the pending interrupt flag with the highest priority.<br>00h = No interrupt pending<br>02h = Interrupt Source: CBOUT interrupt; Interrupt Flag: CBIFG; Interrupt<br>Priority: Highest<br>04h = Interrupt Source: CBOUT interrupt inverted polarity; Interrupt Flag:<br>CBIIFG; Interrupt Priority: Lowest |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated