## TMS320TCI6482 Digital Signal Processor Silicon Revisions 3.1, 2.1, 2.0, 1.1

# Silicon Errata

Literature Number: SPRZ235R October 2005–Revised January 2012

### **Contents**

| 1    | Introdu   | ction        |                                                                                                       | 5       |

|------|-----------|--------------|-------------------------------------------------------------------------------------------------------|---------|

|      | 1.1       |              | and Development-Support Tool Nomenclature                                                             |         |

|      | 1.2       |              | e Symbolization and Revision Identification                                                           |         |

| 2    | Silicon   |              | 1 3.1 Usage Notes and Known Design Exceptions to Functional                                           |         |

| _    |           |              | · · · · · · · · · · · · · · · · · · ·                                                                 | 8       |

|      | 2.1       | Usage N      | Notes for Silicon Revision 3.1                                                                        | 8       |

|      |           | 2.1.1        | DDR2 Memory Controller: Chip Enable Pin Remains Low, Always Active                                    | 8       |

|      |           | 2.1.2        | PLL: Hosts Should Not Access the DSP While PLL Registers are Being Configured                         | 8       |

|      |           | 2.1.3        | EMIFA: Chip Enable Pin Must Be Used to Interface With Devices Connected to EMIFA                      | 8       |

|      |           | 2.1.4        | EMIFA: EDMA FIFO Addressing Mode Should Not Be Used When Reading from EMIFA                           | 9       |

|      |           | 2.1.5        | HPI: Certain HPIC Register Bits Will Reset to Default Value Only With Power-On Reset                  | 12      |

|      |           | 2.1.6        | DDR2 Memory Controller and EMIFA: PRIO_RAISE Bits Should Be Changed From Default<br>Following Reset   | 12      |

|      |           | 2.1.7        | Device: Heatsink/Airflow Recommended to Lower Case Temperature                                        | 12      |

|      |           | 2.1.8        | McBSP: Receiver and/or Transmitter Must Out of Reset to Enable Frame-Sync Detection                   | 12      |

|      |           | 2.1.9        | McBSP: Performance Degradation Can Be Seen When Using PCI, UTOPIA, or VLYNQ                           | 12      |

|      |           | 2.1.10       | Boundary Scan: Warnings Relating to the RSV32 and RSV34 Pins May Be Observed When Using Boundary Scan | 13      |

|      |           | 2.1.11       | PCI: DSP PCI Cannot Burst More Than 64 Bytes When Used in Master Mode                                 | 13      |

|      |           | 2.1.12       | DDR2 Memory Controller: Maximum Addressable Memory Increased to 512MB in 32-bit Mode                  | 12      |

|      |           | 2.1.13       | EMAC: Gigabit Mode Cannot Be Used With CPU Running at Speeds Lower Than 750 MHz $$ .                  | 13      |

|      |           | 2.1.14       | DDR2 EMIF: Delay Before CKE Goes High With Different Combinations of REFRESH_RATE ar<br>DDR Clock     | 14      |

|      |           | 2.1.15       | Manual Cache Coherence Operation                                                                      |         |

|      |           | 2.1.16       | AEA3 Must be Tied High with a 1-k $\Omega$ Resisitor if Power is Applied to the SRIO Supply Pins      |         |

|      | 2.2       | Silicon F    | Revision 3.1 Known Design Exceptions to Functional Specifications                                     | 16      |

| 3    |           |              | n 2.1 Usage Notes and Known Design Exceptions to Functional                                           | <u></u> |

|      | •         |              | later for Officer Devicing 0.4                                                                        |         |

|      | 3.1       | 0            | Notes for Silicon Revision 2.1                                                                        |         |

|      | 3.2       |              | Revision 2.1 Known Design Exceptions to Functional Specifications                                     | 64      |

| 4    |           |              | n 2.0 Usage Notes and Known Design Exceptions to Functional                                           | 75      |

| 5    |           |              | n 1.1 Usage Notes and Known Design Exceptions to Functional                                           | 76      |

|      | 5.1       | Usage N      | Notes for Silicon Revision 1.1                                                                        | 76      |

|      |           | 5.1.1        | EMAC: RMII Reference Clock Will Be Changed to Input on Silicon Revision 2.0 and Later                 |         |

|      | 5.2       | Silicon F    | Revision 1.1 Known Design Exceptions to Functional Specifications                                     |         |

| Revi | sion Hist | t <b>ory</b> |                                                                                                       | 83      |

### List of Figures

| 1  | Lot Trace Code Examples for TMS320TCI6482 (CTZ/GTZ/ZTZ Packages)           | 6  |

|----|----------------------------------------------------------------------------|----|

| 2  | Read and Write Synchronous FIFO Interface With Glue Block Diagram          | 9  |

| 3  | Bad TCK Transition                                                         | 23 |

| 4  | Good TCK Transition                                                        | 24 |

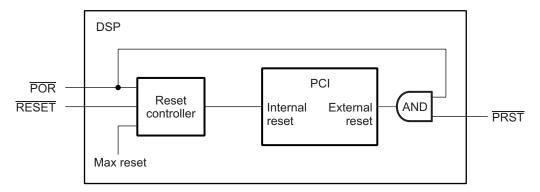

| 5  | Internal Reset Asserted By Reset Controller                                | 29 |

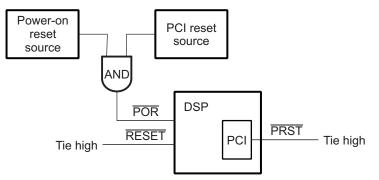

| 6  | Example With RESET and PRST Pins Tied High                                 | 30 |

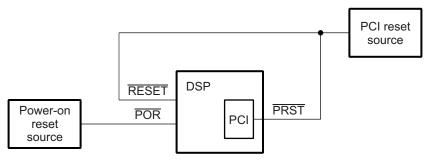

| 7  | Example With PRST and RESET Pins Tied Together                             | 30 |

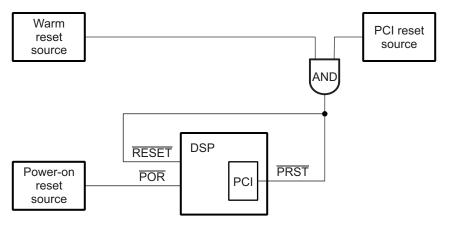

| 8  | Example With Independent Power-On Reset, Warm Reset, and PCI Reset Sources | 30 |

| 9  | Daisy-Chain Example                                                        | 39 |

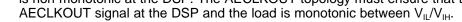

| 10 | AECLKOUT at the DSP                                                        | 43 |

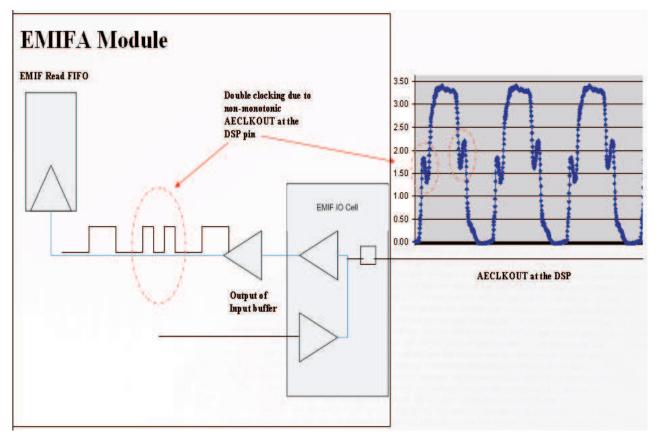

| 11 | 66-MHz Buffer Slew and Timing Performance vs Specification Performance     | 48 |

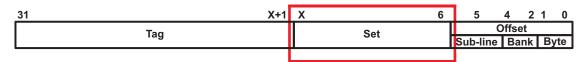

| 12 | L1D Cache Address Mapping                                                  | 56 |

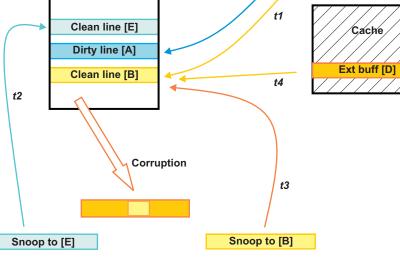

| 13 | Sequence of Events                                                         | 57 |

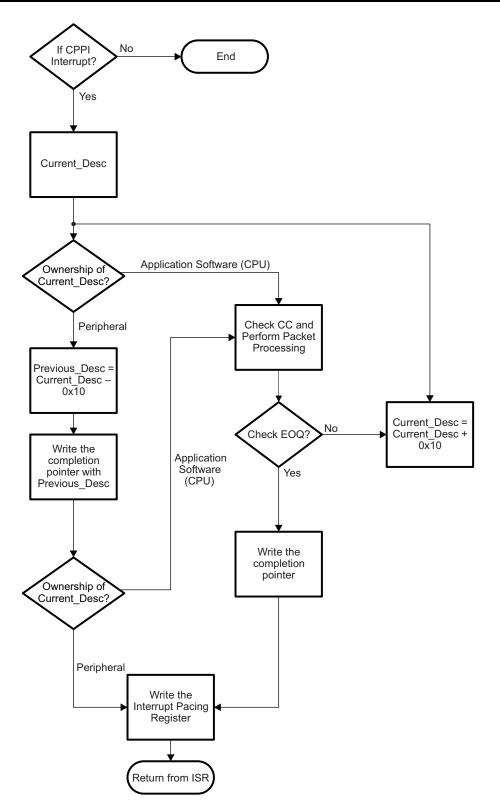

| 14 | ISR Workaround Flowchart                                                   | 62 |

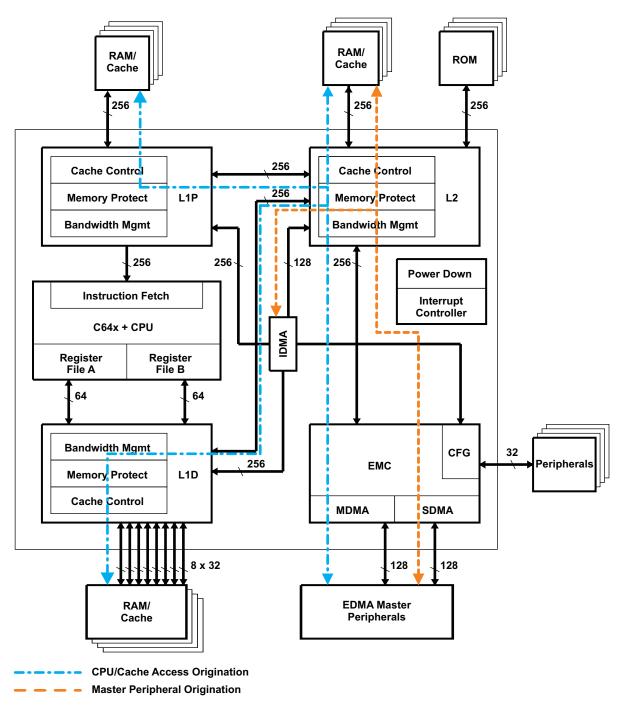

| 15 | IDMA, SDMA, and MDMA Paths                                                 | 66 |

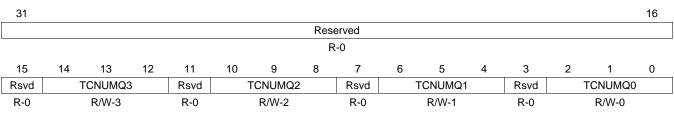

| 16 | QUETCMAP Register (02A0 0280h)                                             | 82 |

### List of Tables

| 1  | Lot Trace Codes                                          | 6         |

|----|----------------------------------------------------------|-----------|

| 2  | Speed and Temperature Grade Symbolization                | 6         |

| 3  | Silicon Revision Variables                               | 7         |

| 4  | 200-µs Delay Calculated Values                           | 14        |

| 5  | 7.8125-µs Interval Calculated Values                     | 14        |

| 6  | Silicon Revision 3.1 Advisory List                       | 16        |

| 7  | Receive Internal Bus Utilization                         | 34        |

| 8  | 1 Port 4x mode Using 4 LSUs, NWRITE packets, 3.125 Gbaud | 34        |

| 9  | 1 Port 1x mode Using 1 LSU, NWRITE packets, 3.125 Gbaud  | 35        |

| 10 | PCI Slew Rate                                            | 48        |

| 11 | Valid Signal Delay                                       | 48        |

| 12 | 66-MHz PCI System Timing                                 | 49        |

| 13 | TCI6482 Default Master Priorities                        | <b>50</b> |

| 14 | Value of X for L1D Cache                                 | 56        |

| 15 | Silicon Revision 2.1 Advisory List                       | 64        |

| 16 | Stall Conditions on Silicon Revisions                    | 72        |

| 17 | Silicon Revision 1.1 Advisory List                       | 77        |

| 18 | TC Connection Matrix                                     | 81        |

| 19 | QUETCMAP Register Field Descriptions                     | 82        |

4

### TMS320TCI6482 Digital Signal Processor Silicon Revisions 3.1, 2.1, 2.0, 1.1

#### 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS320TCI6482 digital signal processor; see the *TMS320TCI6482 Communications Infrastructure Digital Signal Processor* data manual (literature number <u>SPRS246</u>).

The advisory numbers in the document are not sequential. Some advisory numbers have been moved to the next revision. When items are moved, the remaining advisory numbers are not resequenced.

This document also contains "Usage Notes." Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data manual), and the behaviors they describe will not be altered in future silicon revisions.

#### 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., TMS320TCI6482CTZ). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- TMS Fully qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing

- **TMDS** Fully qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

All trademarks are the property of their respective owners.

#### 1.2 Package Symbolization and Revision Identification

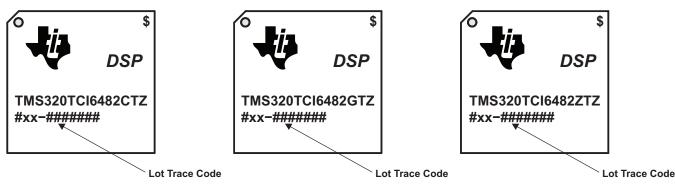

Figure 1 shows an example of TCI6482 package symbolization. The device revision can be determined by the lot trace code marked on the top of the package. The location of the lot trace code for the CTZ, GTZ, and ZTZ packages is shown in Figure 1.

- A Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

- $\mathsf{B} \quad "\#" \text{ denotes an alphanumeric character. } "x" \text{ denotes a numeric character only.}$

- C "\$" denotes the speed and temperature grade of the device. For more information, see Table 2. Note that this symbol is included on all TMS devices. Some TMX devices may not have this symbolization.

#### Figure 1. Lot Trace Code Examples for TMS320TCI6482 (CTZ/GTZ/ZTZ Packages)

Silicon revision correlates to the lot trace code marked on the package. This code is of the format #xx-########. If xx is "11", then the silicon is revision 1.1; if xx is "20", then the silicon is revision 2.0, etc. Table 1 lists the silicon revisions associated with each lot trace code for the TCI6482 devices. Each package also contains symbolization at the top right corner that denotes the speed and temperature grade of the device, see Figure 1 and Table 2. Note that this symbol is included on all TMS devices. Some TMX devices may not have this symbolization.

Each silicon revision uses a specific revision of the CPU and the C64x+ Megamodule. The CPU revision ID identifies the silicon revision of the CPU. Table 3 lists the CPU and C64x+ Megamodule revision associated with each silicon revision. The CPU revision can be read from the REVISION\_ID field of the CPU Control Status Register (CSR). The C64x+ Megamodule revision can be read from the REVISION field of the Megamodule Revision ID register (MM\_REVID) located at address 0181 2000h.

The VARIANT field of the JTAG ID Register (located at 02A8 008h) changes between silicon revisions. Table 2 lists the contents of the JTAG ID Register for each revision of the device. More details on the JTAG ID Register can be found in the *TMS320TCI6482 Communications Infrastructure Digital Signal Processor* data manual (literature number <u>SPRS246</u>).

| LOT TRACE CODE (xx) | SILICON REVISION | COMMENTS                 |

|---------------------|------------------|--------------------------|

| 31                  | 3.1              | Silicon revision 3.1     |

| 21                  | 2.1              | Silicon revision 2.1     |

| 20                  | 2.0              | Silicon revision 2.0     |

| 11                  | 1.1              | Initial silicon revision |

#### Table 1. Lot Trace Codes

| Table 2. Speed and | Temperature | Grade Symbolization |

|--------------------|-------------|---------------------|

|--------------------|-------------|---------------------|

| SPEED/TEMPERATURE GRADE SYMBOLIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SPEED GRADE | TEMPERATURE GRADE |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|

| 1GHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 GHz       | Commercial        |

| A1GHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 GHz       | Extended          |

| <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | 850 MHz     | Commercial        |

7

| SILICON REVISION | CPU REVISION       | C64X+ MEGAMODULE REVISION | JTAG ID REGISTER VALUE |

|------------------|--------------------|---------------------------|------------------------|

| 3.1              | 1.0                | Rev.1                     | 0x4008 A02Fh           |

|                  | (REVISION_ID = 0h) | (MM_REVID[REVISION] = 5h) | (VARIANT = 0100)       |

| 2.1              | 1.0                | Rev. 1                    | 0x2008 A02Fh           |

|                  | (REVISION_ID = 0h) | (MM_REVID[REVISION] = 1h) | (VARIANT = 0010b)      |

| 2.0              | 1.0                | Rev. 1                    | 0x1008 A02Fh           |

|                  | (REVISION_ID = 0h) | (MM_REVID[REVISION] = 1h) | (VARIANT = 0001b)      |

| 1.1              | 1.0                | Rev. 0                    | 0x0008 A02Fh           |

|                  | (REVISION_ID = 0h) | (MM_REVID[REVISION] = 0h) | (VARIANT = 0000b)      |

#### 2 Silicon Revision 3.1 Usage Notes and Known Design Exceptions to Functional Specifications

This section describes the usage notes and advisories that apply to revision 3.1 of the TCI6482 device.

#### 2.1 Usage Notes for Silicon Revision 3.1

8

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data manual), and the behaviors they describe will not be altered in future silicon revisions.

#### 2.1.1 DDR2 Memory Controller: Chip Enable Pin Remains Low, Always Active

The chip enable pin of the DDR2 memory controller, DCE0, is used to enable the DDR2 SDRAM memory device during external memory accesses. Currently, TI documentation shows that the DCE0 pin is goes low to enable the DDR2 SDRAM memory device during external memory accesses and then goes high at the end of the access. However, on the TMS320TCI6482 device, the DCE0 pin stays low throughout the operation of the DDR2 memory controller; it never goes high. Note that this behavior does not affect the ability of the DDR2 memory controller to access DDR2 SDRAM memory devices.

#### 2.1.2 PLL: Hosts Should Not Access the DSP While PLL Registers are Being Configured

The PLL1 controller and PLL2 controller registers can only be programmed through the CPU and the emulator. To configure the PLL controllers, hosts like the HPI and PCI would have to load a small program that does this. However, hosts should hold off accesses to the DSP while the PLL controllers are being configured. Therefore, a mechanism must be in place such that the DSP can let the host know when the PLL configuration has been completed.

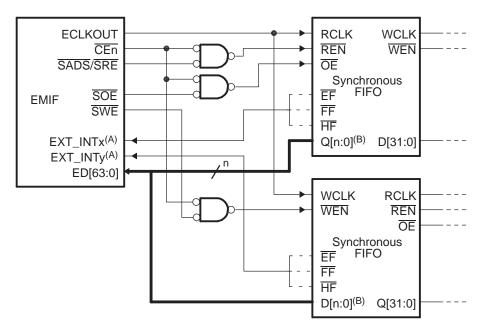

#### 2.1.3 EMIFA: Chip Enable Pin Must Be Used to Interface With Devices Connected to EMIFA

The state of the EMIFA control pins is not defined while the chip enable pins ( $\overline{CE[5:2]}$ ) are high. Furthermore, some control pins may become active while the chip enable pins are driven high. To avoid erroneously activating devices connected to EMIFA, the chip enable pins should be used to select/deselect these devices. If a device being used does not have a chip enable input, then the control pins going to that device should be qualified with a chip enable pin. An example of this is shown in Figure 2.

A GPIO pins on TCI648x devices may be configured as external interrupt sources to the CPU. For more details, see the TMS320TCI648x DSP General-Purpose Input/Output (GPIO) User's Guide (literature number <u>SPRU725</u>).

#### Figure 2. Read and Write Synchronous FIFO Interface With Glue Block Diagram

#### 2.1.4 EMIFA: EDMA FIFO Addressing Mode Should Not Be Used When Reading from EMIFA

As documented in the *TMS320TCI648x DSP Enhanced DMA (EDMA3) Controller User's Guide* (literature number <u>SPRU727</u>), the EDMA includes two types of addressing modes: increment mode and FIFO mode (constant addressing mode). One of these modes must be selected for the source address mode and the destination address mode (SAM and DAM in the channel options parameter (OPT)).

Even though the EDMA supports FIFO mode configurations for SAM and DAM, the EMIFA does not fully support constant addressing mode. Attempts to perform writes to the EMIFA with FIFO mode (constant addressing mode) (DAM == FIFO) will result in the destination address incrementing within a Modulo-64-byte address range; i.e., the data will be written to address <Dst> to <Dst>+63 bytes, repeatedly, until the transfer count programmed for the EDMA transfer is exhausted. This behavior will not be modified on future versions of the TCI6482 device.

Attempts to perform reads from the EMIFA with FIFO mode (SAM == FIFO) on TCI6482 revision 1.1 will result in reading invalid data. An enhancement will be added to TCI6482 revision 2.0 such that reads from the EMIFA in constant addressing mode (SAM == FIFO) will behave much like writes; i.e., reads will be issued to address  $\langle$ SRC> to  $\langle$ SRC> + 63 bytes, repeatedly, until the transfer count programmed for the EDMA transfer is exhausted.

In order to avoid the issues described above with reads/writes to EMIFA when EDMA is configured for FIFO mode, irrespective of device revision, it is suggested that the EDMA always be programmed with SAM and DAM in increment mode. The ACNT and BCNT values, along with proper indexing, can be used to mimic FIFO addressing mode. This is addressed in the first and second recommendations/use cases below. For legacy reasons, it may be necessary to use FIFO mode. This is addressed in the third recommended use case below.

No special requirements exist for addresses accessed by the EDMA in increment mode or for single-word accesses by the CPU or DMA.

9

#### 2.1.4.1 Recommended Implementations for Read/Writes to FIFO Connected to EMIFA

**NOTE:** In the case of ACNT < 64 bytes even though FIFO mode (fixed-mode addressing) is selected by EDMA configuration, the EMIFA will execute the transfer as if it were an increment address transfer. Therefore, the recommended implementation for read/write to FIFO should be increment mode instead of FIFO mode. The examples below provide suggestions for read/writes to FIFO using increment mode.

The following scenarios highlight various options for interfacing with a FIFO connected to the EMIFA and programming the EDMA to access the FIFO.

In general, the use cases are numbered in order of priority. The system designer should attempt to design a system/board/ASIC memory map such that a relatively large memory range is devoted to a FIFO. In this way, the EDMA can be programmed in increment mode for a given DMA transfer, and the transfer from start to finish will reside in the memory range dedicated to a given FIFO.

**Approach 1:** Address space dedicated to the FIFO is greater than or equal to the largest expected EDMA transfer. No performance hit since EDMA ACNT is not artificially constrained.

- FIFO should be aligned on a 64-byte boundary in EMIFA address space.

System memory map and glue logic should be implemented to use EMIFA MS-address bits to decode FIFO address and select FIFO.

- EDMA transfer starting address should match the FIFO's base address.

- Use INCR transfer SRC/DST address mode with ACNT = transfer size.

- Use SBIDX or DBIDX of 0 such that the next EDMA transfer will also begin at the base address of the FIFO (assuming BCNT and/or CCNT are greater than 1).

For example, if the largest possible DMA transfer to/from a FIFO interfaced to EMIFA is 1024 bytes, then a memory range of at least 1024 bytes should be devoted to the FIFO in the EMIFA's memory map. The system glue logic should use the chip enable signals and logical address bits 10 and above if multiple FIFOs reside in the chip enable space. The EDMA transfer can be set with ACNT = 1024 bytes, BCNT = X, CCNT = Y, and an EDMA synchronization type of A-synchronized, The index for the FIFO side of the transfer (either SRC or DST) should be set to 0 such that the same address is used for the next DMA trigger.

**Approach 2:** If the amount of space dedicated to the FIFO is less than the largest expected EDMA, then ACNT and BCNT value with appropriate indexing can be used to control access to the FIFO. This will result in a potential performance impact depending on the size of ACNT.

• FIFO should be aligned on 64-byte boundary in EMIFA address space.

System memory map and glue logic should be implemented to use EMIFA MS-address bits to decode FIFO address and select FIFO.

- EDMA transfer starting address should match the FIFO's base address.

- The EDMA size must be broken into

- ACNT × BCNT = transfer size.

- ACNT must be less than or equal to the address space dedicated to the FIFO.

- If the EDMA transfer size is not a multiple of ACNT, then two EDMA channels must be used.

Completion of the first channel can chain to the second channel, where the second channel is used to transfer the remaining data.

- Use SBIDX or DBIDX of 0 such that the next EDMA transfer will also begin at the base address of the FIFO (assuming BCNT and/or CCNT are greater than 1).

For example, if the desired DMA transfer size to/from a FIFO interfaced to EMIFA is 1024 bytes, but the memory range dedicated to the FIFO is only 64 bytes, then the EDMA transfer must be broken into a 2-D transfer, with ACNT = 64 bytes, BCNT = 16, CCNT = X, and an EDMA synchronization type of AB-synchronized. The index for the FIFO side of the transfer (either SRC or DST) should be set to 0 such that the same address is used for the next DMA trigger.

With the same example, if the desired DMA transfer size is 1028-bytes, an additional channel with ACNT = 4 bytes must be used. Completion of the first channel needs to chain trigger the second channel.

**Approach 3:** For legacy purposes, FIFO mode can be used with the restrictions below. This is a compromise between Approach 1 and Approach 2. Approach 3 allows the programmer to use an unrestricted ACNT value while the hardware forces the addresses accessed to reside within a 64-byte boundary, whereas Approach 2 uses a software mechanism to restrict addresses to the desired address ranges. If a FIFO requires an address range smaller than 64 bytes, then FIFO mode cannot be used; Approach 2 must be used instead.

### TCI6482 revision 1.1

Writes to EMIFA in FIFO mode are allowed but addresses will increment within a 64-byte boundary.

- FIFO should be aligned on 64-byte boundary in EMIFA address space.

- System memory map and glue logic should be implemented to use EMIFA MS-address bits to decode FIFO address and select FIFO.

- EDMA transfer starting address should match the FIFO's base address.

- Use FIFO transfer DST address mode with ACNT = transfer size.

- Use DBIDX of 0 such that the next EDMA transfer will also begin at the base address of the FIFO (assuming BCNT and/or CCNT are greater than 1).

For example, if a transfer is greater than or equal to 64 bytes, then a memory range of at least 64 bytes should be devoted to the FIFO in the EMIFA's memory map. The system glue logic should use the chip enable signal and logical address bits 6 and above for address decoding if multiple FIFOs or other memory types reside in the chip enable space. The EDMA transfer can be set with ACNT = X-bytes, BCNT = Y, CCNT = Z, and an EDMA synchronization type of A-synchronized. The DBIDX should be set to 0 such that the same address is used for the next DMA trigger.

If a transfer is X bytes, where X is less than 64 bytes, then a memory range of at least X bytes should be devoted to the FIFO in the EMIFA's memory map. The system glue logic should use the chip enable signal and the appropriate MS-bits of the address for address decoding if multiple FIFOs or other memory types reside in the chip enable space. The EDMA transfer can be set with ACNT = X-bytes, BCNT = Y, CCNT = Z, and an EDMA synchronization type of A-synchronized. The DBIDX should be set to 0 such that the same address is used for the next DMA trigger.

Reads from EMIFA in FIFO mode will return invalid data and therefore must not be used. Use increment mode for SAM instead of FIFO mode. See Approaches 1 and 2 above.

### TCI6482 revision 2.0

Reads and writes from EMIFA in FIFO mode will both behave like writes in revision 1.1, as described above (increment within 64-byte boundary).

• FIFO should be aligned on 64-byte boundary in EMIFA address space.

System memory map and glue logic should be implemented to use EMIFA MS-address bits to decode FIFO address and select FIFO.

- EDMA transfer starting address should match the FIFO's base address.

- Use FIFO transfer address mode for the FIFO side of the transfer (either SRC or DST) with ACNT = transfer size in bytes.

- Use SBIDX or DBIDX of 0 such that the next EDMA transfer will also begin at the base address of the FIFO (assuming BCNT and/or CCNT are greater than 1).

For example, if a transfer is greater than or equal to 64 bytes, then a memory range of at least 64 bytes should be devoted to the FIFO in the EMIFA's memory map. The system glue logic should use the chip enable signal and logical address bits 6 and above for address decoding if multiple FIFOs or other memory types reside in the chip enable space. The EDMA transfer can be set with ACNT = X-bytes, BCNT = Y, CCNT = Z, and an EDMA synchronization type of A-synchronized. The SBIDX or DBIDX should be set to 0 such that the same address is used for the next DMA trigger.

If a transfer is X bytes, where X is less than 64 bytes, then a memory range of at least X bytes should be devoted to the FIFO in the EMIFA's memory map. The system glue logic should use the chip enable signal and the appropriate MS-bits of the address for address decoding if multiple FIFOs or other memory types reside in the chip enable space. The EDMA transfer can be set with ACNT = X-bytes, BCNT = Y, CCNT = Z, and an EDMA synchronization type of A-synchronized. The SBIDX or DBIDX should be set to 0 such that the same address is used for the next DMA trigger.

#### 2.1.5 HPI: Certain HPIC Register Bits Will Reset to Default Value Only With Power-On Reset

The following bits of the Host Port Interface Control register (HPIC) will only reset to their default values with a power-on reset (POR pin). Other resets, like warm reset (RESET pin) and emulation reset, will not affect these bits.

- HWOB (bit 0)

- HRDY (bit 3)

- HWOBSTAT (bit 8)

- DUALHPIA (bit 9)

- HPIARWSEL (bit 11)

## 2.1.6 DDR2 Memory Controller and EMIFA: PRIO\_RAISE Bits Should Be Changed From Default Following Reset

The reordering and scheduling rules used by EMIFA and DDR2 Memory Controller may lead to command starvation, which is the prevention of certain commands from being processed. Command starvation can result when a continuous stream of high-priority read commands blocks a low-priority write command.

To avoid this condition, EMIFA and DDR2 Memory Controller momentarily raise the priority of the oldest command in the command FIFO after a set number of transfers have been made. The PRIO\_RAISE field in the Burst Priority Register (BPRIO) sets the number of the transfers that must be made before the priority of the oldest command is raised.

By default, this feature of EMIFA and DDR2 Memory Controller is disabled. This means commands can stay in the command FIFO indefinitely. Therefore, to enable this feature with the highest level of allowable memory transfers, the PRIO\_RAISE bits should be set to FEh immediately following reset. These bits can be left as FEh unless advanced bandwidth/prioritization control is required. It is suggested that prioritization be set at the system level to avoid placing high-bandwidth masters on the highest priority levels.

#### 2.1.7 Device: Heatsink/Airflow Recommended to Lower Case Temperature

It is strongly recommended that users complete system-level thermal analysis to account for details of heatsink requirements, airflow, and other factors in order to achieve the case temperature specification of 90°C. The latest power data for the TMS320TCI6482 device indicates that static power is a significant contributor to overall power. Since static power varies with case temperature and voltage, a lower case temperature can greatly impact the overall power consumption. Therefore, the use of a heatsink to lower the case temperature is an effective way to lower power consumption. For further details on the power consumption of the TMS320TCI6482 device, see the *TMS320TCI6482 Power Consumption Summary* (literature number <u>SPRAAF1</u>) application report.

#### 2.1.8 McBSP: Receiver and/or Transmitter Must Out of Reset to Enable Frame-Sync Detection

The McBSP transmitter and receiver on the TCI6482 device are capable of generating an interrupt upon the detection of frame synchronization. The *TMS320C6000 DSP Multichannel Buffered Serial Port (McBSP) Reference Guide* (literature number <u>SPRU580</u>) states that this feature will operate even while the associated portion of the serial port is in reset. However, on the TCI6482 device, the receiver and/or transmitter must be out of reset to enable this feature.

Note that frame synchronization can be detected while the receiver or transmitter are in reset by using the GPIO mode of the frame-sync pin (FSR or FSX). In this configuration, the CPU can monitor the status of the frame-sync pin and switch to the non-GPIO mode when a transition on the frame-sync pin is detected. For more information on the GPIO mode and frame sync detection feature of the McBSP, see the *TMS320C6000 DSP Multichannel Buffered Serial Port (McBSP) Reference Guide* (literature number SPRU580).

#### 2.1.9 McBSP: Performance Degradation Can Be Seen When Using PCI, UTOPIA, or VLYNQ

The McBSP Data Receive Register (DRR) and Data Transmit Register (DXR) can be accessed through two separate busses: the configuration bus and the data bus. Both the CPU and the EDMA can access these busses and, in most cases, the highest performance method is achieved by using the data bus.

However, as shown in the device-specific data manual (see section 4, *System Interconnect*), the McBSP data bus shares a bridge to the data switched central resource with the PCI, UTOPIA, and VLYNQ peripherals. Performance degradations can be observed if any of these peripherals are used and the McBSP DRR and DXR are accessed through the data bus.

Therefore, when the PCI, UTOPIA, and VLYNQ peripherals are used, it is recommended the configuration bus is used to access the McBSP DRR and DXR.

Note that the PCI and VLYNQ peripherals consist of an independent master and slave. The above performance degradation is only an issue when the peripheral is used to initiate transactions on the external bus.

# 2.1.10 Boundary Scan: Warnings Relating to the RSV32 and RSV34 Pins May Be Observed When Using Boundary Scan

Previously, the device-specific data manual required that the RSV32 and RSV34 be tied to  $V_{ss}$  for proper device operation. This is an incorrect configuration for these pins. This configuration may case boundary-scan tools to generate warnings relating to these pins; these warnings are not critical and can be ignored.

The current device-specific data manual has been corrected such that the requirement is now to tie the RSV32 and RSV34 pins to the 1.8-V I/O supply ( $DV_{DD18}$ ) via a 1-k $\Omega$  resistor. This configuration will prevent any boundary-scan warnings relating to these pins.

Existing TCI6482 designs need not be modified to meet the new requirement. The boundary-scan warnings relating to these two pins are not critical and can be ignored. TCI6482 devices will not be damaged by tying the RSV32 and RSV34 pins to  $V_{ss}$ . New TCI6482 designs must tie the RSV32 and RSV34 pins to the 1.8-V I/O supply via a pull-up resistor to avoid these boundary-scan warnings.

### 2.1.11 PCI: DSP PCI Cannot Burst More Than 64 Bytes When Used in Master Mode

The PCI on the TCI6482 can operate as a PCI master and slave. As a slave, the DSP PCI responds to accesses initiated by an off-chip PCI master. As a master, the DSP PCI, itself, initiates transfers on the PCI bus. Usually, for memory read and write transfers, another DSP master such as the EDMA is configured to move data to/from the DSP PCI.

As a PCI master, the DSP PCI is only capable of bursting a maximum of up to 64 bytes. In other words, for memory transfers larger than 64 bytes, the DSP PCI will initiate a transfer, transfer 64 bytes, stop the transfer, and then repeat. As a PCI slave, external PCI masters can burst an infinite amount of data to the DSP PCI. Note that the DSP PCI may insert wait states or generate a target retry if it cannot meet the latency requirement set forth by the PCI system. For example, a PCI access to DSP DDR2 memory may stall due to other master accesses or because of a scheduled DDR2 memory refresh. In this case the DSP PCI will generate a target retry until the DDR2 memory controller is ready to service the PCI request.

Because of this limitation, the DSP PCI throughput will be lower in master mode than in slave mode. To avoid low throughput performance, external PCI masters should be used to move data to/from the DSP PCI whenever possible.

### 2.1.12 DDR2 Memory Controller: Maximum Addressable Memory Increased to 512MB in 32-bit Mode

The maximum addressable memory has been increased from 256MB to 512MB in 32-bit mode and from 128MB to 256MB in 16-bit mode. Revision G and later of the *TMS320TCI6482 Communications Infrastructure Digital Signal Processor* data manual (literature number <u>SPRS246</u>) has been updated to show this change. Revision B and late of the *TMS320TCI648x DSP DDR2 Memory Controller User's Guide* (literature number <u>SPRU894</u>) has been updated to reflect this change.

#### 2.1.13 EMAC: Gigabit Mode Cannot Be Used With CPU Running at Speeds Lower Than 750 MHz

The EMAC internal bus frequency must be greater than or equal to the I/O bus frequency. The EMAC internal bus is clocked by SYSCLK3 of the PLL1 controller, which has a frequency equal to the CPU frequency divided by 6. The I/O bus frequency of the EMAC is determined by the bit rate being used: 1.25 MHz for 10 Mbps, 12.5 MHz for 100 Mbps, and 125 MHz for 1000 Mbps. This restriction applies whether RGMII or GMII mode is being used.

Note that if the CPU speed is less than 750 MHz, the gigabit mode of the EMAC (1000 Mbps) cannot be used since the SYSCLK3 frequency will be less than 125 MHz.

### 2.1.14 DDR2 EMIF: Delay Before CKE Goes High With Different Combinations of REFRESH\_RATE and DDR Clock

The SDRAM refresh control register (SDRFC) contains a count value that is used for two purposes. At power up, it is used to control the delay before CKE goes high. Later, it is used to control the time between refreshes. The DDR2 JEDEC specification requires a 200 µs delay before CKE goes high during initialization. The calculation of the delay before CKE goes high involves the following: The default value for REFRESH\_RATE is 0x1388 at POR.

If the DDR clock period is set at 3.75 ns, the delay would be 16 \*  $(0x1388) / 266.666 = 300 \ \mu s$ . Users have to make sure that any time when the DDR2 is enabled, the delay before CKE goes high with different combinations of REFRESH\_RATE and DDR clock is always longer than 200  $\mu s$ . Table 4 lists a few typical calculated values (200- $\mu s$  delay).

| CLOCK PERIOD | REFRESH_RATE |

|--------------|--------------|

| 3.75 ns      | 0xD04        |

| 5 ns         | 0x9C4        |

| 8 ns         | 0x61A        |

#### Table 4. 200-µs Delay Calculated Values

During normal operation, the DDR memories require a refresh cycle at an average interval of 7.8125 µs (MAX). The calculation of RERESH\_RATE involves the following:

REFRESH\_RATE = DDR2CLKOUT frequency × memory refresh period

If the DDR clock period is set at 3.75 ns, the RERESH\_RATE would be:

REFRESH\_RATE = 266.666 MHz × 7.8125 µs = 2082 = 0x822.

Table 5 lists a few typical calculated values (an average interval of 7.8125 µs).

| CLOCK PERIOD | REFRESH_RATE |

|--------------|--------------|

| 3.75 ns      | 0x822        |

| 5 ns         | 0x61A        |

| 8 ns         | 0x3D0        |

If the DDR2 needs to be put into self-refresh mode or power-down mode, users need to write a new value to the REFRESH\_RATE field of the SDRFC register to guarantee the 200-µs delay of CKE during power-up or self-refresh mode exit.

#### 2.1.15 Manual Cache Coherence Operation

When an L1DWB, L1DWBINV, L2DWB, or L2DWBINV command is executed, and the writeback is complete, the C64x+ Megamodule sends a single 128-bit message with the address of the last word for that block operation. On the TCI6482 device, TI did not hook up this signal and, therefore, this looks like any other write command.

Because CPU-to-CPU transfers are not allowed in the connectivity of the SCR, the address is treated as an invalid address and the command is immediately terminated at the null-endpoint within the SCR and goes nowhere. There should be no effect at all to the system by this behavior.

Silicon Revision 3.1 Usage Notes and Known Design Exceptions to Functional Specifications

#### 2.1.16 AEA3 Must be Tied High with a 1-k $\Omega$ Resisitor if Power is Applied to the SRIO Supply Pins

The AEA3 pin must be pulled up at device reset using a 1-kΩ resistor if power is applied to the SRIO supply pins. Failure to do so may occur in L2 memory errors and Die-ID not being read correctly. If the SRIO peripheral is not used and the SRIO supply pins are connected to VSS, the AEA3 pin must be pulled down to VSS using a  $1-k\Omega$  resistor.

Silicon Revision 3.1 Usage Notes and Known Design Exceptions to Functional Specifications

www.ti.com

### 2.2 Silicon Revision 3.1 Known Design Exceptions to Functional Specifications

### Table 6. Silicon Revision 3.1 Advisory List

| Title                                                                                                                                         | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Advisory 3.1.1 — VCP2: Specific Parameter Combinations Generate Incorrect Results                                                             | 17   |

| Advisory 3.1.2 — VCP2 and TCP2: Emulator Access to TCP2 and VCP2 Registers Through EDMA Bus Return<br>Incorrect Results                       | 18   |

| Advisory 3.1.3 — EMAC: RMII Interface Cannot be Used in Half-Duplex Mode                                                                      | 21   |

| Advisory 3.1.4 — EMAC: RMCRSDV Signal is Asserted from the PHY Asynchronously and Can Cause Undefined<br>Behavior Internal to the RMII Module |      |

| Advisory 3.1.5 — EMAC: Signal Transitions on RMRXER are Ignored for Least Significant Di-Bit                                                  |      |

| Advisory 3.1.6 — EMAC: RMCRSDV Not Being Passed Asynchronously to the EMAC                                                                    |      |

| Advisory 3.1.7 — EMU: Emulation Prone to Failure Under Certain Situations                                                                     |      |

| Advisory 3.1.8 — McBSP: Emulation Access to McBSP Registers May Cause Sample Loss                                                             |      |

| Advisory 3.1.9 — SRIO: Using NREAD to Read Invalid Memory Space Causes a Timeout and Halts the Port that<br>Processed the NREAD Request       |      |

| Advisory 3.1.10 — L1D Cache: C64x+ L1D Cache May Lose Data or Hang DMA Operations Under Certain<br>Conditions                                 | 27   |

| Advisory 3.1.11 — McBSP: Transfers Less than 32 Bits are Ignored in Some Cases When Device is Configured for Big-Endian Mode                  | 28   |

| Advisory 3.1.12 — PCI: PCI Reset and Chip Reset Must Always Be Asserted Together                                                              | 29   |

| Advisory 3.1.13 — PCI: SRIO Max Reset Should Not Be Used When PCI is Used                                                                     |      |

| Advisory 3.1.14 — PCI: Device State Control Registers Should Not Be Used to Disable the PCI Once it is Enabled                                |      |

| Advisory 3.1.15 — Chip: Writing to Certain Peripheral Memory-Mapped Registers Will Modify Value of PRI_ALLOC Register.                        |      |

| Advisory 3.1.16 — SRIO: Performance Issues Identified Prohibiting Full Utilization of Pin Bandwidth                                           |      |

| Advisory 3.1.17 — CPU: Back-to-Back SPLOOPs With Interrupts Can Cause Incorrect Operation on C64x+ CPU                                        |      |

| Advisory 3.1.18 — CPU: C64x+ CPU Incorrectly Generates False Exceptions for Multiple Writes                                                   |      |

| Advisory 3.1.19 — SRIO: Packet Forwarding Cannot Be Used With NREAD Response Packets Greater Than 16<br>Bytes                                 |      |

| Advisory 3.1.20 — PLL Controller: GOSTAT Bit of PLL Controller Does Not Reflect GO Operation Status                                           | 40   |

| Advisory 3.1.21 — Potential SerDes Clocking Issue                                                                                             |      |

| Advisory 3.1.22 — EMIFA: Occurrence of Read Data Corruption for Synchronous Interface Due to Impedance                                        |      |

| Mismatch at AECLKOUT                                                                                                                          |      |

| Advisory 3.1.23 — DDR2 EMIF Buffers Not Totally Compensated by Default                                                                        | 45   |

| Advisory 3.1.24 — SRIO Port 0 Reset Affects Other Ports                                                                                       | 47   |

| Advisory 3.1.25 — SRIO OUTBOUND_ACKID Field Not Read Correctly                                                                                | 47   |

| Advisory 3.1.26 — PCI AC Timings Differ From Specifications                                                                                   | 48   |

| Advisory 3.1.27 — DMA Access to L2 SRAM May Stall When the DMA and the CPU Command Priority is Equal                                          | 50   |

| Advisory 3.1.29 — Potential McBSP Transmit Frame Corruption When XDATDLY = 0 and CLKX/FSX is Input Pin                                        |      |

| Driven By External Clock                                                                                                                      |      |

| Advisory 3.1.31 — SPLOOP CPU Cross-Path Stall                                                                                                 |      |

| Advisory 3.1.32 — DMA Corruption of L1D\$ Allocation                                                                                          |      |

| Advisory 3.1.33 — Error Detection and Correction Incorrectly Reporting Error                                                                  |      |

| Advisory 3.1.34 — SRIO May Fail to Send Interrupt for Completed TX or RX Message                                                              | 61   |

| www.ti.com            | Silicon Revision 3.1 Usage Notes and Known Design Exceptions to Functional Specifications |

|-----------------------|-------------------------------------------------------------------------------------------|

| Advisory 3.1.1        | VCP2: Specific Parameter Combinations Generate Incorrect Results                          |

| Revision(s) Affected: | 3.1 and earlier                                                                           |

| Details:              | Using the following parameter combinations with VCP2 and a constraint length of $K = 8$   |

will generate incorrect results on the TCI6482 device.

**TRACE-BACK MODE** Κ С R F 8 98 119 2557 Convergent 8 105 63 Convergent 120

> Note this advisory applies to convergent trace-back mode with K = 8 and these particular combinations of R, C and F. These may be used in some VoIP, HD radio, and radio network applications, but are not used in any 3-G wireless infrastructure standards.

Workaround(s): There is no workaround for this advisory.

| Advisory 3.1.2        | VCP2 and TCP2: Emulator Access to TCP2 and VCP2 Registers Through EDMA<br>Bus Return Incorrect Results                                                                                                                                                                                                                                                                                                                                     |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected: | 3.1 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Details:              | Some VCP2 and TCP2 registers are accessed either through the EDMA bus or through the configuration bus. Register access through the EDMA bus is only supported for 64-bit accesses.                                                                                                                                                                                                                                                        |  |

|                       | The emulation software (Code Composer Studio) accesses memory mapped registers (MMRs) via 32-bit accesses. Therefore, reading VCP2 and TCP2 registers through the EDMA bus results in the <i>odd word</i> accesses being returned as 0s.                                                                                                                                                                                                   |  |

| Workaround(s):        | There is no hardware workaround. In order to view these registers for debug purposes, a software workaround must be implemented.                                                                                                                                                                                                                                                                                                           |  |

|                       | One possible limited intrusive method would be to use an interrupt service routine (ISR) to access the registers and store them in a global structure. The ISR would not be executed during normal operations, but can be executed when desired through the use of a GEL script. Debugging would proceed as normal, except when it is desired to view the TCP2 and/or VCP2 registers.                                                      |  |

|                       | A GEL script can be written to generate an interrupt and, hence, execute the ISR. A breakpoint should be placed at the end of the ISR. After the ISR has completed execution, the data can be viewed in the global structure.                                                                                                                                                                                                              |  |

|                       | The ISR needs to access the registers with 64-bit accesses. This can be achieved with LDDWs to access two registers at a time or via DMA accesses. IDMA channel 0 is a good option for this, as it is fast and easy to set up. The setup of the ISR and mapping of interrupts is left up to the developer. The code segments shown in Example 1 through Example 3 are provided as examples to show how this workaround can be implemented. |  |

Example 1. Interrupt Service Routine Setup

```

interrupt TCP2_regDump_ISR(){

/* Code to copy DMA Based MMRs to Global Struct */

}

```

#### Example 2. Interrupt Initialization

```

void DoInterruptsInitialization()

{

CSL_IntcParam vectId1;

CSL_IntcGlobalEnableState state;

/* Setup the global Interrupt */

context.numEvtEntries = 1;

context.eventhandlerRecord = Record;

CSL_intcInit(&context);

/* Enable NMIs */

CSL_intcGlobalNmiEnable();

/* Enable Global Interrupts */

CSL_intcGlobalEnable(&state);

/* VectorID for the TCP2 Register Dump Event */

vectId1 = CSL_INTC_VECTID_4;

/* Opening a handle for the Global EDMA Event */

hIntcTcp2

= CSL_intcOpen( &intcTcp2,

CSL_INTC_EVENTID_##, // Event Driven By GEL

&vectId1,

NULL);

//Hook the ISRs

CSL_intcHookIsr(vectId1,& TCP2_regDump_ISR);

// Clear the Interrupt

CSL_intcHwControl(hIntcTcp2, CSL_INTC_CMD_EVTCLEAR, NULL);

//Enable the Event & the interrupt

CSL_intcHwControl(hIntcTcp2, CSL_INTC_CMD_EVTENABLE, NULL);

ipr[0] = 0xFFFFFFF;

ipr[1] = 0xFFFFFFF;

}

```

#### Example 3. GEL Script

```

/* GEL FILE

*/

#define EVENTSET0 0x01800020 // Event Set Register 0

#define EVENTSET1

0x01800024 // Event Set Register 1

#define EVENTSET2

0x01800028 // Event Set Register 2

#define EVENTSET3

0x0180002C // Event Set Register 3

StartUp()

{

/* Initialization portion of GEL File */

}

/*_____*/

/* TCP2 VCP2 Register Access

*/

/*-----*/

menuitem "TCP2VCP2RegAccess";

hotmenu TCP2RegAccess()

*(int *)EVENTSET0 = 0xXXXXXXX; // Only need to set one of these

*(int *)EVENTSET1 = 0xXXXXXXX; // corresponding to the event

*(int *)EVENTSET2 = 0xXXXXXXX; // used to trigger the ISR

*(int *)EVENTSET3 = 0xXXXXXXX;

GEL_GO(TCP2_regDump_ISR); /* Runs until TCP2_regDump_ISR function is called */

}

hotmenu VCP2RegAccess()

{

*(int *)EVENTSET0 = 0xXXXXXXX; // Only need to set one of these

*(int *)EVENTSET1 = 0xXXXXXXX; // corresponding to the event

*(int *)EVENTSET2 = 0xXXXXXXX; // used to trigger the ISR

*(int *)EVENTSET3 = 0xXXXXXXX;

GEL_GO(VCP2_regDump_ISR); /* Runs until VCP2_regDump_ISR function is called */

}

```

| www.ti.com            | Silicon Revision 3.1 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advisory 3.1.3        | EMAC: RMII Interface Cannot be Used in Half-Duplex Mode                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Revision(s) Affected: | 3.1 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Details:              | The RMII Ethernet MAC interface on TCI6482 cannot be used during normal operation in half-duplex mode. Only full-duplex mode is supported.                                                                                                                                                                                                                                                                                        |  |  |

|                       | It is anticipated that some RMII devices connecting to this device will initialize by default to half-duplex mode. This will still be allowed on TCI6482 given that the system negotiates to full-duplex mode immediately and a reset to the TCI6482 RMII is issued via the EMAC configuration register (EMACCFG). Note that this register and the ability to reset the RMII individually does not exist in silicon revision 1.1. |  |  |

| Workaround(s):        | No workaround exists for support of RMII in half-duplex mode.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                       | If half-duplex mode must be used, MII should be considered for connection to 10/100 Mbps devices and RGMII should be considered for 1 Gbps devices.                                                                                                                                                                                                                                                                               |  |  |

| Advisory 3.1.4        | EMAC: RMCRSDV Signal is Asserted from the PHY Asynchronously and Can<br>Cause Undefined Behavior Internal to the RMII Module                                                                                                                                                                                                                                                                                                      |  |  |

| Revision(s) Affected: | 3.1 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Details:              | The RMCRSDV input pin, used in the Ethernet MAC RMII interface, is susceptible to metastability due to the fact that it is not properly synchronized inside the device. Any activating transition on the RMCRSDV input may cause undefined behavior during EMAC RMII reception operation. This failure can result in lost frames.                                                                                                 |  |  |

| Workaround(s):        | The best way to eliminate the issue is to create a synchronized gating signal externally (based on the RMII reference clock) then AND that signal with the RMCRSDV input. Care must be taken as RMCRSDV also toggles at the end of frames.                                                                                                                                                                                        |  |  |

| Advisory 3.1.5        | EMAC: Signal Transitions on RMRXER are Ignored for Least Significant Di-Bit                                                                                                                                                                                                   |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 3.1 and earlier                                                                                                                                                                                                                                                               |  |  |

| Details:              | For RMII operation, if a pulse on RMRXER is driven during the least significant di-bit time, the pulse is ignored. This can result in corrupt receive frames that are not seen as erroneous data. This can cause errant frames to be seen as normal frames with corrupt data. |  |  |

| Workaround(s):        | This issue can be resolved in hardware by ORing a delayed version of RMRXER (previous di-bit) with the current RMRXER. Note that AC timing must still be met.                                                                                                                 |  |  |

| Advisory 3.1.6        | EMAC: RMCRSDV Not Being Passed Asynchronously to the EMAC                                                                                                                                                                                                                     |  |  |

| Revision(s) Affected: | 3.1 and earlier                                                                                                                                                                                                                                                               |  |  |

| Details:              | During RMII operation, RMCRSDV should be received asynchronously to the RMREFCLK and passed to the EMAC as CRS to minimize latency. However, this signal is being clocked internally which can cause a slight performance impact.                                             |  |  |

| Workaround(s):        | There is currently no workaround for this issue.                                                                                                                                                                                                                              |  |  |

| Advisory 3.1.7        | EMU: Emulation Prone to Failure Under Certain Situations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 3.1 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Details:              | Under certain conditions, the emulation hardware may corrupt the emulation control state<br>machine or may cause it to lose synchronization with the emulator software. When<br>emulation commands fail as a result of the problem, Code Composer Studio Integrated<br>Development Environment (IDE) may be unable to start or it may report errors when<br>interacting with the C64x+ DSP (for example, when halting the CPU, reaching a<br>breakpoint, etc.).                                                                                       |  |  |

|                       | This phenomenon is observed when an erroneous clock edge is generated from the TCK signal inside the C64x+ DSP. This can be caused by several factors, acting independently or cumulatively:                                                                                                                                                                                                                                                                                                                                                          |  |  |

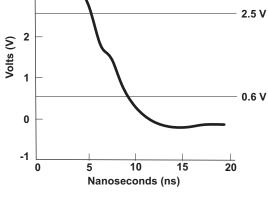

|                       | <ul> <li>TCK transition times (as measured between 2.5 V and 0.6 V) in excess of 3 ns.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                       | <ul> <li>Operating the C64x DSP in a socket, which can aggravate noise or glitches on the<br/>TCK input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                       | <ul> <li>Simultaneous switching EMU pins during trace can affect the TCK signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                       | <ul> <li>Poor signal integrity on the TCK line from reflections or other layout issues.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

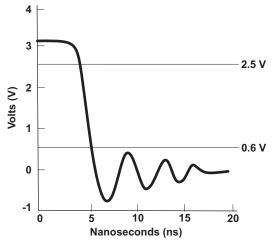

|                       | A TCK edge that can cause this problem might look similar to the one shown in Figure 3. A TCK edge that does not cause the problem will look similar to the one shown in Figure 4. The key difference between the two figures is that Figure 4 has a clean and sharp transition whereas Figure 3 has a "knee" in the transition zone. Problematic TCK signals may not have a knee that is as pronounced as the one in Figure 3. Due to the TCK signal amplification inside the chip, any perturbation of the signal can create erroneous clock edges. |  |  |

|                       | As a result of the faster edge transition, there is increased ringing in Figure 4. As long as the ringing does not cross logic input thresholds (0.6 V for falling edges, and 2.5 V for rising edges), this ringing is acceptable.                                                                                                                                                                                                                                                                                                                    |  |  |

|                       | When examining a TCK signal for this issue, either in board simulation or on an actual board, it is very important to probe the TCK line as close to the DSP input pin as possible. In simulation, it should not be difficult to probe right at the DSP input. For most physical boards, this means using the via for the TCK pad on the back side of the board. Similarly, ground for the probe should come from one of the nearby ground pad vias to minimize EMI noise picked up by the probe.                                                     |  |  |

|                       | 4<br>3<br>2<br>2<br>5<br>5<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>2<br>5<br>7<br>5<br>7                                                                                                                                                                                                                                                                                                                                                                 |  |  |

Figure 3. Bad TCK Transition

Figure 4. Good TCK Transition

## Workaround(s): As the problem may be caused by one or more of the above factors, one or more of the steps outlined below may be necessary to fix it:

- Avoid using a socket.

- Ensure that the board design achieves rise times and fall times of less than 3 ns with clean, monotonic edges for the TCK signal.

- For designs where TCK is supplied by the emulation pod, use an external buffer equal, or similar to, TI's CDCV304 on the TCK signal.

| www.ti.com            | Silicon Revision 3.1 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                         |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advisory 3.1.8        | McBSP: Emulation Access to McBSP Registers May Cause Sample Loss<br>. 3.1 and earlier                                                                                                                                                                                                                                                                                                                             |  |  |