# **Core Voltage Accumulation**

### ABSTRACT

This document provides a description of the issue referred to as " $V_{CORE}$  Accumulation", which impacts versions of the MSP430F543xA, MSP430F55xx, MSP430F550x, and CC430F61xx devices and their derivatives. This document also provides guidance in assessing whether the issue may affect a given application and to what extent.

### Topic

| 1 | Overview                                        | 2 |

|---|-------------------------------------------------|---|

| 2 | Affected Devices                                | 2 |

| 3 | Problem Description                             | 3 |

| 4 | How to Determine if the Application is Affected | 5 |

| 5 | Software Fix                                    | 7 |

| 6 | Summary                                         | 7 |

|   |                                                 |   |

### 1 Overview

Under specific conditions, the core voltage of the device,  $V_{CORE}$ , may rise incrementally until it is beyond 2.0 V, which is the maximum allowable limit for digital circuitry internal to the MSP430. This increase may remain undetected in an application with no functional impact but could potentially result in decreased endurance and increased wear over the lifetime of the device, because the digital circuitry is continually subjected to overvoltage.

The root cause of  $V_{CORE}$  accumulation is understood and the implementation of the fix is already in progress. Device revisions incorporating this fix are currently being processed.

However, for released devices that are affected by this issue, this document provides details on the issue and helps the user assess the potential impact. The document also addresses the means by which the issue can be avoided by making changes to the application flow.

### 2 Affected Devices

The list of affected devices in the MSP430F543xA, MSP430F550x, MSP430F55xx, and CC430F61xx are shown in Table 1.

| Family       | Device Derivatives | Lot Trace Code |

|--------------|--------------------|----------------|

|              | F5438A             |                |

|              | F5437A             |                |

| MSP430F543xA | F5435A             | < 18xxxxx      |

| W5P430F543XA | F5418A             | - < 10xxxxx    |

|              | F5419A             | -              |

|              | BT5190             |                |

|              | F5500              |                |

|              | F5501              |                |

|              | F5502              | -              |

|              | F5503              | -              |

|              | F5504              | -              |

| MSP430F550x  | F5505              | < 19xxxxx      |

|              | F5506              | 7              |

|              | F5507              |                |

|              | F5508              |                |

|              | F5509              | -              |

|              | F5510              |                |

|              | F5513              |                |

|              | F5514              |                |

|              | F5515              | -              |

|              | F5517              | -              |

|              | F5519              | -              |

|              | F5521              |                |

| MSP430F55xx  | F5522              | < 16xxxxx      |

|              | F5524              | -              |

|              | F5525              | -              |

|              | F5526              |                |

|              | F5527              | 1              |

|              | F5528              | 7              |

|              | F5529              |                |

### **Table 1. Affected Devices**

| www.ti.com |

|------------|

|            |

| Family       | Device Derivatives | Lot Trace Code                                  |

|--------------|--------------------|-------------------------------------------------|

|              | F5133              |                                                 |

|              | F5135              |                                                 |

|              | F5137              | -                                               |

| CC 420Ec1.w/ | F6125              | Affected revisions are shown in errata document |

| CC430F61xx   | F6126              | Anected revisions are shown in enata document   |

|              | F6127              |                                                 |

|              | F6135              |                                                 |

|              | F6137              |                                                 |

Table 1. Affected Devices (continued)

## 3 **Problem Description**

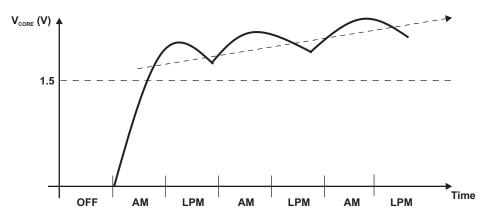

The core voltage can rise up to the voltage rail of the device  $DV_{DD}$  if the device is periodically switching between low power mode 2/3/4 (LPM) and active mode (AM) at a very high frequency.

## 3.1 Accumulation of Core Voltage and Prolongation

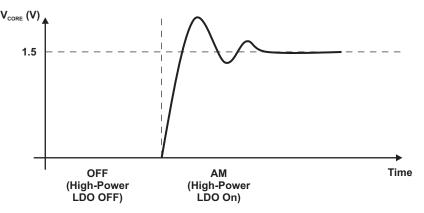

The core voltage that powers the digital domain of the MSP430 is generated internally by two DV<sub>DD</sub>-sourced LDOs that are a part of the Power Management Module (PMM). Depending on the power mode either the high-power LDO (AM, LPM0, LPM1) or the low-power LDO (LPM2, LPM3, LPM4) is used to source the core voltage. In LPMx.5 both LDOs as well as the core voltage is turned off.

The high-power LDO that generates the core voltage in AM, LPM0, and LPM1 is a regulator with a regulation time constant that is at least an order of magnitude larger than the minimum active time achievable by the MSP430 (greater than 2 µs).

Switching between active/LPM0/LPM1 and LPM2/3/4 causes the PMM to successively switch between the high-power and low-power LDOs. If this sequence occurs in short time intervals, the high-power LDO does not settle and there is a charge accumulation on the external capacitance connected to the  $V_{CORE}$  pin  $CV_{CORE}$  (470 nF). This results in an incremental increase in the core voltage until it is above the maximum allowable limit of 2.0 V.

Figure 2. Voltage Accumulation With Repeated Switching Between AM and LPM

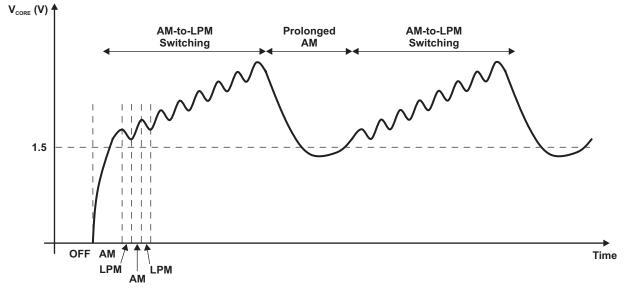

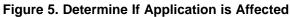

To prevent this effect, a prolongation mechanism is implemented in PMM that prolongs the active time of the PMM independent of the application. This prolongation mechanism is enabled by software at start up in the boot code. When switching at a high frequency, at every eighth instance of being in active mode, the PMM forces an active time of at least 1 VLO clock cycle to give the high-power LDO enough time to settle.

In affected devices, the prolongation mechanism that prevents the accumulation of  $V_{CORE}$ , is not enabled. This results in an increased core voltage under specific conditions as described in Section 3.2.

# 3.2 Susceptible Conditions for V<sub>CORE</sub> Accumulation

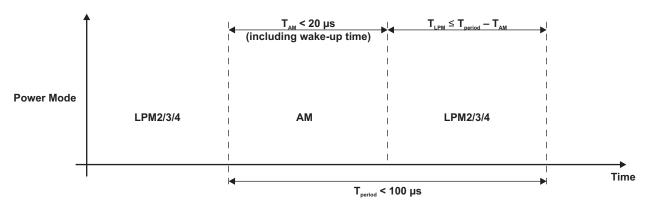

The effect of  $V_{CORE}$  accumulation can be seen when the device switches periodically between AM and LPM2/3/4 modes while remaining in both modes for very short time intervals. Figure 4 shows the timing budget window for which this effect can be seen:

#### www.ti.com

Figure 4. Conditions for Voltage Accumulation

From Figure 4, it can be seen that the device is required to be in active mode for a time period less than 20  $\mu$ s, contributing to a total time period of less than 100  $\mu$ s and limiting the time in LPM2/3/4 mode to less than or equal to 80  $\mu$ s. The minimum T<sub>AM</sub> includes the system wakeup time which is specified in the device datasheet as t<sub>wake-up-FAST</sub>.

Due to a maximum susceptible AM time of 20  $\mu s$ , only the  $t_{wake-up-FAST}$  configuration of PMM low side is affected. If the PMM low side is configured to operate in  $t_{wake-up-SLOW}$  (typically greater than 100  $\mu s$ ) the  $V_{CORE}$  accumulation would not occur.

# 3.3 Characteristics of V<sub>CORE</sub> Accumulation

The following list describes the impact of  $V_{\mbox{\scriptsize CORE}}$  accumulation:

- With shorter  $T_{AM}$  and  $T_{LPM}$ , the resulting  $V_{CORE}$  can increase up to  $DV_{DD}$ : In testing, typical seen value was  $T_{AM} = 4.5 \ \mu s$  and  $T_{LPM} = 30 \ \mu s$  (for  $V_{CORE} = DV_{DD}$ ).

- V<sub>CORE</sub> increases approximately 5 to 10 mV per LPM-to-AM transition

- The ratio between  $T_{\mbox{\tiny AM}}$  and  $T_{\mbox{\tiny LPM}}$  has no significant influence

- · The system frequency has no influence

- At lower temperatures, increased  $T_{AM}$  and  $T_{LPM}$  times are required to cause the issue

- If a nonstandard C<sub>VCORE</sub> (470 nF) is used, note that a smaller C<sub>VCORE</sub> reduces T<sub>AM</sub> and T<sub>LPM</sub> times.

# 3.4 System Effects of V<sub>CORE</sub> Accumulation

When the core voltage increases beyond expected values and up to  $\mathsf{DV}_{\mathsf{DD}}$ , the following effects can be observed:

- A short term effect of V<sub>CORE</sub> accumulation is seen as improper operation of the digital domain (CPU, Digital Peripherals). The device behavior is not predictable in this case.

- The long term effect of V<sub>CORE</sub> accumulation can cause reduced endurance of the digital domain over the life time of the device.

## 4 How to Determine if the Application is Affected

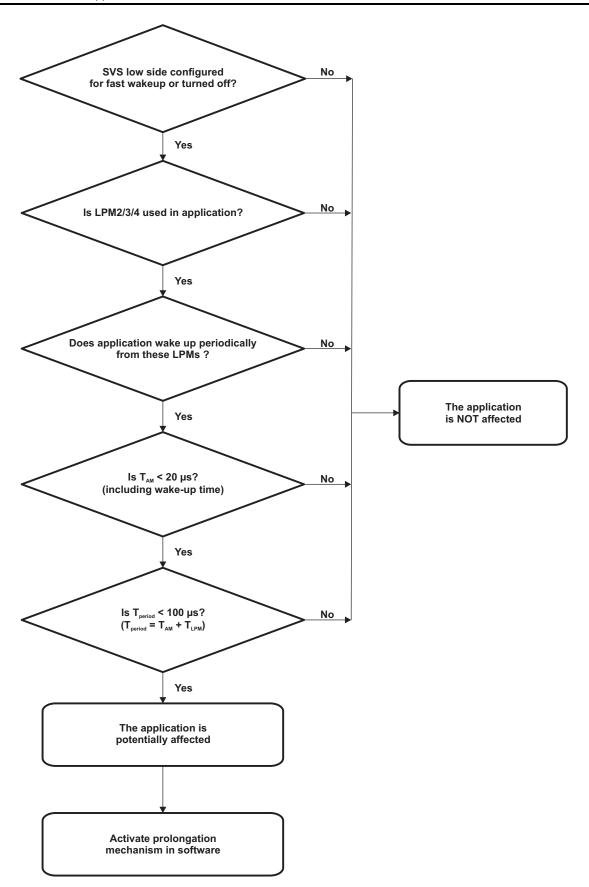

The flowchart in Figure 5 highlights specific areas to assess within a given application to determine if the conditions previously outlined are present:

How to Determine if the Application is Affected

www.ti.com

#### www.ti.com

### 5 Software Fix

The  $V_{CORE}$  accumulation is fixed by enabling the prolongation mechanism in software. The following lines of code need to be implemented before periodic execution of LPM-to-AM-LPM. It is recommended to execute the code at program start:

ASM code:

```

mov.w #0x9602, &0110h;

bis.w #0x0800, &0112h;

```

C code:

```

*(unsigned int*)(0x0110)=0x9602;

```

\*(unsigned int\*)(0x0112) =0x0800;

The automatic prolongation mechanism is disabled with a BOR and must be enabled after each boot code execution.

# 5.1 Effects of Active Prolongation Mechanism

The prolongation mechanism has no impact on startup, wakeup, or system response times. Because the prolongation mechanism keeps the high-power LDO in PMM enabled every eighth LPM-to-AM cycle for at least one VLO cycle, independent of application code execution, the average current consumption over eight LPM-to-AM cycles might be increased based on application timing budget.

Figure 6. Prolonged Active Time

During prolonged active time, the system is in quasi LPM2/3/4 but the high-power LDO remains active to regulate the  $V_{CORE}$  voltage level. The prolongation delay is triggered with every eighth LPM-to-AM transition and keeps the high-power LDO enabled for:

1 VLO cycle ×  $T_{Prol}$  < 2 VLO cycles

Depending on application code execution during the eighth AM, the prolonged active time can be 0  $\mu$ s. During prolonged active time, the system consumes 20  $\mu$ A to 40  $\mu$ A (typically 33  $\mu$ A) instead of the current specified in the device-specific data sheet for LPM2/3/4.

## 6 Summary

The information in this document provides the reader with information that can be applied in assessing the susceptibility of an application to the unintended accumulation of  $V_{CORE}$  voltage. A software solution is provided to fix the issue.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|  | Products               |                                 | Applications                  |                                   |

|--|------------------------|---------------------------------|-------------------------------|-----------------------------------|

|  | Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

|  | Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

|  | Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

|  | DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

|  | DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

|  | Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

|  | Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

|  | Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

|  | Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

|  | Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

|  | RFID                   | www.ti-rfid.com                 |                               |                                   |

|  | OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

|  | Wireless Connctivity   | www.ti.com/wirelessconnectivity |                               |                                   |

|  |                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated