# PORT17 Guidance

## ABSTRACT

CC430 erratum PORT17 describes the behavior of certain CC430 devices that can latch-up under specific conditions on the general-purpose I/O pins. This document described the conditions that cause the latch up, the affected devices and pins, and workarounds to prevent the latch up from occurring.

Due to the multiple factors that can cause the latch-up to occur, it is challenging to provide a single solution that fits all applications. The user is expected to analyze the requirements of each system and adapt a workaround or a combination of different steps to provide maximum robustness against latch-up.

|   | Contents                                             |   |  |  |

|---|------------------------------------------------------|---|--|--|

|   | Introduction                                         |   |  |  |

| 2 | Erratum: PORT17                                      | 2 |  |  |

| 3 | Affected Devices: CC430F613x and CC430F513x Families | 3 |  |  |

| 4 | Causes for Latch-up and Prevention                   | 5 |  |  |

|   | Summary                                              |   |  |  |

# List of Figures

| 1 | CC430F6137 RGC Package pinout showing an example of trigger pin and affected pins | 3 |

|---|-----------------------------------------------------------------------------------|---|

|   |                                                                                   |   |

## List of Tables

| 1 | CC430F61xx, CC430F51xx device pins that cause latch-up when subject to high current triggers                                                          | 4 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2 | CC430F61xx, CC430F51xx device pins that cause latch-up when subject to medium current triggers                                                        | 4 |

| 3 | CC430F61xx, CC430F51xx device pin that causes latch-up when subject to low current triggers                                                           | 5 |

| 4 | Bench test results at $V_{cc}$ = 3.6 V with holding current for different pins and the series resistance values above which latch-up is not sustained | 7 |

### 1 Introduction

Latch-up testing of CC430 devices uses tests based on the JEDEC standard JESD78C and includes a set of tests known as the I-Tests. These tests involve powering the device under test (DUT) and subjecting port pins to a trigger current that is polarized and characterized as per the test conditions mandated by the JEDEC standard. To pass the test, pins subject to the trigger current and any neighboring pins must not latch-up when a specific trigger current is applied.

For CC430 devices that are affected by PORT17 erratum, subjecting specific pins to the high negative trigger current can cause a latch-up to occur in the neighboring pins. The list of affected devices, the trigger currents required to cause the latch-up, and the specific pins that are affected are listed in the following sections. Note that while the pins are subject to high current pulses as a part of routine stress tests, these conditions are outside the absolute maximum rating for device operation. One possible situation where a device may undergo similar (but not identical) exposure to such conditions is in the case of an ESD event. It is important to understand that the occurrence of latch-up is unlikely and manifests only under special circumstances.

## 2 Erratum: PORT17

### Module: General-Purpose I/O

Function: Certain pins when subject to negative high current pulses may cause latch-up in adjacent pins.

#### **Description:**

Pins subject to negative high current pulses may cause latch-up in adjacent pins. The latch-up condition exists only if the adjacent pin configurations also referred to as 'affected-pin' configuration are one of the following:

- · GPIO input driven high by an external source

- GPIO output driven high with full drive strength or reduced drive strength settings

- Peripheral configuration where the peripheral drives pin high or causes pin to be driven high externally

The following affected-pin configurations do not sustain latch-up:

- GPIO input driven low

- GPIO output driven low

- Peripheral configuration where the peripheral drives pin low or causes pin to be driven low externally

- Peripheral configuration as LCD pin

Note that for affected-pin configurations with LCD functionality, the window of latch-up when the pin is driven being high still exists but is of extremely short duration and hence there is a low probability of latch-up occurrence.

#### Workaround:

All affected pins must be driven low when not in use. If the affected pins are not driven low, then connecting a series resistor of 330  $\Omega$  to limit the latch-up current is recommended.

**NOTE:** For CC430 devices that are affected by PORT17 erratum, only negative high current triggers can cause latch-up. Latch-up does not occur for any value of positive high current triggers.

INSTRUMENTS

Texas

www.ti.com

# 3 Affected Devices: CC430F613x and CC430F513x Families

The following devices in the CC430F613x and CC430F513x families are affected by PORT17 erratum.

CC430F6137 CC430F6135 CC430F6127 CC430F6126 CC430F6125 CC430F5137

CC430F5135

CC430F5133

# 3.1 Trigger Pins

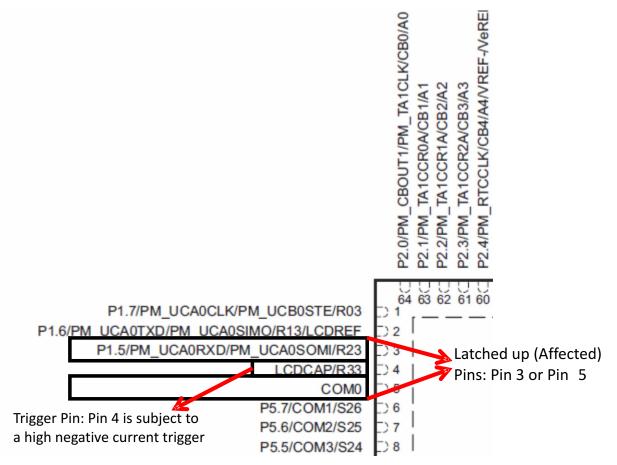

For devices affected by the erratum, the pins subjected to high trigger currents may cause latch-up in either one of the adjacent pins. For the remainder of this document, the pin under test that is subjected to the high negative current trigger pulse is referred to as the 'Trigger' pin, and pins that are latched-up due to the proximity to the Trigger pin are referred to as the 'Affected' pins. As an example, see Figure 1, which shows that when pin 4 (LCDCAP/R33) on the CC430F6137RGC device is subject to a high negative current trigger due to an ESD event, it may result in the latch-up of the pins on either side of pin 4; that is, pin 3 or pin 5. In this case, pin 4 is referred to a 'Trigger' pin and pins 3 and 5 are referred to as 'Affected' pins.

Figure 1. CC430F6137 RGC Package pinout showing an example of trigger pin and affected pins

Table 1, Table 2, and Table 3 list the Trigger pins that cause latch-up in one or both neighboring pins (referred to as the 'Affected' pins) for each package variant. The trigger current on the pin that is likely to cause latch-up is also highlighted. The tables are categorized as high, medium, and low trigger current categories based on the current required to cause a latch-up. Note that the affected pins need to have certain specific configurations to sustain the latch-up if it occurs. These configurations are explained in Section 4.1.

### 3.1.1 High-Current Triggers

The pins listed in Table 1 are categorized as low risk, because a very high trigger current is required to cause latch-up on an 'Affected' pin. The actual trigger current for each trigger pin that results in a latch-up is also listed.

| Table 1. CC430F61xx, CC430F51xx device pins that cause latch-up when subject to high current |

|----------------------------------------------------------------------------------------------|

| triggers                                                                                     |

| Affected Pin Terminal Name     | RGC Package Pin<br>Number | RGZ Package Pin<br>Number | Trigger Current |

|--------------------------------|---------------------------|---------------------------|-----------------|

| COM0                           | 5                         | Not Available             | -85 mA          |

| P1.4/PM_UCB0CLK/PM_UCA0STE/S22 | 12                        | 9                         | -110 mA         |

| P3.7/PM_SMCLK/S17              | 17                        | 14                        | -70 mA          |

| P3.6/PM_RFGDO1/S16             | 18                        | 15                        | -85 mA          |

| P3.2/PM_TA0CCR1A/S12           | 22                        | 19                        | -85 mA          |

| P4.7/S9                        | 26                        | Not Available             | -80 mA          |

| P4.2/S4                        | 31                        | Not Available             | -80 mA          |

| P4.0/S2                        | 33                        | Not Available             | -110 mA         |

### 3.1.2 Medium-Current Triggers

The pins listed in Table 2 are categorized as medium risk, because a trigger current in the range of - 25 mA to -35 mA is required to cause latch-up in an 'Affected' pin. The actual trigger current for each trigger pin that results in a latch-up is also listed.

| Table 2. CC430F61xx, CC430F51xx device pins that cause latch-up when subject to medium |  |  |  |  |

|----------------------------------------------------------------------------------------|--|--|--|--|

| current triggers                                                                       |  |  |  |  |

| Affected Pin Terminal Name      | RGC Package Pin<br>Number | RGZ Package Pin<br>Number | Trigger Current |  |

|---------------------------------|---------------------------|---------------------------|-----------------|--|

| P5.7/COM1/S26                   | 6                         | Not Available             | -25 mA          |  |

| P5.6/COM2/S25                   | 7                         | Not Available             | -35 mA          |  |

| P5.5/COM3/S24                   | 8                         | Not Available             | -35 mA          |  |

| P5.4/S23                        | 9                         | Not Available             | -35 mA          |  |

| P1.3/PM_UCB0SIMO/PM_UCB0SDA/S21 | 13                        | 10                        | -35 mA          |  |

| P1.2/PM_UCB0SOMI/PM_UCB0SCL/S20 | 14                        | 11                        | -35 mA          |  |

| P1.1/PM_RFGDO2/S19              | 15                        | 12                        | -35 mA          |  |

| P1.0/PM_RFGDO0/S18              | 16                        | 13                        | -35 mA          |  |

| P3.5/PM_TA0CCR4A/S15            | 19                        | 16                        | -25 mA          |  |

| P3.4/PM_TA0CCR3A/S14            | 20                        | 17                        | -25 mA          |  |

| P3.3/PM_TA0CCR2A/S13            | 21                        | 18                        | -25 mA          |  |

| P3.1/PM_TA0CCR0A/S11            | 23                        | 20                        | -25 mA          |  |

| P3.0/PM_CBOUT0/PM_TA0CLK/S10    | 24                        | 21                        | -25 mA          |  |

| P4.6/S8                         | 27                        | Not Available             | -25 mA          |  |

| P4.5/S7                         | 28                        | Not Available             | -25 mA          |  |

| P4.4/S6                         | 29                        | Not Available             | -25 mA          |  |

| P4.3/S5                         | 30                        | Not Available             | -25 mA          |  |

# Table 2. CC430F61xx, CC430F51xx device pins that cause latch-up when subject to medium current triggers (continued)

| Affected Pin Terminal Name | RGC Package Pin<br>Number | RGZ Package Pin<br>Number | Trigger Current |

|----------------------------|---------------------------|---------------------------|-----------------|

| P4.1/S3                    | 32                        | Not Available             | -25 mA          |

| P5.3/S1                    | 34                        | Not Available             | -35 mA          |

| P5.2/S0                    | 35                        | Not Available             | -25 mA          |

## 3.1.3 Low-Current Triggers

The pins listed in Table 3 are categorized as high risk, because a trigger current in the range of -15 mA can cause latch-up in an 'Affected' pin. The actual trigger current for each trigger pin that results in a latch-up is also listed.

# Table 3. CC430F61xx, CC430F51xx device pin that causes latch-up when subject to low current triggers

| Affected Pin Terminal Name | RGC Package Pin<br>Number | RGZ Package Pin<br>Number | Trigger Current |

|----------------------------|---------------------------|---------------------------|-----------------|

| LCDCAP/R33                 | 4                         | Not Available             | -15 mA          |

On CC430F513x (non-LCD) devices, this pin must be configured as a digital ground pin (DVSS) and, hence, is not affected by the erratum.

On CC430F613x devices that have the recommended 4.7-µF capacitor populated on the LCDCAP pin, the risk of current injection is very low, making this pin very unlikely to be affected by the erratum.

# 4 Causes for Latch-up and Prevention

In CMOS circuits, latch-up is caused by the creation of a parasitic silicon controlled rectifier (SCR). To sustain the latch-up, a minimum current is required to hold the latched SCR in the ON state. This minimum current level is known as the holding current. Hence a voltage pulse is required to trigger the SCR, and a holding current is required to sustain it.

On the CC430F613x devices and variants, the affected pins must be configured using specific settings that make it capable of sustaining the latch-up. These settings are described in the following sections.

There are two important factors to consider:

- To cause a latch-up, the affected pin needs to be driven high either internally or externally.

- The latch-up is sustained only as long as the V/I relationship (that is, the holding current) is maintained by the affected port pin.

Section 4.1 discusses the affected pin configurations that might result in a latch-up.

# 4.1 Affected Pin Configurations That Sustain Latch-up

Any of the following affected-pin configurations can sustain a latch-up if a neighboring Trigger pin is subject to a high negative current trigger:

• GPIO input driven high by an external source

In this case, the external current source that is used to drive the pin high must be capable of sustaining the latch-up. If the source is current-limited to below the holding current, then this prevents the latch-up from occurring.

• GPIO output driven high with Reduced Drive strength OR Full Drive strength settings

When any 'Affected' pins are driven high internally, they can latch-up when the trigger pin is subject to a high negative current. Driving a pin high internally is done by setting the PxDIR and PxOUT registers to 1.

As already mentioned a certain minimum amount of current, the holding current, is required to sustain the latch-up. The device's ability to supply this holding current when the affected pin is driven high

#### Causes for Latch-up and Prevention

www.ti.com

internally is directly dependent on the V/I characteristics of the pin. On the CC430F613x devices and variants, the GPIO pins have two configurable drive strength settings – full and reduced. When configured with the full drive strength setting the GPIO can sustain a high voltage level ( $V_{OH}$ ) with larger sink currents. This makes it more likely to sustain a latch-up condition. When the pin is driven high with a reduced drive strength setting, it may be on the margin of being able to sustain the holding current and latch-up may not occur.

The V/I relationship needs to be evaluated on a per-device basis and is specified in the data sheet in the *Schmitt Trigger Inputs-General Purpose I/O* section.

• Peripheral or module driving pin high or being driven high externally

This case would be similar to (1) and, if the module continually drives the pin high, it is possible that latch-up occurs.

Section 4.2 discusses the affected pin configurations that prevent or avoid latch-up.

# 4.2 Affected Pin Configurations That Avoid Latch-up

When affected pins are setup using any of the configurations described below, the pins cannot sustain a latch-up since the voltage needed to trigger the SCR is not available.

- GPIO input driven low

- GPIO output driven low

- Peripheral/ module driving pin low or being driven low externally

- Peripheral configuration as LCD pin: Typically pins configured as LCD segments pin are driven high for brief time intervals. The probability that a high negative current strike on a neighboring pin is synchronized with the high interval on the LCD pin is very low. Hence this configuration option will most likely avoid latch-up or the latch-up will not continue longer than one LCD period, since intermediate or low voltage levels will not sustain the holding current.

## 4.3 Recommendations to Prevent Latch-up

Any one of the following recommendations can be used to prevent latch-up of the affected pin:

- Use pin configurations provided in Section 4.2

- For affected pins driven high internally, use software to periodically drive the pin low, thereby interrupting a possible latch-up condition or reducing the window of probability for latch-up to occur.

- For affected pins driven high externally, ensure that the external source is current-limited to provide only less than the holding current (<15 mA).

- Use a resistance of at least 330 Ω in series with affected pins to ensure that the minimum holding current is not sustainable. See Section 4.3.1 for more details on how the series resistance value affects latch-up.

- Drive all unused pins low or tie to GND.

- When an affected pin is configured as a peripheral pin (other than as an LCD segment pin), pins not in use can be temporarily configured as a GPIO and driven low.

### 4.3.1 Using a Series Resistance to Prevent Latch-up

To test the minimum holding current required to sustain the latch-up, bench tests were performed on multiple CC430F6137 devices and the results are summarized in Table 4. It should be noted that temperature has an impact on the holding current, an increase in temperature results in a reduced holding current. Hence the measurements were made at three different temperatures 25C, 50C and 85C. When measuring the holding current a variable resistance was added in series to the affected GPIO to determine the maximum resistance at which latch-up is maintained. In other words, a higher resistance will render the latch-up condition unsustainable. Note that the data shown in Table 4 was collected across multiple units and different temperatures to provide a guidance estimate and must be regarded as such.

The results in Table 4 are sorted by temperature and three different trigger and affected-pin combinations are shown as examples.

www.ti.com

## Table 4. Bench test results at $V_{cc}$ = 3.6 V with holding current for different pins and the series resistance values above which latch-up is not sustained

| Temperature<br>(°C)                     | Series<br>Resistance<br>(Ω) | V <sub>pin</sub><br>(V) | Holding<br>Current, I <sub>pin</sub><br>(mA) |  |  |

|-----------------------------------------|-----------------------------|-------------------------|----------------------------------------------|--|--|

| Trigger Pin = LC                        | DCAP, Affected p            | in = COM0               | •                                            |  |  |

| 25                                      | 130                         | 1.3                     | 19                                           |  |  |

| 50                                      | 180                         | 1.2                     | 14                                           |  |  |

| 85                                      | 260                         | 1.1                     | 9                                            |  |  |

| Trigger Pin = P3.6, Affected Pin = P3.5 |                             |                         |                                              |  |  |

| 25                                      | 150                         | 1.4                     | 15                                           |  |  |

| 50                                      | 220                         | 1.3                     | 11                                           |  |  |

| 85                                      | 320                         | 1.1                     | 8                                            |  |  |

| Trigger Pin = P3.5, Affected Pin = P3.6 |                             |                         |                                              |  |  |

| 25                                      | 150                         | 1.4                     | 15                                           |  |  |

| 50                                      | 220                         | 1.3                     | 11                                           |  |  |

| 85                                      | 320                         | 1.1                     | 8                                            |  |  |

Based on bench test results we can reach the following conclusions:

- To prevent latch-up across the temperature range of the device (-40°C to 85°C) a series resistance in the order of 300 to 350 Ω is needed in series with the affected GPIOs. For temperature-restricted applications (at room temperature), this value can be reduced to 150 Ω or less.

- The current required to hold the latch-up can vary from approximately 8 mA to approximately 19 mA across the temperature range of the device. Note that the V<sub>pin</sub>/I<sub>pin</sub> relationship must be maintained by the affected pin to sustain the latch-up.

# 5 Summary

The occurrence of PORT17 can be minimized by ensuring that the affected pins are either configured in a manner as to avoid latch-up or by periodically changing the configuration to ensure that latch-up is not sustained. The most reliable method to avoid the occurrence of PORT17 is to prevent GPIOs from being subject to high negative current pulses (that is, prevent the occurrence of trigger currents on pins). This can be done by ensuring that the application is not subject to any condition that is outside of the device absolute maximum ratings and by undertaking proper ESD precautions. *MSP430 System-Level ESD Considerations* (SLAA530) gives a good overview on how to protect the device from ESD.

It must be noted that latch-up issues due to PORT17 are a rare occurrence and can only be brought about by a combination of both a high negative trigger current and specific affected pin configuration. Hence, it is reasonable to assume that the probability of being affected is low and is significantly reduced when following the recommendations provided in this document.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated