# Application Note Migration Guide From STM32<sup>®</sup> to Arm<sup>®</sup>-Based MSPM0

# ABSTRACT

This application note assists with migrating from the STMicroelectronics STM32<sup>®</sup> platform to the Texas Instruments MSPM0 MCU ecosystem. This guide introduces the MSPM0 development and tool ecosystem, core architecture, peripheral considerations, and software development kit. The intent is highlight the differences between the two families and to leverage existing knowledge of the STM32 ecosystem to quickly ramp with the MSPM0 series of MCUs.

# **Table of Contents**

| 1 MSPMU Portfolio Overview                             |    |

|--------------------------------------------------------|----|

| 1.1 Introduction                                       |    |

| 1.2 Portfolio Comparison of STM32 MCUs to MSPM0 MCUs   | 2  |

| 2 Ecosystem and Migration                              | 3  |

| 2.1 Software Ecosystem Comparison                      | 3  |

| 2.2 Hardware Ecosystem                                 | 4  |

| 2.3 Debug Tools                                        | 5  |

| 2.4 Migration Process                                  | 6  |

| 2.5 Migration and Porting Example                      |    |

| 3 Core Architecture Comparison                         | 15 |

| 3.1 CPU                                                |    |

| 3.2 Embedded Memory Comparison                         |    |

| 3.3 Power Up and Reset Summary and Comparison          |    |

| 3.4 Clocks Summary and Comparison                      |    |

| 3.5 MSPM0 Operating Modes Summary and Comparison       |    |

| 3.6 Interrupt and Events Comparison                    |    |

| 3.7 Debug and Programming Comparison                   | 24 |

| 4 Digital Peripheral Comparison                        |    |

| 4.1 General-Purpose I/O (GPIO, IOMUX)                  |    |

| 4.2 Universal Asynchronous Receiver-Transmitter (UART) |    |

| 4.3 Serial Peripheral Interface (SPI)                  |    |

| 4.4 l <sup>2</sup> C                                   |    |

| 4.5 Timers (TIMGx, TIMAx)                              |    |

| 4.6 Windowed Watchdog Timer (WWDT)                     |    |

| 4.7 Real-Time Clock (RTC)                              |    |

| 5 Analog Peripheral Comparison                         |    |

| 5.1 Analog-to-Digital Converter (ADC)                  |    |

| 5.2 Comparator (COMP)                                  |    |

| 5.3 Digital-to-Analog Converter (DAC)                  |    |

| 5.4 Operational Amplifier (OPA)                        |    |

| 5.5 Voltage References (VREF)                          |    |

| 6 Revision History                                     |    |

# Trademarks

MSP430<sup>™</sup>, TI E2E<sup>™</sup>, Code Composer Studio<sup>™</sup>, LaunchPad<sup>™</sup>, EnergyTrace<sup>™</sup>, and BoosterPack<sup>™</sup> are trademarks of Texas Instruments.

STM32<sup>®</sup> is a registered trademark of STMicroelectronics International N.V.

Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm Limited.

All trademarks are the property of their respective owners.

1

# 1 MSPM0 Portfolio Overview

# 1.1 Introduction

The MSP430<sup>™</sup> MCUs have nearly 30 years of history as TI's classic microcontroller. The latest generation introduces the MSPM0 family. MSPM0 microcontrollers (MCUs) are part of the MSP highly-integrated ultra-low-power 32-bit MCU family based on the enhanced Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit core platform. These cost-optimized MCUs offer high-performance analog peripheral integration, support extended temperature ranges, and offer small footprint packages. The TI MSPM0 family of low-power MCUs consists of devices with varying degrees of analog and digital integration allowing engineers to find the MCU that meets their project's needs. The MSPM0 MCU family combines the Arm Cortex-M0+ platform with a ultra-low-power system architecture, allowing system designers to increase performance while reducing energy consumption.

The MSPM0 MCUs offer a competitive alternative to the STM32 MCUs. This application note assists with migration from STM32 MCUs to MSPM0 MCUs by comparing device features and ecosystems.

| Table 1-1. Comparison of the TI MSPM0Gx/Lx and STM32G0/F0 Series |                                                                                                                       |                                                         |                                                                                                                                                        |                                                                |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

|                                                                  | ST Micro<br>STM32G0 Series                                                                                            | ST Micro<br>STM32F0 Series                              | TI MSPM0<br>MSPM0Gx Series                                                                                                                             | TI MSPM0<br>MSPM0Lx Series                                     |  |

| Core / Frequency                                                 | CM0+ / 64 MHz                                                                                                         | CM0 / 48 MHz                                            | CM0+ / 80 MHz                                                                                                                                          | CM0+ / 32 MHz                                                  |  |

| Supply Voltage                                                   | 1.7 V to 3.6 V                                                                                                        | 2 V to 3.6 V                                            | 1.62 V to 3.6 V                                                                                                                                        | 1.62 V to 3.6 V                                                |  |

| Temperature                                                      | -40°C to 125°C                                                                                                        | -40°C to 105°C                                          | -40°C to 125°C                                                                                                                                         | -40°C to 125°C                                                 |  |

| Memory                                                           | 512KB to 16KB                                                                                                         | 256KB to 16KB                                           | 128KB to 32KB                                                                                                                                          | 64KB to 8KB                                                    |  |

| RAM                                                              | Up to 144KB                                                                                                           | Up to 32KB                                              | Up to 32KB                                                                                                                                             | Up to 4KB                                                      |  |

| GPIO (max)                                                       | 90                                                                                                                    | 88                                                      | 60                                                                                                                                                     | 28                                                             |  |

| Analog                                                           | 1x 2.5-Msps 12-bit ADC<br>1x 12-bit DAC<br>3x comparators                                                             | 1x 1-Msps 12-bit ADC<br>1x 12-bit DAC<br>2x comparators | 2x 4-Msps 12-bit ADC<br>1x 12-bit DAC<br>3x high-speed<br>comparators<br>2x op amps                                                                    | 1x 1-Msps 12-bit ADC<br>1x high-speed comparator<br>2x op amps |  |

| Communication (max)                                              | 3x SPI2x SPI2x SPI3x I²C Fast+2x I²C Fast+2x I²C Fast+6x UART (LIN)8x UART (LIN)4x UART (LIN)2x CAN-FD1x CAN1x CAN-FD |                                                         | 2x I <sup>2</sup> C Fast+         2x I <sup>2</sup> C Fast+         1x           8x UART (LIN)         4x UART (LIN)         2x I <sup>2</sup> C Fast+ |                                                                |  |

| Timers                                                           | 8                                                                                                                     | 4                                                       | 7                                                                                                                                                      | 4                                                              |  |

| Advance Timers                                                   | Yes (1)                                                                                                               | Yes (1)                                                 | Yes (3x)                                                                                                                                               | No                                                             |  |

| Hardware Accelerator                                             | N/A                                                                                                                   | N/A                                                     | Optional                                                                                                                                               | N/A                                                            |  |

| Security                                                         | CRC, TRNG, AES256                                                                                                     | CRC                                                     | CRC, TRNG, AES256                                                                                                                                      | CRC                                                            |  |

| Low power                                                        | Active: 100 μA/MHz<br>Standby (RTC): 1.5 μA                                                                           | Active: 281 μA/MHz<br>Standby (RTC): 2.5 μA             | Active: 85 μA/MHz<br>Standby (RTC): 1.5 μA                                                                                                             | Active: 85 μA/MHz<br>Standby: 1.5 μA                           |  |

# 1.2 Portfolio Comparison of STM32 MCUs to MSPM0 MCUs

2

# 2 Ecosystem and Migration

MSPM0 MCUs are supported by an extensive hardware and software ecosystem with reference designs and code examples to get designs started quickly. MSPM0 MCUs are also supported by online resources, trainings with MSP Academy, and online support through the TI E2E<sup>™</sup> support forums.

# 2.1 Software Ecosystem Comparison

|                         | STM32          | MSPM0                                       |  |

|-------------------------|----------------|---------------------------------------------|--|

| IDE                     | CubeIDE        | Code Composer Studio <sup>™</sup> IDE (CCS) |  |

| Software Configuration  | CubeMX         | SysConfig                                   |  |

| Stand-alone programming | CubeProgrammer | UniFlash                                    |  |

| Display/Demo GUI Editor | CubeMonitor    | GuiComposer                                 |  |

#### 2.1.1 MSPM0 Software Development Kit (MSPM0 SDK)

The MSPM0 SDK delivers software APIs, examples, documentation, and libraries that help engineers quickly develop applications on Texas Instruments MSPM0+ microcontroller devices. Examples are provided to demonstrate the use of each functional area on every supported device and are a starting point for your own projects. Additionally, interactive MSP Academy trainings are included in the MSPM0 SDK to provide a guided learning path.

The examples folder is divided into RTOS and non-RTOS subfolders (currently only non-RTOS is supported). These folders contain examples for each LaunchPad<sup>™</sup> development kit and are organized categories such as lower-level DriverLib examples, higher-level TI Drivers examples, and examples for middleware such as GUI Composer, LIN, IQMath, and others. For details, refer to the *MSPM0 SDK User's Guide*.

### 2.1.2 CubeIDE vs Code Composer Studio IDE (CCS)

Code Composer Studio IDE (CCS) is TI's equivalent of STM32's CubeIDE. CCS is a free Eclipse-based IDE that supports TI's microcontroller (MCU) and embedded processor portfolios. CCS comprises a suite of tools used to develop and debug embedded applications including an optimizing C/C++ compiler, source code editor, project build environment, debugger, profiler and many other features. CCS is available as both a desktop or cloud-based IDE.

CCS integrates MSPM0 device configuration and auto-code generation from SysConfig as well as MSPM0 code examples and academy trainings in the integrated TI Resource explorer. CCS offers an all-in-one development tool experience.

In addition to CCS, MSPM0 devices are also supported in industry-standard IDEs listed in the following table.

| Table 2-2. WSPW0 Supported IDES |              |  |  |

|---------------------------------|--------------|--|--|

| IDE                             | MSPM0        |  |  |

| CCS                             | ✓            |  |  |

| IAR                             | ✓            |  |  |

| Keil                            | $\checkmark$ |  |  |

# Table 2-2. MSPM0 Supported IDEs

# 2.1.3 CubeMX vs SysConfig

SysConfig is an intuitive and comprehensive collection of graphical utilities for configuring pins, peripherals, radios, subsystems, and other components. It is TI's equivalent of STM32 CubeMX. SysConfig helps manage, expose, and resolve conflicts visually so that you have more time to create differentiated applications. The tool's output includes C header and code files that can be used with MSPM0 SDK examples or used to configure custom software. SysConfig is integrated into CCS but can also be used as a standalone program.

For details, refer to the MSPM0 SysConfig Guide.

3

|                   |                        | -                      |                     |

|-------------------|------------------------|------------------------|---------------------|

|                   | Welco                  | me To <b>SysConfig</b> |                     |

| ) Start a new De  | sign 🗇                 |                        |                     |

| Software Product: | MSPM0 SDK (0.46.00.03) |                        | ▼ Eq.               |

| Board:            | MSPM0G3507 LaunchPad   |                        | -                   |

| Device:           | MSPM0G350X             |                        | ~                   |

| Part:             | Default                |                        | Ŧ                   |

| Package:          | LQFP-64(PM)            |                        | $\overline{\nabla}$ |

|                   |                        | START                  |                     |

|                   |                        | START                  |                     |

| Open an Existir   | g Design               | BROWSE                 |                     |

| Open an Existir   |                        | BROWSE                 | î                   |

|                   |                        | _                      | î                   |

|                   |                        | BROWSE                 | ï                   |

#### Figure 2-1. MSPM0 SysConfig

# 2.2 Hardware Ecosystem

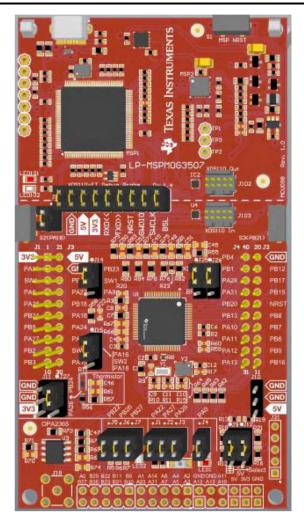

LaunchPad development kits are the only evaluation modules for the MSPM0. LaunchPad kits are easy-to-use EVMs that contain everything needed to start developing on the MSPM0. This includes an onboard debug probe for programming, debugging, and measuring power consumption with EnergyTrace<sup>™</sup> technology. MSPM0 LaunchPad kits also feature onboard buttons, LEDs, and temperature sensors among other circuitry. Rapid prototyping is simplified by the 40-pin BoosterPack<sup>™</sup> plug-in module headers, which support a wide range of available BoosterPack plug-in modules. You can quickly add features like wireless connectivity, graphical displays, environmental sensing, and more.

- LP-MSPM0G3507 LaunchPad development kit

- LP-MSPM0L1306 LaunchPad development kit

Figure 2-2. LP-MSPM0G3507 LaunchPad Development Kit

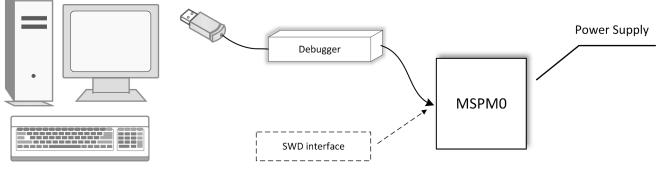

# 2.3 Debug Tools

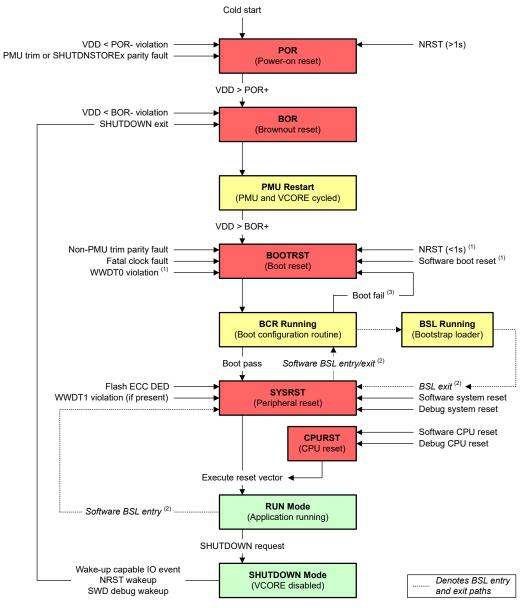

The debug subsystem (DEBUGSS) interfaces the serial wire debug (SWD) two-wire physical interface to multiple debug functions within the device. MSPM0 devices support debugging of processor execution, the device state, and the power state (using EnergyTrace technology). Figure 2-3 shows the connection of the debugger.

MSPM0 support XDS110 and J-Link debugger for standard serial wire debug.

The Texas Instruments XDS110 is designed for TI embedded processors. XDS110 connects to the target board through a TI 20-pin connector (with multiple adapters for TI 14-pin and Arm 10-pin and Arm 20-pin) and to the host PC through USB2.0 High Speed (480 Mbps). It supports a wider variety of standards (IEEE1149.1, IEEE1149.7, SWD) in a single pod. All XDS debug probes support Core and System Trace in all Arm and DSP processors that feature an Embedded Trace Buffer (ETB). For details, refer to XDS110 Debug Probe.

J-Link debug probes are the most popular choice for optimizing the debugging and flash programming experience. Benefit from record-breaking flash loaders, up to 3-MiB/s RAM download speed and the ability to set an unlimited number of breakpoints in the flash memory of MCUs. J-Link also supports a wide range of CPUs and architectures included CortexM0+. For details, visit the Segger J-Link Debug Probes page.

Figure 2-3 shows a high-level diagram of the major functional areas and interfaces of the XDS110 probe to MSPM0 target.

5

Ecosystem and Migration

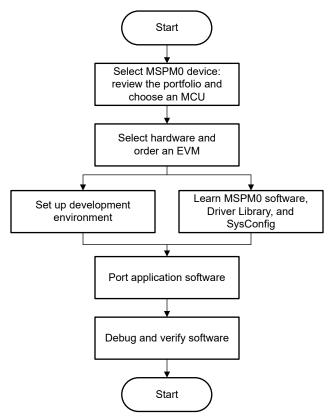

# 2.4 Migration Process

The first step in migrating is to review the portfolio and choose the best MSPM0 MCU. After an MSPM0 MCU has been selected, choose a development kit. Development kits include a LaunchPad kit available for purchase and design files for a Target-Socket Board. TI also provides a free MSPM0 Software Development Kit (SDK), which is available as a component of Code Composer Studio IDE desktop and cloud version within the TI Resource Explorer. Use the peripheral sections of this application note for help with porting software from STM32 to MSPM0. Finally, once the software ported, download and debug the application with our debugging tools.

Figure 2-4. MSPM0 Migration Flowchart

# 2.5 Migration and Porting Example

To become more familiar with the TI ecosystem and explain how to best get started with MSPM0, this section describes the step-by-step migration process of a basic application.

To demonstrate the process of porting from STM32 to MSPM0, this description includes the steps to port a basic low-power UART monitor application from an STM32G0x to a MSPM0 device using an existing ST UART example as the starting point.

# Step 1. Chose the right MSPM0 MCU

The first step of migration is to choose the correct MSPM0 device for the application. To do this, the portfolio section of this guide can be used to choose a MSPM0 family. To narrow down to a specific device using the product selection tool. STM32G0 and MSPM0 share the M0+ core, but features such as memory size, power, and key peripherals must also be considered. MSPM0 also offers many pin-to-pin scalable options, providing the ability to easily scale to larger or smaller memory devices without changing anything else in the system.

For purposes of this example, we have chosen the MSPM0G3507 as the best fit for his application.

### Step 2. Select hardware and order an EVM

Using an evaluation module (EVM) can expedite the migration process. For the MSPM0 MCUs, a LaunchPad kit is the easiest hardware to begin on. LaunchPad kits are easy to use because they come with a built-in programmer and are designed to enable rapid development.

The MSPM0G3507 has a LaunchPad development kit (LP-MSPM0G3507) that can be used for porting the software.

### Step 3. Setup software IDE and SDK

Before the software can be ported, a software development environment must be chosen and setup. Section 2.1 shows all of the IDEs supported by MSPM0. The migration and porting process is similar for any IDE that is chosen. The latest version of the MSPM0 SDK should be used.

For this example, TI's CCS is the chosen IDE.

Figure 2-5. Code Composer Studio IDE

# Step 4. Software porting

When the environment is ready, start using the MSPM0 SDK. As mentioned, the MSPM0 SDK is similar to the STM32Cube software package. The MSPM0 SDK offers different layers for software development. MSPM0 TI Drivers operate at a similar level to STM32Cube HAL, while MSPM0 DriverLib is comparable to the STM32Cube low-level drivers. Most MSPM0 users find DriverLib level software is the best fit for their applications, so most MSPM0 software examples are also DriverLib based. This example uses DriverLib.

One option when porting a project is to try to replace each section of code with equivalent MSPM0 DriverLib APIs, but this is not generally the easiest path. Generally, it is best to first understand the application code being ported. Then start with the closest MSPM0 example project and modify it to match the original code functionality. This process is going to be shown below using a low-power UART example from STM32CubeG0. For more complex projects using many peripherals, this process is typically repeated for each peripheral.

7

# Step 4a: Understand the application

# The following description is from the example project from STM32CubeG0 named 'LPUART\_WakeUpFromStop\_Init'.

@par Example Description

```

Configuration of GPIO and LPUART peripherals to allow characters received on LPUART RX pin to

wake up the MCU from low-power mode. This example is based on the LPUART LL API. The peripheral

initialization uses LL initialization function to demonstrate LL init usage.

LPUART Peripheral is configured in asynchronous mode (9600 bauds, 8 data bit, 1 start bit, 1 stop

bit, no parity).

No HW flow control is used.

LPUART Clock is based on HSI.

Example execution:

After startup from reset and system configuration, LED3 is blinking quickly during 3 sec, then MCU

enters "Stop 0" mode (LED3 off). On first character reception by the LPUART from PC Com port (ex:

using HyperTerminal) after "Stop 0" Mode period, MCU wakes up from "Stop 0" Mode.

Received character value is checked :

- On a specific value ('S' or 's'), LED3 is turned On and program ends.

- If different from 'S' or 's', program performs a quick LED3 blinks during 3 sec and enters

again "Stop 0" mode, waiting for next character to wake up.

```

The first step is to understand the main settings for the MCU. This is generally clock speeds and power policies. In this example, the general clock frequency is not specified because the only important setting is that the UART works in low power Stop0 mode. It states the low power UART clock is based on the 'HIS' or high-speed internal oscillator meaning there is no external crystal being used. The UART runs at 9600 baud, 8 data bits, 1 start and stop bit, no parity. No hardware flow control is used. The application side checks for an 'S' or 's' to be received and blinks an LED.

#### Step 4b: Find the closest MSPM0 example

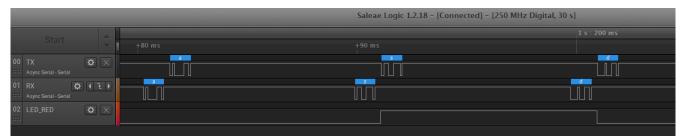

Next step is to understand any differences between the UART modules for STM32G0 and MSPM0 and then find the closest example in the MSPM0 SDK. This is easily accomplished by referring to the UART section in Section 4. This section highlights differences between the UART modules and links to the UART-related MSPM0 SDK code examples. The closest example in the SDK for this example is probably uart\_echo\_interrupts\_standby where the "UART RX/TX echos using interrupts while device is in STANDBY mode".

This MSPM0 example is similar, but not identical to the being ported. This example is going to standby mode, which is a lower power mode than Stop mode. The UART communication settings must be checked as well as which GPIOs are being used. Finally, the application layer of monitoring for a specific character must be added.

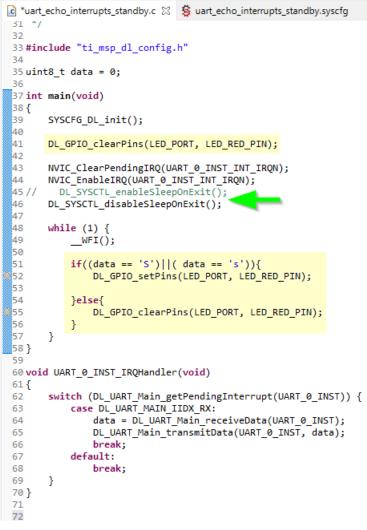

#### Step 4c: Import and modify the example

Once a similar example is found, Open CCS and import the code example by going to **Project > Import CCS Projects...** and navigate it to the MSPM0 SDK example folder. Import the example. Here is the *uart\_echo\_interrupts\_standby* example imported. This is a SysConfig project, so the main C file is simple. It first calls the SysConfig driverlib initialization which is a function autogenerated by SysConfig to configures the device. Then it enables the UART interrupt. Finally it goes to sleep waiting for any UART transaction. If it receives a UART transaction, it echos the data right back and wakes up.

| 😚 Panasonic_Intro - uart_echo_interrupts_standby_LP_MSPM0G3507_nortos_ticlang/uart_echo_interrupts_standby.c - Code Composer Studio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - |   | ×  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|

| File Edit View Navigate Project Run Scripts Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |   |    |

| : C1 ▼ □□ □ □ : □ : □ : □ : □ : □ : ○ : ◇ · · ○ : ○ : ○ : ○ : ○ : ○ : ○ : ○ : ○ :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q | 8 | *⊳ |

| Project Explorer 🛛 🔲 😫 🏹 🖇 🧮 🗋 🗋 uart_echo_interrupts_standby.c 🕅                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |    |

| <pre>v @ uart_echo_interrupts_standby_LP_MSPM0G3507 v @ Generated Source v @ ledude v @ contended Source v @ contended Sour</pre> |   |   | *  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | > |    |

| Writable Smart Insert 31:4:1613                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |   | 1  |

Figure 2-6. uart\_echo\_interrupts\_standby Example

To see the SysConfig configuration, open the .syscfg file, which opens on the SYSCTL tab by default. For detailed guide on using SysConfig, see the SysConfig Guide in the in the MSPM0 SDK.

The first thing to note is the power policy. This MSPM0 example is using Standby0 mode but the goal is to use Stop0 mode. By clicking the drop-down list, the correct low-power mode can be chosen. All of the clocks and oscillators can be configured on this tab as well, but are fine for now.

| y ua | rt_echo_interrupts_standby.syscfg 🔀          |                                                              |                  | - I                                   |

|------|----------------------------------------------|--------------------------------------------------------------|------------------|---------------------------------------|

|      | ╤ Type Filter Text 🗙 ≪                       | $\leftrightarrow$ $\rightarrow$ Software $ ightarrow$ SYSCTL |                  | (j <> 🏟 🕓 …                           |

| 82   | <ul> <li>MSPM0 DRIVER LIBRARY (7)</li> </ul> | SYSCTL                                                       |                  | ⊕ ADD TREMOVE ALL                     |

|      | <ul> <li>SYSTEM (8)</li> </ul>               |                                                              |                  |                                       |

|      | Board 1/1 🥑 🕀                                | Power & Systems Configuration                                |                  | ~                                     |

|      | DMA 🕀                                        |                                                              |                  |                                       |

|      | GPIO                                         | Power Policy @                                               | STANDBYO         |                                       |

|      | MATHACL                                      | BOR Threshold                                                | SLEEP0           | *                                     |

|      | RTC 🕀<br>SYSCTL 1/1 🔮 🕀                      | Enable Write Lock                                            | SLEEP1<br>SLEEP2 |                                       |

|      | SYSTICK 🕀                                    | Enable Sleep On Exit                                         | STOP0            |                                       |

|      | WWDT (+)                                     | Enable Event on Pending                                      | STOP1            |                                       |

|      | ✓ ANALOG (5)                                 |                                                              | STOP2            |                                       |

|      | ADC12                                        | FCC Configuration                                            | STANDBYO         | $\checkmark$                          |

|      | COMP (+)                                     | Enable FCC                                                   | STANDBY1         |                                       |

|      | DAC12                                        |                                                              |                  |                                       |

|      | OPA 🕀                                        | Fleeb Controller (FleebOth Configuration                     |                  | ^                                     |

|      | VREF $\stackrel{\smile}{\oplus}$             | Flash Controller (FlashCtl) Configuration                    |                  | ^                                     |

|      | ✓ COMMUNICATIONS (5)                         | Deven & Overhamer Internet                                   |                  |                                       |

|      | 12C 🕀                                        | Power & Systems Interrupts                                   |                  | ^                                     |

|      | MCAN 🕀                                       |                                                              |                  |                                       |

|      | SPI 🕀                                        | Clock Configuration                                          |                  | ~                                     |

|      | UART 1/4 🔮 🕀                                 |                                                              |                  |                                       |

|      | UART - LIN 🕀                                 | Enable Check for Clock Stabilization                         |                  |                                       |

|      | ✓ TIMERS (4)                                 | MCLK (Main Clock)                                            |                  | ~                                     |

|      | TIMER                                        |                                                              |                  |                                       |

|      | TIMER - CAPTURE                              | MCLK Source                                                  | SYSOSC           | Ψ                                     |

|      | TIMER - PWM                                  | Main Clock Divider                                           | 1                | Ŧ                                     |

|      | TIMER - QEI<br>SECURITY (2)                  |                                                              |                  |                                       |

|      | AES (+)                                      | MFCLK (Middle Frequency Clock)                               |                  | ^                                     |

|      | TRNG                                         |                                                              |                  |                                       |

|      | ✓ DATA INTEGRITY (1)                         | LFCLK (Low-Frequency Clock)                                  |                  | ~                                     |

|      | CRC                                          | LEOLI Courses                                                | 15050            | _                                     |

|      | ✓ READ-ONLY (1)                              | LFCLK Source                                                 | LFOSC            | · · · · · · · · · · · · · · · · · · · |

|      | EVENT 🕀                                      | MFPCLK (Middle Frequency Precision Clock)                    |                  | ^                                     |

|      |                                              | ULPCLK (Low Power Clock)                                     |                  | ~                                     |

|      |                                              | ULPCLK Divider                                               | 1                | · · · · · · · · · · · · · · · · · · · |

|      |                                              | HFCLK (High-Frequency External Clock)                        |                  | ^                                     |

|      |                                              | External Clock Output (CLK_OUT)                              |                  | ^                                     |

|      |                                              | Internal Oscillators                                         |                  | ^                                     |

|      |                                              | External Oscillators                                         |                  | ^                                     |

|      |                                              | Clock Interrupts                                             |                  | ~                                     |

|      |                                              | Enable Interrupts                                            | None             | *                                     |

# Figure 2-7. Power Mode Configuration

Next, check the UART communication settings on the UART tab (see Figure 2-8). In this case, the baud rate is already set to 9600 and the rest of communication settings are correct. The receive interrupt is already enabled and used in the main program. Also check the UART module and pins being used by clicking the chip icon in the top right and checking the highlighted pins for the UART. Nothing here needs to be changed as these are already connected to the MSPM0G3507 LaunchPad kit's backchannel UART.

| 💲 uar | t_echo_interrupts_standby.s                                                    | syscfg 🛛                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            |                                                                                                           |          |                                                                                                                                  |                                                                                              |               | - 0              |

|-------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|------------------|

|       | Ţ Type Filter Text                                                             | $\times \ll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\leftrightarrow$ $\rightarrow$ Software $ ightarrow$ UART |                                                                                                           |          |                                                                                                                                  | (                                                                                            | i 🗘 👜         | •••              |

| =     | <ul> <li>MSPM0 DRIVER LIBRARY</li> <li>SYSTEM (8)</li> <li>Board 1.</li> </ul> | (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | UART (1 of 4 Added) ⊙                                      | (⊕ ADD ) = REMO                                                                                           | VE ALL   | < > Generated Files<br>Filter: all                                                                                               |                                                                                              | 1             | 2 <sup>7</sup> × |

|       | DMA                                                                            | Ð                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Name                                                       | UART_0                                                                                                    |          | File name                                                                                                                        | Category                                                                                     | Include in bu | ild              |

|       | GPIO<br>MATHACL<br>RTC                                                         | (†)<br>(†)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Selected Peripheral                                        | UARTO                                                                                                     |          | ti_msp_dl_config.c                                                                                                               | MSPM0<br>Driver Library                                                                      |               |                  |

|       | SYSTICK                                                                        | /1 ♥ ⊕<br>⊕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Quick Profiles                                             | Custom                                                                                                    | ¥<br>•   | ti_msp_dl_config.h                                                                                                               | MSPM0<br>Driver Library                                                                      | -             |                  |

|       | WWDT<br>ANALOG (5)                                                             | <ul> <li>(1)</li> <li>(2)</li> <li>(3)</li> <li>(4)</li> <li>(4)</li> <li>(5)</li> <li>(4)</li> <li>(5)</li> <li>(5)</li> <li>(6)</li> <li>(6)</li> <li>(7)</li> <li>(7)</li></ul> | Basic Configuration                                        |                                                                                                           | -        | uart_echo_interrupts_standby.syscfg                                                                                              | Configuration<br>Script                                                                      |               |                  |

|       | ADC12<br>COMP<br>DAC12                                                         | (†)<br>(†)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UART Initialization Configuration                          |                                                                                                           |          | 3 Total Files                                                                                                                    |                                                                                              |               | _                |

|       | OPA<br>VREF                                                                    | $( \div )$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clock Source                                               | LFCLK                                                                                                     | Ť        | MSPM0G350X<br>(Device)<br>LQFP-64(PM)                                                                                            |                                                                                              |               | ζ <sup>π</sup> × |

|       | <ul> <li>COMMUNICATIONS (5)</li> <li>I2C</li> </ul>                            | $\oplus$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clock Divider                                              | Divide by 1                                                                                               | •<br>•   | (Package)                                                                                                                        |                                                                                              |               |                  |

|       | MCAN<br>SPI                                                                    | ( <del>)</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Calculated Clock Source<br>Target Baud Rate                | 32768<br>9600                                                                                             |          | SWITCH                                                                                                                           |                                                                                              |               |                  |

|       | UART 1.<br>UART - LIN                                                          | /4 ♥ ⊕<br>⊕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Calculated Baud Rate                                       | 9576.04                                                                                                   | - I      | ₩+₩¥¥¥₩₩₩<br>₩+₩¥₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩                                                                                       | 32                                                                                           |               |                  |

|       | <ul> <li>TIMERS (4)</li> <li>TIMER</li> <li>TIMER - CAPTURE</li> </ul>         | ( <del>)</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Calculated Error (%)                                       | 0.2496<br>Using 3x oversampling with LFCLK<br>result in significant deviation in the<br>actual baud rate. | can      | 49<br>50<br>51<br>52 Pin Assigned<br>53 Warning<br>54 Warning<br>56 Ground<br>57 Fixed (N/A)<br>58<br>60<br>61<br>62<br>63<br>64 | 32<br>31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>19<br>18 |               |                  |