# Application Brief **TPS7H1111-SP Pin Failure Mode Analysis (FMA)**

This application brief provides a *Failure Mode Analysis* (FMA) for the pins of the TPS7H1111-SP ultra-low noise, high PSRR, LDO. The failure conditions covered in this document include the typical pin-by-pin failure scenarios:

- Pin short-circuited to ground (see Table 1)

- Pin short-circuited to V<sub>IN</sub> supply (see Table 2)

- Pin short-circuited to V<sub>OUT</sub> supply (see Table 3)

- Pin open-circuited (see Table 4)

- Pin short-circuited to an adjacent pin (see Table 5)

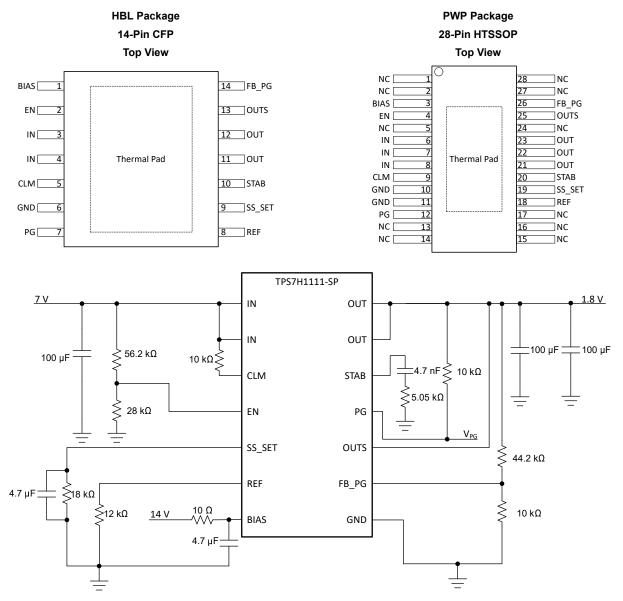

In the tables below, *damage* means there is a possibility of immediate device damage, gradual device damage, or lifetime reductions. It only encompasses damage of the device itself, not upstream or downstream components. *Functional* means the device as a whole behaves as described in the data sheet (although this does not necessarily mean the device is regulating). This analysis was considered for the schematic shown in Figure 3 with a resistive 0.5-A load. See comments in the tables below for details on each situation.

This analysis was considered primarily for the ceramic HBL 14-pin package of the TPS7H1111-SP device. However, most results are also applicable for the plastic PWP 28-pin package of the TPS7H1111-SP and TPS7H1111-SEP devices.

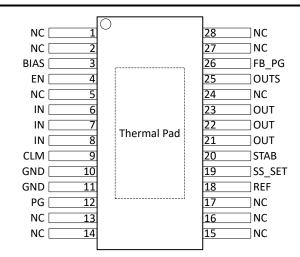

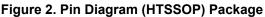

Figure 1 and Figure 2 show the TPS7H1111-SP pin diagrams for the CFP and HTSSOP packages. For a detailed description of the device pins, see the *Pin Configuration and Functions* section in the TPS7H1111-SP data sheet.

Figure 1. Pin Diagram (CFP) Package

1

| Pin Name | Pin No. | Damage | Functional                                                                                                                                                                                                                                                                                                                                                                                | Description of Potential Failure Effects                                                                                                                                                                                                                                                                                                                                                 |  |  |

|----------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BIAS     | 1       | No     | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Device turns off (enters UVLO).                                                                                                                                                                                                                                                                                                                                                          |  |  |

| EN       | 2       | No     | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Device turns off (disabled).                                                                                                                                                                                                                                                                                                                                                             |  |  |

| IN       | 3       | Yes    | Yes                                                                                                                                                                                                                                                                                                                                                                                       | If both IN pins are shorted, the device is below internal UVLO and                                                                                                                                                                                                                                                                                                                       |  |  |

| IN       | 4       | Yes    | Yes                                                                                                                                                                                                                                                                                                                                                                                       | therefore turns off. If only one is shorted there will be a potentially damaging overcurrent event between the two pins.                                                                                                                                                                                                                                                                 |  |  |

| CLM      | 5       | No     | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Normal operation – device configured for turn-off current limit mode. If CLM was previously connected directly to V <sub>IN</sub> when the short to ground occurs, a short circuit could result, potentially causing damage. As the schematic shows a 10 k $\Omega$ pull-up to V <sub>IN</sub> , damage is not expected.                                                                 |  |  |

| GND      | 6       | N/A    | N/A                                                                                                                                                                                                                                                                                                                                                                                       | N/A                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PG       | 7       | No     | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Pin remains at 0 V since it is an open-drain pin and doesn't have an internal pull-up voltage.                                                                                                                                                                                                                                                                                           |  |  |

| REF      | 8       | Yes    | No                                                                                                                                                                                                                                                                                                                                                                                        | An overcurrent event occurs on the REF pin that could cause damage.<br>Additionally, this may cause improper biasing in other circuits which could<br>cause other failures.                                                                                                                                                                                                              |  |  |

| SS_SET   | 9       | No     | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Device regulates to 0 V output. If FB_PG falls below $V_{FB_PG(rising)} - V_{FB_PG(HYS)}$ , the 2-mA current will turn-on and flow out of this SS_SET pin.                                                                                                                                                                                                                               |  |  |

| STAB     | 10      | No     | No The pass element turns-on which could cause entering of currer<br>or the output to rise above the programmed SS_SET value. Wh<br>device damage isn't expected, downstream circuitry may be da<br>Damage would be expected if this short occurred while the dev<br>powered but disabled as STAB is internally driven high. This wo<br>excessive current on STAB which may cause damage. |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| OUT      | 11      | Yes    | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Short circuit protection activated to prevent immediate damage; not                                                                                                                                                                                                                                                                                                                      |  |  |

| OUT      | 12      | Yes    | Yes                                                                                                                                                                                                                                                                                                                                                                                       | intended for prolonged operation.                                                                                                                                                                                                                                                                                                                                                        |  |  |

| OUTS     | 13      | Yes    | Yes                                                                                                                                                                                                                                                                                                                                                                                       | The device senses 0 V on the output and therefore will regulate to the maximum voltage possible. However, this 0 V on OUTS causes improper internal biasing which may cause unexpected voltage stresses which may cause damage over time. Additionally, since OUTS is externally connected to OUT, this could cause a high current path externally, potentially causing external damage. |  |  |

| FB_PG    | 14      | Yes    | Yes                                                                                                                                                                                                                                                                                                                                                                                       | Device enters soft start mode and outputs 2 mA on the SS_SET pin<br>which causes a higher output voltage. The device itself will be fine<br>unless it reaches current limit and remains in constant current limit for<br>a prolonged period of time.                                                                                                                                     |  |  |

#### Table 1. Pin Short-Circuited to Ground

| Table 2. Pin Short-Circuited to V <sub>IN</sub> |         |        |            |                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------------------------------|---------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                        | Pin No. | Damage | Functional | Description of Potential Failure Effects                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1                                               | BIAS    | Yes    | Yes        | If V <sub>BIAS</sub> is higher than V <sub>IN</sub> then the device may stop properly regulating since the proper bias voltage isn't supplied. If V <sub>IN</sub> is an acceptable bias supply then the device may continue operating properly. If V <sub>BIAS</sub> is high than 7 V, the IN pins are overstressed and damage occurs.                                           |  |  |

| 2                                               | EN      | No     | Yes        | Device turns on.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 3                                               | IN      | N/A    | N/A        | N/A                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 4                                               | IN      | N/A    | N/A        |                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 5                                               | CLM     | No     | Yes        | Normal operation – the device is configured for brick-wall current limit mode. If CLM was previously connected directly to GND when the short to $V_{IN}$ occurs, a short circuit could result, potentially causing damage. If the CLM was pulled-down to GND through a 10 k $\Omega$ pull-down to GND, damage is not expected.                                                  |  |  |

| 6                                               | GND     | Yes    | No         | Improper grounding could cause damage to various internal circuits.                                                                                                                                                                                                                                                                                                              |  |  |

| 7                                               | PG      | Yes    | Yes        | If PG is asserted and it's directly shorted to $V_{\text{IN}}$ an excessive amount of current will flow through this pin causing damage.                                                                                                                                                                                                                                         |  |  |

| 8                                               | REF     | Yes    | No         | Current flows into REF which damages the device and stops proper regulation.                                                                                                                                                                                                                                                                                                     |  |  |

| 9                                               | SS_SET  | Yes    | No         | Current flows into SS_SET which damages the device and stops proper regulation                                                                                                                                                                                                                                                                                                   |  |  |

| 10                                              | STAB    | Yes    | No         | The pass element turns-off. However, excessive current on STAB may cause damage.                                                                                                                                                                                                                                                                                                 |  |  |

| 11                                              | OUT     | Yes    | Yes        | Device stops regulation as the control loop senses the output is too high                                                                                                                                                                                                                                                                                                        |  |  |

| 12                                              | OUT     | Yes    | Yes        | and turns-off the pass element. However, this causes improper internal error amplifier biasing which may cause unexpected voltage stresses which cause damage over time.                                                                                                                                                                                                         |  |  |

| 13                                              | OUTS    | Yes    | Yes        | Device stops regulation as the control loop senses the output is too high<br>and turns-off the pass element. However, this causes improper internal<br>error amplifier biasing which may cause unexpected voltage stresses<br>which cause damage over time.                                                                                                                      |  |  |

| 14                                              | FB_PG   | Yes    | No         | If $V_{IN} > 6 V$ , this exceeds the recommended operating conditions leadin<br>to improper internal biasing which could cause functional failures. If $V_{II}$<br>< 6 V, the device is unable to enter soft start mode and PG is always<br>asserted; otherwise operation proceeds as normal. The lack of soft star<br>may result in current limit being reached during startup. |  |  |

### Table 2. Pin Short-Circuited to V

| Table 3. Pin Short-Circuited to V <sub>OUT</sub> |         |        |            |                                                                                                                                                                                                                                                                                                        |  |  |  |

|--------------------------------------------------|---------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                         | Pin No. | Damage | Functional | Description of Potential Failure Effects                                                                                                                                                                                                                                                               |  |  |  |

| 1                                                | BIAS    | Yes    | No         | The device stops regulating or reduces output voltage as there is not enough V <sub>BIAS</sub> to V <sub>OUT</sub> headroom. If V <sub>BIAS</sub> is above 7 V, it will cause improper overvoltage within the error amplifier which causes damage.                                                     |  |  |  |

| 2                                                | EN      | No     | Yes        | As long as $V_{\text{OUT}}$ is above the $V_{\text{EN}(\text{rising})}$ threshold it stays on and continues regulating, otherwise the device turns off.                                                                                                                                                |  |  |  |

| 3                                                | IN      | Yes    | Yes        | The device stops regulation as $V_{\text{OUT}}$ rises to $V_{\text{IN}}$ and the control loop                                                                                                                                                                                                          |  |  |  |

| 4                                                | IN      | Yes    | Yes        | senses the output is too high and turns-off the pass element. However,<br>this causes improper internal error amplifier biasing which may cause<br>unexpected voltage stresses which cause damage over time.                                                                                           |  |  |  |

| 5                                                | CLM     | Yes    | No         | The current limit mode is not well controlled since it changes with output voltage. This can lead to excess $V_{\text{IN}}$ current from input buffer shoot-through.                                                                                                                                   |  |  |  |

| 6                                                | GND     | Yes    | No         | Causes current limit on $V_{OUT}$ . The device is not intended to remain in constant current limit for a prolonged period of time. Additionally, if the GND pin is no longer the system ground, the improper grounding could cause damage to various internal circuits.                                |  |  |  |

| 7                                                | PG      | Yes    | Yes        | If PG is asserted and it's directly shorted to $V_{\text{OUT}},$ an excessive amount of current will flow through this pin.                                                                                                                                                                            |  |  |  |

| 8                                                | REF     | Yes    | No         | Current flows into or out of REF which damages the device and stops proper regulation                                                                                                                                                                                                                  |  |  |  |

| 9                                                | SS_SET  | Yes    | No         | Since $V_{SS\_SET}$ is nominally equal to $V_{OUT}$ there is no immediate damage as long as SS_SET is able to continue sourcing its current; however, there could be a complicated interaction causing too high of an output voltage or an attempt to sink current through the OUT pin causing damage. |  |  |  |

| 10                                               | STAB    | No     | No         | When enabled, the pass element turns mostly-off. When disabled, forcing STAB to 0 V will cause higher $V_{\text{BIAS}}$ current to flow, which could cause damage.                                                                                                                                     |  |  |  |

| 11                                               | OUT     | N/A    | N/A        | N/A                                                                                                                                                                                                                                                                                                    |  |  |  |

| 12                                               | OUT     | N/A    | N/A        | 1                                                                                                                                                                                                                                                                                                      |  |  |  |

| 13                                               | OUTS    | No     | Yes        | Nominal operation.                                                                                                                                                                                                                                                                                     |  |  |  |

| 14                                               | FB_PG   | No     | Yes        | When $V_{OUT}$ rises above the $V_{FB\_PG(rising)}$ threshold, PG is asserted and the fast-start current turns off (resulting in a longer startup time).                                                                                                                                               |  |  |  |

| Pin Name Pin No. Da |    | Damage | Functional | Description of Potential Failure Effects                                                                                                                                                                      |  |  |

|---------------------|----|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BIAS                | 1  | No     | No         | Device stops regulating as there is no V <sub>BIAS</sub> voltage.                                                                                                                                             |  |  |

| EN                  | 2  | No     | No         | Device may oscillate on and off.                                                                                                                                                                              |  |  |

| IN                  | 3  | Yes    | Yes        | If only one pin is floating then current will go through the other pin                                                                                                                                        |  |  |

| IN                  | 4  | Yes    | Yes        | causing the current of the individual pin to be too large, eventually causing damage.                                                                                                                         |  |  |

| CLM                 | 5  | Yes    | No         | The current limit mode is not well controlled. Additionally, an undefined voltage on the CLM input buffer will cause additional $V_{\text{IN}}$ shoot-through current to flow, which could damage the device. |  |  |

| GND                 | 6  | Yes    | No         | Improper biasing is expected to cause oscillations with large current spikes.                                                                                                                                 |  |  |

| PG                  | 7  | No     | No         | PG will work when pulled-down but since it's an open drain it cannot go high and will be in an unknown state.                                                                                                 |  |  |

| REF                 | 8  | No     | No         | The reference current will not be created and therefore the part will output 0 V when attempting to regulate.                                                                                                 |  |  |

| SS_SET              | 9  | Yes    | No         | A 100 $\mu$ A will attempt to be forced out of this pin causing it to reach<br>a high voltage. This may result in improper internal error amp biasing,<br>causing overvoltage failures.                       |  |  |

| STAB                | 10 | No     | Yes        | The control loop response will be different with potentially worse phase margin, but the part is still operational.                                                                                           |  |  |

| OUT                 | 11 | Yes    | Yes        | If only one pin is floating then current will go through the other pin                                                                                                                                        |  |  |

| OUT                 | 12 | Yes    | Yes        | causing the current of the individual pin to be too large, eventually causing damage.                                                                                                                         |  |  |

| OUTS                | 13 | Yes    | No         | The device will not know what voltage to regulate to and will likely oscillate, potentially causing damage.                                                                                                   |  |  |

| FB_PG               | 14 | Yes    | No         | Device fast start current will oscillate, potentially causing damage.                                                                                                                                         |  |  |

| Pin Name | Pin No. | Short to Pin<br>No. | Short to Pin<br>Name | Damage | Functional | COMMENTS                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|---------------------|----------------------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIAS     | 1       | 2                   | EN                   | Yes    | Yes        | Depending on the bias supply voltage, the device will<br>be turned on or turned off. If the bias voltage is over<br>7 V, the EN pin is overstressed.                                                                                                                                                                                              |

| EN       | 2       | 3                   | IN                   | No     | Yes        | Depending on the input supply voltage, the device will be turned-on or turned-off.                                                                                                                                                                                                                                                                |

| IN       | 3       | 4                   | IN                   | No     | Yes        | Normal operation                                                                                                                                                                                                                                                                                                                                  |

| IN       | 4       | 5                   | CLM                  | No     | Yes        | Normal operation – the device is configured for<br>brick-wall current limit mode. If CLM was previously<br>connected directly to GND when the short to $V_{IN}$<br>occurs, a short circuit could result, potentially causing<br>damage. If the CLM was pulled-down to GND<br>through a 10 k $\Omega$ pull-down to GND, damage is not<br>expected. |

| CLM      | 5       | 6                   | GND                  | No     | Yes        | Normal operation – device configured for turn-off current limit mode. If CLM was previously connected directly to V <sub>IN</sub> when the short to ground occurs, a short circuit could result, potentially causing damage. As the schematic shows a 10 k $\Omega$ pull-up to V <sub>IN</sub> , damage is not expected.                          |

| GND      | 6       | 7                   | PG                   | No     | Yes        | PG remains at 0 V since it's an open drain and doesn't have an internal pull-up voltage.                                                                                                                                                                                                                                                          |

| REF      | 8       | 9                   | SS_SET               | Yes    | No         | The $V_{\text{REF}}$ voltage will be unstable since it cannot handle large output capacitance and SS_SET will always be 1.2 V. This control loop instability may cause damage.                                                                                                                                                                    |

| SS_SET   | 9       | 10                  | STAB                 | Yes    | No         | The STAB voltage will rise as it is charged by the SS_SET pin current source. This causes the pass element to slowly turn-off. However, the SS_SET and OUT voltages will be unstable since STAB components are impacted by the RC of SS_SET. This may cause improper overvoltage within the internal error amplifier, causing damage.             |

| STAB     | 10      | 11                  | OUT                  | No     | No         | When enabled, the pass element turns partially-off. When disabled, forcing STAB to 0 V will cause higher $V_{BIAS}$ current to flow, which could cause damage.                                                                                                                                                                                    |

| OUT      | 11      | 12                  | OUT                  | No     | Yes        | Normal operation.                                                                                                                                                                                                                                                                                                                                 |

| OUT      | 12      | 13                  | OUTS                 | No     | Yes        | Normal operation.                                                                                                                                                                                                                                                                                                                                 |

| OUTS     | 13      | 14                  | FB_PG                | No     | Yes        | Since OUTS is connected to OUT, when $V_{OUT}$ rises above the $V_{FB_PG(rising)}$ threshold, PG is asserted and the fast-start current turns off (resulting in a longer startup time).                                                                                                                                                           |

## Table 5. Pin Short-Circuited to Adjacent Pin Circuited

7

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated