www.ti.com

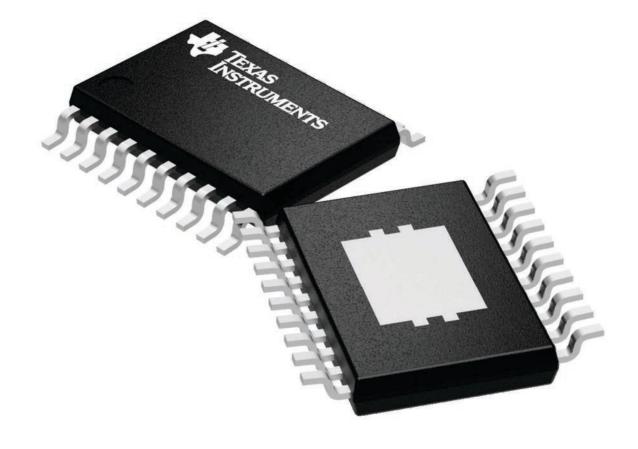

# 12-Channel, 16-Bit, Enhanced Spectrum PWM, RGB, LED Driver with 3.3-V Linear Regulator and Watchdog Timer

Check for Samples: TLC59711

#### **FEATURES**

- 12 Constant-Current Sink Output Channels

- Current Capability: 60 mA per channel

- Grayscale (GS) Control with Enhanced Spectrum PWM: 16-bit (65536 steps)

- Global Brightness Control (BC):

7-bit (128 steps) for each color group

- Power-Supply Voltage Range: Internal linear regulator: 4.0 V to 17 V Direct power supply: 3.0 V to 5.5 V

- LED Supply Voltage: Up to 17 V

- Constant-Current Accuracy:

- Channel-to-Channel = ±1% (typ), ±3% (max)

- Device-to-Device =  $\pm 1\%$  (typ),  $\pm 4\%$  (max)

- Data Transfer Rate: 10 MHz (cascading)

- Linear Voltage Regulator: 3.3 V

- Auto Display Repeat Function

- Display Timing Reset Function

- Internal/External Selectable GS Clock

- Thermal Shutdown (TSD) with Auto Restart

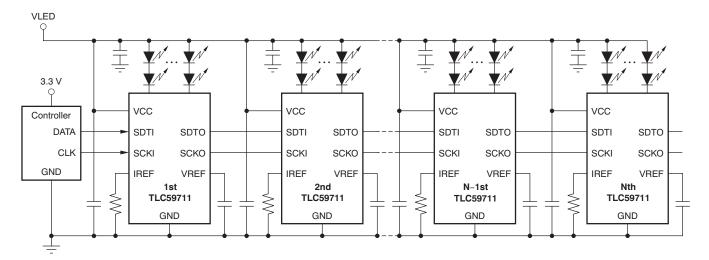

- Unlimited Device Cascading

- Watchdog Timer for External Clock Failure

- Operating Temperature Range: -40°C to +85°C

#### **APPLICATIONS**

RGB LED Cluster Lamp Displays

#### DESCRIPTION

The TLC59711 is a 12-channel, constant-current sink driver. Each output channel has individually adjustable currents with 65536 PWM grayscale (GS) steps. Also, each color group can be controlled by 128 constant-current sink steps with the global brightness control (BC) function. GS control and BC are accessible via a two-wire signal interface. The maximum current value for each channel is set by a single external resistor. All constant-current outputs are turned off when the IC is in an over-temperature condition.

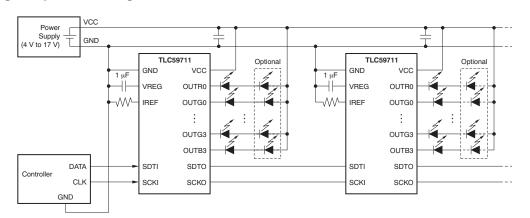

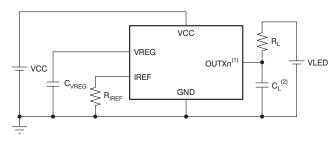

NOTE: The number of LEDs in series changes, depending on the VCC voltage.

## Typical Application Circuit Example (Internal Linear Regulator Using $V_{CC}$ = 4 V to 17 V)

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incoporated. All other trademarks are the property of their respective owners.

#### **DESCRIPTION (CONTINUED)**

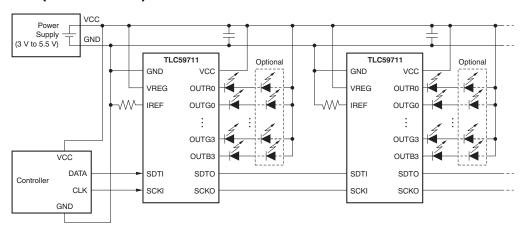

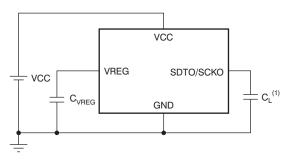

NOTE: The number of LEDs in series changes, depending on the VCC voltage.

## Typical Application Circuit Example (Direct Power Supplying $V_{CC}$ = 3 V to 5.5 V)

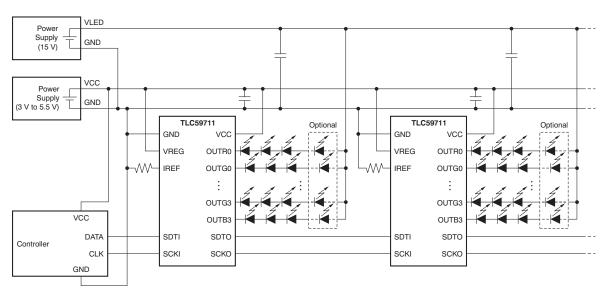

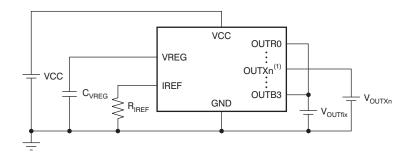

NOTE: The number of LEDs in series changes, depending on the VLED voltage.

## Typical Application Circuit Example (Direct Power Supplying $V_{CC}$ = 3 V to 5.5 V, $V_{LED}$ = 15 V)

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

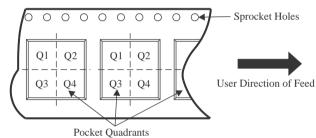

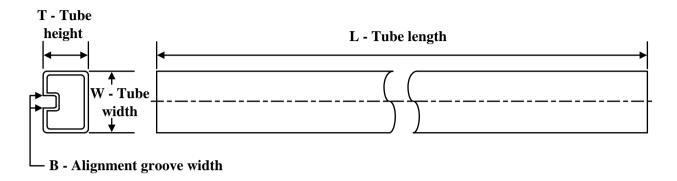

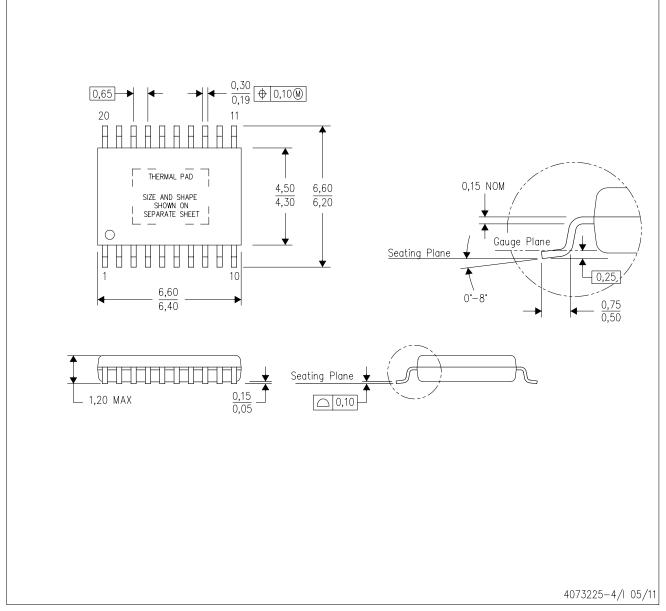

#### ORDERING INFORMATION(1)

| PRODUCT  | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR | ORDERING NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|----------|-----------------------|-----------------------|-----------------|------------------------------|

| TLC59711 | LITECOD 20 DowerDADIM | DWD                   | TLC59711PWPR    | Tape and Reel, 2000          |

| 11009/11 | HTSSOP-20 PowerPAD™   | PWP                   | TLC59711PWP     | Tube, 70                     |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

www.ti.com

### **ABSOLUTE MAXIMUM RATINGS**(1)(2)

Over operating free-air temperature range, unless otherwise noted.

|                                |                                                | VALUE |            | LINUT |

|--------------------------------|------------------------------------------------|-------|------------|-------|

|                                |                                                | MIN   | MAX        | UNIT  |

| Supply voltage                 | VCC                                            | -0.3  | +18        | V     |

| lament violtame                | IREF                                           | -0.3  | VREG + 0.3 | V     |

| Input voltage                  | SDTI, SCKI                                     | -0.3  | VREG + 0.6 | V     |

|                                | OUTR0 to OUTR3, OUTG0 to OUTG3, OUTB0 to OUTB3 | -0.3  | +18        | V     |

| Output voltage                 | SDTO, SCKO                                     | -0.3  | VREG + 0.3 | V     |

|                                | VREG                                           | -0.3  | +6         | V     |

| Outrat surrent (DO)            | OUTR0 to OUTR3, OUTG0 to OUTG3, OUTB0 to OUTB3 |       | 75         | mA    |

| Output current (DC)            | VREG                                           |       | -30        | mA    |

| Operating junction temperature | T <sub>J (max)</sub>                           |       | +150       | °C    |

| Storage temperature            | T <sub>stg</sub>                               | -55   | +150       | °C    |

| Clastrostatic discharge ratios | Human body model (HBM)                         |       | 4          | kV    |

| Electrostatic discharge rating | Charged device model (CDM)                     |       | 2          | kV    |

|                                |                                                |       |            |       |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                     |                                              | TLC59711 |       |

|---------------------|----------------------------------------------|----------|-------|

|                     | THERMAL METRIC <sup>(1)</sup>                | PWP      | UNITS |

|                     |                                              | 20 PINS  |       |

| $\theta_{JA}$       | Junction-to-ambient thermal resistance       | 68.6     |       |

| $\theta_{ m JCtop}$ | Junction-to-case (top) thermal resistance    | 44.2     |       |

| θ <sub>JB</sub>     | Junction-to-board thermal resistance         | 19.3     | 0000  |

| ₽лт                 | Junction-to-top characterization parameter   | 2.7      | °C/W  |

| ₽ <sub>ЈВ</sub>     | Junction-to-board characterization parameter | 15.7     |       |

| $\theta_{JCbot}$    | Junction-to-case (bottom) thermal resistance | 1.8      |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Copyright © 2011–2012, Texas Instruments Incorporated

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

#### **RECOMMENDED OPERATING CONDITIONS**

At  $T_A = -40$ °C to +85°C, and  $V_{CC} = 4$  V to 17 V or  $V_{CC} = V_{REG} = 3.0$  V to 5.5 V, unless otherwise noted.

|                                  |                                                                               | Т          | LC59711    |            |      |  |

|----------------------------------|-------------------------------------------------------------------------------|------------|------------|------------|------|--|

|                                  |                                                                               | MIN        | NOM        | MAX        | UNIT |  |

| DC CHARAC                        | CTERISTICS                                                                    |            |            | 1          |      |  |

| V <sub>CC</sub>                  | Supply voltage, internal voltage regulator used                               | 4          |            | 17         | V    |  |

| $V_{REG}$                        | Supply voltage, VREG connected to VCC                                         | 3          | 3.3        | 5.5        | V    |  |

| Vo                               | Voltage applied to output (OUTR0 to OUTR3, OUTG0 to OUTG3, OUTB0 to OUTB3)    |            |            | 17         | V    |  |

| V <sub>IH</sub>                  | High-level input voltage (SDTI, SCKI)                                         | 0.7 × VREG |            | VREG       | V    |  |

| V <sub>IL</sub>                  | Low-level input voltage (SDTI, SCKI)                                          | GND        |            | 0.3 × VREG | V    |  |

| V <sub>IHYS</sub>                | Input voltage hysteresis (SDTI, SCKI)                                         |            | 0.2 × VREG |            | V    |  |

| I <sub>OH</sub>                  | High-level output current (SDTO)                                              |            |            | -2         | mA   |  |

| I <sub>OL</sub>                  | Low-level output current (SDTO)                                               |            |            | 2          | mA   |  |

| l <sub>oLC</sub>                 | Constant output sink current (OUTR0 to OUTR3, OUTG0 to OUTG3, OUTB0 to OUTB3) |            |            | 60         | mA   |  |

| I <sub>REG</sub>                 | Voltage regulator output current (VREG)                                       |            |            | -25        | mA   |  |

| T <sub>A</sub>                   | Operating free temperature range                                              | -40        |            | +85        | °C   |  |

| T <sub>J</sub>                   | Operating junction temperature                                                | -40        |            | +125       | °C   |  |

| AC CHARAC                        | CTERISTICS                                                                    |            |            |            |      |  |

| f <sub>CLK (SCKI)</sub>          | Data clock frequency and GS control clock frequency, SCKI                     | 0.007      |            | 10         | MHz  |  |

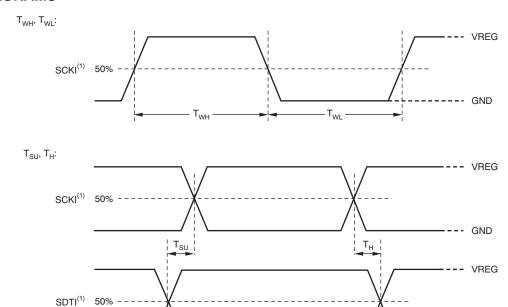

| t <sub>WH</sub> /t <sub>WL</sub> | Pulse duration, SCKI                                                          | 10         |            |            | ns   |  |

| t <sub>SU</sub>                  | Setup time, SDTI – SCKI↑                                                      | 5          |            |            | ns   |  |

| t <sub>H</sub>                   | Hold time, SDTI – SCKI↑                                                       | 3          |            |            | ns   |  |

#### **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40$ °C to +85°C,  $V_{CC} = 4$  V to 17 V or  $V_{CC} = V_{REG} = 3$  V to 5.5 V,  $V_{LED} = 5$  V, and  $C_{VREG} = 1$   $\mu F$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C and  $V_{CC} = 12$  V.

|                   |                                           |                                                                                                                                                                                                     |                        | TLC59711 |           |      |

|-------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-----------|------|

|                   | PARAMETER                                 | TEST CONDITIONS                                                                                                                                                                                     | MIN                    | TYP      | MAX       | UNIT |

| V <sub>OH</sub>   | High-level output voltage, SDTO/SCKO      | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                            | V <sub>REG</sub> - 0.4 |          | $V_{REG}$ | V    |

| V <sub>OL</sub>   | Low-level output voltage, SDTO/SCKO       | Low-level output voltage, SDTO/SCKO $I_{OL} = 2 \text{ mA}$ 0 0.                                                                                                                                    |                        | 0.4      | V         |      |

| V <sub>IREF</sub> | Reference voltage output, IREF            | $R_{IREF} = 0.82 \text{ k}\Omega$                                                                                                                                                                   | 1.18                   | 1.21     | 1.24      | V    |

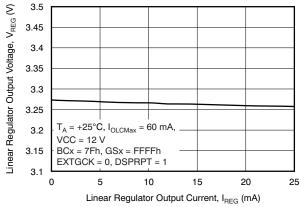

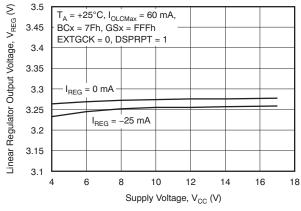

| V <sub>REG</sub>  | Linear regulator output voltage, VREG     | V <sub>CC</sub> = 4 V to 17 V, I <sub>REG</sub> = 0 mA to -25 mA                                                                                                                                    | 3.1                    | 3.3      | 3.5       | V    |

| $\Delta V_{REG}$  | Line regulation of linear regulator, VREG | V <sub>CC</sub> = 4 V to 17 V, I <sub>REG</sub> = 0 mA                                                                                                                                              |                        |          | 90        | mV   |

| $\Delta V_{REG1}$ | Load regulation of linear regulator, VREG | V <sub>CC</sub> = 12 V, I <sub>REG</sub> = 0 mA to -25 mA                                                                                                                                           |                        |          | 120       | mV   |

| V <sub>STR</sub>  | Undervoltage lockout release, VREG        |                                                                                                                                                                                                     | 2.5                    | 2.7      | 2.9       | V    |

| V <sub>HYS</sub>  | Undervoltage lockout hysteresis, VREG     |                                                                                                                                                                                                     | 300                    | 400      | 500       | mV   |

| I <sub>1</sub>    | Input current, SDTI/SCKI                  | V <sub>I</sub> = V <sub>REG</sub> or GND                                                                                                                                                            | -1                     |          | 1         | μΑ   |

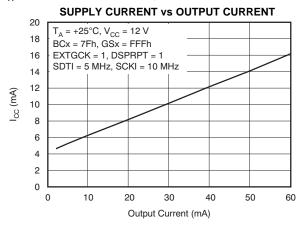

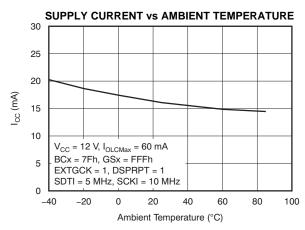

| Icc               |                                           | SDTI/SCKI = low, BLANK = 1, GSn = FFFFh, BCX = 7Fh, $V_{OUTXn}$ = 1 V, $R_{IREF}$ = 24 k $\Omega$ ( $I_{OLCMax}$ = 2 mA)                                                                            |                        | 2        | 4         | mA   |

| I <sub>CC1</sub>  |                                           | SDTI/SCKI = low, BLANK = 1, GSn = FFFFh, BCX = 7Fh, $V_{OUTXn}$ = 1 V, $R_{IREF}$ = 1.6 k $\Omega$ ( $I_{OLCMax}$ = 30 mA)                                                                          |                        | 6        | 9         | mA   |

| I <sub>CC2</sub>  | Supply current                            | SDTI = 5 MHz, SCKI = 10 MHz, BLANK = 0, auto repeat enable, external GS clock selected, GSn = FFFFh, BCX = 7Fh, V <sub>OUTXn</sub> = 1 V, R <sub>IREF</sub> = 1.6 kΩ (I <sub>OLCMax</sub> = 30 mA)  |                        | 10       | 18        | mA   |

| I <sub>CC3</sub>  |                                           | SDTI = 5 MHz, SCKI = 10 MHz, BLANK = 0, auto repeat enable, external GS clock selected, GSn = FFFFh, BCX = 7Fh, V <sub>OUTXn</sub> = 1 V, R <sub>IREF</sub> = 0.82 kΩ (I <sub>OLCMax</sub> = 60 mA) |                        | 16       | 32        | mA   |

| I <sub>OLC</sub>  | Constant output current, OUTXn            | All OUTXn on, BCX = 7Fh, $V_{OUTXn}$ = 1 V, $V_{OUTfix}$ = 1 V, $R_{IREF}$ = 0.82 k $\Omega$ ( $I_{OLCMax}$ = 60 mA)                                                                                | 56.3                   | 60.5     | 64.7      | mA   |

| I <sub>OLKG</sub> | Leakage output current, OUTXn             | All OUTXn off, BCX = 7Fh, $V_{OUTXn}$ = 17 V, $V_{OUTfix}$ = 17 V, $R_{IREF}$ = 0.82 k $\Omega$ ( $I_{OLCMax}$ = 60 mA)                                                                             |                        |          | 0.1       | μΑ   |

#### **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_A = -40$ °C to +85°C,  $V_{CC} = 4$  V to 17 V or  $V_{CC} = V_{REG} = 3$  V to 5.5 V,  $V_{LED} = 5$  V, and  $C_{VREG} = 1$   $\mu$ F, unless otherwise noted. Typical values are at  $T_A = +25$ °C and  $V_{CC} = 12$  V.

|                    |                                                                                           |                                                                                                                                                                            | TLC59711 |      |      |      |

|--------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

|                    | PARAMETER                                                                                 | TEST CONDITIONS                                                                                                                                                            | MIN      | TYP  | MAX  | UNIT |

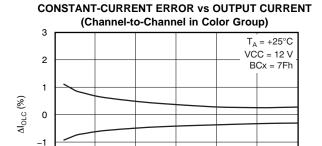

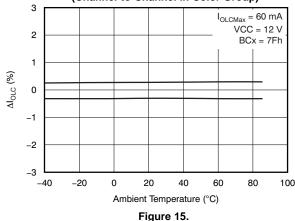

| ΔI <sub>OLC</sub>  | Constant-current error <sup>(1)</sup> (channel-to-channel in same color group), OUTXn     | All OUTXn on, BCX = 7Fh, $V_{OUTXn} = V_{OUTfix} = 1 \text{ V}$ , $R_{IREF} = 0.82 \text{ k}\Omega \text{ (}I_{OLCMax} = 60 \text{ mA)}$                                   |          | ±1   | ±3   | %    |

| ΔI <sub>OLC1</sub> | Constant current error <sup>(2)</sup><br>(device-to-device in same color group),<br>OUTXn | All OUTXn on, BCX = 7Fh, $V_{OUTXn} = V_{OUTfix} = 1V$ , $R_{IREF} = 0.82~k\Omega$ ( $I_{OLCMax} = 60~mA$ ), at same grouped color output of OUTR0-3, OUTG0-3, and OUTB0-3 |          | ±1   | ±4   | %    |

| ΔI <sub>OLC2</sub> | Line regulation of constant-current output, OUTXn <sup>(3)</sup>                          | All OUTn on, BCX = 7Fh, $V_{OUTXn} = V_{OUTfix} = 1 \text{ V}$ , $R_{IREF} = 0.82 \text{ k}\Omega \left(I_{OLCMax} = 60 \text{ mA}\right)$                                 |          | ±0.5 | ±1   | %/V  |

| ΔI <sub>OLC3</sub> | Load regulation of constant-current output, OUTXn <sup>(4)</sup>                          | All OUTn on, BCX = 7Fh, $V_{OUTXn} = V_{OUTfix} = 1 \text{ V}$ , $R_{IREF} = 0.82 \text{ k}\Omega \left(I_{OLCMax} = 60 \text{ mA}\right)$                                 |          | ±1   | ±3   | %/V  |

| T <sub>TSD</sub>   | Thermal shutdown temperature                                                              | Junction temperature (5)                                                                                                                                                   | 150      | 165  | 180  | °C   |

| T <sub>HYS</sub>   | Thermal shutdown hysteresis                                                               | Junction temperature <sup>(5)</sup>                                                                                                                                        | 5        | 10   | 20   | °C   |

| V <sub>IREF</sub>  | Reference voltage output, IREF                                                            | $R_{IREF} = 0.82 \text{ k}\Omega$                                                                                                                                          | 1.18     | 1.21 | 1.24 | V    |

| $V_{REG}$          | Linear regulator output voltage, VREG                                                     | $V_{CC}$ = 4 V to 17 V, $I_{REG}$ = 0 mA to -25 mA                                                                                                                         | 3.1      | 3.3  | 3.5  | V    |

| $\Delta V_{REG}$   | Line regulation of linear regulator, VREG                                                 | V <sub>CC</sub> = 4 V to 17 V, I <sub>REG</sub> = 0 mA                                                                                                                     |          |      | 90   | mV   |

| ∆V <sub>REG1</sub> | Load regulation of linear regulator, VREG                                                 | V <sub>CC</sub> = 12 V, I <sub>REG</sub> = 0 mA to -25 mA                                                                                                                  |          |      | 120  | mV   |

| / <sub>STR</sub>   | Undervoltage lockout release, VREG                                                        |                                                                                                                                                                            | 2.5      | 2.7  | 2.9  | V    |

| / <sub>HYS</sub>   | Undervoltage lockout hysteresis, VREG                                                     |                                                                                                                                                                            | 300      | 400  | 500  | mV   |

The deviation of each output in the same color group (OUTR0-OUTR3 or OUTG0-OUTG3 or OUTB0-OUTB3) from the average current from the same color group. Deviation is calculated by the formula:

$$\Delta \text{ (\%)} = \left[ \frac{I_{\text{OLCXn}}}{\frac{(I_{\text{OLCX0}} + I_{\text{OLCX1}} + I_{\text{OLCX2}} + I_{\text{OLCX3}})}{4}} - 1 \right] \times 100$$

Where: X = R/G/B, and n = 0-3

The deviation of each color group constant-current average from the ideal constant-current value.

Deviation is calculated by the following formula:

$$\Delta \text{ (\%)} = \left[ \begin{array}{c} \frac{(I_{\text{OLCX0}} + I_{\text{OLCX2}} + I_{\text{OLCX2}} + I_{\text{OLCX3}})}{4} - \text{(Ideal Output Current)} \\ \hline & \text{Ideal Output Current} \end{array} \right] \times 100$$

Where: X = R/G/B.

Ideal current is calculated by the following formula for the OUTRn and OUTGn groups:

$$I_{OLCXn(IDEAL)}$$

(mA) = 41 ×  $\left[\frac{1.21}{R_{IREF}(\Omega)}\right]$

Where: X = R/G/B.

Line regulation is calculated by this equation:

$$\Delta \, (\%/V) = \left[ \frac{(I_{OLCXn} \, \text{at VCC} = 5.5 \, \text{V}) - (I_{OLCXn} \, \text{at VCC} = 3 \, \text{V})}{(I_{OLCXn} \, \text{at VCC} = 3 \, \text{V})} \right] \times \frac{100}{5.5 \, \text{V} - 3 \, \text{V}}$$

Where: X = R/G/B, n = 0-3.

Load regulation is calculated by the equation:

$$\Delta \ (\%/V) = \left[ \frac{(I_{OLCXn} \text{ at } V_{OUTXn} = 3 \text{ V}) - (I_{OLCXn} \text{ at } V_{OUTXn} = 1 \text{ V})}{(I_{OLCXn} \text{ at } V_{OUTXn} = 1 \text{ V})} \right] \times \frac{100}{3 \text{ V} - 1 \text{ V}}$$

Where: X = R/G/B, n = 0-3.

Not tested, specified by design.

Copyright © 2011–2012, Texas Instruments Incorporated

#### **SWITCHING CHARACTERISTICS**

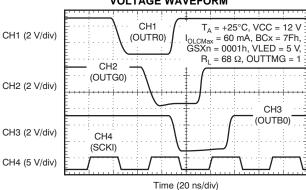

At  $T_A = -40$ °C to +85°C,  $V_{CC} = 4$  V to 17 V or  $V_{CC} = V_{REG} = 3$  V to 5.5 V,  $C_{VREG} = 1$   $\mu F$ ,  $C_L = 15$  pF,  $R_L = 68$   $\Omega$ , and  $V_{LED} = 5$  V, unless otherwise noted. Typical values are at  $T_A = +25$ °C and  $V_{CC} = 12$  V.

|                                |                                    |                                                                                                                                                                                                                      |                    |        | TLC59711               |      |  |  |

|--------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|------------------------|------|--|--|

|                                | PARAMETER                          | TEST CONDITIONS                                                                                                                                                                                                      | MIN                | TYP MA |                        | UNIT |  |  |

| t <sub>R0</sub>                | Rise time, SDTO/SCKO               |                                                                                                                                                                                                                      | 4                  | 10     | 15                     | ns   |  |  |

| t <sub>R1</sub>                | Rise time, OUTXn                   | BCX = 7Fh                                                                                                                                                                                                            |                    | 5      | 15                     | ns   |  |  |

| t <sub>F0</sub>                | Fall time, SDTO/SCKO               |                                                                                                                                                                                                                      | 4                  | 10     | 15                     | ns   |  |  |

| t <sub>F1</sub>                | Fall time, OUTXn                   | BCX = 7Fh                                                                                                                                                                                                            |                    | 15     | 25                     | ns   |  |  |

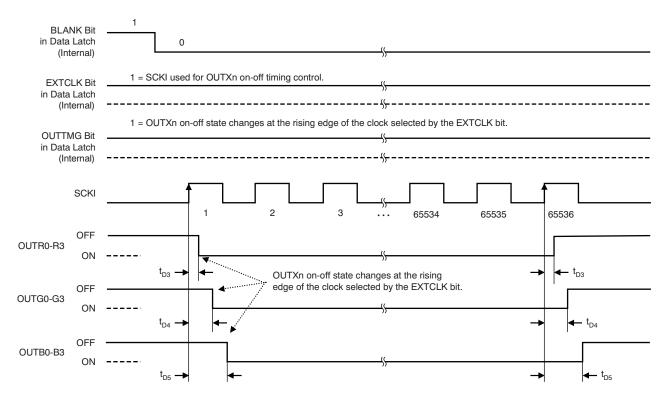

| t <sub>D0</sub>                | Propagation delay                  | SCKI↑ to SDTO↑↓                                                                                                                                                                                                      | 44                 | 72     | 124                    | ns   |  |  |

| t <sub>D1</sub>                |                                    | SCKI↑ to SCKO↑, V <sub>REG</sub> = 3.3 V                                                                                                                                                                             | 11                 | 22     | 53                     | ns   |  |  |

| t <sub>D2</sub> <sup>(1)</sup> |                                    | SCKO↑ to SDTO↑↓, V <sub>REG</sub> = 3.3 V                                                                                                                                                                            | 33                 | 50     | 71                     | ns   |  |  |

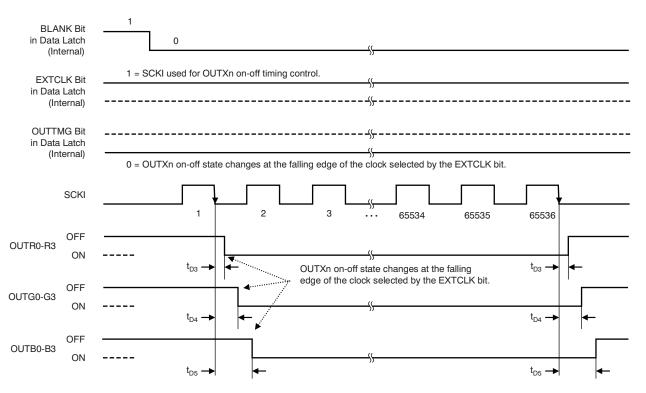

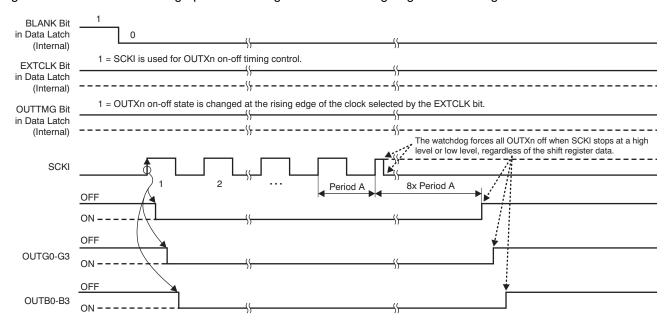

| t <sub>D3</sub>                |                                    | SCKI↑ to OUTRn↑↓, BLANK = 0,<br>BCXn = 7Fh, OUTTMG = 1<br>Or SCKI↓ to OUTRn↑↓, BLANK = 0,<br>BCXn = 7Fh, OUTTMG = 0                                                                                                  | 10                 | 25     | 60                     | ns   |  |  |

| t <sub>D4</sub>                |                                    | $\begin{array}{l} SCKI\uparrow \ to \ OUTGn\uparrow\downarrow, \ BLANK = 0, \\ BCXn = 7Fh, \ OUTTMG = 1 \\ Or \ SCKI\downarrow \ to \ OUTGn\uparrow\downarrow, \ BLANK = 0, \\ BCXn = 7Fh, \ OUTTMG = 0 \end{array}$ | 25                 | 50     | 90                     | ns   |  |  |

| t <sub>D5</sub>                |                                    | SCKI↑ to OUTBn↑↓, BLANK = 0,<br>BCXn = 7Fh, OUTTMG = 1<br>Or SCKI↓ to OUTBn↑↓, BLANK = 0,<br>BCXn = 7Fh, OUTTMG = 0                                                                                                  | 40                 | 75     | 120                    | ns   |  |  |

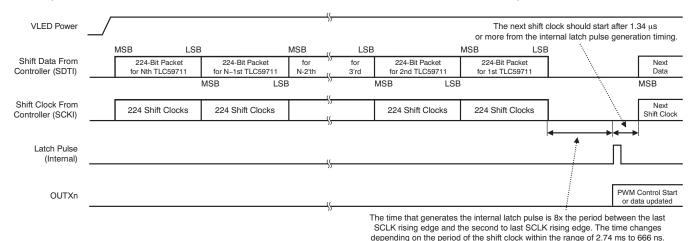

| t <sub>D6</sub> <sup>(2)</sup> |                                    | Last SCKI↑ to internal latch pulse genaration                                                                                                                                                                        | 8/f <sub>OSC</sub> |        | 16384/f <sub>OSC</sub> | sec  |  |  |

| t <sub>W(SCKO)</sub>           | Shift clock output one pulse width | SCKO↑ to SCKO↓                                                                                                                                                                                                       | 29                 | 41     | 70                     | ns   |  |  |

| fosc                           | Internal oscillator frequency      |                                                                                                                                                                                                                      | 7                  | 10     | 12                     | MHz  |  |  |

<sup>(1)</sup> The propagation delays are calculated by t<sub>D2a</sub> = t<sub>D0a</sub> - t<sub>D1a</sub> or t<sub>D2b</sub> = t<sub>D0b</sub> - t<sub>D1b</sub>.

(2) The generation timing of the internal latch pulse changes depending on the SCKI clock frequency; see the *Internal Latch Pulse* Generation Timing section.

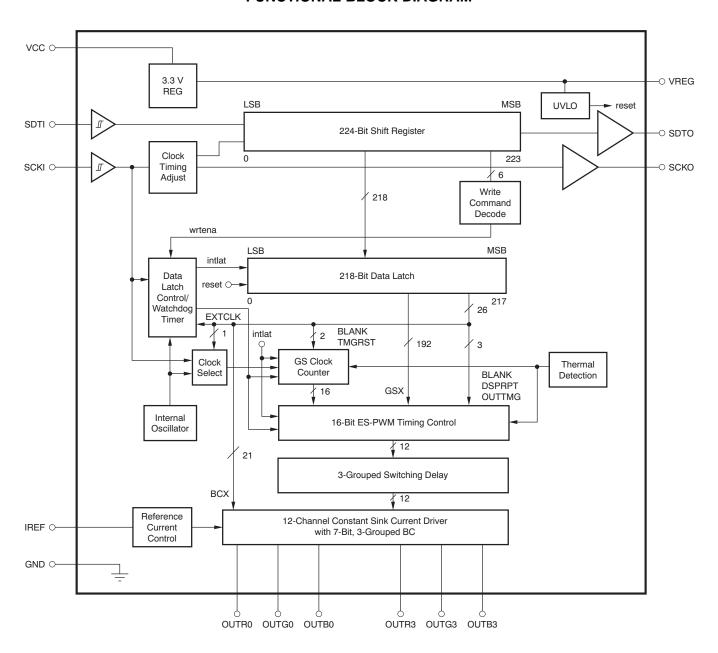

#### **FUNCTIONAL BLOCK DIAGRAM**

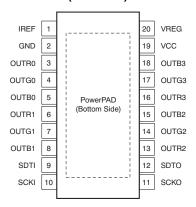

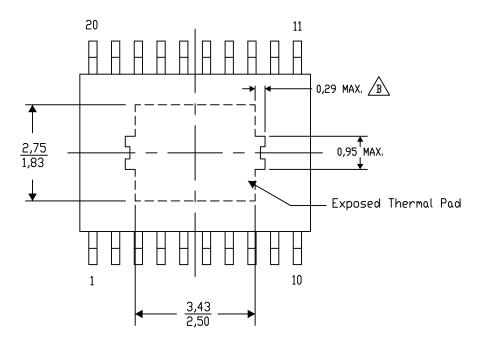

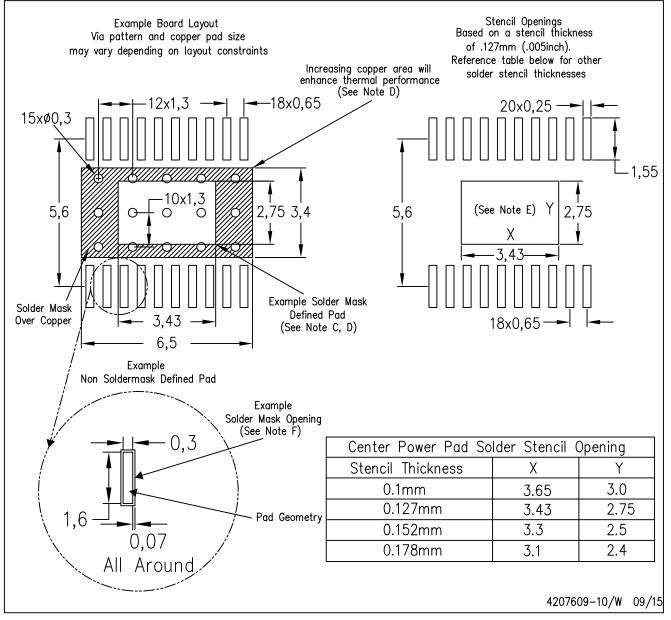

#### **PIN CONFIGURATIONS**

#### PWP PACKAGE HTSSOP-20 PowerPAD (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| TERMI | INAL |     |                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | PWP  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |

| IREF  | 1    | I/O | Maximum current programming terminal.  A resistor connected between IREF and GND sets the maximum current for every constant-current output. When this terminal is directly connected to GND, all outputs are forced off. The external resistor should be placed close to the device.                                                                                                 |

| GND   | 2    | _   | Power ground terminal                                                                                                                                                                                                                                                                                                                                                                 |

| OUTB0 | 5    | 0   |                                                                                                                                                                                                                                                                                                                                                                                       |

| OUTB1 | 8    | 0   | BLUE constant-current outputs.                                                                                                                                                                                                                                                                                                                                                        |

| OUTB2 | 15   | 0   | Multiple outputs can be configured in parallel to increase the constant-current capability.  Different voltages can be applied to each output.                                                                                                                                                                                                                                        |

| OUTB3 | 18   | 0   |                                                                                                                                                                                                                                                                                                                                                                                       |

| OUTG0 | 4    | 0   |                                                                                                                                                                                                                                                                                                                                                                                       |

| OUTG1 | 7    | 0   | GREEN constant-current outputs.                                                                                                                                                                                                                                                                                                                                                       |

| OUTG2 | 14   | 0   | Multiple outputs can be configured in parallel to increase the constant-current capability.  Different voltages can be applied to each output.                                                                                                                                                                                                                                        |

| OUTG3 | 17   | 0   | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                               |

| OUTR0 | 3    | 0   |                                                                                                                                                                                                                                                                                                                                                                                       |

| OUTR1 | 6    | 0   | RED constant-current outputs.                                                                                                                                                                                                                                                                                                                                                         |

| OUTR2 | 13   | 0   | Multiple outputs can be configured in parallel to increase the constant-current capability.  Different voltages can be applied to each output.                                                                                                                                                                                                                                        |

| OUTR3 | 16   | 0   |                                                                                                                                                                                                                                                                                                                                                                                       |

| SCKI  | 10   | I   | Serial data shift clock input.  Data present on SDTI are shifted to the LSB of the 224-bit shift register with the SCKI rising edge Data in the shift register are shifted toward the MSB at each SCKI rising edge.  The MSB data of the shift register appear on SDTO.                                                                                                               |

| SCKO  | 11   | 0   | Serial data shift clock output. The input shift clock signal from SCKI is adjusted to the timing of the serial data output for SDTO and the signal is then output at SCKO.                                                                                                                                                                                                            |

| SDTI  | 9    | I   | Serial data input for the 224-bit shift register                                                                                                                                                                                                                                                                                                                                      |

| SDTO  | 12   | 0   | Serial data output of the 224-bit shift register. SDTO is connected to the MSB of the 224-bit shift register. Data are clocked out at the falling edge SCKO.                                                                                                                                                                                                                          |

| VREG  | 20   | I/O | Internal linear voltage regulator output. A decoupling capacitor of 1 $\mu$ F must be connected. This output can be used for external devices as a 3.3-V power supply. This terminal can be connected with the VREG terminal of other devices to increase the supply current. Also, this pin can be supplied with 3 V to 5.5 V from an external power supply by connecting it to VCC. |

| VCC   | 19   | _   | Power-supply terminal                                                                                                                                                                                                                                                                                                                                                                 |

Submit Documentation Feedback

Copyright © 2011–2012, Texas Instruments Incorporated

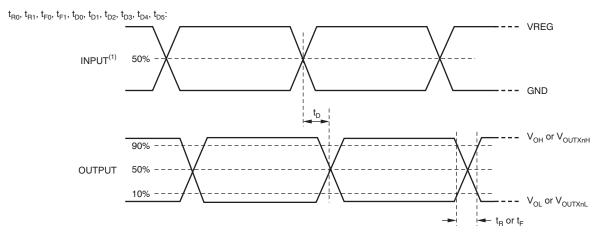

#### PARAMETRIC MEASUREMENT INFORMATION

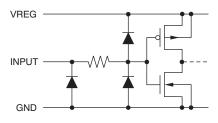

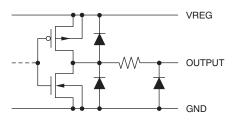

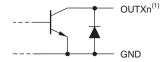

#### PIN EQUIVALENT INPUT/OUTPUT SCHEMATICS

Figure 1. SDTI/SCKI

Figure 2. SDTO/SCKO

(1) X = R/G/B, n = 0-3.

Figure 3. OUTR0 Through OUTB3

#### **TEST CIRCUITS**

- (1) X = R/G/B, n = 0-3.

- (2) C<sub>L</sub> includes measurement probe and stray capacitance.

Figure 4. Rise/Fall Time Test Circuit for OUTXn

(1) C<sub>L</sub> includes measurement probe and stray capacitance.

Figure 5. Rise/Fall Time Test Circuit for SDTO/SCKO

(1) X = R/G/B, n = 0-3.

Figure 6. Constant-Current Test Circuit for OUTXn

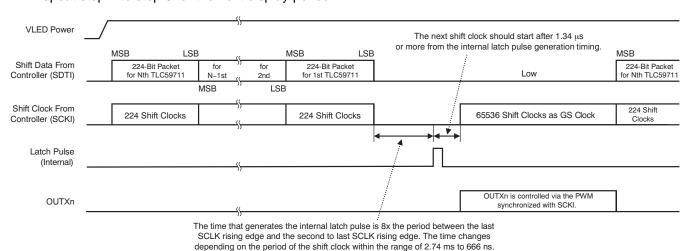

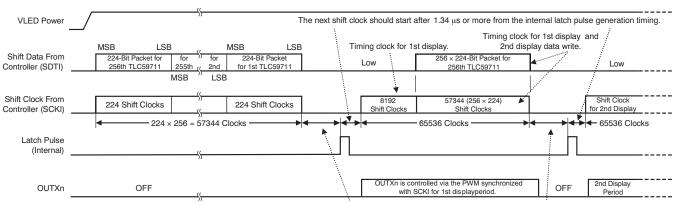

#### **TIMING DIAGRAMS**

(1) Input pulse rise and fall time is 1ns to 3ns.

Figure 7. Input Timing

(1) Input pulse rise and fall time is 1ns to 3ns.

Figure 8. Output Timing

Submit Documentation Feedback

-- GND

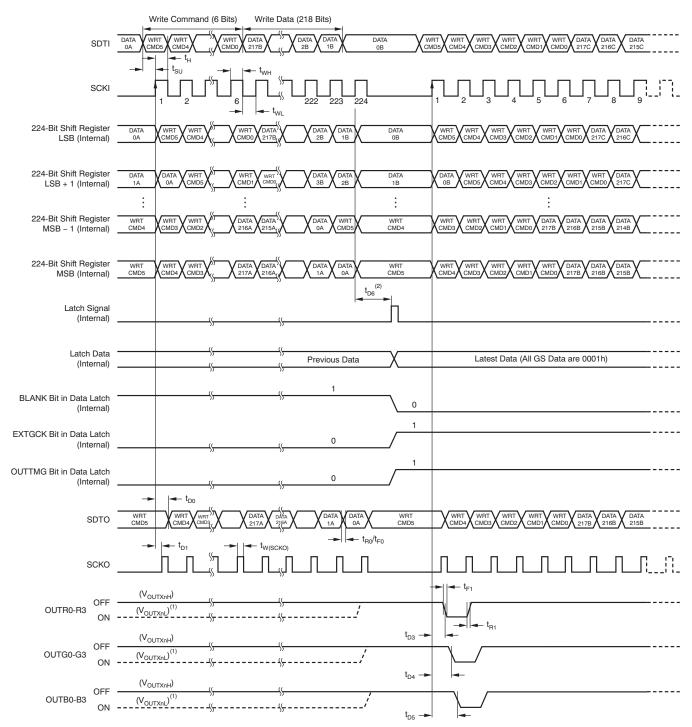

- (1) OUTXn on-off timing depends on previous GS data in the 218-bit data latch.

- (2) The propagation delay time shows the period from the rising edge of the last SCKI, not the 224th SCKI to the internal latch signal generation.

Figure 9. Data Write and OUTXn Switching Timing (OUTTMG = 1)

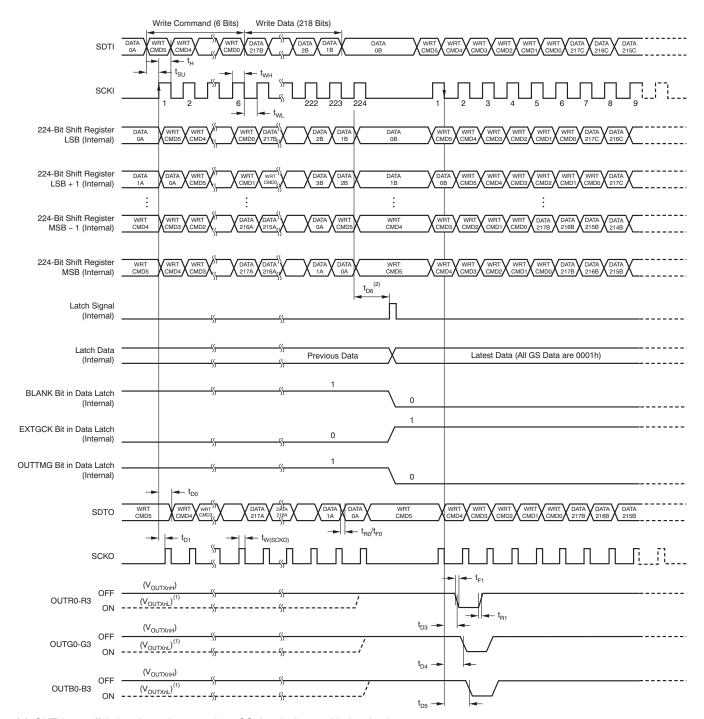

- (1) OUTXn on-off timing depends on previous GS data in the 218-bit data latch.

- (2) The propagation delay time shows the period from the rising edge of the last SCKI, not the 224th SCKI to the internal latch signal generation.

Figure 10. Data Write and OUTXn Switching Timing (OUTTMG = 0)

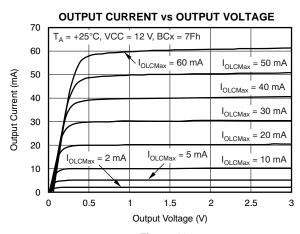

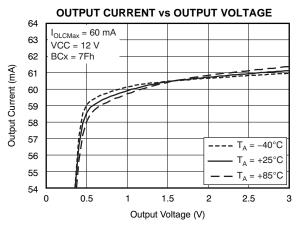

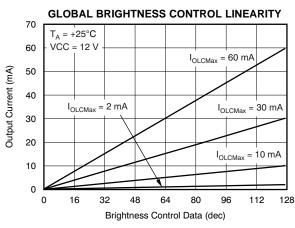

#### TYPICAL CHARACTERISTICS

At  $T_A = +25$ °C and VCC = 24 V, unless otherwise noted.

Figure 11.

Figure 12.

Figure 13.

Output Current (mA) Figure 14.

20

30

40

50

60

-2

-3

0

10

Figure 16.

#### TYPICAL CHARACTERISTICS (continued)

At  $T_A = +25$ °C and VCC = 24 V, unless otherwise noted.

Figure 17.

Figure 18.

#### LINEAR REGULATOR OUTPUT VOLTAGE vs LINEAR REGULATOR OUTPUT CURRENT

Figure 19.

## LINEAR REGULATOR OUTPUT VOLTAGE vs SUPPLY VOLTAGE

Figure 20.

## CONSTANT-CURRENT OUTPUT VOLTAGE WAVEFORM

Figure 21.

#### **APPLICATION INFORMATION**

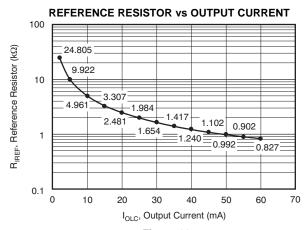

#### MAXIMUM CONSTANT SINK CURRENT SETTING

The maximum constant sink current value for each channel,  $I_{OLCMax}$ , is programmed through a single resistor,  $R_{IRFF}$ , placed between IREF and GND. The desired value can be calculated with Equation 1:

$$R_{IREF} (k\Omega) = \frac{V_{IREF} (V)}{I_{OLCMax} (mA)} \times 41$$

#### Where:

$V_{IREF}$  = the internal reference voltage on the IREF pin (1.21 V, typically, when the the global brightness control data are at maximum),

$$I_{OLCMax} = 2 \text{ mA to 60 mA}. \tag{1}$$

I<sub>OLCMax</sub> is the maximum current for each output. Each output sinks the I<sub>OLCMax</sub> current when it is turned on and global brightness control data (BC) are set to the maximum value of 7Fh (127d).

$R_{IREF}$  must be between 0.82 k $\Omega$  and 24.8 k $\Omega$  to hold  $I_{OLCMax}$  between 60 mA (typical) and 2 mA (typical). Otherwise, the output may be unstable. Output currents lower than 2 mA can be achieved by setting  $I_{OLCMax}$  to 2 mA or higher and then using global brightness control to lower the output current. The constant-current sink values for specific external resistor values are shown in Figure 11 and Table 1.

Table 1. Maximum Constant-Current versus External Resistor Value

| I <sub>OLCMax</sub> (mA) | R <sub>IREF</sub> (kΩ, Typical) |

|--------------------------|---------------------------------|

| 60                       | 0.827                           |

| 55                       | 0.902                           |

| 50                       | 0.992                           |

| 45                       | 1.1                             |

| 40                       | 1.24                            |

| 35                       | 1.42                            |

| 30                       | 1.65                            |

| 25                       | 1.98                            |

| 20                       | 2.48                            |

| 15                       | 3.31                            |

| 10                       | 4.96                            |

| 5                        | 9.92                            |

| 2                        | 24.8                            |

Product Folder Link(s): TLC59711

(2)

#### GLOBAL BRIGHTNESS CONTROL (BC) FUNCTION (SINK CURRENT CONTROL)

The TLC59711 has the capability to adjust all output currents of each color group (OUTR0-3, OUTG0-3, and OUTB0-3) to the same current value. This function is called *global brightness (BC) control*. The BC data are seven bits long, which allows each color group output current to be adjusted in 128 steps from 0% to 100% of the maximum output current, I<sub>OLCMax</sub>. The BC data are set via the serial interface. When the BC data are changed, the output current is changed immediately.

When the IC is powered on, all outputs are forced off by BLANK (bit 213). BLANK initializes in the data latch but the data in the 224-bit shift register and the 218-bit data latch are not set to a default value, except for the BLANK bit. Therefore, BC data must be written to the data latch when BLANK is set to '0'.

Equation 2 determines each color group maximum output sink current:

$$I_{OUT}$$

(mA) =  $I_{OLCMax}$  (mA) ×  $\left(\frac{BCX}{127d}\right)$

#### Where:

$I_{OLCMax}$  = the maximum channel current for each channel determined by  $R_{IREF}$  BC = the global brightness control value in the data latch for the specific color group (BCX = 0d to 127d, X = R/G/B)

Table 2 summarizes the BC data value versus the output current ratio and set current value.

Table 2. BC Data versus Current Ratio and Set Current Value

| BC DATA (Binary) | BC DATA (Decimal) | BC DATA<br>(Hex) | OUTPUT CURRENT<br>RATIO TO I <sub>OLCMax</sub><br>(%, Typical) | 60 mA I <sub>OLCMax</sub><br>(mA, Typical) | 2 mA I <sub>OLCMax</sub><br>(mA, Typical) |

|------------------|-------------------|------------------|----------------------------------------------------------------|--------------------------------------------|-------------------------------------------|

| 000 0000         | 0                 | 00               | 0                                                              | 0                                          | 0                                         |

| 000 0001         | 1                 | 01               | 0.8                                                            | 0.47                                       | 0.02                                      |

| 000 0010         | 2                 | 02               | 1.6                                                            | 0.94                                       | 0.03                                      |

| _                | _                 | _                | _                                                              | _                                          | _                                         |

| 111 1101         | 125               | 7D               | 98.4                                                           | 59.06                                      | 1.97                                      |

| 111 1110         | 126               | 7E               | 99.2                                                           | 59.53                                      | 1.98                                      |

| 111 1111         | 127               | 7F               | 100                                                            | 60                                         | 2                                         |

www.ti.com

#### **GRAYSCALE (GS) FUNCTION (PWM CONTROL)**

The TLC59711 can adjust the brightness of each output channel using the enhanced spectrum pulse width modulation (ES-PWM) control scheme. The PWM bit length for each output is 16 bits. The use of the 16-bit length results in 65536 brightness steps from 0% to 100% brightness.

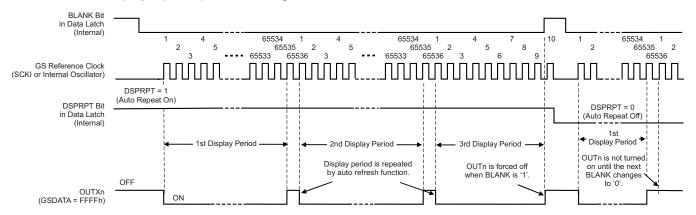

The PWM operation for all color groups is controlled by a 16-bit grayscale (GS) counter. The GS counter increments on each rising or falling edge of the external or internal GS reference clock that is selected by OUTTMG (bit 217) and EXTGCK (bit 216) in the data latch. When the external GS clock is selected, the GS counter uses the SCKI clock as the grayscale clock. The GS counter is reset to 0000h and all outputs are forced off when BLANK (bit 213) is set to '1' in the data latch and the counter value is held at '0' while BLANK is '1', even if the GS reference clock is toggled in between.

Equation 3 calculates each output (OUTXn) total on-time (t<sub>OUT\_ON</sub>):

$t_{OUT\ ON}$  (ns) =  $t_{GSCLK}$  (ns) × GSXn

#### Where:

t<sub>GSCLK</sub> = one period of the selected GS reference clock

(internal clock = 100ns typical, external clock = the period of SCKI)

GSXn = the programmed GS value for OUTXn (0d to 65535d)

(3)

Table 3 summarizes the GS data values versus the output total on-time and duty cycle. When the IC is powered up, BLANK (bit 213) is set to '1' to force all outputs off; however, the 224-bit shift register and the 218-bit data latch are not set to default values. Therefore, the GS data must be written to the data latch when BLANK (bit 213) is set to '0'.

Table 3. Output Duty Cycle and Total On-Time versus GS Data

| GS DATA (decimal) | GS DATA (hex) | ON-TIME DUTY (%) | GS DATA (decimal) | GS DATA (hex) | ON-TIME DUTY (%) |

|-------------------|---------------|------------------|-------------------|---------------|------------------|

| 0                 | 0             | 0                | 32768             | 8000          | 50.001           |

| 1                 | 1             | 0.002            | 32769             | 8001          | 50.002           |

| 2                 | 2             | 0.003            | 32770             | 8002          | 50.004           |

| 3                 | 3             | 0.005            | 32771             | 8003          | 50.005           |

| _                 |               | _                | _                 | _             | _                |

| 8191              | 1FFF          | 12.499           | 40959             | 9FFF          | 62.499           |

| 8192              | 2000          | 12.5             | 40960             | A000          | 62.501           |

| 8193              | 2001          | 12.502           | 40961             | A001          | 62.502           |

| _                 |               | _                | _                 | _             | _                |

| 16383             | 3FFF          | 24.999           | 49149             | BFFF          | 74.997           |

| 16384             | 4000          | 25               | 49150             | C000          | 74.998           |

| 16385             | 4001          | 25.002           | 49151             | C001          | 75               |

| _                 |               | _                | _                 | _             |                  |

| 24575             | 5FFF          | 37.499           | 57343             | DFFF          | 87.5             |

| 24576             | 6000          | 37.501           | 57344             | E000          | 87.501           |

| 24577             | 6001          | 37.502           | 57345             | E001          | 87.503           |

| _                 | _             | _                | _                 | _             | _                |

| 32765             | 7FFD          | 49.996           | 65533             | FFFD          | 99.997           |

| 32766             | 7FFE          | 49.998           | 65534             | FFFE          | 99.998           |

| 32767             | 7FFF          | 49.999           | 65535             | FFFF          | 100              |

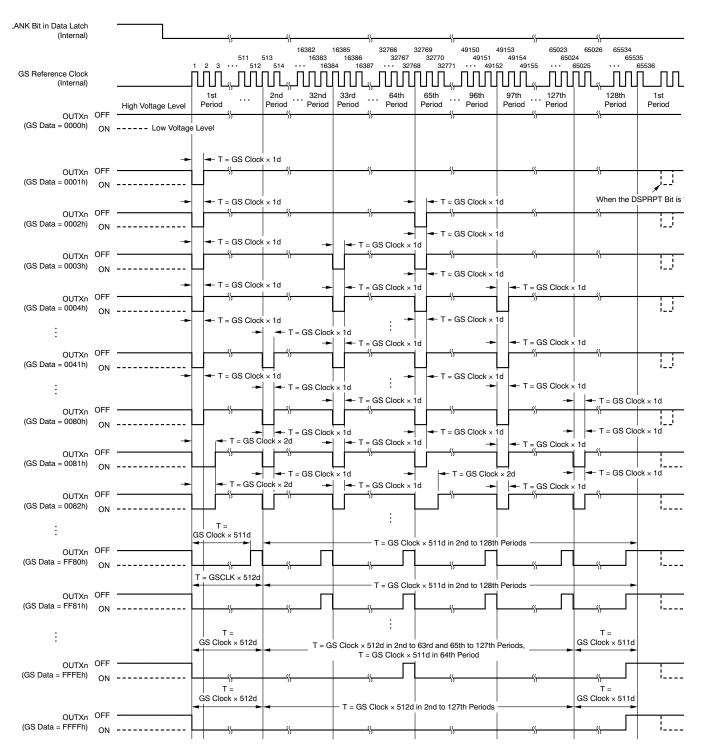

#### **ENHANCED SPECTRUM (ES) PWM CONTROL**

Enhanced spectrum (ES) PWM has the total display period divided into 128 display segments. The total display period refers the period between the first grayscale clock input to the 65536th grayscale clock input after BLANK (bit 213) is set to '0'. Each display period has 512 grayscale values, maximum. Each output on-time changes depending on the grayscale data. Refer to Table 4 for sequence information and Figure 22 for timing information.

Table 4. ES-PWM Drive Turn-On Time Length

| GS DATA (dec) | GS DATA (hex) | OUTn DRIVER OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0000h         | Does not turn on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1             | 0001h         | Turns on during one GS clock period in the 1st display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2             | 0002h         | Turns on during one GS clock period in the 1st and 65th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3             | 0003h         | Turns on during one GS clock period in the 1st, 33rd, and 65th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4             | 0004h         | Turns on during one GS clock period in the 1st, 33rd, 65th, and 97th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5             | 0005h         | Turns on during one GS clock period in the 1st, 17th, 33rd, 65th, and 97th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6             | 0006h         | Turns on during one GS clock period in the 1st, 17th, 33rd, 65th, 81st, and 97th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| _             | _             | The number of display periods that OUTXn is turned on during one GS clock is incremented by the GS data increasing in the following order. The order of display periods that the output turns on are: 1, 65, 33, 97, 17, 81, 49, 113, 9, 73, 41, 105, 25, 89, 57, 121, 5, 69, 37, 101, 21, 85, 53, 117, 13, 77, 45, 109, 29, 93, 61, 125, 3, 67, 35, 99, 19, 83, 51, 115, 11, 75, 43, 107, 27, 91, 59, 123, 7, 71, 39, 103, 23, 87, 55, 119, 15, 79, 47, 111, 31, 95, 63, 127, 2, 66, 34, 98, 18, 82, 50, 114, 10, 74, 42, 106, 26, 90, 58, 122, 6, 70, 38, 102, 22, 86, 54, 118, 14, 78, 46, 110, 30, 94, 62, 126, 4, 68, 36, 100, 20, 84, 52, 116, 12, 76, 44, 108, 28, 92, 60, 124, 8, 72, 40, 104, 24, 88, 56, 120, 16, 80, 48, 112, 32, 96, 64, and 128. |

| 127           | 007Fh         | Turns on during one GS clock period in the 1st to 127th display period, but does not turn on in the 128th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 128           | 0080h         | Turns on during one GS clock period in all display periods (1st to 128th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 129           | 0081h         | Turns on during two GS clock periods in the 1st display period and one GS clock period in the next display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| _             | _             | The number of display periods where OUTn is turned on for two GS clocks is incremented by the increased GS data similar to the previous case where the GS value is 1 trough 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 255           | 00FFh         | Turns on during two GS clock periods in the 1st to 127th display period, but only turns on during one GS clock period in the 128th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 256           | 0100h         | Turns on during two GS clock periods in all display periods (1st to 128th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 257           | 0101h         | Turns on during three GS clock periods in the 1st display period and two GS clock periods in the next display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| _             | _             | Display periods with OUTn turned on is incremented by the increased GS datasimilar to 0101h operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 65478         | FEFFh         | Turns on during 511 GS clock periods in the 1st to 127th display period, but only turns on 510 GS clock periods in the 128th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 65280         | FF00h         | Turns on during 511 GS clock periods in all display periods (1st to 128th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 65281         | FF01h         | Turns on during 512 GS clock periods in the 1st display period and 511 GS clock periods in the 2nd to 128th display periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| _             | _             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 65534         | FFFEh         | Turns on during 512 GS clock periods in the 1st to 63th and 65th to 127th display periods, and turns on 511 GS clock periods in the 64th and 128th display periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 65535         | FFFFh         | Turns on during 512 GS clock periods in the 1st to 127th display period, but only turns on 511 GS clock periods in the 128th display period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 22. ES-PWM Operation

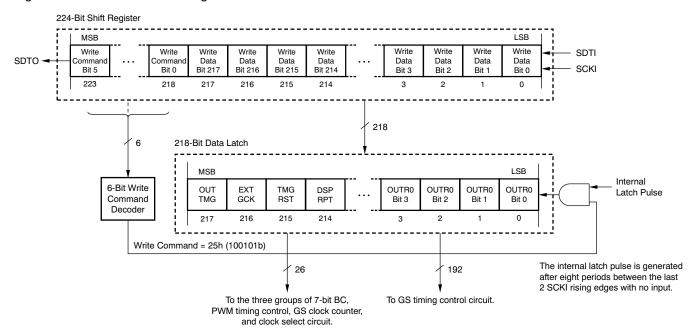

#### REGISTER AND DATA LATCH CONFIGURATION

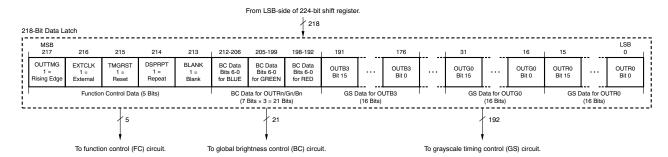

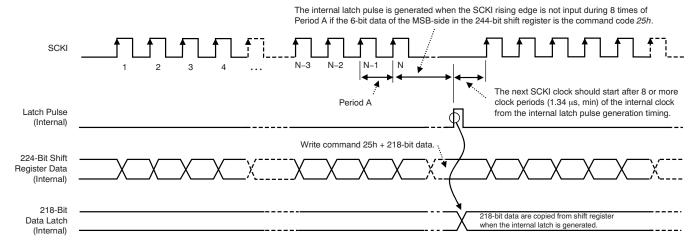

The TLC59711 has a 224-bit shift register and a 218-bit data latch that set grayscale (GS) data, global brightness control (BC), and function control (FC) data into the device. When the internal latch pulse is generated and the data of the six MSBs in the shift register are 25h, the 218 following data bits in the shift register are copied into the 218-bit data latch. If the data of the six MSBs is not 25h, the 218 data bits are not copied into the 218-bit data latch. The data in the data latch are used for GS, BC, and FC functions. Figure 23 shows the shift register and the data latch configuration.

Figure 23. Common Shift Register and Control Data Latch Configuration

#### 224-Bit Shift Register

The 224-bit shift register is used to input data from the SDTI pin with the SCKI clock into the TLC59711. The shifted data in this register is used for GS, BC, and FC. The six MSBs are used for the write command. The LSB of the register is connected to the SDTI pin and the MSB is connected to the SDTO pin. On each SCKI rising edge, the data on SDTI are shifted into the register LSB and all 224 bits are shifted towards the MSB. The register MSB is always connected to SDTO. When the device is powered up, the data in the 224-bit shift register is not set to any default value.

#### 218-Bit Data Latch

The 218-bit data latch is used to latch the GS, BC, and FC data. The 218 LSBs in the 244-bit shift register are copied to the data latch when the internal latch pulse is generated with the 6-bit write command, 25h (100101b). When the device is powered up, the data in the latch are not reset except for BLANK (bit 213) which is set to '1' to force all outputs off. Therefore, GS, BC, and FC data must be set to the proper values before BLANK is set to '0'. The 218-bit data latch configuration is shown in Figure 24 and the data bit assignment is shown in Table 5.

Figure 24. 218-Bit Data Latch Configuration

### Table 5. Data Latch Bit Assignment

|            | Table 3. Data Eaten bit Assignment |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| BIT NUMBER | BIT NAME                           | CONTROLLED CHANNEL/FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 15-0       | GSR0                               | GS data bits 15 to 0 for OUTR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 31-16      | GSG0                               | GS data bits 15 to 0 for OUTG0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 47-32      | GSB0                               | GS data bits 15 to 0 for OUTB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 63-48      | GSR1                               | GS data bits 15 to 0 for OUTR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 79-64      | GSG1                               | GS data bits 15 to 0 for OUTG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 95-80      | GSB1                               | GS data bits 15 to 0 for OUTB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |