Sample &

Buy

LMX2541 SNOSB31J – JULY 2009– REVISED DECEMBER 2014

# LMX2541 Ultra-Low Noise PLLatinum Frequency Synthesizer With Integrated VCO

Technical

Documents

### **1** Features

- Multiple Frequency Options Available (See *Device Comparison Table*)

- Frequencies From 31.6 MHz to 4000 MHz

- Very Low RMS Noise and Spurs

- -225 dBc/Hz Normalized PLL Phase Noise

- Integrated RMS Noise (100 Hz to 20 MHz)

- 2 mRad (100 Hz to 20 MHz) at 2.1 GHz

- 3.5 mRad (100 Hz to 20 MHz) at 3.5 GHz

- Ultra Low-Noise Integrated VCO

- External VCO Option (Internal VCO Bypassed)

- VCO Frequency Divider 1 to 63 (All Values)

- Programmable Output Power

- Up to 104-MHz Phase Detector Frequency

- Integrated Low-Noise LDOs

- Programmable Charge Pump Output

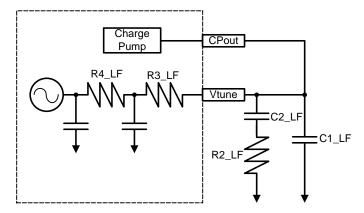

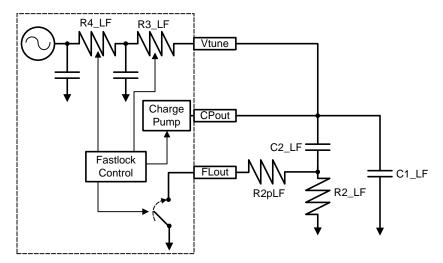

- Partially Integrated Loop Filter

- Digital Frequency Shift Keying (FSK) Modulation

Pin

- Integrated Reference Crystal Oscillator Circuit

- Hardware and Software Power Down

- FastLock Mode and VCO-Based Cycle Slip Reduction

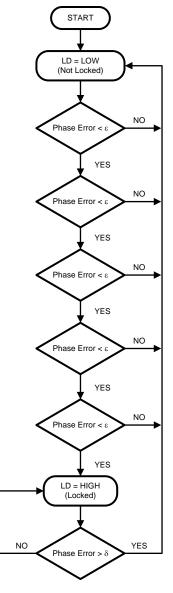

- Analog and Digital Lock Detect

- 1.6-V Logic Compatibility

### 2 Applications

- Wireless Infrastructure (UMTS, LTE, WiMax)

- Broadband Wireless

- Wireless Meter Reading

- Test and Measurement

- FM Mobile Radio

### 3 Description

Tools &

Software

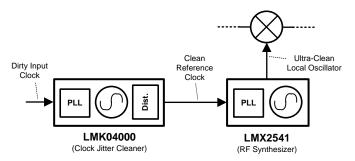

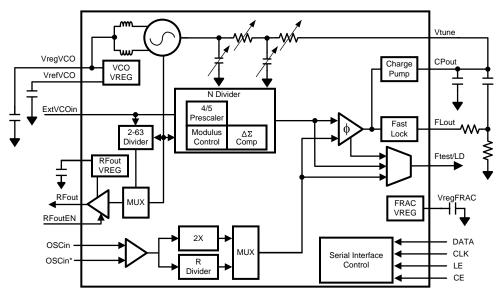

The LMX2541 device is an ultra low-noise frequency synthesizer which integrates a high-performance delta-sigma fractional N PLL, a VCO with fully integrated tank circuit, and an optional frequency divider. The PLL offers an unprecedented normalized noise floor of –225 dBc/Hz and can be operated with up to 104 MHz of phase-detector rate (comparison frequency) in both integer and fractional modes. The PLL can also be configured to work with an external VCO.

Support &

Community

**.**...

The LMX2541 integrates several low-noise, highprecision LDOs and output driver matching network to provide higher supply noise immunity and more consistent performance, while reducing the number of external components. When combined with a highquality reference oscillator, the LMX2541 generates a very stable, ultra low-noise signal.

The LMX2541 is offered in a family of 6 devices with varying VCO frequency range from 1990 MHz up to 4 GHz. Using a flexible divider, the LMX2541 can generate frequencies as low as 31.6 MHz.

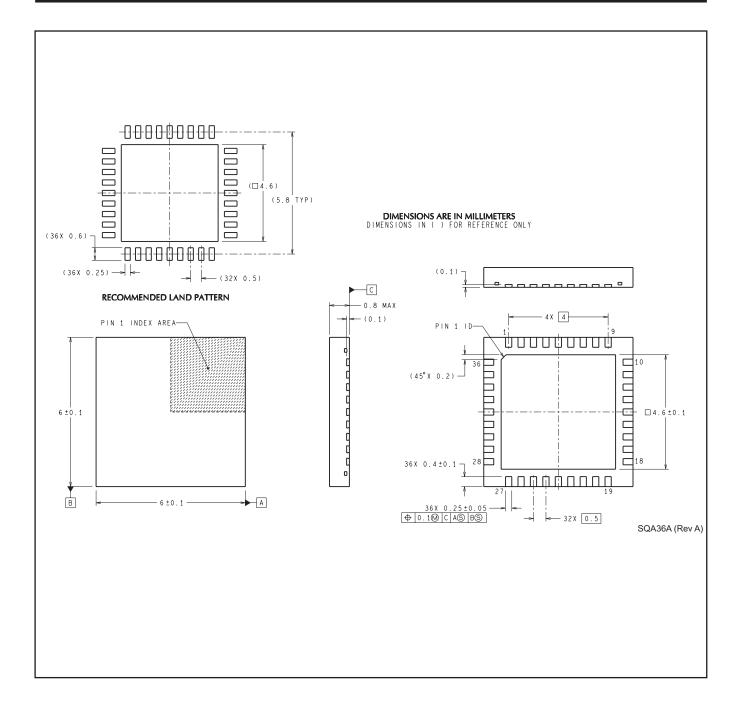

The LMX2541 is a monolithic integrated circuit, fabricated in a proprietary BiCMOS process. Device programming is facilitated using a three-wire MICROWIRE interface that can operate down to 1.6 volts. Supply voltage ranges from 3.15 V to 3.45 V. The LMX2541 is available in a 36-pin 6-mm  $\times$  6-mm  $\times$  0.8-mm WQFN package.

| Dovido information |           |                        |  |  |  |  |  |

|--------------------|-----------|------------------------|--|--|--|--|--|

| PART NUMBER        | PACKAGE   | VCO FREQUENCY<br>(MHz) |  |  |  |  |  |

| LMX2541SQ2060E     | WQFN (36) | 1990 - 2240            |  |  |  |  |  |

| LMX2541SQ2380E     | WQFN (36) | 2200 - 2530            |  |  |  |  |  |

| LMX2541SQ2690E     | WQFN (36) | 2490 - 2865            |  |  |  |  |  |

| LMX2541SQ3030E     | WQFN (36) | 2810 - 3230            |  |  |  |  |  |

| LMX2541SQ3320E     | WQFN (36) | 3130 - 3600            |  |  |  |  |  |

| LMX2541SQ3740E     | WQFN (36) | 3480 - 4000            |  |  |  |  |  |

### Device Information<sup>(1)</sup>

(1) For all available packages, see the orderable addendum at the end of the data sheet.

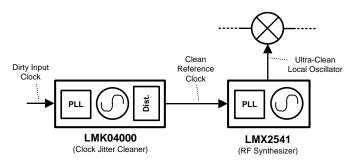

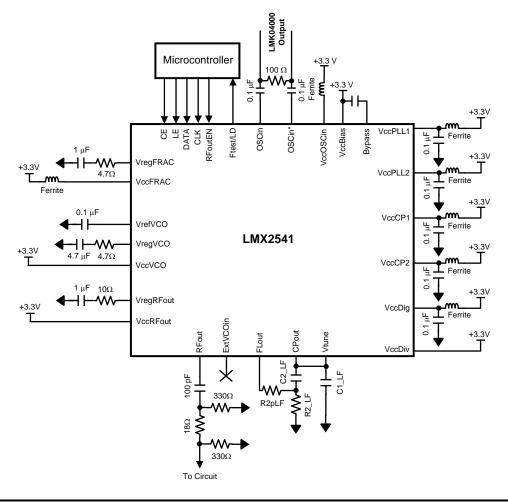

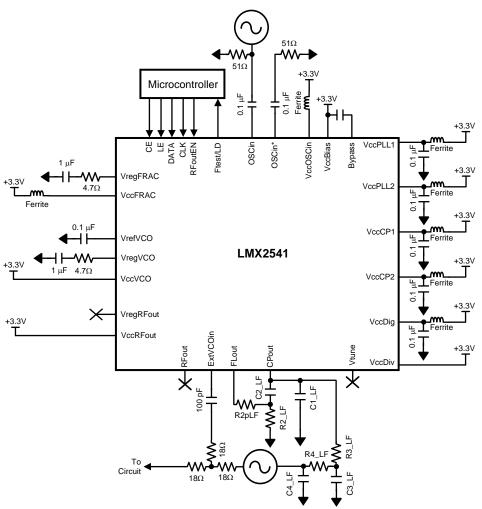

### System Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

1

2

3

4

5

6

7

8

9

7.1

7.2

#### Table of Contents Functional Block Diagrams ...... 25 9.2 9.3 9.4 9.5 Register Maps...... 38 9.6 10 Application and Implementation...... 51 Application Information..... 51 10.1 10.2 Typical Application ..... 59

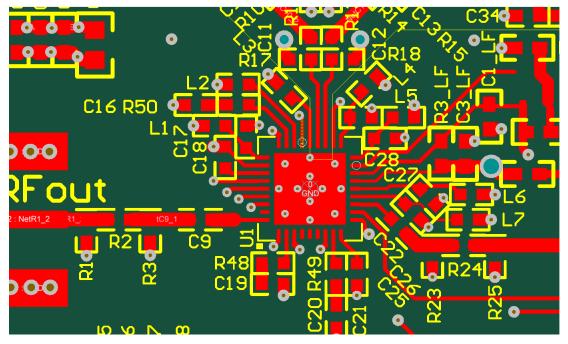

Layout Guidelines ...... 62

12.2 Layout Example ..... 63

Device and Documentation Support ...... 64

13.3 Electrostatic Discharge Caution ...... 64

Information ...... 64

Mechanical, Packaging, and Orderable

| 7.3  | Recommended Operating Conditions  |

|------|-----------------------------------|

| 7.4  | Thermal Information 6             |

| 7.5  | Electrical Characteristics7       |

| 7.6  | Timing Requirements 11            |

| 7.7  | Typical Characteristics 12        |

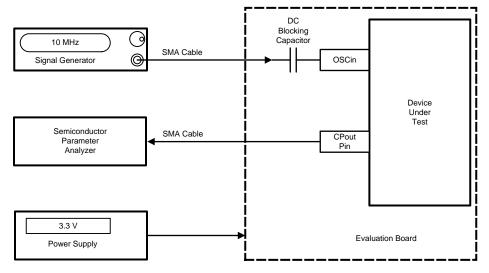

| Para | ameter Measurement Information 23 |

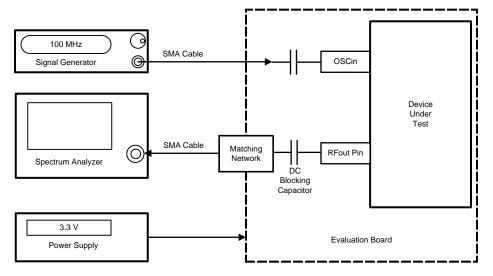

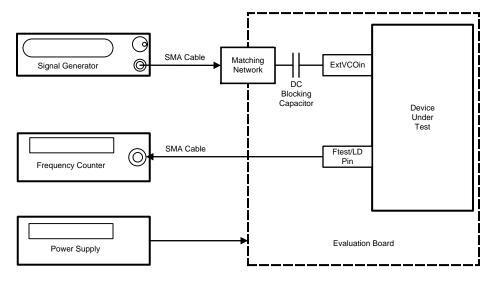

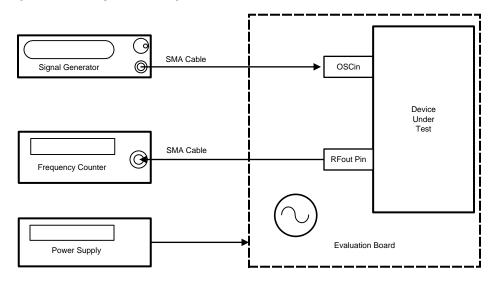

| 8.1  | Bench Test Setups 23              |

| Deta | ailed Description                 |

| 9.1  | Overview                          |

Features ..... 1

Applications ..... 1

Description ..... 1

Revision History..... 2

Device Comparison Table...... 3

Pin Configuration and Functions ...... 4

Absolute Maximum Ratings ...... 6

## Re

| CI | hanges from Revision I (February 2013) to Revision J                                                                                                                                                                                                                                 | Page |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. | 1    |

|    |                                                                                                                                                                                                                                                                                      |      |

| Cł | nanges from Revision H (February 2013) to Revision I | Page |

|----|------------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format   | 36   |

| History                                 |  |

|-----------------------------------------|--|

| evision I (February 2013) to Revision J |  |

|                                         |  |

| vision History                                                                                                                                                                                                                                                                   |      |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| es from Revision I (February 2013) to Revision J                                                                                                                                                                                                                                 | Page |  |  |  |  |

| ed ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation<br>ion, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and<br>chanical, Packaging, and Orderable Information section | 1    |  |  |  |  |

11

13

14

12.1

13.1

STRUMENTS

EXAS

### 5 Device Comparison Table

| VCO  | LMX2541SQ2060E |        | LMX2541SQ2380E |        | LMX2541SQ2690E |        | LMX2541SQ3030E |        | LMX2541SQ3320E |        | LMX2541SQ3740E |        |

|------|----------------|--------|----------------|--------|----------------|--------|----------------|--------|----------------|--------|----------------|--------|

| _DIV | Fmin           | Fmax   |

| 1    | 1990.0         | 2240.0 | 2200.0         | 2530.0 | 2490.0         | 2865.0 | 2810.0         | 3230.0 | 3130.0         | 3600.0 | 3480.0         | 4000.0 |

| 2    | 995.0          | 1120.0 | 1100.0         | 1265.0 | 1245.0         | 1432.5 | 1405.0         | 1615.0 | 1565.0         | 1800.0 | 1740.0         | 2000.0 |

| 3    | 663.3          | 746.7  | 733.3          | 843.3  | 830.0          | 955.0  | 936.7          | 1076.7 | 1043.3         | 1200.0 | 1160.0         | 1333.3 |

| 4    | 497.5          | 560.0  | 550.0          | 632.5  | 622.5          | 716.3  | 702.5          | 807.5  | 782.5          | 900.0  | 870.0          | 1000.0 |

| 5    | 398.0          | 448.0  | 440.0          | 506.0  | 498.0          | 573.0  | 562.0          | 646.0  | 626.0          | 720.0  | 696.0          | 800.0  |

| 6    | 331.7          | 373.3  | 366.7          | 421.7  | 415.0          | 477.5  | 468.3          | 538.3  | 521.7          | 600.0  | 580.0          | 666.7  |

| 7    | 284.3          | 320.0  | 314.3          | 361.4  | 355.7          | 409.3  | 401.4          | 461.4  | 447.1          | 514.3  | 497.1          | 571.4  |

| 8    | 248.8          | 280.0  | 275.0          | 316.3  | 311.3          | 358.1  | 351.3          | 403.8  | 391.3          | 450.0  | 435.0          | 500.0  |

|      |                |        |                |        |                |        |                |        |                |        |                |        |

| 63   | 31.6           | 35.6   | 34.9           | 40.2   | 39.5           | 45.5   | 44.6           | 51.3   | 49.7           | 57.1   | 55.2           | 63.5   |

All devices have continuous frequency coverage below a divide value of 8 (7 for most devices) down to their minimum frequency achievable with divide by 63. The numbers in bold show the upper end of this minimum continuous frequency range. For instance, the LMX2541SQ3740E option offers continuous frequency coverage from 55.2 MHz to 571.4 MHz and LMX2541SQ2060E offers continuous frequency coverage from 31.6 MHz to 280 MHz. If using the part in External VCO mode, all parts have roughly the same performance and any option will do.

LMX2541 SNOSB31J-JULY 2009-REVISED DECEMBER 2014

www.ti.com

### 6 Pin Configuration and Functions

### **Pin Functions**

| PIN      |                                                                         | TYPE         | DESCRIPTION                                                                                                     |  |  |  |

|----------|-------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.                                                                     | ТҮРЕ         | DESCRIPTION                                                                                                     |  |  |  |

| Bypass   | 30                                                                      | Bypass       | Put a cap to the VccBias pin.                                                                                   |  |  |  |

| CE       | 11                                                                      | CMOS         | Chip Enable.<br>The device needs to be programmed for this pin to properly power down the device.               |  |  |  |

| CLK      | 33                                                                      | High-Z Input | MICROWIRE clock input. High impedance CMOS input.<br>This pin is used for the digital FSK modulation feature.   |  |  |  |

| CPout    | 16                                                                      | Output       | utput Charge pump output.                                                                                       |  |  |  |

| DATA     | 32 High-Z Input MICROWIRE serial data input. High impedance CMOS input. |              |                                                                                                                 |  |  |  |

| ExtVCOin | 12                                                                      | RF Input     | Optional input for use with an external VCO.<br>This pin should be AC coupled if used or left open if not used. |  |  |  |

| FLout    | 17                                                                      | Output       | Fastlock output.                                                                                                |  |  |  |

| Ftest/LD | 20                                                                      | Output       | Software controllable multiplexed CMOS output.<br>Can be used to monitor PLL lock condition.                    |  |  |  |

| GND      | 0                                                                       | GND          | The DAP pad must be grounded.                                                                                   |  |  |  |

| GND      | 1                                                                       | GND          |                                                                                                                 |  |  |  |

| GND      | 10                                                                      | GND          |                                                                                                                 |  |  |  |

| GND      | 27                                                                      | GND          |                                                                                                                 |  |  |  |

| L1       | 4                                                                       | NC           | Do not connect this pin.                                                                                        |  |  |  |

| L2       | 6                                                                       | NC           | Do not connect this pin.                                                                                        |  |  |  |

| LE       | 34                                                                      | High-Z Input | MICROWIRE Latch Enable input. High impedance CMOS input.                                                        |  |  |  |

| Lmid     | 5                                                                       | NC           | Do not connect this pin.                                                                                        |  |  |  |

| NC       | 35                                                                      | NC           | No connect.                                                                                                     |  |  |  |

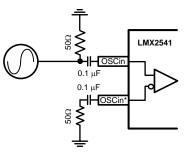

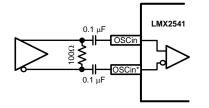

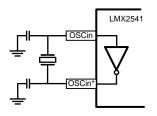

| OSCin    | 21                                                                      | High-Z Input | Oscillator input signal. If not being used with an external crystal, this input should be AC coupled.           |  |  |  |

### Pin Functions (continued)

| PIN       |     | TYPE                  | DESCRIPTION                                                                                                                                                    |  |  |

|-----------|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO. | TYPE                  | DESCRIPTION                                                                                                                                                    |  |  |

| OSCin*    | 22  | High-Z Input          | Complementary oscillator input signal. Can also be used with an external crystal. If not being used with an external crystal, this input should be AC coupled. |  |  |

| RFout     | 36  | RF Output             | RF output. Must be AC coupled if used.                                                                                                                         |  |  |

| RFoutEN   | 24  | Input                 | Software programmable output enable pin.                                                                                                                       |  |  |

| VccBias   | 29  | Supply                | Supply for Bias circuitry that is for the whole chip.                                                                                                          |  |  |

| VccCP1    | 14  | Supply                | Power supply for PLL charge pump.                                                                                                                              |  |  |

| VccCP2    | 18  | Supply                | Power supply for PLL charge pump.                                                                                                                              |  |  |

| VccDig    | 28  | Supply                | Supply for digital circuitry, such the MICROWIRE.                                                                                                              |  |  |

| VccDiv    | 31  | Supply                | Supply for the output divider                                                                                                                                  |  |  |

| VccFRAC   | 25  | Supply<br>(LDO Input) | Power Supply for the PLL fractional circuitry.                                                                                                                 |  |  |

| VccOSCin  | 23  | Supply                | Supply for the OSCin buffer.                                                                                                                                   |  |  |

| VccPLL1   | 13  | Supply                | Power supply for PLL.                                                                                                                                          |  |  |

| VccPLL2   | 19  | Supply                | Power supply for PLL.                                                                                                                                          |  |  |

| VccRFout  | 3   | Supply<br>(LDO Input) | Supply for the RF output buffer.                                                                                                                               |  |  |

| VccVCO    | 7   | Supply<br>(LDO Input) | Supply for the VCO.                                                                                                                                            |  |  |

| VregFRAC  | 26  | LDO Output            | Regulated power supply used for the fractional delta-sigma circuitry.                                                                                          |  |  |

| VregRFout | 2   | LDO Output            | LDO Output for RF output buffer.                                                                                                                               |  |  |

| VrefVCO   | 9   | LDO Bypass            | LDO Bypass                                                                                                                                                     |  |  |

| VregVCO   | 8   | LDO Output            | t LDO Output for VCO                                                                                                                                           |  |  |

| Vtune     | 15  | High-Z Input          | Tuning voltage input to the VCO.                                                                                                                               |  |  |

TEXAS INSTRUMENTS

www.ti.com

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                  |                                           | MIN  | MAX         | UNIT |

|------------------|-------------------------------------------|------|-------------|------|

| Vcc              | Power Supply Voltage                      | -0.3 | 3.6         | V    |

| V <sub>IN</sub>  | Input Voltage to pins other than Vcc Pins | -0.3 | (Vcc + 0.3) | V    |

| TL               | Lead Temperature (solder 4 sec.)          |      | 260         | °C   |

| T <sub>stg</sub> | Storage Temperature                       | -65  | 150         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) Never to exceed 3.6 V.

### 7.2 ESD Ratings

|                        |                         |                                                                                       | VALUE | UNIT |

|------------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Ele |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2500 |      |

|                        | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1750 | V    |

|                        |                         | Machine model (MM)                                                                    | ±400  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

|                |                                     | MIN  | NOM | MAX  | UNIT |

|----------------|-------------------------------------|------|-----|------|------|

| Vcc            | Power Supply Voltage (All Vcc Pins) | 3.15 | 3.3 | 3.45 | V    |

| T <sub>A</sub> | Ambient Temperature                 | -40  |     | 85   | °C   |

### 7.4 Thermal Information

|                                                                   | THERMAL METRIC <sup>(1)</sup>          | LMX2541<br>SQ2060E               | LMX2541<br>SQ2060E                | LMX2541<br>SQ2060E                | UNIT |

|-------------------------------------------------------------------|----------------------------------------|----------------------------------|-----------------------------------|-----------------------------------|------|

|                                                                   |                                        | 9 Thermal<br>Vias <sup>(2)</sup> | 13 Thermal<br>Vias <sup>(3)</sup> | 16 Thermal<br>Vias <sup>(4)</sup> | UNIT |

| $R_{\theta JA}$                                                   | Junction-to-ambient thermal resistance | 31.7                             | 30.3                              | 29.8                              | °C/W |

| $\psi_{JT}$ Junction-to-top characterization parameter 7.3 7.3 7. |                                        | 7.3                              | °C/w                              |                                   |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) Recommended for Most Reliable Solderability.

(3) Compromise Between Solderability, Heat Dissipation, and Fractional Spurs.

(4) Recommended for Optimal Heat Dissipation and Fractional Spurs.

### 7.5 Electrical Characteristics

$(3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{A} \le 85 \text{ }^{\circ}\text{C}; \text{ except as specified. Typical values are at Vcc} = 3.3 \text{ V}, 25 \text{ C}.)$

|                           | PARAMETER                                                 |                                                       | TEST CONDIT        | IONS         | MIN | TYP    | MAX | UNIT   |

|---------------------------|-----------------------------------------------------------|-------------------------------------------------------|--------------------|--------------|-----|--------|-----|--------|

| CURREN                    | IT CONSUMPTION                                            |                                                       |                    |              |     |        |     |        |

|                           | Entire Chip Supply Current with                           | Default Power                                         | VCO_DIV>1          |              |     | 170    | 204 |        |

| l <sub>cc</sub>           | all blocks enabled                                        | Mode (1)                                              | VCO_DIV=1          |              |     | 130    | 156 | mA     |

| PLL                       | Current for External VCO Mode                             | RFoutEN = LOV                                         | N                  |              |     | 72     | 94  | mA     |

| I <sub>DIV</sub>          | Current for Divider Only Mode                             | VCO_DIV >1<br>Default Power N                         | Default Power Mode |              |     |        | 110 | mA     |

| <sub>CC</sub> PD          | Power Down Current                                        | CE = 0 V, Devic                                       | ce Initialized     |              |     | 100    | 250 | μA     |

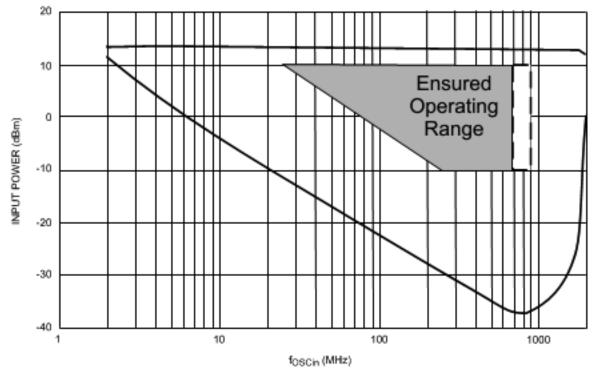

| OSCILLA                   | ATOR (NORMAL MODE OPERATIO                                | ON WITH XO=0)                                         |                    |              |     |        |     |        |

| I <sub>IH</sub> OSC<br>in | Oscillator Input High Current for<br>OSCin and OSCin*     | V <sub>IH</sub> = 2.75 V                              |                    |              |     |        | 300 | μA     |

| l <sub>IL</sub> OSCi<br>n | Oscillator Input Low Current for<br>OSCin and OSCin* pins | $V_{IL} = 0$                                          |                    | -100         |     |        | μA  |        |

|                           |                                                           | OSC_2X = 1                                            |                    |              | 5   |        | 52  |        |

| f <sub>OSCin</sub>        | OSCin Frequency Range                                     | 050 07 0                                              |                    | MODE = 0     | 5   |        | 700 | MHz    |

|                           |                                                           | $OSC_2X = 0$                                          |                    | MODE = 1     | 5   |        | 900 |        |

| dv <sub>OSCin</sub>       | Slew Rate                                                 | (2)                                                   |                    |              | 150 |        |     | V/µs   |

|                           | occillator Sepsitivity                                    |                                                       | 14.10              | Single-Ended | 0.2 |        | 2.0 | Van    |

| VOSCin                    | Oscillator Sensitivity                                    | dv <sub>OSCin</sub> ≥ 150 V                           | νμs                | Differential | 0.4 |        | 3.1 | Vpp    |

| OSCILLA                   | ATOR (CRYSTAL MODE WITH XO                                | =1)                                                   |                    |              |     |        |     |        |

| f <sub>XTAL</sub>         | Crystal Frequency Range                                   | V <sub>IH</sub> = 2.75 V                              |                    |              | 5   |        | 20  | MHz    |

| ESR <sub>XTA</sub><br>L   | Crystal Equivalent Series<br>Resistance                   | This a requirem<br>characteristic of                  |                    |              | 100 | Ω      |     |        |

| P <sub>XTAL</sub>         | Power Dissipation in Crystal                              | This requirement<br>characteristic of                 |                    | 200          |     | μW     |     |        |

| C <sub>OSCin</sub>        | Input Capacitance of OSCin                                |                                                       |                    |              |     | 6      |     | pF     |

|                           |                                                           | 1                                                     | PLL                |              |     |        |     |        |

| f <sub>PD</sub>           | Phase Detector Frequency                                  |                                                       |                    |              |     |        | 104 | MHz    |

|                           |                                                           | CPG = 1X                                              |                    |              |     | 100    |     |        |

|                           |                                                           | CPG = 2X                                              |                    |              |     | 200    |     |        |

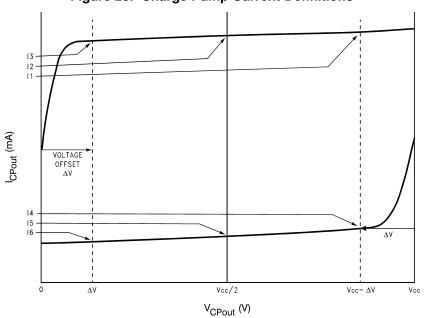

| CPout                     | Charge Pump<br>Output Current Magnitude                   | CPG = 3X                                              |                    |              |     | 300    |     | μA     |

|                           | Output Current Magnitude                                  |                                                       |                    |              |     |        |     |        |

|                           |                                                           | CPG=32X                                               |                    |              |     | 3200   |     |        |

| l <sub>CPout</sub> TR     | CP TRI-STATE Current                                      | 0.4 V < V <sub>CPout</sub> <                          | < Vcc - 0.4        |              |     | 1      | 5   | nA     |

| I <sub>CPout</sub> M<br>M | Charge Pump<br>Sink vs. Source Mismatch                   | $V_{CPout} = Vcc / 2$<br>$T_A = 25^{\circ}C$          | 2                  |              |     | 3%     | 10% |        |

| I <sub>CPout</sub> V      | Charge Pump<br>Current vs. CP Voltage Variation           | 0.4 V < V <sub>CPout</sub> <<br>T <sub>A</sub> = 25°C |                    | 4%           |     |        |     |        |

| I <sub>CPout</sub> T      | CP Current vs. Temperature Variation                      | V <sub>CPout</sub> = Vcc / 2                          | 2                  |              |     | 8%     |     |        |

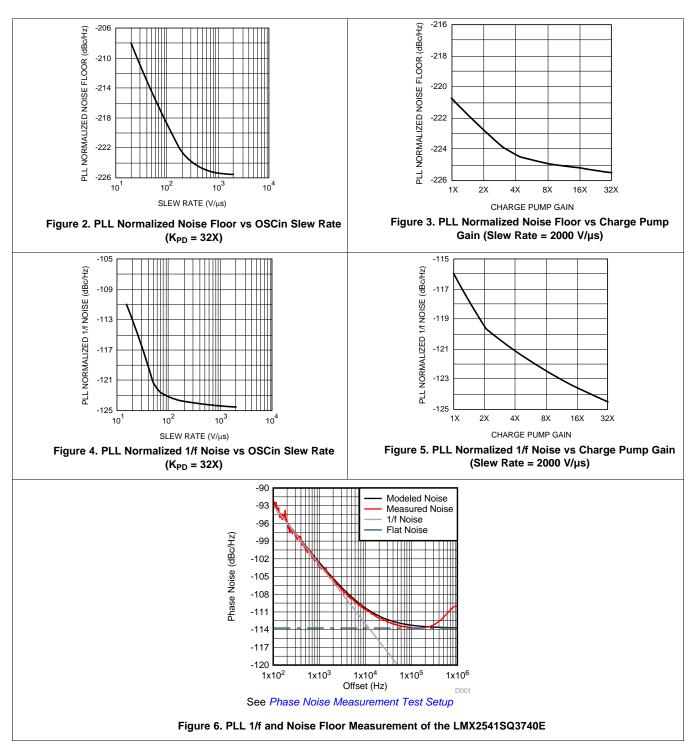

|                           | Normalized PLL 1/f Noise                                  | CPG = 1X                                              |                    |              |     | -116   |     | · //   |

| LN(f)                     | LN <sub>PLL_flicker</sub> (10 kHz)                        | CPG = 32X                                             |                    |              |     | -124.5 |     | dBc/H  |

| (3)                       | Normalized PLL Noise Floor                                | CPG = 1X                                              |                    |              |     | -220.8 |     | ID # 1 |

|                           | LNPLL_flat(1 Hz)                                          | CPG = 1X<br>CPG = 32X                                 |                    |              |     | -225.4 |     | dBc/H  |

(1) The LMX2541 RFout power level is programmable with the program words of VCOGAIN, OUTTERM, and DIVGAIN. Changing these words can change the output power of the VCO as well as the current consumption of the output buffer. For the purpose of consistency in electrical specifications, "Default Power Mode" is defined to be the settings of VCOGAIN = OUTTERM = DIVGAIN = 12.

(2) Not tested in production. Specified by characterization. OSCin is tested only to 400 MHz.

(3) See Application and Implementation for more details on these parameters.

ISTRUMENTS

www.ti.com

XAS

### **Electrical Characteristics (continued)**

$(3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{A} \le 85 \text{ }^{\circ}\text{C}; \text{ except as specified. Typical values are at Vcc = 3.3 V, 25 C.})$

|                       | PARAMETER                                                  | TEST CONDITIO                                                  | NS            | MIN     | TYP     | MAX  | UNIT     |

|-----------------------|------------------------------------------------------------|----------------------------------------------------------------|---------------|---------|---------|------|----------|

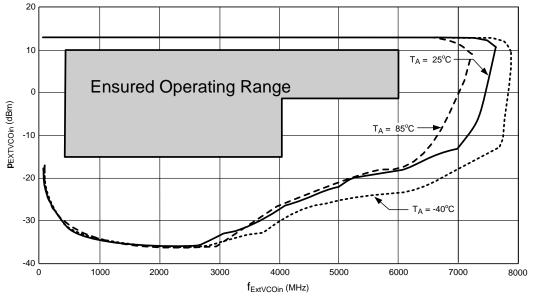

|                       |                                                            | RFout Buffer Enabled and VCO_E                                 | DIV > 1       | 400     |         | 4000 |          |

| f <sub>ExtVCOin</sub> | PLL Input Frequency                                        | RFout Buffer Disabled and VCO_                                 | DIV = 1       | 400     |         | 6000 | MHz      |

| P <sub>ExtVCOi</sub>  | PLL Input Sensitivity                                      | f <sub>ExtVCOin</sub> ≤ 4 GHz                                  |               | -15     |         | 10   | alD-re   |

| n                     | ( <sup>(2)</sup> applies to Max Limit Only)                | f <sub>ExtVCOin</sub> > 4 GHz                                  |               | -5      |         | 10   | dBm      |

| VCO SPI               | ECIFICATIONS                                               |                                                                |               |         |         |      |          |

|                       |                                                            |                                                                | 2060E         | 1990    |         | 2240 |          |

|                       |                                                            |                                                                | 2380E         | 2200    |         | 2530 |          |

| ¢                     | Internal VCO Fraguenov Bongo                               | Mode = Full Chip Mode<br>This is the frequency before the      | 2690E         | 2490    |         | 2865 | MHz      |

| f <sub>VCO</sub>      | Internal VCO Frequency Range                               | VCO divider.                                                   | 3030E         | 2810    |         | 3230 |          |

|                       |                                                            |                                                                | 3320E         | 3130    |         | 3600 |          |

|                       |                                                            |                                                                | 3740E         | 3480    |         | 4000 |          |

| ∆T <sub>CL</sub>      | Maximum Allowable Temperature<br>Drift for Continuous Lock | (2),(4)                                                        |               | 125     |         |      | °C       |

|                       |                                                            |                                                                | 2060E         |         | 3.5     |      |          |

|                       |                                                            |                                                                | 2380E         |         | 2.8     |      |          |

| _                     |                                                            | Maximum Frequency                                              | 2690E         |         | 1.6     |      | dBm      |

| PRFout                | RF Output Power                                            | Default Power Mode<br>VCO_DIV=1                                | 3030E         |         | 1.2     |      |          |

|                       |                                                            | _                                                              | 3320E         |         | 0.2     |      |          |

|                       |                                                            | 3740E                                                          |               | -0.3    |         |      |          |

|                       |                                                            | Fixed Temperature with 100 MHz frequency change at the output  |               |         | 0.3     |      |          |

| ∆P <sub>RFout</sub>   | Change in Output Power                                     | Fixed frequency with a change ov temperature range             | er the entire |         | 0.4     |      | dB       |

|                       |                                                            | The lower number in the range                                  | 2060E         |         | 13 - 23 |      |          |

|                       |                                                            | applies when the VCO is at its lowest frequency and the higher | 2380E         |         | 16 - 30 |      |          |

| K                     | Fine Tuning Sensitivity                                    | number applies when the VCO                                    | 2690E         |         | 17 - 32 |      | MHz/V    |

| K <sub>Vtune</sub>    |                                                            | is at its highest frequency. A linear approximation can be     | 3030E         |         | 20 - 37 |      | IVINZ/ V |

|                       | used for frequencies between                               | 3320E                                                          |               | 21 - 37 |         |      |          |

|                       | these two cases.                                           | 3740E                                                          |               | 24 - 42 |         |      |          |

|                       | Second Harmonic                                            | Default Power Mode                                             | VCO_DIV = 2   |         | -20     |      |          |

| HS <sub>RFout</sub>   | (5)                                                        | 50 Ω Load                                                      | VCO_DIV = 3   |         | -20     |      | dBc      |

|                       | Duty Cycle Error                                           | Default Power Mode                                             | VCO_DIV = 2   |         | 3%      |      |          |

| DE <sub>RFout</sub>   | (5)                                                        | 50 Ω Load                                                      | VCO_DIV = 3   |         | 3%      |      |          |

| PSH <sub>VCO</sub>    | VCO Frequency Pushing                                      | C <sub>VregVCO</sub> = 4.7 μF, Open Loop                       | ł             |         | 600     |      | kHz/V    |

|                       |                                                            | VSWR 1.7 to 1                                                  | VCO_DIV = 1   |         | ±800    |      |          |

| FULVCO                | VCO Frequency Pulling                                      | (6 dB Pad)                                                     | VCO_DIV > 1   |         | ±60     |      | kHz      |

<sup>(4)</sup> Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the R0 register was last programmed, and still have the device stay in lock. The action of programming the R0 register, even to the same value, activates a frequency calibration routine. This implies that the device will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reload the R0 register to ensure that it stays in lock. Regardless of what temperature the device was initially programmed at, the temperature can never drift outside the frequency range of -40°C ≤T<sub>A</sub>≤ 85°C without violating specifications.

<sup>(5)</sup> The duty cycle error (DE) and second harmonic (HS) are theoretically related by the equation HS = 10 log| 2π · DE | - 6 dB. A square wave with 3% duty cycle theoretically has a second harmonic of -20 dBc.

### **Electrical Characteristics (continued)**

|                      | PARAMETER                |                                      | TEST CONDITIONS |                |        | TYP    | MAX | UNIT       |  |

|----------------------|--------------------------|--------------------------------------|-----------------|----------------|--------|--------|-----|------------|--|

|                      |                          | Integration Dead                     | huidth          | 2060E          |        | 1.6    |     |            |  |

|                      |                          | Integration Band<br>= 100 Hz to 20 M | ИНz             | 2380E          |        | 1.8    |     |            |  |

| _                    |                          | Middle VCO Fre                       |                 | 2690E          |        | 2.1    |     |            |  |

| $\sigma_{\Phi}$      | RMS Phase Error          | 100 MHz Wenze<br>Reference           | el Crystal      | 3030E          |        | 2.1    |     | mRad       |  |

|                      |                          | Integer Mode                         | -               | 3320E          |        | 2.3    |     |            |  |

|                      |                          | Optimized Loop                       | Bandwidth       | 3740E          |        | 2.6    |     |            |  |

| CO PH                | ASE NOISE <sup>(6)</sup> |                                      |                 |                |        |        |     |            |  |

|                      |                          |                                      | 10-kHz Offset   |                |        | -89.7  |     |            |  |

|                      |                          | fpEout =                             | 100-k           | 100-kHz Offset |        | -113.7 |     |            |  |

|                      |                          | f <sub>RFout</sub> =<br>Min VCO      | 1-MHz Offset    |                | -      | -134.9 |     |            |  |

|                      |                          | Frequency                            | 10-MHz Offset   |                | -      | -155.4 |     |            |  |

| (£)                  | Phase Noise              |                                      | 20-MHz Offset   |                | -      | -160.3 |     | dDa/U=     |  |

| _(f) <sub>Fout</sub> | 2060E                    |                                      | 10-kHz Offset   |                |        | -86.5  |     | dBc/Hz     |  |

|                      |                          | f <sub>RFout</sub> =                 | 100-kHz Offset  |                | -      | -111.4 |     |            |  |

|                      |                          | Max VCO                              | 1-MF            | Iz Offset      | -      | -132.8 |     |            |  |

|                      |                          | Frequency                            | 10-M            | Hz Offset      | -      | -153.4 |     |            |  |

|                      |                          |                                      | 20-M            | Hz Offset      | -      | -158.5 |     |            |  |

|                      |                          |                                      |                 | Hz Offset      |        | -87.9  |     |            |  |

|                      | f <sub>RFout</sub> =     | 100-k                                | 100-kHz Offset  |                | -112.7 |        |     |            |  |

|                      |                          | f <sub>RFout</sub> =<br>Min VCO      | 1-MF            | Iz Offset      | -      | -133.8 |     |            |  |

|                      |                          | Noise                                | 10-M            | Hz Offset      | -      | -154.2 |     |            |  |

| ( <b>f</b> )         | Phase Noise              |                                      | 20-M            | Hz Offset      | -159.5 |        |     | dBc/Hz     |  |

| _(f) <sub>Fout</sub> | 2380E                    |                                      | 10-kł           | Hz Offset      |        | -83.4  |     | UDC/NZ     |  |

|                      |                          | f <sub>RFout</sub> =                 | 100-k           | Hz Offset      | -      | -109.1 |     |            |  |

|                      |                          | Max VCO                              | 1-MF            | 1-MHz Offset   |        | -130.8 |     | 1          |  |

|                      |                          | Frequency                            | 10-M            | Hz Offset      | -      | -151.8 |     |            |  |

|                      |                          |                                      | 20-M            | Hz Offset      | -      | -157.5 |     | 1          |  |

|                      |                          |                                      | 10-kł           | Hz Offset      |        | -86.9  |     |            |  |

|                      |                          | f <sub>RFout</sub> =                 | 100-k           | Hz Offset      | -      | -111.8 |     |            |  |

|                      |                          | Min VCO                              | 1-MF            | Iz Offset      | -      | -133.3 |     |            |  |

|                      |                          | Frequency                            | 10-M            | Hz Offset      | -      | -154.2 |     |            |  |

| (f)_                 | Phase Noise              |                                      | 20-M            | Hz Offset      |        | -159.4 |     | -/D - // ! |  |

| _(f) <sub>Fout</sub> | 2690E                    |                                      | 10-kł           | Hz Offset      |        | -82.3  |     | dBc/Hz     |  |

|                      |                          | fpeout =                             | 100-k           | Hz Offset      | -      | -108.4 |     |            |  |

|                      |                          | f <sub>RFout</sub> =<br>Max VCO      | 1-MF            | -              | -130.3 |        |     |            |  |

|                      |                          | Frequency                            | 10-M            | Hz Offset      | -      | -151.1 |     |            |  |

|                      |                          |                                      | 20-M            | Hz Offset      | -      | -156.7 |     |            |  |

$(3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{A} \le 85 \text{ }^{\circ}\text{C}; \text{ except as specified. Typical values are at Vcc} = 3.3 \text{ V}, 25 \text{ C}.)$

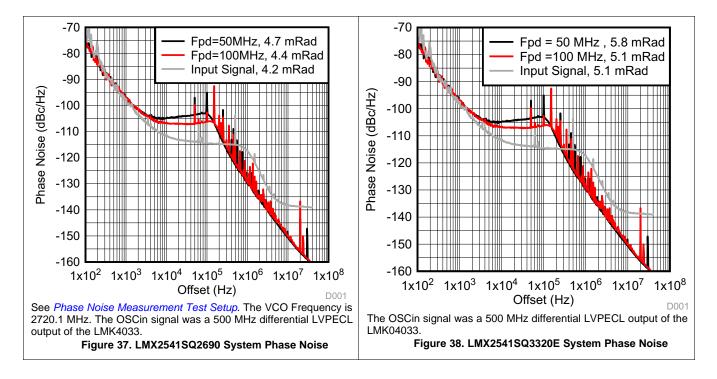

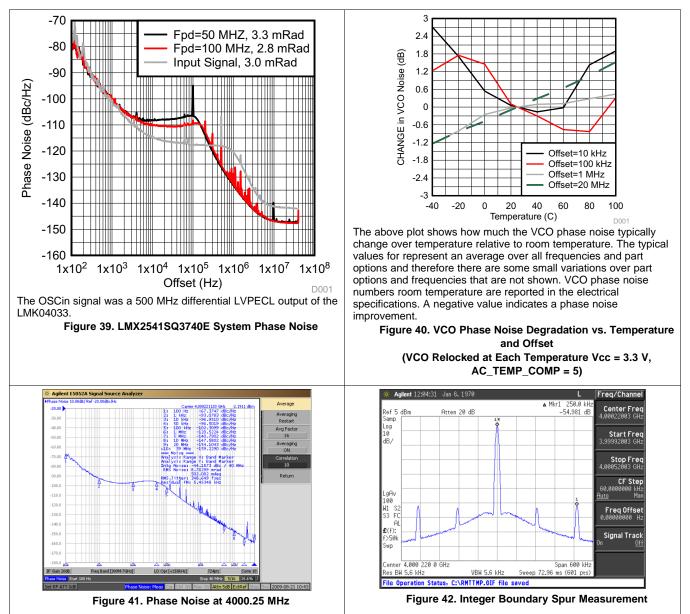

<sup>(6)</sup> The VCO phase noise is measured assuming that the loop bandwidth is sufficiently narrow that the VCO noise dominates. The phase noise is measured with AC\_TEMP\_COMP = 5 and the device is reloaded at each test frequency. The typical performance characteristics section shows how the VCO phase noise varies over temperature and frequency.

### **Electrical Characteristics (continued)**

$(3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{A} \le 85 \text{ }^{\circ}\text{C}; \text{ except as specified. Typical values are at Vcc} = 3.3 \text{ V}, 25 \text{ C}.)$

|                      | PARAMETER                   |                                 | TEST CONDITIONS | MIN TYP | MAX | UNIT     |  |  |

|----------------------|-----------------------------|---------------------------------|-----------------|---------|-----|----------|--|--|

|                      |                             |                                 | 10-kHz Offset   | -86.1   |     |          |  |  |

|                      |                             | f <sub>RFout</sub> =            | 100-kHz Offset  | -110.5  |     |          |  |  |

|                      |                             | Min VCO                         | 1-MHz Offset    | -132.0  |     | 1        |  |  |

|                      |                             | Frequency                       | 10-MHz Offset   | -152.2  |     |          |  |  |

|                      | Phase Noise                 |                                 | 20-MHz Offset   | -157.1  |     | -        |  |  |

| L(f) <sub>Fout</sub> | 3030E                       |                                 | 10-kHz Offset   | -82.2   |     | dBc/Hz   |  |  |

|                      |                             | f <sub>RFout</sub> =            | 100-kHz Offset  | -107.7  |     |          |  |  |

|                      |                             | Max VCO                         | 1-MHz Offset    | -129.4  |     |          |  |  |

|                      |                             | Frequency                       | 10-MHz Offset   | -150.5  |     |          |  |  |

|                      |                             |                                 | 20-MHz Offset   | -156.1  |     | -        |  |  |

|                      |                             |                                 | 10-kHz Offset   | -84.1   |     |          |  |  |

|                      |                             | f                               | 100-kHz Offset  | -109.1  |     |          |  |  |

|                      |                             | f <sub>RFout</sub> =<br>Min VCO | 1-MHz Offset    | -130.7  |     |          |  |  |

|                      |                             | Frequency                       | 10-MHz Offset   | -151.6  |     | dBc/Hz   |  |  |

|                      | Phase Noise                 |                                 | 20-MHz Offset   | -156.9  |     |          |  |  |

| L(f) <sub>Fout</sub> | 3320E                       |                                 | 10-kHz Offset   | -82.0   |     |          |  |  |

|                      |                             | f                               | 100-kHz Offset  | -107.0  |     |          |  |  |

|                      |                             | f <sub>RFout</sub> =<br>Max VCO | 1-MHz Offset    | -128.5  |     |          |  |  |

|                      |                             | Frequency                       | 10-MHz Offset   | -149.6  |     |          |  |  |

|                      |                             |                                 | 20-MHz Offset   | -155.2  |     | <u> </u> |  |  |

|                      |                             |                                 | 10-kHz Offset   | -83.9   |     |          |  |  |

|                      | f                           |                                 | 100-kHz Offset  | -108.3  |     |          |  |  |

|                      |                             | f <sub>RFout</sub> =<br>Min VCO | 1-MHz Offset    | -129.9  |     |          |  |  |

|                      |                             | Frequency                       | 10-MHz offset   | -150.6  |     |          |  |  |

| . (1)                | Phase Noise                 |                                 | 20-MHz Offset   | -156.5  |     | dBc/Hz   |  |  |

| L(f) <sub>Fout</sub> | 3740E                       |                                 | 10-kHz Offset   | -81.6   |     |          |  |  |

|                      |                             | f <sub>RFout</sub> =            | 100-kHz Offset  | -106.5  |     |          |  |  |

|                      |                             | Max VCO                         | 1-MHz Offset    | -127.7  |     |          |  |  |

|                      |                             | Frequency                       | 10-MHz Offset   | -148.6  |     |          |  |  |

|                      |                             |                                 | 20-MHz Offset   | -154.2  |     |          |  |  |

| DIGITA               | L INTERFACE (DATA, CLK, LE, | CE, Ftest/LD, FLo               | ut,RFoutEN)     |         |     |          |  |  |

| V <sub>IH</sub>      | High-Level Input Voltage    |                                 |                 | 1.6     | Vcc | V        |  |  |

| V <sub>IL</sub>      | Low-Level Input Voltage     |                                 |                 |         | 0.4 | V        |  |  |

| I <sub>IH</sub>      | High-Level Input Current    | V <sub>IH</sub> = 1.75, XO      | 0 = 0           | -5      | 5   | μA       |  |  |

| IIL                  | Low-Level Input Current     | V <sub>IL</sub> = 0 V , XO      | = 0             | -5      | 5   | μA       |  |  |

| V <sub>OH</sub>      | High-Level Output Voltage   | I <sub>OH</sub> = 500 μA        |                 | 2       |     | V        |  |  |

| V <sub>OL</sub>      | Low-Level Output Voltage    | I <sub>OL</sub> = -500 μA       |                 | 0       | 0.4 | V        |  |  |

| I <sub>Leak</sub>    | Leakage Current             | Ftest/LD and F                  | Lout Pins Only  | -5      | 5   | μA       |  |  |

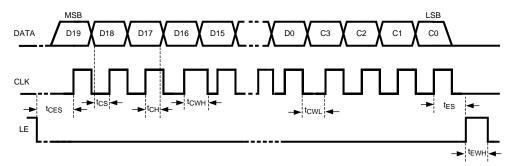

### 7.6 Timing Requirements

|                  |                             |              | MIN | NOM | MAX | UNIT |

|------------------|-----------------------------|--------------|-----|-----|-----|------|

| t <sub>CE</sub>  | Clock to Enable Low Time    | See Figure 1 | 25  |     |     | ns   |

| t <sub>CS</sub>  | Data to Clock Set Up Time   | See Figure 1 | 25  |     |     | ns   |

| t <sub>CH</sub>  | Data to Clock Hold Time     | See Figure 1 | 20  |     |     | ns   |

| t <sub>CWH</sub> | Clock Pulse Width High      | See Figure 1 | 25  |     |     | ns   |

| t <sub>CWL</sub> | Clock Pulse Width Low       | See Figure 1 | 25  |     |     | ns   |

| t <sub>CES</sub> | Enable to Clock Set Up Time | See Figure 1 | 25  |     |     | ns   |

| t <sub>EWH</sub> | Enable Pulse Width High     | See Figure 1 | 25  |     |     | ns   |

Figure 1. Serial Data Timing Diagram

LMX2541 SNOSB31J-JULY 2009-REVISED DECEMBER 2014 TEXAS INSTRUMENTS

www.ti.com

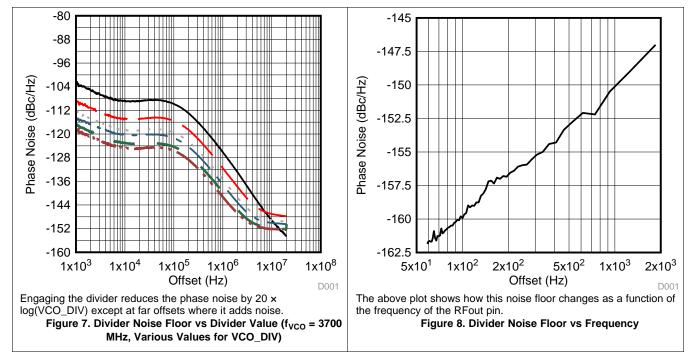

### 7.7 Typical Characteristics

### 7.7.1 Not Ensured Characteristics

### Not Ensured Characteristics (continued)

### Table 1. Relative VCO Phase Noise Over Temperature Drift (AC\_TEMP\_COMP = 24, Vcc = 3.3 V)<sup>(1)</sup>

| TEMPERATURE |         | PHASE NOISE CHANGE IN CELSIUS FOR VARIOUS OFFSETS                             |         |       |        |        |  |  |

|-------------|---------|-------------------------------------------------------------------------------|---------|-------|--------|--------|--|--|

| LOCK        | CURRENT | 10 kHz                                                                        | 100 kHz | 1 MHz | 10 MHz | 20 MHz |  |  |

| -40         | -40     | +0.4                                                                          | -2.0    | -1.6  | -1.8   | -1.6   |  |  |

| -40         | 25      | +0.3                                                                          | +0.5    | +0.5  | +0.5   | +0.4   |  |  |

| -40         | 85      | +0.9                                                                          | +2.0    | +2.4  | +2.5   | +2.3   |  |  |

| 25          | -40     | +0.2                                                                          | -2.2    | -1.7  | -2.0   | -1.8   |  |  |

| 25          | 25      | This is the default condition to which these other numbers are normalized to. |         |       |        |        |  |  |

| 25          | 85      | +0.6                                                                          | +1.5    | +2.0  | +2.0   | +1.9   |  |  |

| 85          | -40     | +0.2                                                                          | -2.2    | -1.7  | -1.9   | -1.8   |  |  |

| 85          | 25      | +0.2                                                                          | +0.2    | +0.3  | +0.2   | +0.2   |  |  |

| 85          | 85      | +0.6                                                                          | +1.8    | +2.2  | +2.3   | +2.1   |  |  |

(1) The table shows the typical degradation for VCO phase noise when the VCO is locked at one temperature and the temperature is allowed to drift to another temperature. A negative value indicates a phase noise improvement.

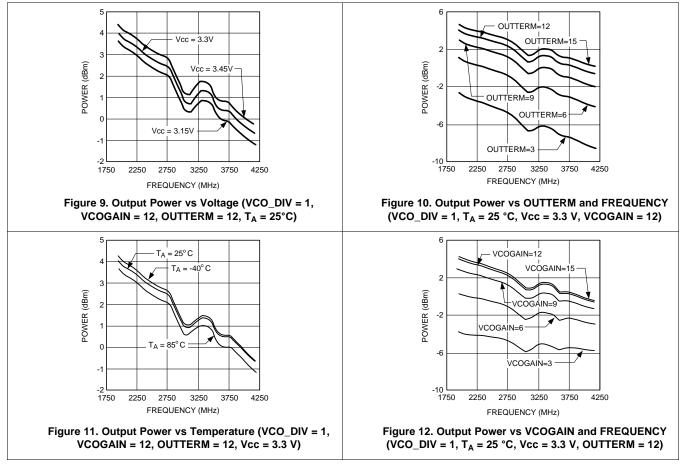

### 7.7.2 Output Power in Bypass Mode

The following plots show the trends in output power as a function of temperature, voltage, and frequency. For states where VCOGAIN and OUTTERM are not 12, the table below shows how the output power is modified based on these programmable settings. The measurement of the output power is sensitive to the test circuit. All the numbers in the electrical specifications and typical performance curves were obtained from a characterization setup that accommodate temperature testing and changing of parts. In a more optimized setup the measured RF output power is typically on the order of 1.5 to 2.4 dB higher.

|         |    |      |      | VCOGAIN |      |      |

|---------|----|------|------|---------|------|------|

|         |    | 3    | 6    | 9       | 12   | 15   |

|         | 3  | -9.7 | -8.4 | -7.9    | -7.8 | -7.9 |

|         | 6  | -6.6 | -4.5 | -3.6    | -3.4 | -3.6 |

| OUTTERM | 9  | -5.7 | -3.1 | -1.7    | -1.3 | -1.3 |

|         | 12 | -5.4 | -2.5 | -0.8    | +0.0 | +0.1 |

|         | 15 | -5.3 | -2.2 | -0.3    | +0.8 | +1.1 |

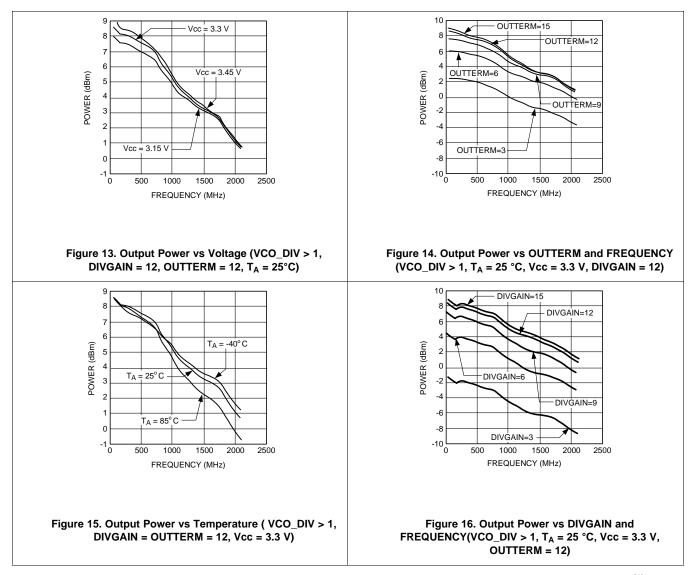

#### 7.7.3 Output Power in Divided Mode

The measurement of the output power is sensitive to the test circuit. All the numbers in the electrical specifications and typical performance curves were obtained from a characterization setup that accommodate temperature testing and changing of parts. In a more optimized setup the measured RF output power is typically on the order of 1.5 to 2.4 dB higher.

|         |    |       | DIVGAIN |      |      |      |  |

|---------|----|-------|---------|------|------|------|--|

|         |    | 3     | 6       | 9    | 12   | 15   |  |

|         | 3  | -10.2 | -6.1    | -5.7 | -5.5 | -5.5 |  |

|         | 6  | -9.8  | -4.4    | -2.4 | -2.1 | -2.0 |  |

| OUTTERM | 9  | -9.8  | -4.3    | -1.5 | -0.7 | -0.5 |  |

|         | 12 | -9.9  | -4.3    | -1.4 | +0.0 | +0.2 |  |

|         | 15 | -9.9  | -4.4    | -1.4 | +0.3 | +0.7 |  |

(1) The table shows the RELATIVE output power to the case of VCOGAIN = OUTTERM = 12.

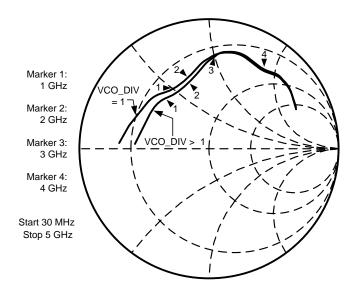

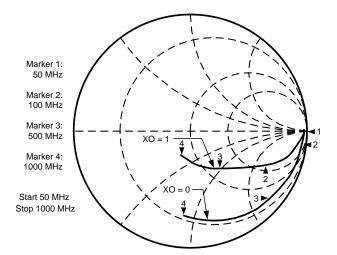

#### 7.7.4 RFout Output Impedance

The impedance of the RFout pin varies as a function of frequency, VCO\_DIV, OUTTERM, VCOGAIN, DIVGAIN, and frequency. When in bypass mode (VCO\_DIV = 1), the DIVGAIN word has no impact on the output impedance. When in divided mode (VCO\_DIV>1), the VCOGAIN has no impact on the output impedance. This graphic shows how the input impedance varies as a function of frequency for both the bypass and divided cases.

Figure 17. RFout Output Impedance

| Table 4. RFout Ou | tput Impedance vs | . VCOGAIN ( | Bypass Mode) <sup>(1)</sup> |

|-------------------|-------------------|-------------|-----------------------------|

|-------------------|-------------------|-------------|-----------------------------|

| Freq.<br>(MHz) | vcoo | GAIN=3        | VCOG | GAIN=6        | vcoo | GAIN=9        | VCOG | AIN=12        | vcoo | AIN=15        |

|----------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|

|                | REAL | IMAGINA<br>RY |

| 50             | 3.8  | 2.1           | 5.5  | 1.9           | 7.3  | 1.8           | 9.5  | 1.7           | 10.1 | 1.7           |

| 100            | 4.8  | 4.1           | 6.1  | 3.9           | 7.8  | 3.7           | 9.8  | 3.6           | 10.3 | 3.6           |

| 200            | 5.4  | 5.7           | 6.8  | 6.0           | 8.7  | 6.3           | 10.9 | 6.5           | 11.4 | 6.6           |

| 400            | 5.5  | 9.4           | 7.5  | 10.0          | 9.8  | 10.6          | 12.4 | 11.0          | 13.1 | 11.0          |

| 600            | 5.8  | 15.1          | 8.1  | 15.4          | 10.7 | 15.7          | 13.7 | 15.7          | 14.5 | 15.6          |

| 800            | 7.0  | 20.7          | 9.6  | 20.8          | 12.6 | 20.8          | 15.8 | 20.3          | 16.7 | 20.1          |

| 1000           | 9.2  | 26.3          | 12.1 | 26.1          | 15.4 | 25.6          | 19.0 | 24.6          | 19.8 | 24.1          |

| 1200           | 10.7 | 28.6          | 13.4 | 27.9          | 16.3 | 26.9          | 19.3 | 25.5          | 20.0 | 25.0          |

| 1400           | 12.2 | 30.9          | 14.7 | 29.7          | 17.1 | 28.2          | 19.7 | 26.4          | 20.2 | 25.9          |

| 1600           | 13.7 | 33.2          | 15.9 | 31.5          | 18.0 | 29.5          | 20.1 | 27.4          | 20.5 | 26.8          |

| 1800           | 15.2 | 35.5          | 17.2 | 33.3          | 18.8 | 30.8          | 20.5 | 28.3          | 20.7 | 27.7          |

| 2000           | 14.5 | 39.5          | 16.4 | 37.4          | 17.9 | 35.0          | 19.6 | 32.5          | 19.8 | 31.9          |

| 2200           | 15.6 | 42.9          | 17.4 | 40.7          | 18.7 | 38.2          | 20.3 | 35.6          | 20.4 | 35.0          |

| 2400           | 14.2 | 47.6          | 16.0 | 45.3          | 17.4 | 42.8          | 19.0 | 40.1          | 19.2 | 39.4          |

| 2600           | 12.2 | 51.3          | 14.1 | 48.7          | 15.6 | 46.5          | 17.2 | 43.5          | 17.3 | 42.5          |

| 2800           | 11.5 | 57.9          | 13.7 | 55.3          | 15.3 | 52.4          | 17.0 | 49.0          | 17.1 | 48.3          |

| 3000           | 10.6 | 67.1          | 13.1 | 64.0          | 14.8 | 60.5          | 16.3 | 56.5          | 16.4 | 55.7          |

| 3200           | 13.1 | 77.3          | 15.7 | 73.2          | 17.3 | 69.0          | 18.4 | 64.2          | 18.4 | 63.3          |

| 3400           | 17.6 | 88.1          | 20.0 | 82.8          | 21.1 | 77.4          | 21.7 | 71.8          | 21.5 | 70.8          |

| 3600           | 29.0 | 96.0          | 30.6 | 90.2          | 30.9 | 83.6          | 30.2 | 76.7          | 29.8 | 75.6          |

| 3800           | 38.2 | 99.4          | 38.0 | 94.4          | 36.4 | 87.3          | 34.1 | 80.5          | 33.4 | 79.4          |

(1) This is for the VCO divider in bypass mode (VCO\_DIV=1) and the RFout pin powered up. OUTTERM was set to 12.

### **RFout Output Impedance (continued)**

|  | Table 4. RFout Output Impedance | e vs. VCOGAIN (Bypass Mode) <sup>(1)</sup> (continued) |

|--|---------------------------------|--------------------------------------------------------|

|--|---------------------------------|--------------------------------------------------------|

| Freq.<br>(MHz) | VCOG  | GAIN=3        | VCOG  | AIN=6         | VCOG  | AIN=9         | VCOG  | AIN=12        | VCOG  | AIN=15        |

|----------------|-------|---------------|-------|---------------|-------|---------------|-------|---------------|-------|---------------|

|                | REAL  | IMAGINA<br>RY |

| 4000           | 43.5  | 106.0         | 41.6  | 99.0          | 38.9  | 92.0          | 35.5  | 85.1          | 34.8  | 83.7          |

| 4200           | 48.0  | 119.3         | 45.9  | 109.8         | 43.1  | 101.9         | 37.2  | 94.2          | 36.0  | 93.0          |

| 4400           | 62.4  | 137.9         | 56.4  | 126.6         | 49.8  | 117.6         | 42.3  | 109.5         | 40.8  | 108.3         |

| 4600           | 87.0  | 149.4         | 76.0  | 138.1         | 65.4  | 129.5         | 54.3  | 122.2         | 52.3  | 121.2         |

| 4800           | 128.1 | 153.7         | 109.7 | 145.6         | 93.0  | 140.1         | 76.7  | 135.9         | 74.0  | 135.5         |

| 5000           | 168.1 | 134.7         | 145.4 | 135.5         | 124.9 | 138.0         | 105.4 | 141.1         | 102.4 | 141.9         |

### Table 5. RFout Output Impedance vs. OUTTERM (Bypass Mode)<sup>(1)</sup>

| Freq.<br>(MHz) | OUTT | ERM=3         | OUTT | ERM=6         | OUTT | ERM=9         | OUTTE | ERM=12        | TER   | M=15          |

|----------------|------|---------------|------|---------------|------|---------------|-------|---------------|-------|---------------|

|                | REAL | IMAGINA<br>RY | REAL | IMAGINA<br>RY | REAL | IMAGINA<br>RY | REAL  | IMAGINA<br>RY | REAL  | IMAGINA<br>RY |

| 50             | 27.9 | 1.6           | 16.2 | 1.9           | 12.3 | 1.8           | 9.5   | 1.7           | 7.8   | 1.7           |

| 100            | 28.5 | 2.8           | 16.7 | 3.6           | 12.7 | 3.6           | 9.8   | 3.6           | 8.0   | 3.5           |

| 200            | 29.2 | 3.8           | 18.1 | 5.9           | 14.0 | 6.3           | 10.9  | 6.5           | 9.0   | 6.6           |

| 400            | 28.8 | 5.7           | 19.2 | 9.5           | 15.3 | 10.3          | 12.4  | 11.0          | 10.6  | 11.2          |

| 600            | 28.8 | 8.8           | 20.4 | 13.7          | 16.5 | 14.9          | 13.7  | 15.7          | 11.9  | 16.0          |

| 800            | 29.1 | 11.7          | 22.5 | 17.5          | 18.7 | 19.2          | 15.8  | 20.3          | 14.0  | 20.8          |

| 1000           | 28.6 | 13.4          | 22.8 | 19.2          | 19.3 | 21.2          | 16.5  | 22.5          | 14.6  | 23.1          |

| 1200           | 28.0 | 15.0          | 23.1 | 20.9          | 19.8 | 23.2          | 17.1  | 24.7          | 15.2  | 25.4          |

| 1400           | 27.5 | 16.7          | 23.3 | 22.7          | 20.4 | 25.2          | 17.7  | 26.9          | 15.8  | 27.7          |

| 1600           | 27.0 | 18.4          | 23.6 | 24.4          | 20.9 | 27.2          | 18.4  | 29.0          | 16.5  | 30.0          |

| 1800           | 26.4 | 20.1          | 23.9 | 26.1          | 21.4 | 29.2          | 19.0  | 31.2          | 17.1  | 32.3          |

| 2000           | 25.9 | 21.8          | 24.1 | 27.9          | 22.0 | 31.1          | 19.6  | 33.4          | 17.7  | 34.6          |

| 2200           | 25.3 | 23.5          | 24.4 | 29.6          | 22.5 | 33.1          | 20.3  | 35.6          | 18.3  | 36.9          |

| 2400           | 23.1 | 26.9          | 22.9 | 33.2          | 21.3 | 37.1          | 19.0  | 40.1          | 17.0  | 41.8          |

| 2600           | 20.1 | 29.3          | 20.5 | 35.4          | 19.3 | 39.6          | 17.2  | 42.9          | 15.1  | 44.9          |

| 2800           | 18.5 | 34.2          | 19.6 | 40.4          | 18.8 | 45.0          | 17.0  | 49.0          | 14.8  | 51.6          |

| 3000           | 16.6 | 40.6          | 18.1 | 46.9          | 17.8 | 51.9          | 16.3  | 56.5          | 14.3  | 59.7          |

| 3200           | 16.5 | 47.0          | 18.9 | 53.4          | 19.3 | 58.9          | 18.4  | 64.2          | 16.7  | 68.2          |

| 3400           | 17.1 | 53.8          | 20.4 | 60.1          | 21.8 | 65.8          | 21.7  | 71.8          | 20.4  | 76.6          |

| 3600           | 20.8 | 59.4          | 25.4 | 65.0          | 28.3 | 70.5          | 30.2  | 76.8          | 30.3  | 82.5          |

| 3800           | 22.0 | 64.9          | 27.3 | 69.7          | 31.1 | 74.6          | 34.1  | 80.5          | 35.4  | 86.1          |

| 4000           | 23.0 | 70.0          | 28.1 | 74.9          | 32.1 | 80.0          | 35.5  | 86.4          | 37.6  | 92.0          |

| 4200           | 23.7 | 77.9          | 28.6 | 82.8          | 32.8 | 87.7          | 37.0  | 94.2          | 39.9  | 100.9         |

| 4400           | 23.7 | 93.2          | 30.1 | 98.0          | 35.4 | 102.9         | 42.3  | 109.4         | 47.8  | 116.6         |

| 4600           | 27.3 | 107.4         | 36.6 | 112.0         | 44.8 | 116.3         | 54.3  | 122.2         | 62.6  | 128.9         |

| 4800           | 40.1 | 126.6         | 52.2 | 129.8         | 63.3 | 132.3         | 76.7  | 135.9         | 89.3  | 140.5         |

| 5000           | 61.4 | 142.8         | 76.2 | 143.3         | 89.5 | 142.3         | 105.5 | 141.0         | 121.0 | 140.5         |

(1) The VCO divider was bypassed (VCO\_DIV = 1) and the RFout pin was enabled. The VCOGAIN word was set to 12.

| Freq.<br>(MHz) | DIVGAIN=3 DIVGAIN=6 |               | DIVG  | AIN=9         | DIVG  | AIN=12        | DIVGAIN=15 |               |      |               |

|----------------|---------------------|---------------|-------|---------------|-------|---------------|------------|---------------|------|---------------|

|                | REAL                | IMAGINAR<br>Y | REAL  | IMAGINAR<br>Y | REAL  | IMAGINAR<br>Y | REAL       | IMAGINAR<br>Y | REAL | IMAGINAR<br>Y |

| 50             | 3.2                 | 2.2           | 3.6   | 2.1           | 5.8   | 2.0           | 13.9       | 1.9           | 22.3 | 1.6           |

| 100            | 4.5                 | 4.1           | 4.6   | 4.0           | 6.6   | 3.8           | 14.7       | 3.2           | 23.2 | 2.3           |

| 200            | 5.7                 | 5.3           | 6.4   | 5.7           | 7.0   | 5.9           | 15.0       | 4.7           | 23.0 | 2.7           |

| 400            | 5.0                 | 9.2           | 5.6   | 9.4           | 7.7   | 9.5           | 15.6       | 7.7           | 22.8 | 4.4           |

| 600            | 5.2                 | 14.6          | 5.7   | 14.6          | 7.8   | 14.6          | 15.9       | 12.1          | 22.2 | 7.9           |

| 800            | 6.0                 | 20.2          | 6.5   | 20.2          | 8.7   | 20.2          | 16.9       | 16.5          | 22.3 | 11.4          |

| 1000           | 7.9                 | 25.7          | 8.4   | 25.7          | 10.7  | 25.5          | 18.7       | 20.5          | 22.9 | 14.6          |

| 1200           | 11.0                | 29.9          | 11.6  | 30.0          | 13.9  | 29.5          | 21.4       | 23.1          | 24.3 | 16.8          |

| 1400           | 13.2                | 32.3          | 13.9  | 32.3          | 16.1  | 31.7          | 22.5       | 24.3          | 23.9 | 18.2          |

| 1600           | 14.2                | 34.4          | 15.0  | 34.3          | 17.1  | 33.5          | 22.5       | 25.8          | 23.1 | 20.1          |

| 1800           | 13.9                | 37.2          | 14.6  | 37.0          | 16.7  | 36.2          | 21.6       | 28.2          | 21.7 | 22.9          |

| 2000           | 13.5                | 41.1          | 14.3  | 40.9          | 16.4  | 39.9          | 20.9       | 31.4          | 20.6 | 26.4          |

| 2200           | 14.8                | 45.1          | 15.6  | 44.7          | 17.8  | 43.6          | 21.7       | 34.5          | 20.9 | 29.7          |

| 2400           | 14.1                | 49.4          | 14.9  | 49.0          | 17.1  | 47.7          | 20.4       | 38.1          | 19.3 | 33.5          |

| 2600           | 12.4                | 52.1          | 13.2  | 51.6          | 15.5  | 50.1          | 18.2       | 40.4          | 16.8 | 36.2          |

| 2800           | 11.8                | 59.3          | 12.5  | 58.7          | 15.0  | 56.8          | 17.0       | 46.2          | 15.3 | 42.0          |

| 3000           | 10.7                | 68.3          | 11.5  | 67.6          | 14.0  | 65.2          | 15.2       | 53.4          | 13.0 | 49.2          |

| 3200           | 13.1                | 78.6          | 14.0  | 77.6          | 16.7  | 74.5          | 16.5       | 61.1          | 13.8 | 56.9          |

| 3400           | 18.1                | 89.6          | 18.9  | 88.4          | 21.6  | 84.4          | 19.4       | 69.2          | 16.0 | 65.1          |

| 3600           | 29.2                | 98.6          | 29.8  | 96.9          | 31.9  | 91.6          | 26.1       | 75.4          | 21.7 | 71.6          |

| 3800           | 36.0                | 105.8         | 36.5  | 103.9         | 37.8  | 97.5          | 28.9       | 81.1          | 24.0 | 77.8          |

| 4000           | 43.6                | 101.4         | 43.7  | 99.5          | 43.7  | 92.9          | 32.3       | 78.8          | 27.1 | 76.3          |

| 4200           | 40.6                | 122.9         | 40.8  | 120.3         | 40.6  | 111.8         | 26.6       | 94.7          | 20.7 | 91.8          |

| 4400           | 63.6                | 143.0         | 62.9  | 139.6         | 59.9  | 128.6         | 37.8       | 111.4         | 30.0 | 109.2         |

| 4600           | 90.9                | 155.3         | 88.8  | 151.4         | 81.1  | 139.6         | 49.9       | 125.8         | 40.3 | 124.9         |

| 4800           | 135.8               | 159.1         | 131.2 | 155.7         | 116.3 | 145.5         | 73.7       | 142.1         | 61.7 | 144.0         |

| 5000           | 179.4               | 135.1         | 173.2 | 133.9         | 153.3 | 131.4         | 107.1      | 147.7         | 94.5 | 155.2         |

## Table 6. RFout Output Impedance vs. DIVGAIN (Divided Mode)<sup>(1)</sup>

(1) This was done with RFout buffer powered up and with OUTTERM=12. VCO\_DIV was set to 50.

| Freq.(MHz) | OUTT | ERM=3         | OUTT | ERM=6         | OUTT | ERM=9         | OUTTE | RM=12         | OUTTE | ERM=15        |

|------------|------|---------------|------|---------------|------|---------------|-------|---------------|-------|---------------|

|            | REAL | IMAGINA<br>RY | REAL | IMAGINA<br>RY | REAL | IMAGINA<br>RY | REAL  | IMAGINA<br>RY | REAL  | IMAGINA<br>RY |

| 50         | 44.1 | -0.3          | 31.8 | 1.0           | 21.2 | 1.7           | 14.0  | 1.9           | 9.3   | 2.0           |

| 100        | 44.9 | -2.2          | 32.8 | 0.7           | 22.1 | 2.5           | 14.8  | 3.2           | 10.0  | 3.5           |

| 200        | 43.2 | -7.2          | 33.2 | -1.2          | 23.3 | 2.8           | 16.1  | 4.7           | 11.3  | 5.6           |

| 400        | 33.2 | -8.1          | 28.5 | -1.5          | 21.9 | 4.5           | 15.7  | 7.7           | 11.2  | 9.1           |

| 600        | 28.0 | -3.8          | 25.7 | 1.8           | 21.4 | 8.0           | 15.9  | 12.1          | 11.4  | 13.9          |

| 800        | 25.1 | 1.1           | 24.0 | 5.6           | 21.7 | 11.5          | 16.9  | 16.5          | 12.5  | 19.0          |

| 1000       | 23.7 | 5.8           | 23.3 | 9.6           | 22.4 | 14.7          | 18.7  | 20.5          | 14.6  | 23.8          |

| 1200       | 23.5 | 9.3           | 23.7 | 12.4          | 23.8 | 16.7          | 21.4  | 23.1          | 17.7  | 27.2          |

| 1400       | 22.6 | 12.3          | 22.9 | 14.8          | 23.5 | 18.1          | 22.5  | 24.3          | 19.5  | 28.9          |

| 1600       | 21.5 | 15.3          | 21.8 | 17.4          | 22.6 | 20.0          | 22.5  | 25.8          | 20.2  | 30.5          |

| 1800       | 20.2 | 18.8          | 20.5 | 20.7          | 21.3 | 22.8          | 21.6  | 28.2          | 19.7  | 33.0          |

(1) This was done in divided mode (VCO\_DIV=50) with VCOGAIN=12.

www.ti.com

|            | Table 7. RFout Output Impedance vs. OUTTERM (Divided Mode)(*) (continued) |       |       |       |      |       |       |       |       |       |

|------------|---------------------------------------------------------------------------|-------|-------|-------|------|-------|-------|-------|-------|-------|

| Freq.(MHz) | OUTT                                                                      | ERM=3 | OUTTI | ERM=6 | OUTT | ERM=9 | OUTTE | RM=12 | OUTTE | RM=15 |

| 2000       | 19.1                                                                      | 22.9  | 19.4  | 24.5  | 20.1 | 26.3  | 20.9  | 31.4  | 19.3  | 36.4  |

| 2200       | 19.4                                                                      | 26.4  | 19.7  | 28.0  | 20.5 | 29.6  | 21.7  | 34.5  | 20.6  | 39.8  |

| 2400       | 17.9                                                                      | 30.4  | 18.2  | 32.0  | 18.9 | 33.4  | 20.4  | 38.1  | 19.8  | 43.6  |

| 2600       | 15.7                                                                      | 33.3  | 15.9  | 34.9  | 16.5 | 36.1  | 18.2  | 40.4  | 17.9  | 45.7  |