Sample &

Buy

TAS5421-Q1

ZHCSCN7C - MARCH 2014-REVISED JANUARY 2015

Support &

Community

20

## TAS5421-Q1 具有负载突降和 I<sup>2</sup>C 诊断功能的 22W 单声道汽车类数字音频 放大器

Technical

Documents

#### 1 特性

- 单声道桥接式负载 (BTL) 数字功率放大器 •

- 负载为 4Ω 且总谐波失真+噪声 (THD+N) 为 10% 时的输出功率为 22W

- 4.5V 至 18V 的工作范围

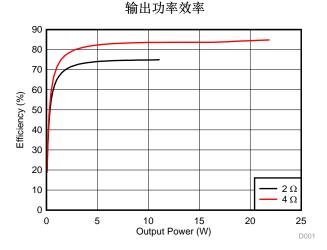

- 4Ω负载时的效率达85%

- 差分模拟输入

- 采用可调功率限制器的 Speaker Guard<sup>™</sup> 扬声器保 护

- 75dB 电源抑制比 (PSRR)

- 负载诊断功能: •

- 开路和短路输出负载

- 输出到电源和输出到接地短接

- 保护和监控功能:

- 短路保护

- 40V负载突降保护符合 ISO-7637-2 标准

- 在音乐播放的同时进行输出直流电平检测

- 过热保护

- 过压及欠压保护

- 耐热增强型 16 引脚散热薄型小外形尺寸 HTSSOP • (PWP) 封装以及 PowerPAD<sup>™</sup> 封装(焊盘朝下)

- 设计用于汽车电磁兼容性 (EMC) 要求

- 符合 AEC-Q100 标准 2 级

- 经 ISO9000:2002 TS16949 认证

- -40°C 至 125°C 环境温度范围

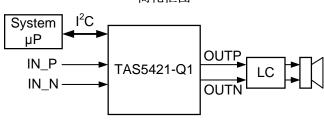

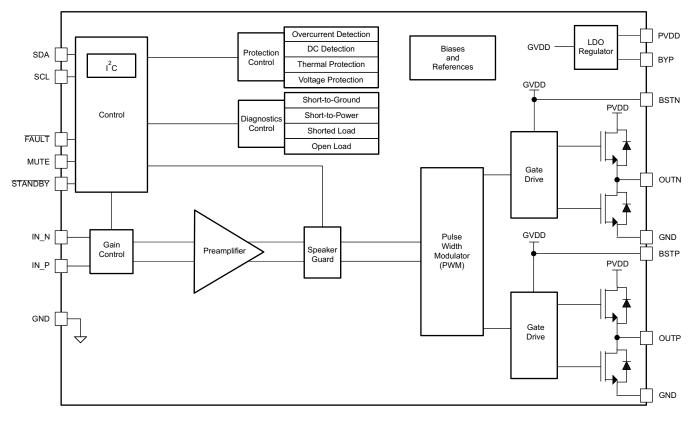

简化框图

## 2 应用

汽车类紧急呼叫 (eCall) 放大器 •

Tools &

Software

- 车载通讯系统

- 仪表板系统 •

- 信息娱乐音频

## 3 说明

TAS5421-Q1 是一款单声道数字音频放大器,非常适 用于汽车类紧急呼叫 (eCall)、车载通讯、仪表板和信 息娱乐应用。 该器件采用 14.4 VDC 汽车电池供电, 可在负载为 4Ω 且 THD+N 不超过 10% 的情况下提供 高达 22W 的功率。 该器件具有较宽的工作电压范围和 优异的效率,是需要起停支持或使用备用电池运行时的 理想选择。 集成的负载突降保护能够缩减外部电压钳 位电路的成本与尺寸,板载负载诊断功能能够通过 I<sup>2</sup>C 报告扬声器状态。

器件信息(1)

| 器件型号       | 封装          | 封装尺寸(标称值)       |

|------------|-------------|-----------------|

| TAS5421-Q1 | HTSSOP (16) | 5.00mm x 4.40mm |

|            |             |                 |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

#### An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

8

9

| 1 | 特性   | £                                                           |

|---|------|-------------------------------------------------------------|

| 2 | 应用   | 1                                                           |

| 3 | 说明   | 1                                                           |

| 4 | 修订   | 历史记录                                                        |

| 5 | Pin  | Configuration and Functions 3                               |

| 6 | Spe  | cifications                                                 |

|   | 6.1  | Absolute Maximum Ratings 3                                  |

|   | 6.2  | ESD Ratings 4                                               |

|   | 6.3  | Recommended Operating Conditions 4                          |

|   | 6.4  | Thermal Information 4                                       |

|   | 6.5  | Electrical Characteristics 5                                |

|   | 6.6  | Timing Requirements for I <sup>2</sup> C Interface Signals7 |

|   | 6.7  | Typical Characteristics 8                                   |

| 7 | Deta | ailed Description 10                                        |

|   | 7.1  | Overview                                                    |

#### 修订历史记录 4

7.2

2

# Changes from Revision B (July 2014) to Revision C

Functional Block Diagram ..... 10

| • | Moved T <sub>stg</sub> from Handling Ratings table to Absolute Maximum Ratings table                                     | 3  |

|---|--------------------------------------------------------------------------------------------------------------------------|----|

| • | Changed Handling Ratings table to ESD Ratings                                                                            | 4  |

| • | In "1. Load Diagnostics" paragraph, changed "at start-up" to "on de-assertion of STANDBY" and appended two new sentences | 12 |

| • | Changed Section number of ${}^{ m P}C$ Serial Communication Bus from 7.4 to 7.3.7                                        | 13 |

| • | Changed Table 3                                                                                                          | 16 |

| • | Added disclaimer to beginning of Application and Implementation section                                                  | 18 |

| • | Added Power Supply Recommendations section and moved the contents of former Section 8.2.1.5 here                         | 22 |

| • | Created a Layout Examples section to contain former sections 9.1.1 through 9.1.4                                         | 22 |

| • | Placed text ahead of graphics for Figure 18 through Figure 21                                                            | 22 |

| • | 添加了第三方组件免责声明                                                                                                             | 24 |

| Changes from Revision A (July 2014) to Revision B                                           | Page |

|---------------------------------------------------------------------------------------------|------|

| <ul> <li>数据表状态从产品预览更改为生产数据</li> </ul>                                                       | 1    |

|                                                                                             |      |

| Changes from Original (March 2014) to Revision A                                            | Page |

| • Added content to the preliminary data sheet to create the full PRODUCT PREVIEW data sheet |      |

#### 7.3 Feature Description..... 10 Device Functional Modes..... 15 7.4 Register Maps ..... 16 7.5 Application and Implementation ...... 18 8.1 Application Information...... 18 Power Supply Recommendations ...... 22 10 Layout...... 22 10.1 Layout Guidelines ..... 22 10.2 Layout Examples..... 22 11 器件和文档支持 ...... 24 器件支持......24 11.1 11.2 商标......24 11.3 静电放电警告...... 24 11.4 术语表 ...... 24

12 机械、封装和可订购信息...... 24

www.ti.com.cn

Page

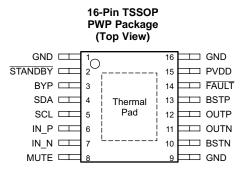

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN         |                                                              | TYPE <sup>(1)</sup>       | DESCRIPTION                                              |  |

|-------------|--------------------------------------------------------------|---------------------------|----------------------------------------------------------|--|

| NAME        | NO.                                                          | ITPE                      | DESCRIPTION                                              |  |

| BSTN        | 10                                                           | AI                        | Bootstrap for negative-output high-side FET              |  |

| BSTP        | 13                                                           | AI                        | Bootstrap for positive-output high-side FET              |  |

| BYP         | 3                                                            | PBY                       | Voltage-regulator bypass-capacitor pin                   |  |

| FAULT       | 14                                                           | DO                        | Active-low open-drain output used to report faults       |  |

| GND         | 1, 9, 16                                                     | GND                       | Ground                                                   |  |

| IN_N        | 7                                                            | AI Inverting analog input |                                                          |  |

| IN_P        | 6                                                            | AI                        | Non-inverting analog input                               |  |

| MUTE        | 8                                                            | DI                        | Mute input, active-high (no internal pullup or pulldown) |  |

| OUTN        | 11                                                           | PO                        | Output (–)                                               |  |

| OUTP        | 12                                                           | PO                        | Output (+)                                               |  |

| PVDD        | 15                                                           | PWR                       | Power supply                                             |  |

| SCL         | 5                                                            | DI                        | I <sup>2</sup> C clock                                   |  |

| SDA         | 4 DI/DO I <sup>2</sup> C data                                |                           |                                                          |  |

| STANDBY     | 2 DI Active-low STANDBY pin (no internal pullup or pulldown) |                           |                                                          |  |

| Thermal pad | —                                                            | —                         | Must be soldered to ground                               |  |

(1) DI = digital input, DO = digital output, AI = analog input, PWR = power supply, PBY = power bypass, PO = power output, GND = ground

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                          |                                                                          |                     | MIN  | MAX | UNIT |

|------------------------------------------|--------------------------------------------------------------------------|---------------------|------|-----|------|

|                                          | DC supply voltage range, V(PVDD)                                         | Relative to GND     | -0.3 | 30  | V    |

|                                          | Pulsed supply voltage range, V(PVDD_MAX)                                 | t ≤ 400 ms exposure | -1   | 40  | v    |

| Input Voltage                            | Supply voltage ramp rate, $\Delta V_{(PVDD_RAMP)}$                       |                     |      | 15  | V/ms |

|                                          | For SCL, SDA, STANDBY pins                                               | Relative to GND     | -0.3 | 5   | V    |

|                                          | For IN_N, IN_P, and MUTE pins                                            | Relative to GND     | -0.3 | 6.5 |      |

|                                          | DC current on PVDD, GND and OUTx pins, $\mathrm{I}_{(\mathrm{PV}}$       | DD), IO             |      | ±4  | А    |

| Current                                  | Maximum current, on all input pins, I <sub>(IN_MAX)</sub> <sup>(2)</sup> |                     |      | ±1  | ~ ^  |

|                                          | Maximum sink current for open-drain pin, I(IN_ODMAX)                     |                     |      | 7   | mA   |

| Storage<br>temperature, T <sub>stg</sub> |                                                                          |                     | -55  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) See the Application Information section for information on analog input voltage and ac coupling.

STRUMENTS www.ti.com.cn

EXAS

## 6.2 ESD Ratings

|                    |                         |                                                 |                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------|-------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-           | -002 <sup>(1)</sup>           | ±3500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM) per AEC              | All pins                      | ±1000 | V    |

| · (ESD)            |                         | Charged-device model (CDM), per AEC<br>Q100-011 | Corner pins (1, 8, 9, and 16) | ±1000 |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

|                                   |                                                                      |                                                                                  | MIN  | TYP  | MAX                   | UNIT            |

|-----------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|-----------------------|-----------------|

|                                   | Supply voltage range relative to GND.                                | 4-Ω ±20% load (or higher)                                                        | 4.5  | 14.4 | 18                    |                 |

| V <sub>(PVDD_OP)</sub>            | Includes ac transients, requires proper decoupling. <sup>(1)</sup>   | 2-Ω ±20% load                                                                    | 5    | 14.4 | 18                    | V               |

| V <sub>(PVDD_RIPPLE)</sub>        | Maximum ripple on PVDD                                               | $V_{(PVDD)} < 8 V$                                                               |      |      | 1                     | V <sub>pp</sub> |

| V <sub>(AIN)</sub> <sup>(2)</sup> | Analog audio input-signal level                                      | AC-coupled input voltage                                                         | 0    |      | 0.25–1 <sup>(3)</sup> | Vrms            |

| $V_{(IH\_STANDBY)}$               | STANDBY pin input voltage for logic-level<br>high                    |                                                                                  | 2    |      |                       | V               |

| V <sub>(IL_STANDBY)</sub>         | STANDBY pin input voltage for logic-level low                        |                                                                                  |      |      | 0.7                   | V               |

| V <sub>(IH_SCL)</sub>             | SCL pin input voltage for logic-level high                           |                                                                                  | 2.1  |      | 5.5                   | V               |

| V <sub>(IH_SDA)</sub>             | SDA pin input voltage for logic-level high                           | $R_{(PU, I2C)} = 4.7 \text{-} \text{k}\Omega$ pullup, supply voltage =           | 2.1  |      | 5.5                   | V               |

| V <sub>(IL_SCL)</sub>             | SCL pin input voltage for logic-level low                            | 3.3 V or 5 V                                                                     | -0.5 |      | 1.1                   | V               |

| V <sub>(IL_SDA)</sub>             | SDA pin input voltage for logic-level low                            |                                                                                  | -0.5 |      | 1.1                   | V               |

| T <sub>A</sub>                    | Ambient temperature                                                  |                                                                                  | -40  |      | 125                   | °C              |

| R <sub>(L)</sub>                  | Nominal speaker load impedance                                       | When using low-impedance loads, do not exceed overcurrent limit.                 | 2    | 4    | 16                    | Ω               |

| V <sub>(PU)</sub>                 | Pullup voltage supply (for open-drain logic outputs)                 |                                                                                  | 3    | 3.3  | 3.6                   | V               |

| R <sub>(PU_EXT)</sub>             | External pullup resistor on open-drain logic outputs                 | Resistor connected between open-drain logic output and $V_{(\text{PU})}$ supply. | 10   |      | 50                    | kΩ              |

| R <sub>(PU_I2C)</sub>             | I <sup>2</sup> C pullup resistance on SDA and SCL pins               |                                                                                  | 1    | 4.7  | 10                    | kΩ              |

| C <sub>(PVDD)</sub>               | External capacitor on the PVDD pin, typical value $\pm 20\%^{(1)}$   |                                                                                  |      | 10   |                       | μF              |

| C <sub>(BYP)</sub>                | External capacitor on the BYP pin, typical value $\pm$ 10%           |                                                                                  |      | 1    |                       | μF              |

| C <sub>(OUT)</sub>                | External capacitance to GND on OUT_X pins                            |                                                                                  |      |      | 4                     | μF              |

| C <sub>(IN)</sub>                 | External capacitance to analog input pin in series with input signal |                                                                                  |      | 1    |                       | μF              |

| $C_{(BSTN)},C_{(BSTP)}$           | External boostrap capacitor, typical value $\pm$ 20%                 |                                                                                  |      | 220  |                       | nF              |

|                                   |                                                                      |                                                                                  |      |      |                       |                 |

(1)

See the *Power Supply Recommendations* section. Signal input for full unclipped output with gains of 36 dB, 32 dB, 26 dB, and 20 dB (2)

Maximum recommended input voltage is determined by the gain setting. (3)

#### 6.4 Thermal Information

|                       |                                              | TAS5421-Q1   |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 16 PINS      |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 39.4         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.9         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20           | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.6          | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 19.8         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2            | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

| $T_{C} = 25^{\circ}C, PVDD = 14.4 V, R_{L} = 4 \Omega, P_{(O)} = 1^{\circ}$ | W/ch, AES17 filter, default I <sup>2</sup> C settings (unless otherwise | noted) |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|--------|

|                                                                             |                                                                         |        |

| PARAMETER                                       | TEST CONDITIONS                                        | MIN  | TYP       | MAX  | UNIT |

|-------------------------------------------------|--------------------------------------------------------|------|-----------|------|------|

| OPERATING CURRENT                               |                                                        |      |           |      |      |

| PVDD idle current                               | In PLAY mode, no audio present                         |      | 16        |      | mA   |

| PVDD standby current                            | STANDBY mode, MUTE = 0 V                               |      | 5         | 20   | μA   |

| OUTPUT POWER                                    |                                                        |      |           |      |      |

|                                                 | 4 Ω, THD+N ≤ 1%, 1 kHz, $T_C$ = 75°C                   |      | 18        |      |      |

| Output power per channel                        | 4 Ω, THD+N = 10%, 1 kHz, T <sub>C</sub> = 75°C         |      | 22        |      | W    |

| Power efficiency                                | 4 Ω, P <sub>(O)</sub> = 22 W (10% THD)                 |      | 85%       |      |      |

| AUDIO PERFORMANCE                               |                                                        |      |           |      |      |

| Noise voltage at output                         | G = 20 dB, zero input, and A-weighting                 |      | 65        |      | μV   |

| Common-mode rejection ratio                     | f = 1 kHz, 100 mVrms referenced to GND, G = 20 dB      |      | 63        |      |      |

| Power-supply rejection ratio                    | PVDD = 14.4 Vdc + 1 Vrms, f = 1 kHz                    |      | 75        |      | dB   |

| Total harmonic distortion + noise               | P <sub>(O)</sub> = 1 W, f = 1 kHz                      |      | 0.05<br>% |      |      |

|                                                 | Switching frequency selectable for AM interference     |      | 400       |      |      |

| Switching frequency                             | avoidance                                              |      | 500       |      | kHz  |

| Internal common-mode input bias voltage         | Internal bias applied to IN_N, IN_P pins               |      | 3         |      | V    |

|                                                 |                                                        | 19   | 20        | 21   |      |

|                                                 |                                                        | 25   | 26        | 27   | dB   |

| Voltage gain (V <sub>O</sub> /V <sub>IN</sub> ) | Source impedance = 0 $\Omega$ , P <sub>(O)</sub> = 1 W | 31   | 32        | 33   |      |

|                                                 |                                                        | 35   | 36        | 37   |      |

| PWM OUTPUT STAGE                                |                                                        |      |           |      | -    |

| FET drain-to-source resistance                  | $T_J = 25^{\circ}C$                                    |      | 180       |      | mΩ   |

| Output offset voltage                           | Zero input signal, G = 20 dB                           |      |           | ±25  | mV   |

| PVDD OVERVOLTAGE (OV) PROTECTION                |                                                        |      |           |      | -    |

| PVDD overvoltage-shutdown set                   |                                                        | 19.5 | 21        | 22.5 | V    |

| PVDD overvoltage-shutdown hysteresis            |                                                        |      | 0.6       |      | V    |

| PVDD UNDERVOLTAGE (UV) PROTECTION               |                                                        |      |           |      |      |

| PVDD undervoltage-shutdown set                  |                                                        | 3.6  | 4         | 4.4  | V    |

| PVDD undervoltage-shutdown hysteresis           |                                                        |      | 0.25      |      | V    |

| ВҮР                                             |                                                        | ÷    |           |      |      |

| BYP pin voltage                                 |                                                        | 6.4  | 6.9       | 7.4  | V    |

| POWER-ON RESET (POR)                            |                                                        | ÷    |           |      |      |

| PVDD voltage for POR                            |                                                        |      |           | 4.1  | V    |

| PVDD recovery hysteresis voltage for POR        |                                                        |      | 0.3       |      | V    |

## **Electrical Characteristics (continued)**

$T_{C} = 25^{\circ}C$ , PVDD = 14.4 V,  $R_{L} = 4 \Omega$ ,  $P_{(O)} = 1$  W/ch, AES17 filter, default I<sup>2</sup>C settings (unless otherwise noted)

| PARAMETER                                                               | TEST CONDITIONS                                                          | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| OVERTEMPERATURE (OT) PROTECTION                                         | ·                                                                        | ·   |     |     |      |

| Junction temperature for overtemperature shutdown                       |                                                                          | 155 | 170 |     | °C   |

| Junction temperature overtemperature shutdown<br>hystersis              |                                                                          |     | 15  |     | °C   |

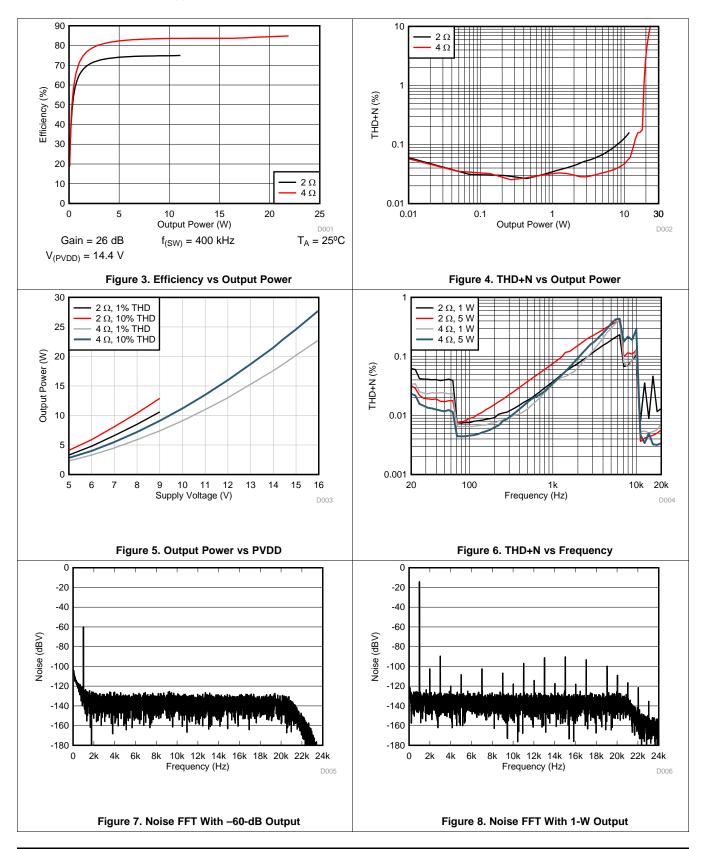

| OVERCURRENT (OC) SHUTDOWN PROTECTION                                    |                                                                          |     |     |     |      |

| Maximum current (peak output current)                                   |                                                                          |     | 3.5 |     | Α    |

| STANDBY PIN                                                             |                                                                          |     |     |     |      |

| STANDBY pin current                                                     |                                                                          |     | 0.1 | 0.2 | μA   |

| DC DETECT                                                               |                                                                          |     |     |     |      |

| DC detect threshold                                                     |                                                                          |     | 2.9 |     | V    |

| DC detect step response time                                            |                                                                          |     |     | 700 | ms   |

| FAULT REPORT                                                            | ·                                                                        | ÷   |     |     |      |

| FAULT pin output voltage for logic-level high (open-drain logic output) |                                                                          | 2.4 |     |     | V    |

| FAULT pin output voltage for logic-level low (open-drain logic output)  | External 47-kΩ pullup resistor to 3.3 V                                  |     |     | 0.5 | V    |

| LOAD DIAGNOSTICS                                                        |                                                                          |     |     |     |      |

| Resistance to detect a short from OUT $pin(s)$ to $PVDD$ or ground      |                                                                          |     |     | 200 | Ω    |

| Open-circuit detection threshold                                        |                                                                          | 70  | 95  | 120 | Ω    |

| Short-circuit detection threshold                                       | Including speaker wires                                                  | 0.9 | 1.2 | 1.5 | Ω    |

| I <sup>2</sup> C                                                        | ·                                                                        | ÷   |     | 1   |      |

| SDA pin output voltage for logic-level high                             | $R_{(PU_{12C})} = 4.7$ -k $\Omega$ pullup, supply voltage = 3.3 V or 5 V | 2.4 |     |     | V    |

| SDA pin output voltage for logic-level low                              | 3-mA sink current                                                        |     |     | 0.4 | V    |

| Capacitance for SCL and SDA pins                                        |                                                                          |     |     | 10  | pF   |

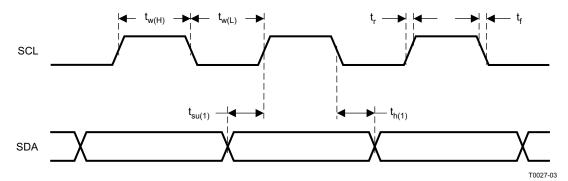

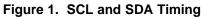

## 6.6 Timing Requirements for I<sup>2</sup>C Interface Signals

over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                                        | MIN              | TYP MA |       |

|--------------------|------------------------------------------------------------------|------------------|--------|-------|

| f <sub>(SCL)</sub> | SCL clock frequency                                              |                  | 40     | ) kHz |

| t <sub>r</sub>     | Rise time for both SDA and SCL signals                           |                  | 30     | ) ns  |

| t <sub>f</sub>     | Fall time for both SDA and SCL signals                           |                  | 30     | ) ns  |

| t <sub>w(H)</sub>  | SCL pulse duration, high                                         | 0.6              |        | μs    |

| t <sub>w(L)</sub>  | SCL pulse duration, low                                          | 1.3              |        | μs    |

| t <sub>su(2)</sub> | Setup time for START condition                                   | 0.6              |        | μs    |

| t <sub>h(2)</sub>  | START condition hold time before generation of first clock pulse | 0.6              |        | μs    |

| t <sub>su(1)</sub> | Data setup time                                                  | 100              |        | ns    |

| t <sub>h(1)</sub>  | Data hold time                                                   | 0 <sup>(1)</sup> |        | ns    |

| t <sub>su(3)</sub> | Setup time for STOP condition                                    | 0.6              |        | μs    |

| C <sub>(B)</sub>   | Load capacitance for each bus line                               |                  | 40     | ) pF  |

(1) A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

Figure 2. Timing for Start and Stop Conditions

TAS5421-Q1

ZHCSCN7C-MARCH 2014-REVISED JANUARY 2015

www.ti.com.cn

**NSTRUMENTS**

**Texas**

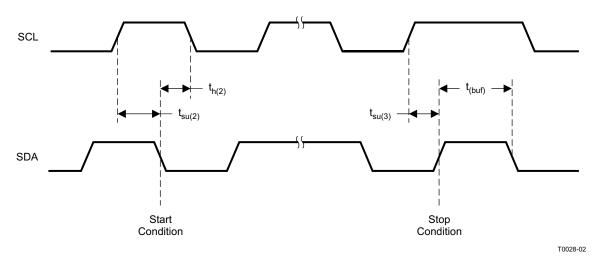

## 6.7 Typical Characteristics

$PVDD = 14.4 V, T_A = 25^{o}C, P_{(O)} = 1 W, 1-kHz input, default I<sup>2</sup>C settings (unless otherwise noted)$

## **Typical Characteristics (continued)**

$\underline{\text{PVDD}} = 14.4 \text{ V}, \text{ } \text{T}_{\text{A}} = 25^{\circ}\text{C}, \text{ } \text{P}_{(\text{O})} = 1 \text{ W}, \text{ } 1\text{-kHz} \text{ input, default } \text{l}^{2}\text{C} \text{ settings (unless otherwise noted)}$

## 7 Detailed Description

### 7.1 Overview

The TAS5421-Q1 is a mono analog-input audio amplifier for use in the automotive environment. The design uses an ultra-efficient class-D technology developed by Texas Instruments, but with features added for the automotive industry. This technology allows for reduced power consumption, reduced heat, and reduced peak currents in the electrical system. The device realizes an audio sound system design with smaller size and lower weight than traditional class-AB solutions.

There are seven core design blocks:

- PWM

- Gate drive

- Power FETs

- Diagnostics

- Protection

- Power supply

- I<sup>2</sup>C serial communication bus

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Analog Audio Input and Preamplifier

The differential input stage of the amplifier cancels common-mode noise that appears on the inputs. For a differential audio source, connect the positive lead to IN\_P and the negative lead to IN\_N. The inputs must be ac-coupled to minimize the output dc-offset and ensure correct ramping of the output voltages. For good transient performance, the impedance seen at each of the two differential inputs should be the same.

The gain setting impacts the analog input impedance of the amplifier. See Table 1 for typical values.

| Gain  | Input Impedance |

|-------|-----------------|

| 20 dB | 60 kΩ ± 20%     |

| 26 dB | 30 kΩ ± 20%     |

| 32 dB | 15 kΩ ± 20%     |

| 36 dB | 9 kΩ ± 20%      |

#### Table 1. Input Impedance and Gain

#### 7.3.2 Pulse-Width Modulator (PWM)

The PWM converts the analog signal from the preamplifier into a switched signal of varying duty cycle. This is the critical stage that defines the class-D architecture. In the TAS5421-Q1, the modulator is an advanced design with high bandwidth, low noise, low distortion, and excellent stability.

The pulse-width modulation scheme allows increased efficiency at low power. Each output is switching from 0 V to PVDD. The OUTP and OUTN pins are in phase with each other with no input, so that there is little or no current in the speaker. The duty cycle of OUTP is greater than 50% and OUTN is less than 50% for positive output voltages. The duty cycle of OUTN is greater than 50% and that of OUTP is less than 50% for negative output voltages. The voltage across the load is at 0 V through most of the switching period, reducing power loss.

#### 7.3.3 Gate Drive

The gate driver accepts the low-voltage PWM signal and level shifts it to drive a high-current, full-bridge, power FET stage. The device uses proprietary techniques to optimize EMI and audio performance.

#### 7.3.4 Power FETs

The BTL output comprises four matched N-channel FETs for high efficiency and maximum power transfer to the load. By design, the FETs withstand large voltage transients during a load-dump event.

#### 7.3.5 Load Diagnostics

The device incorporates load diagnostic circuitry designed for detecting and determining the status of output connections. The device supports the following diagnostics:

- Short to GND

- Short to PVDD

- Short across load

- Open load

The device reports the presence of any of the short or open conditions to the system via I<sup>2</sup>C register read.

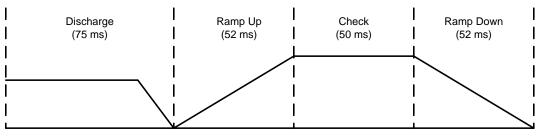

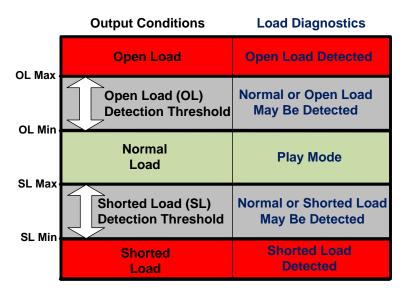

1. Load Diagnostics—The load diagnostic function runs on de-assertion of STANDBY or when the device is in a fault state (dc detect, overcurrent, overvoltage, undervoltage, and overtemperature). During this test, the outputs are in a Hi-Z state. The device determines whether the output is a short to GND, short to PVDD, open load, or shorted load. The load diagnostic biases the output, which therefore requires limiting the capacitance value for proper functioning; see the *Recommended Operating Conditions*. The load diagnostic test takes approximately 229 ms to run. Note that the *check* phase repeats up to 5 times if a fault is present or a large capacitor to GND is present on the output. On detection of an open load, the output still operates. On detection of any other fault condition, the output goes into a Hi-Z state, and the device checks the load continuously until removal of the fault condition. After detection of a normal output condition, the audio output starts. The load diagnostics run after every other overvoltage (OV) event. The load diagnostic for open load only has I<sup>2</sup>C reporting. All other faults have I<sup>2</sup>C and FAULT pin assertion.

The device performs load diagnostic tests as shown in Figure 11.

Figure 12 illustrates how the diagnostics determine the load based on output conditions.

Figure 11. Load Diagnostics Sequence of Events

Figure 12. Load Diagnostic Reporting Thresholds

2. Faults During Load Diagnostics—If the device detects a fault (overtemperature, overvoltage, undervoltage) during the load diagnostics test, the device exits the load diagnostics, which may result in a pop or click on the output.

#### 7.3.6 Protection and Monitoring

- Overcurrent Shutdown (OCSD)—The overcurrent shutdown forces the output into Hi-Z. The device asserts the FAULT pin and updates the I<sup>2</sup>C register.

- DC Detect—This circuit checks for a dc offset continuously during normal operation at the output of the amplifier. If a dc offset occurs, the device asserts the FAULT pin and updates the I<sup>2</sup>C register. Note that the dc detection threshold follows PVDD changes.

- Overtemperature Shutdown (OTSD)—The device shuts down when the die junction temperature reaches the overtemperature threshold. The device asserts the FAULT pin asserts and updates I<sup>2</sup>C register. Recovery is automatic when the temperature returns to a safe level.

- Undervoltage (UV)—The undervoltage (UV) protection detects low voltages on PVDD. In the event of an

undervoltage condition, the device asserts the FAULT pin and resets the I<sup>2</sup>C register.

- Power-On Reset (POR)—Power-on reset (POR) occurs when PVDD drops below the POR threshold. A POR event causes the l<sup>2</sup>C bus to go into a high-impedance state. After recovery from the POR event, the device restarts automatically with default l<sup>2</sup>C register settings. The l<sup>2</sup>C is active as long as the device is not in POR.

- Overvoltage (OV) and Load Dump—OV protection detects high voltages on PVDD. If PVDD reaches the

overvoltage threshold, the device asserts the FAULT pin and updates the I<sup>2</sup>C register. The device can

withstand 40-V load-dump voltage spikes.

- SpeakerGuard protection circuitry limits the output voltage to the value selected in I<sup>2</sup>C register 0x03. This

value determines both the positive and negative limits. One can use this feature to improve battery life or

protect the speaker from exceeding its excursion limits.

- Adjacent-Pin Shorts—The device design is such that shorts between adjacent pins do not cause damage.

#### 7.3.7 I<sup>2</sup>C Serial Communication Bus

The device communicates with the system processor via the  $I^2C$  serial communication bus as an  $I^2C$  slave-only device. The processor can poll the device via  $I^2C$  to determine the operating status. All reports of fault conditions and detections are via  $I^2C$ . The system can also set numerous features and operating conditions via  $I^2C$ . The  $I^2C$  interface is active approximately 1 ms after the STANDBY pin is high.

TEXAS INSTRUMENTS

www.ti.com.cn

The I<sup>2</sup>C interface controls the following device features:

- Changing gain setting to 20 dB, 26 dB, 32 dB, or 36 dB.

- Controlling peak voltage value of SpeakerGuard protection circuitry

- Reporting load diagnostic results

- Changing of switching frequency for AM radio avoidance

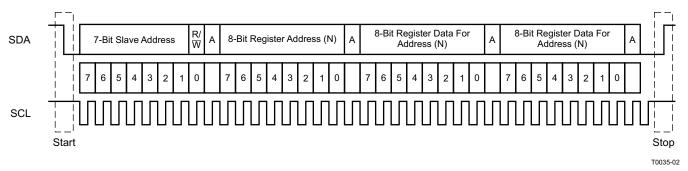

### 7.3.7.1 $m \ell^2 C$ Bus Protocol

The device has a bidirectional serial control interface that is compatible with the Inter IC ( $I^2C$ ) bus protocol and supports 400-kbps data transfer rates for random and sequential write and read operations. This is a slave-only device that does not support a multimaster bus environment or wait-state insertion. The master device uses the  $I^2C$  control interface to program the registers of the device and to read device status.

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data transfer on the bus is serial, one bit at a time. The transfer of address and data is in byte (8-bit) format with the most-significant bit (MSB) transferred first. In addition, the receiving device acknowledges each byte transferred on the bus with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data pin (SDA) while the clock is HIGH to indicate start and stop conditions. A HIGH-to-LOW transition on SDA indicates a start, and a LOW-to-HIGH transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. Figure 13 shows these conditions. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The device holds SDA LOW during the acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence. The address for each device is a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. The SDA and SCL signals require the use of an external pullup resistor to set the HIGH level for the bus. There is no limit on the number of bytes that the communicating devices can transmit between start and stop conditions. After transfer of the last word, the master generates a stop condition to release the bus.

#### Figure 13. Typical I<sup>2</sup>C Sequence

To communicate with the device, the I<sup>2</sup>C master uses addresses shown in Figure 13. Transmission of read and write data can be by single-byte or multiple-byte data transfers.

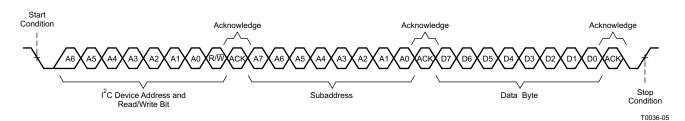

#### 7.3.7.2 Random Write

As shown in Figure 14, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit is a 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the device responds with an acknowledge bit. Next, the master transmits the address byte corresponding to the internal memory address being accessed. After receiving the data byte for writing to the memory address being accessed. After receiving the data byte for writing to the memory address being accessed. After receiving the data byte for writing to the memory address being accessed. After receiving the data byte for writing to the memory address being accessed. After receiving the data byte, the device again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

Figure 14. Random Write Transfer

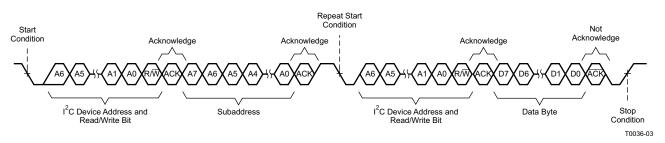

#### 7.3.7.3 Random Read

As shown in Figure 15, a single-byte data-read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data-read transfer, the master device performs both a write and a following read. Initially, the master device performs a write to transfer the address byte of the internal memory address to be read. As a result, the read/write bit is a 0. After receiving the address and the read/write bit, the device responds with an acknowledge bit. In addition, after sending the internal memory address byte, the master device transmits another start condition followed by the device address and the read/write bit again. This time, the read/write bit is a 1, indicating a read transfer. After receiving the address and the read/write bit, the device again responds with an acknowledge bit. Next, the device transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data-read transfer.

Figure 15. Random Read Transfer

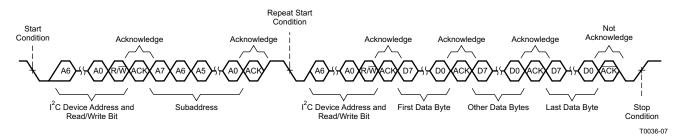

#### 7.3.7.4 Sequential Read

A sequential data-read transfer is identical to a single-byte data-read transfer except that the TAS5421-Q1 transmits multiple data bytes to the master device as shown in Figure 16. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte and automatically increments the I<sup>2</sup>C subaddress by one. After receiving the last data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the transfer.

Figure 16. Sequential Read Transfer

## 7.4 Device Functional Modes

#### 7.4.1 Hardware Control Pins

There are three discrete hardware pins for real-time control and indication of device status.

#### TAS5421-Q1 ZHCSCN7C – MARCH 2014–REVISED JANUARY 2015

#### **Device Functional Modes (continued)**

**FAULT** pin: This active-low open-drain output pin indicates the presence of a fault condition which requires the device to go into the Hi-Z mode. On assertion of this pin, the device has protected itself and the system from potential damage. The system can read the exact nature of the fault via I<sup>2</sup>C with the exception of PVDD undervoltage faults below POR, in which case the I<sup>2</sup>C bus is no longer operational.

**STANDBY** pin: Assertion of this active-low pin sends the device goes into a complete shutdown, limiting the current draw.

**MUTE** pin: On assertion of this active-high pin, the device is in mute mode. The output pins stop switching and audio does not pass from the input to the output. To place the device back into play mode, it is necessary to deassert this pin.

#### 7.4.2 EMI Considerations

Automotive-level EMI performance depends on both careful integrated-circuit design and good system-level design. Controlling sources of electromagnetic interference (EMI) was a major consideration in all aspects of the design.

The design has minimal parasitic inductances due to the short leads on the package. This dramatically reduces the EMI that results from current passing from the die to the system PCB. The design incorporates circuitry that optimizes output transitions that cause EMI.

#### 7.4.3 Operating Modes and Faults

The following tables list operating modes and faults.

#### Table 2. Operating Modes

| STATE NAME      | OUTPUT               | OSCILLATOR | I <sup>2</sup> C |

|-----------------|----------------------|------------|------------------|

| STANDBY         | Hi-Z, floating       | Stopped    | Stopped          |

| Load diagnostic | DC biased            | Active     | Active           |

| Fault and mute  | Hi-Z, floating       | Active     | Active           |

| Play            | Switching with audio | Active     | Active           |

| FAULT<br>EVENT             | FAULT EVENT<br>CATEGORY | MONITORING<br>MODES | REPORTING<br>METHOD          | ACTION<br>TYPE      | ACTION<br>RESULT            | CLEARING                              |

|----------------------------|-------------------------|---------------------|------------------------------|---------------------|-----------------------------|---------------------------------------|

| POR                        |                         |                     | Not applicable               |                     | Standby                     |                                       |

| UV or OV                   | Voltage fault           | All                 | I <sup>2</sup> C + FAULT pin |                     |                             |                                       |

| Load dump <sup>(1)</sup>   |                         |                     | FAULT pin                    | Hard mute (no ramp) | Hi-Z                        | Self-clearing                         |

| OTSD                       | Thermal fault           | Hi-Z, mute, play    |                              |                     |                             |                                       |

| OC fault                   | Output channel          | Diav                |                              |                     |                             |                                       |

| DC detect                  | fault                   | Play                | I <sup>2</sup> C + FAULT pin |                     |                             |                                       |

| Load diagnostic -<br>short |                         |                     |                              |                     | Hi-Z, re-run<br>diagnostics |                                       |

| Load diagnostic -<br>open  | Diagnostic              | Hi-Z                | l <sup>2</sup> C             | None                | None                        | Clears on next<br>diagnostic<br>cycle |

Table 3. Faults and Actions

(1) Tested in accordance with ISO7637-1

## 7.5 Register Maps

| Table 4. I <sup>2</sup> C Address |

|-----------------------------------|

|-----------------------------------|

| DESCRIPTION            |     |   | FIX | ED ADDR | <b>READ/WRITE BIT</b> | I <sup>2</sup> C ADDRESS |   |     |            |  |

|------------------------|-----|---|-----|---------|-----------------------|--------------------------|---|-----|------------|--|

| DESCRIPTION            | MSB | 6 | 5   | 4       | 3                     | 2                        | 1 | LSB | FC ADDRESS |  |

| I <sup>2</sup> C write | 1   | 1 | 0   | 1       | 1                     | 0                        | 0 | 0   | 0xD8       |  |

| I <sup>2</sup> C read  | 1   | 1 | 0   | 1       | 1                     | 0                        | 0 | 1   | 0xD9       |  |

#### TAS5421-Q1 ZHCSCN7C – MARCH 2014–REVISED JANUARY 2015

www.ti.com.cn

## Table 5. I<sup>2</sup>C Address Register Definitions

| ADDRESS | R/W | REGISTER DESCRIPTION                 |  |  |  |  |  |  |  |

|---------|-----|--------------------------------------|--|--|--|--|--|--|--|

| 0x01    | R   | Latched fault register               |  |  |  |  |  |  |  |

| 0x02    | R   | Status and load diagnostics register |  |  |  |  |  |  |  |

| 0x03    | R/W | Control register                     |  |  |  |  |  |  |  |

#### Table 6. Fault Register (0x01)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                    |

|----|----|----|----|----|----|----|----|---------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | No protection-created faults, default value |

| -  | -  | -  | -  | -  | -  | -  | 1  | Reserved                                    |

| -  | -  | -  |    | -  | -  | 1  | -  | Reserved                                    |

| -  | _  | -  | -  | -  | 1  | -  | -  | A load-diagnostics fault has occurred.      |

| -  | -  | -  |    | 1  | -  | -  | -  | Overcurrent shutdown has occurred.          |

| -  | -  | -  | 1  | 1  | -  | -  | -  | PVDD undervoltage has occurred.             |

| -  | -  | 1  |    | 1  | -  | -  | -  | PVDD overvoltage has occurred.              |

| -  | 1  | -  | -  | -  | _  | -  | -  | DC offset protection has occurred.          |

| 1  | -  | -  | -  | -  | -  | -  | -  | Overtemperature shutdown has occurred.      |

### Table 7. Status and Load Diagnostic Register (0x02)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                            |  |

|----|----|----|----|----|----|----|----|-----------------------------------------------------|--|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | No speaker-diagnostic-created faults, default value |  |

| -  | -  | -  | -  | -  | -  | -  | 1  | Output short to PVDD is present.                    |  |

| -  | -  | -  | Ι  | -  | -  | 1  | -  | Output short to ground is present.                  |  |

| -  | _  | -  | -  | -  | 1  | -  | -  | Open load is present.                               |  |

| -  | _  | -  | -  | 1  | -  | -  | -  | Shorted load is present.                            |  |

| -  | _  | _  | 1  | _  | _  | -  | -  | In a fault condition                                |  |

| -  | _  | 1  | -  | _  | _  | -  | -  | Performing load diagnostics                         |  |

| -  | 1  | -  | -  | -  | -  | -  | -  | In mute mode                                        |  |

| 1  | -  | -  | -  | -  | -  | -  | -  | In play mode                                        |  |

## Table 8. Control Register (0x03)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                                                                      |  |

|----|----|----|----|----|----|----|----|-----------------------------------------------------------------------------------------------|--|

| 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0 26-dB gain, switching frequency set to 400 kHz , SpeakerGuard protection circuitry disabled |  |

| -  | _  | -  | Ι  | _  | Ι  | Ι  | 1  | Switching frequency set to 500 khz                                                            |  |

| -  | -  | -  | -  | -  | 1  | 1  | -  | Reserved                                                                                      |  |

| -  | -  | 1  | 1  | 0  | Ι  | I  | -  | SpeakerGuard protection circuitry set to 14-V peak output                                     |  |

| -  | -  | 1  | 0  | 1  | Ι  | I  | -  | SpeakerGuard protection circuitry set to 11.8-V peak output                                   |  |

| -  | -  | 1  | 0  | 0  | Ι  | I  | -  | SpeakerGuard protection circuitry set to 9.8-V peak output                                    |  |

| -  | -  | 0  | 1  | 1  | 1  | 1  | -  | SpeakerGuard protection circuitry set to 8.4-V peak output                                    |  |

| -  | -  | 0  | 1  | 0  | Ι  | I  | -  | SpeakerGuard protection circuitry set to 7-V peak output                                      |  |

| -  | -  | 0  | 0  | 1  | Ι  | I  | -  | SpeakerGuard protection circuitry set to 5.9-V peak output                                    |  |

| -  | -  | 0  | 0  | 0  | -  | I  | -  | SpeakerGuard protection circuitry set to 5-V peak output                                      |  |

| 0  | 0  | -  | -  | -  | -  | I  | -  | Gain set to 20 dB                                                                             |  |

| 1  | 0  | -  | -  | -  | -  | -  | -  | Gain set to 32 dB                                                                             |  |

| 1  | 1  | -  | -  | -  | -  | -  | -  | Gain set to 36 dB                                                                             |  |

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

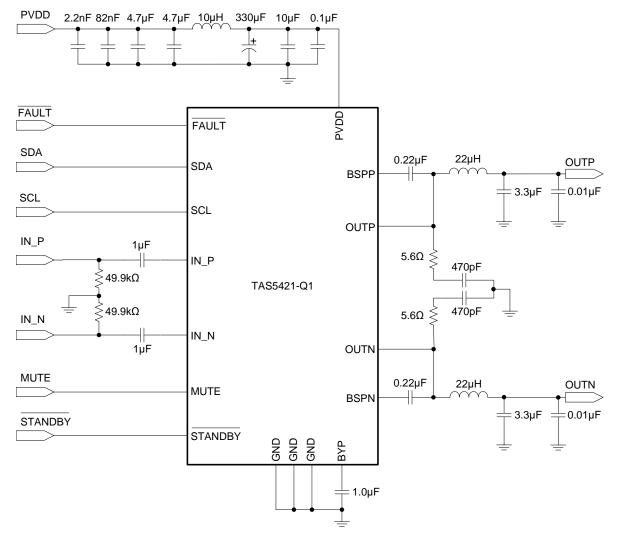

The device is a mono high-efficiency class-D audio amplifier. Typical use of the device is to amplify an audio input to drive a speaker. The intent of its use is for a bridge-tied load (BTL) application, not for support of single-ended configuration. This section presents how to use the device in the application, including what external components are necessary and how to connect unused pins.

#### 8.2 Typical Application

Figure 17. TAS5421-Q1 Typical Application Schematic

#### **Typical Application (continued)**

#### 8.2.1 Design Requirements

Power Supplies

The device needs only a single power supply compliant with the recommended operation range. The device is designed to work with either a vehicle battery or regulated power supply such as from a backup battery.

Communication

The device communicates with the system controller with both discrete hardware control pins and with  $I^2C$ . The device is an  $I^2C$  slave and thus requires a master. If a master  $I^2C$ -compliant device is not present in the system, it is still possible to use the device, but only with the default settings. Diagnostic information is limited to the discrete reporting FAULT pin.

External Components

Table 9 lists the components required for the device.

| EVM Designator | Quanity | Value          | Size                | Description                      | Use in Application                |

|----------------|---------|----------------|---------------------|----------------------------------|-----------------------------------|

| C7             | 1       | 10 µF ± 10%    | 1206                | X7R ceramic capacitor, 25-V      | Power supply                      |

| C8             | 1       | 330 µF ± 20%   | 10 mm               | Low-ESR aluminum capacitor, 25-V | Power supply                      |

| C9, C16, C20   | 3       | 1 μF ± 10%     | 0805                | X7R ceramic capacitor, 25-V      | Analog audio input filter, bypass |

| C10, C14       | 2       | 0.22 µF ± 10%  | 0603                | X7R ceramic capacitor, 25-V      | Bootstrap capacitors              |

| C11, C17       | 2       | 3.3 µF ± 10%   | 0805                | X7R ceramic capacitor, 25-V      | Amplifier output filtering        |

| C13, C15       | 2       | 470 pF ± 10%   | 0603                | X7R ceramic capacitor, 250-V     | Amplifier output snubbers         |

| C6             | 1       | 0.1 μF ± 10%   | 0603                | X7R ceramic capacitor, 25-V      | Power supply                      |

| C2             | 1       | 2200 pF ± 10%  | 0603                | X7R ceramic capacitor, 50-V      | Power supply                      |

| C3             | 1       | 0.082 µF ± 10% | 0603                | X7R ceramic capacitor, 25-V      | Power supply                      |

| C4, C5         | 2       | 4.7 μF ± 10%   | 1206                | X7R ceramic capacitor, 25-V      | Power supply                      |

| C12, C18       | 2       | 0.01 µF ± 10%  | 0603                | X7R ceramic capacitor, 25-V      | Output EMI filtering              |

| L1             | 1       | 10 µH ± 20%    | 13.5 mm<br>×13.5 mm | Shielded ferrite inductor        | Power supply                      |

| L2             | 1       | 22 µH ± 20%    | 8 mm × 8<br>mm      | Coupled inductor                 | Amplifier output filtering        |

| R5, R6         | 2       | 49.9 kΩ ± 1%   | 0805                | Resistors, 0.125-W               | Analog audio input filter         |

| R4, R7         | 2       | 5.6 Ω ± 5%     | 0805                | Resistors, 0.125-W               | Output snubbers                   |

**Table 9. Supporting Components**

#### 8.2.1.1 Amplifier Output Filtering

Output FETs drive the amplifier outputs in an H-bridge configuration. These transistors are either fully off or on. The result is a square-wave output signal with a duty cycle that is proportional to the amplitude of the audio signal. The amplifier outputs require a low-pass filter to filter out the PWM modulation carrier frequency. People frequently call this filter the L-C filter, due to the presence of an inductive element L and a capacitive element C to make up the 2-pole low-pass filter. The L-C filter attenuates the carrier frequency, reducing electromagnetic emissions and smoothing the current waveform which the load draws from the power supply. See the *Class-D LC Filter Design* application report, SLOA119, for a detailed description on proper component selection and design of an L-C filter based upon the desired load and response.

#### 8.2.1.2 Amplifier Output Snubbers

A snubber is an RC network placed at the output of the amplifier to dampen ringing or overshoot on the PWM output waveform. Overshoot and ringing has several negative impacts including: potential EMI sources, degraded audio performance, and overvoltage stress of the output FETs or board components. For more information on the use and design of output snubbers, see the *Class-D Output Snubber Design Guide*, SLOA201.

#### TAS5421-Q1

ZHCSCN7C-MARCH 2014-REVISED JANUARY 2015

#### 8.2.1.3 Bootstrap Capacitors

The output stage uses dual NMOS transistors; therefore, the circuit requires bootstrap capacitors for the high side of each output to turn on correctly. The required capacitor connection is from BSTN to OUTN and from BSTP to OUTP as shown in Figure 17.

#### 8.2.1.4 Analog Audio Input Filter

The circuit requires an input capacitor to allow biasing of the amplifier put to the proper dc level. The input capacitor and the input impedance of the amplifier form a high-pass filter with a –3-dB corner frequency determined by the equation:  $f = 1 / (2\pi R_{(i)}C_{(i)})$ , where  $R_{(i)}$  is the input impedance of the device based on the gain setting and  $C_{(i)}$  is the input capacitor value. Table 10 lists largest recommended input capacitor values. Use a capacitor which matches the application need for the lowest frequency but does not exceed the values listed.

| Gain (dB) | Typical Input Impedance (kΩ) | Input Capacitance (µF) | High-Pass Filter (Hz) |

|-----------|------------------------------|------------------------|-----------------------|

| 20        | 60                           | 1                      | 2.7                   |

|           |                              | 1.5                    | 1.8                   |

| 26        | 30                           | 1                      | 5.3                   |

|           |                              | 3.3                    | 1.6                   |

| 32        | 15                           | 5.6                    | 2.3                   |

| 36        | 9                            | 10                     | 1.8                   |

#### 8.2.2 Detailed Design Procedure

- Step 1: Hardware Schematic Design: Using the Typical Application Schematic as a guide, integrate the hardware into the system schematic.

- Step 2: Following the recommended layout guidelines, integrate the device and its supporting components into the system PCB file.

- Step 3: Thermal Design: The device has an exposed thermal pad which requires proper soldering. For more information, see the *Semiconductor and IC Package Thermal Metrics*, SPRA953, and the *PowerPAD Thermally Enhanced Package*, SLMA002G, application reports.

- Step 4: Develop software: The EVM User's Guide has detailed instructions for how to set up the device, interpret diagnostic information, and so forth. For information about control registers, see the *Register Maps* section.

- For questions and support go to the E2E forums.

#### 8.2.3 Application Curves

See the *Typical Characteristics* section for application performance plots.

#### 8.2.4 Unused Pin Connections

Even if unused, always connect pins to a fixed rail; do not leave them floating. Floating input pins represent an ESD risk, so adhere to the following guidance for each pin.

#### 8.2.4.1 MUTE Pin

If the MUTE pin is unused in the application, connect it to GND through a high-impedance resistor.

#### 8.2.4.2 STANDBY Pin

If the STANDBY pin is unused in the application, connect it to a low-voltage rail such as 3.3 V or 5 V through a high-impedance resistor.

#### 8.2.4.3 $\beta$ C Pins (SDA and SCL)

If there is no microcontroller in the system, use of the device without  $I^2C$  communication is possible. In this situation, connect the SDA and SCL pins to 3.3 V.

#### 8.2.4.4 Terminating Unused Outputs

If the FAULT pin does not report to a system microcontroller in the application, connect it to GND.

#### 8.2.4.5 Using a Single-Ended Audio Input

When using a single-ended audio source, ac-ground the negative input through a capacitor equal in value to the input capacitor on the positive input, and apply the audio source to the positive input. For best performance, the ac ground should be at the audio source instead of at the device input if possible.

## 9 Power Supply Recommendations

A car battery that can have a large voltage range most commonly provides power for the device. PVDD, a filtered battery voltage, is the supply for the output FETs and the low-side FET gate driver. Good power-supply decoupling is necessary, especially at low voltage and temperature levels. To meet the PVDD specifications in the *Electrical Characteristics* section, TI uses 10- $\mu$ F and 0.1- $\mu$ F ceramic capacitors near the PVDD pin along with a larger bulk 330- $\mu$ F electrolytic decoupling capacitor.

An internal linear regulator, which powers the analog circuitry, provides the voltage on the BYP pin. This supply requires an external bypass ceramic capacitor at the BYP pin.

#### 10 Layout

#### **10.1 Layout Guidelines**

The EVM layout optimizes for thermal dissipation and EMC performance. The TAS5421-Q1 device has a thermal pad down, and good thermal conduction and dissipation require adequate copper area. Layout also affects EMC performance. TAS5421Q1EVM illustrations form the basis for the layout discussions.

#### **10.2 Layout Examples**

#### 10.2.1 Top Layer

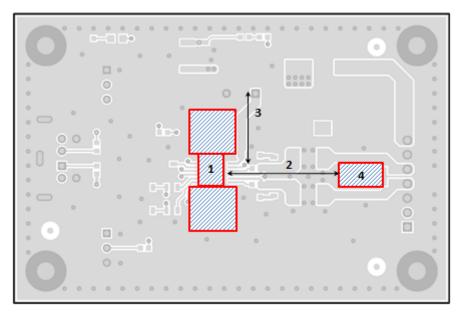

The red boxes around number 1 are the copper ground on the top layer. Soldered directly to the thermal pad, this ground is the first significant thermal dissipation needed. There are vias that go to the other layers for further thermal relief, but vias have high thermal resistance. TI recommends that use of this top layer be mostly for thermal dissipation. A further recommendation is short routes from output pins to the second-order LC filter for EMC suppression. The number 2 arrow indicates these short routes. The shorter the distance, the less EMC radiates. A short route from the PVDD pin to the LC filter from the battery or power source, as indicated by the number 3 arrow, also improves EMC suppression. The red box around number 4 indicates the ground plane that is common to both OUTP and OUTN. Place the capacitors of the LC filter in this common ground plane to help with common-mode noise and short ground loops.

Figure 18. Top Layer

#### Layout Examples (continued)

#### 10.2.2 Second Layer – Signal Layer

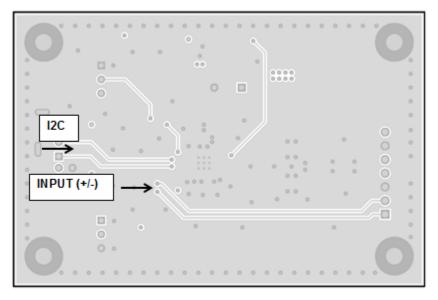

If possible, route the I<sup>2</sup>C and the positive and negative input traces close together and cover with ground plane, keeping the signals from noise.

Figure 19. Signal Layer

#### 10.2.3 Third Layer – Power Layer

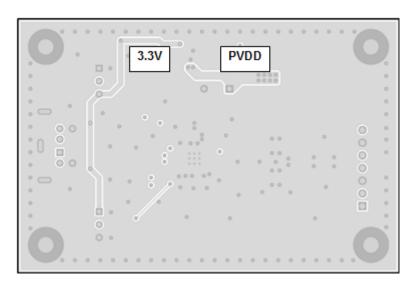

There is no need for a power plane, but TI recommends a wide single PVDD trace to keep the switching noise to a minimum and provide enough current to the device. The wide trace provides a low-impedance path from the power source to the PVDD pin and from the GND pin to the source return. Suppression of switching noise (ripple voltage) on both the positive and return (ground) paths requires a low impedance.

Figure 20. Power Layer

#### Layout Examples (continued)

#### 10.2.4 Bottom Layer – Ground Layer

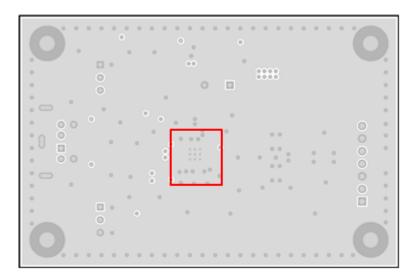

The device has an exposed thermal pad on the bottom side for improved thermal performance. Conducting heat from the thermal pad to other layers requires thermal vias. Because the bottom layer is the secondary heat exchange surface to ambient, the thermal vias area must have low thermal resistance, that is, no signal vias or traces that can increase thermal resistance from the thermal vias to the bottom copper.

Figure 21. Bottom Layer

## 11 器件和文档支持

#### 11.1 器件支持

#### 11.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

### 11.2 商标

PowerPAD is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.3 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可

#### 11.4 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

## 12 机械、封装和可订购信息

能会导致器件与其发布的规格不相符。

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 本数据随时可能发生变更并且不对本文档进行修订, 恕不另行通知。 要获得这份数据表的浏览器版本, 请查阅左侧导航栏。

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | e Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|----------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TAS5421QPWPRQ1   | ACTIVE        | HTSSOP       | PWP                  | 16   | 2000           | RoHS & Green    | NIPDAU                               | Level-3-260C-168 HR  | -40 to 125   | TAS5421                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

www.ti.com

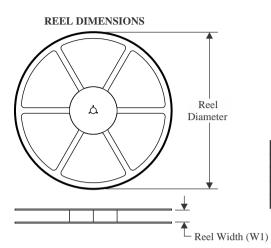

## TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nomina | d i |

|----------------------------|-----|

|                            |     |

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TAS5421QPWPRQ1 | HTSSOP          | PWP                | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com

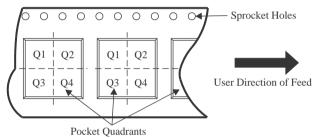

## PACKAGE MATERIALS INFORMATION

5-Dec-2023

| *All | dimensions | are | nominal |  |

|------|------------|-----|---------|--|

|------|------------|-----|---------|--|

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TAS5421QPWPRQ1 | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |  |

## **GENERIC PACKAGE VIEW**

## **PWP 16**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司