🕳 Order

Now

### bq24770, bq24773

ZHCSDO3C - AUGUST 2014 - REVISED DECEMBER 2016

# bq2477x 具有系统功率监视器 和处理器热量指示器的窄电压直流 (NVDC) 电池充电控制器

# 1 特性

- 主机控制的 NVDC-1 1-4 节电池充电控制器, 输入 电压范围为 4.5-24V

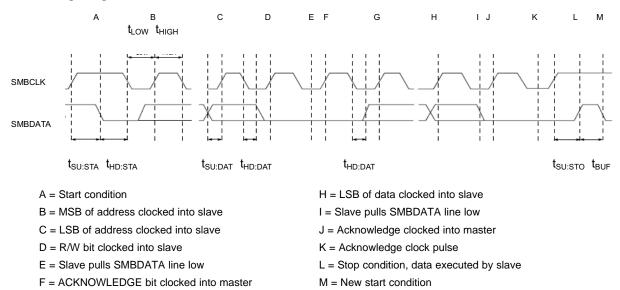

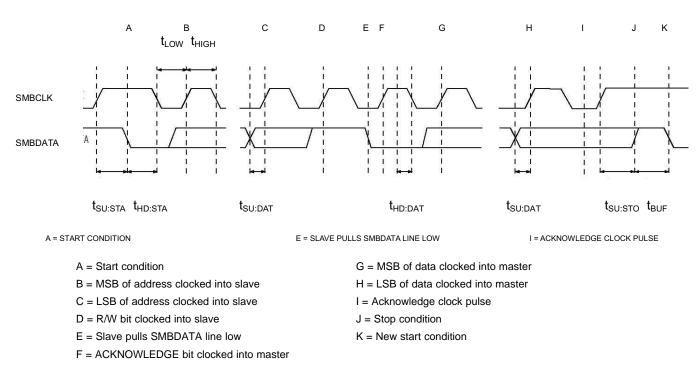

- 支持 SMBus (bq24770) 和 I2C (bq24773)

- 无电池或电池深度放电的情况下支持系统即时启动操作

- 可在适配器满载时进入补充模式,支持同步

BATFET 控制

- 100µs 超快速输入电流 DPM

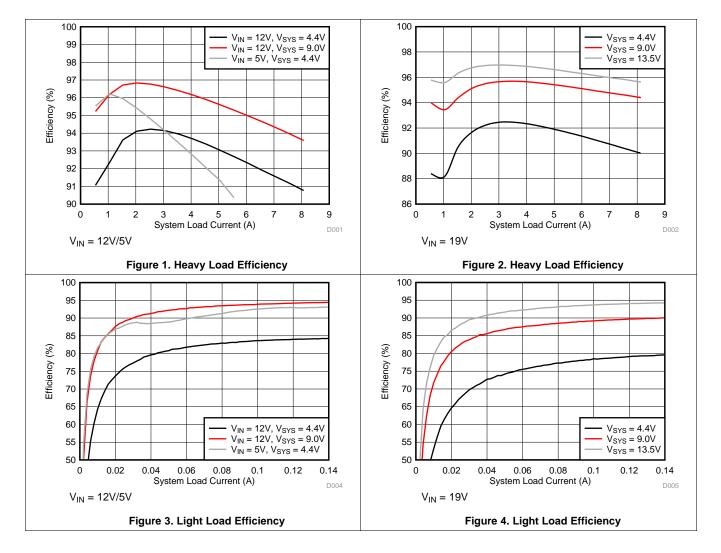

- 20mA 负载条件下,兼具 600μA 的超低静态电流和 >80% 的高脉冲频率调制 (PFM) 轻负载效率,符合 Energy Star 和 ERP Lot6 标准。

- 高精度电源/电流监视器,可限制 CPU 的运行速度

- 全面的 PROCHOT 配置

- 输入和电池电流监视器 (IADP/IBAT)

- 系统功率监视器 (PMON)

- 可编程输入电流限制、充电电压、充电电流和最小 系统电压调节

- ±0.5% 充电电压(16mV/步长)

- ±2% 输入/充电电流(64mA/步长)

- ±2% 40x 输入/16x 放电/20x 充电电流监视器

- 支持电池 LEARN (学习) 功能

- 高集成度

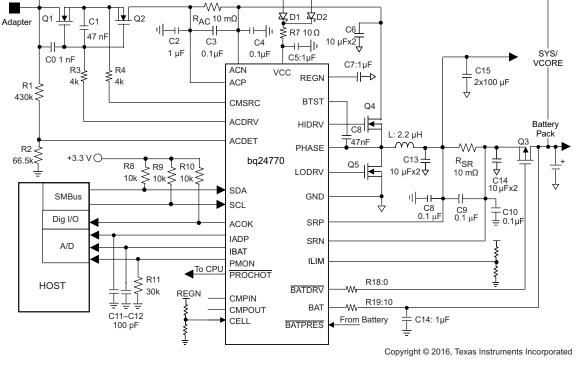

- N 沟道金属氧化物半导体 (NMOS) ACFET 和 RBFET 驱动器

- P 沟道金属氧化物半导体 (PMOS) 电池场效应 管 (FET) 栅极驱动器

- 内部环路补偿

- 独立比较器

- 支持自动涓流充电,用于唤醒电量监测计

- 600kHz 至 1.2MHz 的可编程开关频率

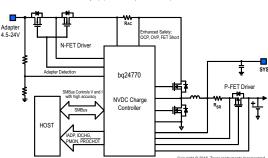

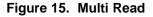

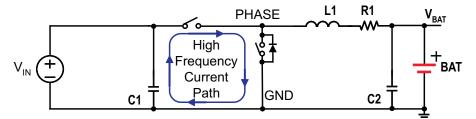

# 简化电路原理图

# 2 应用

- 超极本、笔记本、可拆卸平板电脑和常规平板电脑

- 手持式终端

- 工业、医疗、便携式设备

# 3 说明

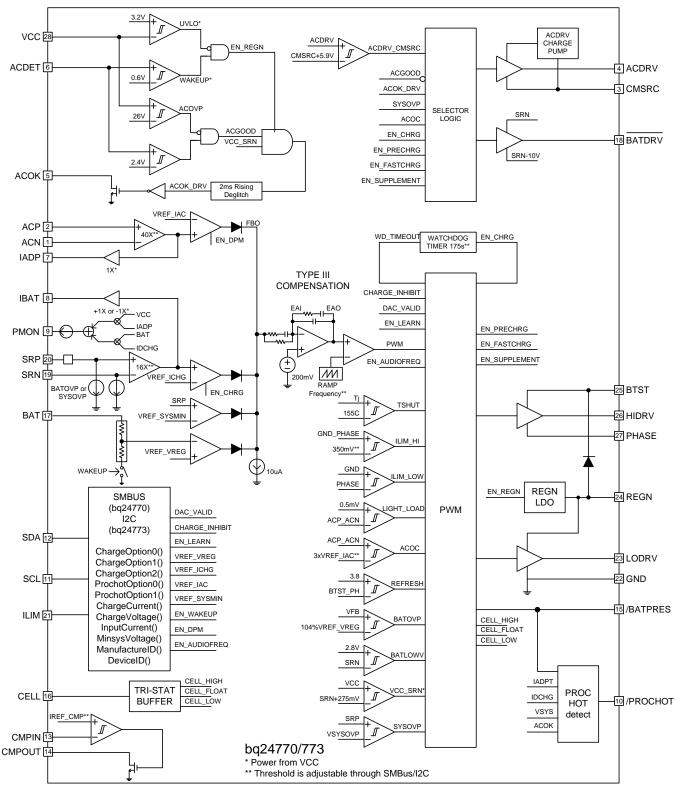

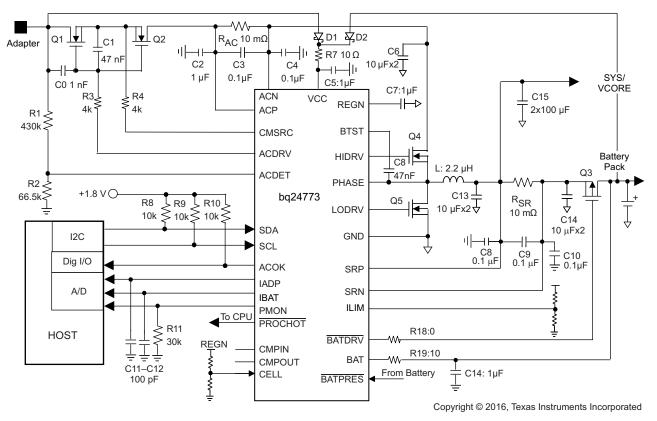

bq2477x 是一款高效同步的 NVDC-1 电池充电控制器,所含元件数较少,适用于空间受限的多化合物电池充电 解决方案。

电源路径管理可将系统电压稳定在电池电压,但不会低于最小系统电压(可编程)。借助该功能,即使在电池 完全放电或被移除的情况下,系统也能够保持运行。凭 借电源路径管理,电池可为系统提供补充电流,避免输 入电源发生过载。

bq2477x 可为 N 沟道 ACFET 和反向阻断 FET 提供驱动器和电源路径管理。该器件还提供了相应的驱动器以控制外部 P 沟道电池 FET 的 NVDC 操作。它还能够驱动开关稳压器的高侧和低侧金属氧化物半导体场效应晶体管 (MOSFET)。

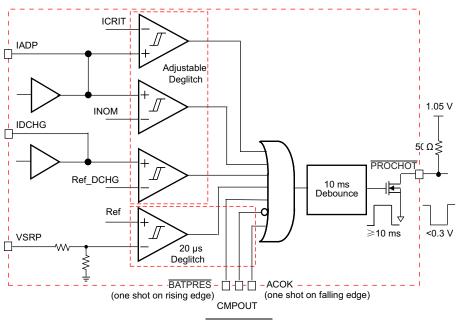

bq2477x 可监视适配器电流 (IADP)、电池充电/放电电流 (IBAT) 以及系统功率 (PMON)。该器件还具有可灵活编程的 PROCHOT 输出,可根据需要直接控制 CPU 降低其运行速度。

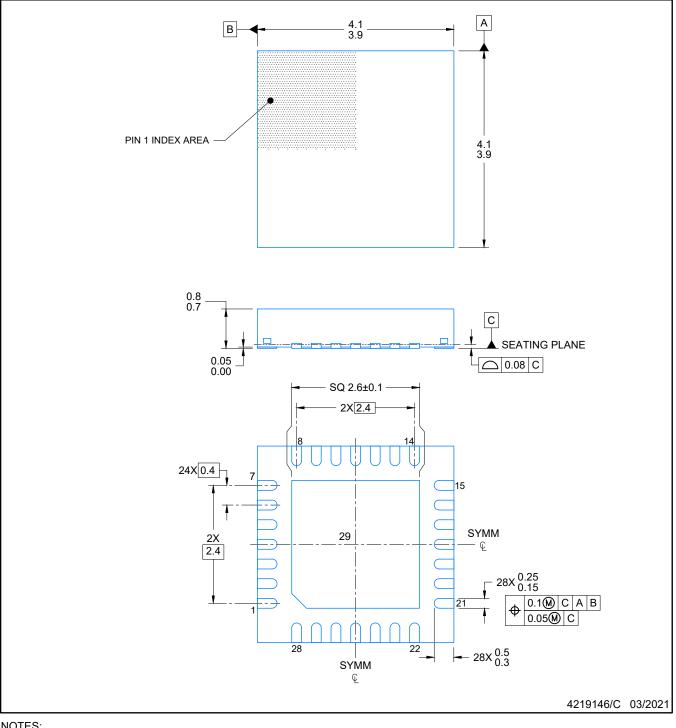

器件信息<sup>(1)</sup>

| 器件型号    | 封装          | 封装尺寸(标称值)                    |  |  |

|---------|-------------|------------------------------|--|--|

| bq24770 |             | 4.00mm x 4.00mm <sup>2</sup> |  |  |

| bq24773 | WQFN(28 引脚) |                              |  |  |

|         |             |                              |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

#### 轻负载效率 (V<sub>IN</sub> = 19.5V) 100 95 90 85 Efficiency (%) 80 75 70 65 60 V<sub>SYS</sub> = 9.0V V<sub>SYS</sub> = 13.5\ 55 50 0.02 0.04 0.06 0.08 0 System Load Current (A) 0.12 0.14

### bq24770, bq24773 ZHCSDO3C - AUGUST 2014 - REVISED DECEMBER 2016

| _ |      |                                   |    |

|---|------|-----------------------------------|----|

| 1 | 特性   |                                   | 1  |

| 2 | 应用   |                                   | 1  |

| 3 | 说明   |                                   | 1  |

| 4 | 修订   | 历史记录                              | 2  |

| 5 | Dev  | ice Comparison Table              | 3  |

| 6 | Pin  | Configuration and Functions       | 3  |

| 7 | Spe  | cifications                       | 5  |

|   | 7.1  | Absolute Maximum Ratings          | 5  |

|   | 7.2  | ESD Ratings                       | 5  |

|   | 7.3  | reconnected operating contaitorie |    |

|   | 7.4  | Thermal Information               | 6  |

|   | 7.5  | Electrical Characteristics        | 6  |

|   | 7.6  | Timing Requirements               | 12 |

|   | 7.7  | Typical Characteristics           | 13 |

| 8 | Deta | ailed Description                 | 14 |

|   | 8.1  | Overview                          | 14 |

|   | 8.2  | Functional Block Diagram          | 15 |

|   | 8.3  | Feature Description               | 16 |

|   |      |                                   |    |

# 4 修订历史记录

| CI | hanges from Revision B (October 2014) to Revision C | Page |

|----|-----------------------------------------------------|------|

| •  | 首次公开发布的完整数据表                                        | 1    |

|    |                                                     |      |

# Changes from Revision A (October 2014) to Revision B

| • | 己将简化电路原理图中的"混合动力升压充电"更改为"NVDC 充电"                                                  | 1    |

|---|------------------------------------------------------------------------------------|------|

| • | Changed Equation 1 From: "V = K <sub>(PMON)</sub> " To:" I = K <sub>(PMON)</sub> " | 17   |

| • | Changed 0x2011H to 0x0211H in the POS STATE column of Table 4                      | . 26 |

| • | Changed 0x4854H to 0x4B54H in the POS STATE column of Table 4                      | . 26 |

| • | Changed Table 7, column "SMBus 0x3CH" To: "SMBus 0x38H"                            | . 29 |

# Changes from Original (August 2014) to Revision A

| • | Changed the equation in the description of pin 21 From: $V_{(ILIM)} = 20 \times IDPM \times (V_{(ACP)} - V_{(ACN)})$ To: $V_{(ILIM)} = 20 \times IDPM \times R_{AC}$ | 4    |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed the t <sub>f</sub> MAX value From 300 µs To: 300 ns                                                                                                          |      |

| • | Added a new first paragraph to the Learn Mode section                                                                                                                | . 19 |

| • | Added a NOTE to the Application and Implementation section                                                                                                           | . 36 |

| • | Changed Figure 21                                                                                                                                                    | . 36 |

| • | Changed Figure 36                                                                                                                                                    | . 43 |

|    | 8.4  | Device Functional Modes      | 21 |

|----|------|------------------------------|----|

|    | 8.5  | Programming                  | 21 |

|    | 8.6  | Register Maps                | 26 |

| 9  | Appl | ication and Implementation   | 36 |

|    | 9.1  | Application Information      | 36 |

|    | 9.2  | Typical Application, bq24770 | 36 |

| 10 | Pow  | er Supply Recommendations    | 44 |

| 11 | Layo | out                          | 44 |

|    | 11.1 | Layout Guidelines            | 44 |

|    | 11.2 | Layout Example               | 45 |

| 12 | 器件   | 和文档支持                        | 46 |

|    | 12.1 | 相关链接                         | 46 |

|    | 12.2 | 接收文档更新通知                     | 46 |

|    | 12.3 | 社区资源                         | 46 |

|    | 12.4 | 商标                           | 46 |

|    | 12.5 | 静电放电警告                       | 46 |

|    | 12.6 | Glossary                     | 46 |

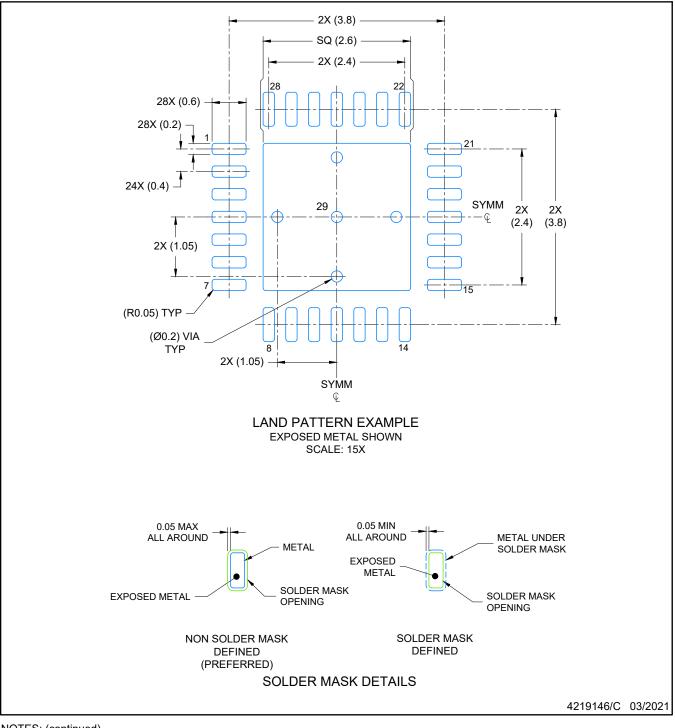

| 13 | 机械   | 、封装和可订购信息                    | 46 |

|    |      |                              |    |

# 目录

www.ti.com.cn

# Page

Page

# 5 Device Comparison Table

|                             | bq24770            | bq24773          |  |  |

|-----------------------------|--------------------|------------------|--|--|

| Communication Interface     | SMBus              | 12C              |  |  |

| Communication Address       | 0x12H (0x00010010) | D4H (0x11010100) |  |  |

| Default Switching Frequency | 800kHz             | 1.2MHz           |  |  |

| Default Input Current Limit | 3200mA             | 2944mA           |  |  |

| Device ID                   | 0x0114H            | 0x41H            |  |  |

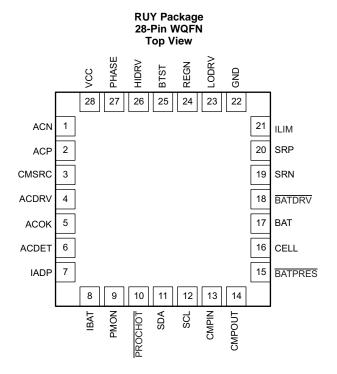

# 6 Pin Configuration and Functions

# **Pin Functions**

| PIN | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                 |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | ACN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input current sense resistor negative input. Place an optional 0.1-µF ceramic capacitor from ACN to GND for common-mode filtering. Place a 0.1-µF ceramic capacitor from ACN to ACP to provide differential mode filtering. |  |  |  |  |

| 2   | ACP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input current sense resistor positive input. Place a 1-µF and 0.1-µF ceramic capacitor from ACP to GND for common-mode filtering. Place a 0.1-µF ceramic capacitor from ACN to ACP to provide differential-mode filtering.  |  |  |  |  |

| 3   | ACDRV charge pump source input. Place a 4 kΩ resistor from CMSRC to the common source of ACFET (Q1) and RBFET (Q2) limits the in-rush current on CMSRC pin.<br>When CMSRC is grounded, ACDRV pin becomes logic output internally puled up to REGN. ACDRV HIGH indicat to external driver that ACFET/RBFET can be turned on. It directly drives CMOS logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                             |  |  |  |  |

| 4   | <ul> <li>ACDRV</li> <li>Charge pump output to drive both adapter input n-channel MOSFET (ACFET) and reverse blocking n-ch<br/>MOSFET (RBFET). ACDRV voltage is 6 V above CMSRC to turn on ACFET/RBFET when ACOK goes<br/>Place a 4 kΩ resistor from ACDRV to the gate of ACFET and RBFET limits the in-rush current on ACDR<br/>When CMSRC is grounded, ACDRV pin becomes logic output internally pulled up to REGN. ACDRV HI<br/>indicates that ACFET/RBFET can be turned on. It directly drives CMOS logic.</li> <li>ACOK</li> <li>ACOK</li> <li>ACOK</li> <li>ACOK</li> <li>ACOK</li> <li>ACOK</li> <li>Charge pump output to drive both adapter is present (ACDET above 2.4 V, VCC above UVLO but below ACC<br/>above BAT). If any of the above conditions is not valid, ACOK is pulled LOW by internal MOSFET. Conr<br/>kΩ pull up resistor from ACOK to the pull-up supply rail.</li> </ul> |                                                                                                                                                                                                                             |  |  |  |  |

| 5   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                             |  |  |  |  |

# **bq24770**, **bq24773** ZHCSDO3C – AUGUST 2014 – REVISED DECEMBER 2016

www.ti.com.cn

Texas Instruments

# Pin Functions (continued)

| PIN | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6   | ACDET   | Adapter detection input. Program adapter valid input threshold by connecting a resistor divider from adapter input to ACDET pin to GND pin.<br>When ACDET pin is above 0.6 V and VCC is above UVLO, REGN LDO is present, ACOK comparator, and input current monitor buffer (IADP) are all active. Independent comparator, IBAT buffer, PMON buffer and PROCHOT can be enabled with SMBus/I2C.<br>When ACDET pin is above 2.4 V, and VCC is above BAT, but below ACOV, ACOK goes HIGH. ACFET/RBFET turns on. |  |  |

| 7   | IADP    | Buffered adapter current output. $V_{(IADP)} = 40$ or $80 \times (V_{(ACP)} - V_{(ACN)})$<br>The ratio of 40x and 80x is selectable with SMBus/I2C. Place 100pF or less ceramic decoupling capacitor from IADP pin to GND. This pin can be floating if it is not in use. IADP output voltage is clamped below 3.3 V.                                                                                                                                                                                        |  |  |

| 8   | IBAT    | Buffered battery current selected by SMBus/I2C. $V_{(IBAT)} = 20 \times (V_{(SRP)} - V_{(SRN)})$ for charge current, or $V_{(IBAT)} = 8$ or 16 × ( $V_{(SRN)} - V_{(SRP)}$ ) for discharge current, with ratio selectable through SMBus/I2C. Place 100pF or less ceramic decoupling capacitor from IBAT pin to GND. This pin can be floating if not in use. Its output voltage is clamped below 3.3 V.                                                                                                      |  |  |

| 9   | PMON    | Current mode system power monitor. The output voltage is proportional to the total power from the adapter and battery. The gain is selectable through SMBus/I2C. This pin can be floating if not in use. Its output voltage is clamped below 3.3 V. The maximum cap on PMON is 100 pF.                                                                                                                                                                                                                      |  |  |

| 10  | PROCHOT | Active low open drain output of "processor hot" indicator. It monitors adapter input current, battery discharge current, and system voltage. After any event in the PROCHOT profile is triggered, a minimum 10-ms pulse is asserted.                                                                                                                                                                                                                                                                        |  |  |

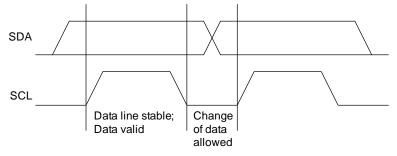

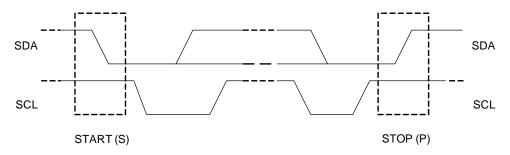

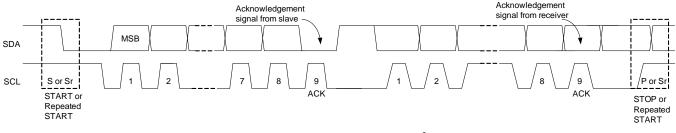

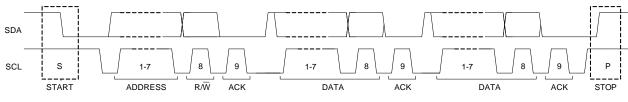

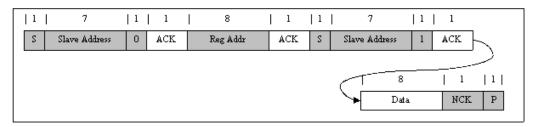

| 11  | SDA     | SMBus/I2C open-drain data I/O. Connect to data line from the host controller or smart battery. Connect a 10-k $\Omega$ pull-up resistor according to SMBus/I2C specifications.                                                                                                                                                                                                                                                                                                                              |  |  |

| 12  | SCL     | SMBus/I2C clock input. Connect to clock line from the host controller or smart battery. Connect a 10-k $\Omega$ pull-up resistor according to SMBus/I2C specifications.                                                                                                                                                                                                                                                                                                                                     |  |  |

| 13  | CMPIN   | Input of independent comparator. Internal reference, output polarity and deglitch time is selectable by SMBus/I2C. With polarity HIGH (0x3B[6]=1), place a resistor between CMPIN and CMPOUT to program hysteresis. With polarity LOW (0x3B[6]=0), the internal hysteresis is 100 mV. If the independent comparator is not in use, tie CMPIN to ground.                                                                                                                                                     |  |  |

| 14  | CMPOUT  | Open-drain output of independent comparator. Place $10k\Omega$ pull-up resistor from CMPOUT to pull-up supply rail. Internal reference, output polarity and deglitch time are selectable by SMBus/I2C.                                                                                                                                                                                                                                                                                                      |  |  |

| 15  | BATPRES | Active low battery present input signal. LOW indicates battery present, HIGH indicates battery absent. When BATPRES pin goes from LOW to HIGH, the device exits LEARN mode, and disable charge. REG 0x15() value goes back to default. Host can enable IDPM and charge through SMBus/I2C when BATPRES is HIGH.                                                                                                                                                                                              |  |  |

| 16  | CELL    | Battery cell selection pin. GND for 1-cell, Float for 2-cell, and HIGH for 3- or 4-cell. CELL pin is biased from REGN. Before host writes to MaxChargeVoltage(), MaxChargeVotage() follows the CELL pin setting. CELL pin also sets SYSOVP threshold. GND for 5 V, Float for 12 V and HIGH for 18.5 V. When REG 0x15() is above 15V, SYSOVP is disabled.                                                                                                                                                    |  |  |

| 17  | BAT     | Battery-voltage remote sense. Directly connect a Kelvin sense trace from the battery-pack positive terminal to the BAT pin to accurately sense the battery pack voltage. Place a $0.1$ - $\mu$ F capacitor from BAT to GND close to the IC to filter high-frequency noise.                                                                                                                                                                                                                                  |  |  |

| 18  | BATDRV  | P-channel battery FET (BATFET) gate driver output. It is shorted to SRN to turn off the BATFET. It goes below SRN to turn on BATFET. BATFET is in linear mode to regulate SYS at minimum system voltage when battery is depleted. BATFET is fully on during fast charge and supplement mode. Connect the source of the BATFET to charge current sensing node SRN pin, and the drain of the BATFET to the battery pack positive node BAT pin.                                                                |  |  |

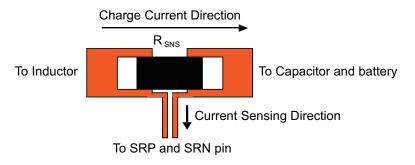

| 19  | SRN     | Charge current sense resistor negative input. SRN pin is for battery voltage sensing as well. Connect SRN pin with a 0.1µF ceramic capacitor to GND for common-mode filtering. Connect a 0.1-µF ceramic capacitor from SRP to SRN to provide differential mode filtering.                                                                                                                                                                                                                                   |  |  |

| 20  | SRP     | Charge current sense resistor positive input. Connect a 0.1-µF ceramic capacitor from SRP to SRN to provide differential mode filtering.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 21  | ILIM    | Input current limit input. Program ILIM voltage by connecting a resistor divider from supply rail to ILIM pin to GND pin. The ILIM voltage is calculated as: $V_{(ILIM)} = 20 \times IDPM \times R_{AC}$ , in which IDPM is the target regulation current. The lower of ILIM voltage and DAC limit voltage sets input current regulation limit. Host can ignore the IDPM setting from ILIM pin by setting 0x38[7]=0.                                                                                        |  |  |

| 22  | GND     | IC ground. On PCB layout, connect to analog ground plane, and only connect to power ground plane through the power pad underneath IC.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 23  | LODRV   | Low side power MOSFET driver output. Connect to low side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 24  | REGN    | 5.4V linear regulator output supplied from VCC. The LDO is active when ACDET above 0.6V, VCC above UVLO. Connect a 1μF ceramic capacitor from REGN to power ground.                                                                                                                                                                                                                                                                                                                                         |  |  |

### **Pin Functions (continued)**

| PIN | NAME                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                            |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 25  | BTST                                                                                                                                                                                                                                                                                                           | High side power MOSFET driver power supply. Connect a 0.047-µF capacitor from BTST to PHASE. The bootstrap diode between REGN and BTST is integrated.                                                                  |  |  |

| 26  | HIDRV                                                                                                                                                                                                                                                                                                          | High side power MOSFET driver output. Connect to the high side n-channel MOSFET gate.                                                                                                                                  |  |  |

| 27  | PHASE                                                                                                                                                                                                                                                                                                          | High side power MOSFET driver source. Connect to the source of the high side n-channel MOSFET.                                                                                                                         |  |  |

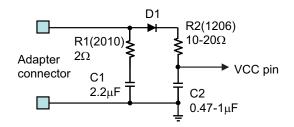

|     |                                                                                                                                                                                                                                                                                                                | Input supply from adapter or battery. Place Schottky diode-OR from adapter/battery. After the Schottky diode, place $10-\Omega$ resistor and $1-\mu$ F capacitor to ground as low pass filter to limit inrush current. |  |  |

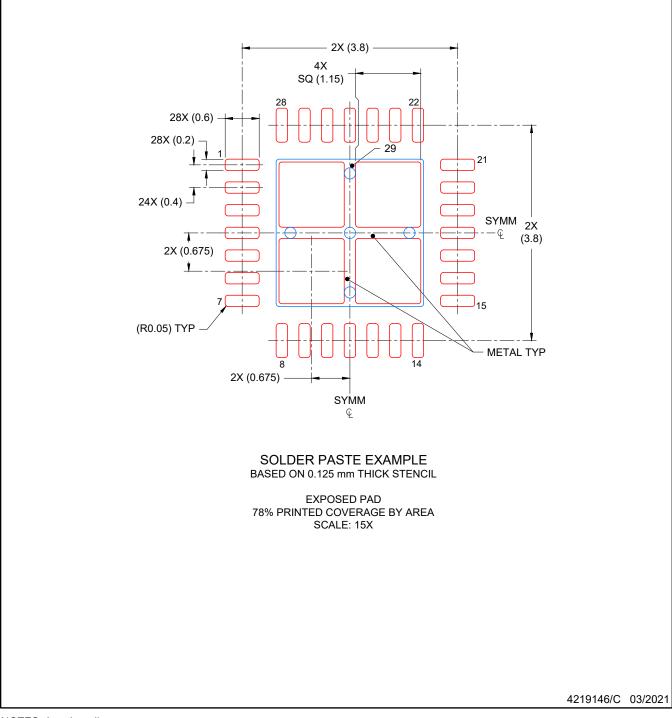

|     | Thermal Pad Exposed pad beneath the IC. Analog ground and power ground star-connected only at the thermal pad plan<br>Always solder thermal pad to the board, and have vias on the thermal pad plane connecting to analog group<br>power ground planes. It also serves as a thermal pad to dissipate the heat. |                                                                                                                                                                                                                        |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                      |                                                                                          | MIN  | MAX | UNIT |

|----------------------|------------------------------------------------------------------------------------------|------|-----|------|

|                      | SRN, SRP, ACN, ACP, CMSRC, VCC, BAT, BATDRV                                              | -0.3 | 30  | V    |

|                      | PHASE                                                                                    | -2.0 | 30  | V    |

|                      | BTST, HIDRV, ACDRV                                                                       | -0.3 | 36  | V    |

|                      | LODRV (2% duty cycle)                                                                    | -4.0 | 7   | V    |

| Voltage range        | HIDRV (2% duty cycle)                                                                    | -4.0 | 36  | V    |

|                      | PHASE (2% duty cycle)                                                                    | -4.0 | 30  | V    |

|                      | ACDET, SDA, SCL, LODRV, REGN, IADP, IBAT, PMON, BATPRES, ACOK, CELL, CMPIN, CMPOUT, ILIM | -0.3 | 7   | V    |

|                      | PROCHOT                                                                                  | -0.3 | 5.5 | V    |

| Differential values  | BTST-PHASE, HIDRV-PHASE                                                                  | -0.3 | 7   | V    |

| Differential voltage | SRP–SRN, ACP–ACN                                                                         | -0.5 | 0.5 | V    |

| Junction temperature | range, T <sub>J</sub>                                                                    | -40  | 155 | °C   |

| Storage temperature  | range, T <sub>stg</sub>                                                                  | -55  | 155 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the data book for thermal limitations and considerations of packages.

# 7.2 ESD Ratings

|             |                            |                                                                                   | MIN | MAX | UNIT |

|-------------|----------------------------|-----------------------------------------------------------------------------------|-----|-----|------|

|             | Flastrastatia              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>       | 0   | 2   | kV   |

| $V_{(ESD)}$ | Electrostatic<br>discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(2)}$ | 0   | 500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# bq24770, bq24773

ZHCSDO3C - AUGUST 2014 - REVISED DECEMBER 2016

Texas Instruments

www.ti.com.cn

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                      |                                                                                          | MIN   | MAX  | UNIT |

|------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|------|

|                                                      | ACN, ACP, CMSRC, VCC                                                                     | 0     | 24   | V    |

|                                                      | BATDRV, BAT, SRN, SRP                                                                    | 0     | 19.2 | V    |

|                                                      | PHASE                                                                                    | -2    | 24   | V    |

| Voltage range                                        | BTST, HIDRV, ACDRV                                                                       | 0     | 30   | V    |

|                                                      | ACDET, SDA, SCL, LODRV, REGN, IADP, IBAT, PMON, BATPRES, ACOK, CELL, CMPIN, CMPOUT, ILIM | 0     | 6.5  | V    |

|                                                      | PROCHOT                                                                                  | -0.3  | 5.3  | V    |

| Differential voltage                                 | BTST-PHASE, HIDRV-PHASE                                                                  | 0     | 6.5  | V    |

| Differential voltage                                 | SRP–SRN, ACP–ACN                                                                         | -0.35 | 0.35 | V    |

| Junction temperature range, T <sub>J</sub>           |                                                                                          | -20   | 125  | °C   |

| Operating free-air temperature range, T <sub>A</sub> |                                                                                          | -40   | 85   | °C   |

# 7.4 Thermal Information

|                       |                                              | bq2477x    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RUY (WQFN) | UNIT |

|                       |                                              | 28 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 33.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.7       | °C/W |

| $R_{\thetaJB}$        | Junction-to-board thermal resistance         | 6.5        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 6.5        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.3        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

$4.5V \le V_{(VCC)} \le 24V, -20^{\circ}C \le T_{J} \le 125^{\circ}C, \text{ typical values are at } T_{A} = 25^{\circ}C, \text{ with respect to GND (unless otherwise noted)}$

|                               | PARAMETER                                                                                                        | TEST CONDITION               | MIN T                                                                                                                                                                                                                                                                                                | P MAX | UNIT |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--|

| OPERATING CON                 | DITIONS                                                                                                          |                              | 4.5         24           1.024         19.2           9.216         9.216           -2%         2%           6.144         -3%           -3%         3%           3.584         -3%           1.024         19.2           13.504         -2%           -2%         2%           9.008         9.008 |       |      |  |

| V <sub>(IN_OP)</sub>          | Input voltage operating range                                                                                    |                              | 4.5                                                                                                                                                                                                                                                                                                  | 24    | V    |  |

| MINIMUM SYSTEM                | I VOLTAGE REGULATION (0x3E REGIS                                                                                 | TER)                         |                                                                                                                                                                                                                                                                                                      |       |      |  |

| V <sub>(SYSMIN_RNG)</sub>     | System voltage regulation range                                                                                  |                              | 1.024                                                                                                                                                                                                                                                                                                | 19.2  | V    |  |

|                               |                                                                                                                  | Minovetem)/oltoge/\_0v240011 | 9.2                                                                                                                                                                                                                                                                                                  | 16    | V    |  |

|                               | Minsystem voltage regulation<br>accuracy<br>Minsystem Voltage ()<br>Minsystem Voltage ()<br>Minsystem Voltage () | MinsystemVoltage()=0x2400H   | -2%                                                                                                                                                                                                                                                                                                  | 2%    |      |  |

|                               |                                                                                                                  |                              | 6.1                                                                                                                                                                                                                                                                                                  | 44    | V    |  |

| V(MINSYS_REG_ACC)             |                                                                                                                  | Minsystem voltage()=0x1800H  | -3%                                                                                                                                                                                                                                                                                                  | 3%    |      |  |

|                               |                                                                                                                  |                              | 3.5                                                                                                                                                                                                                                                                                                  | 84    | V    |  |

|                               |                                                                                                                  | Minsystem voltage()=0x0E00H  | -3%                                                                                                                                                                                                                                                                                                  | 3%    |      |  |

| MAXIMUM SYSTE                 | M VOLTAGE REGULATION (0x15 REGIS                                                                                 | TER, CHARGE DISABLE)         |                                                                                                                                                                                                                                                                                                      |       |      |  |

| V <sub>(SYSMAX_RNG)</sub>     | System voltage regulation range                                                                                  |                              | 1.024                                                                                                                                                                                                                                                                                                | 19.2  | V    |  |

|                               |                                                                                                                  |                              | 13.5                                                                                                                                                                                                                                                                                                 | 04    | V    |  |

|                               |                                                                                                                  | MaxChargVoltage() = 0x34C0H  | -2%                                                                                                                                                                                                                                                                                                  | 2%    |      |  |

| .,                            | Maximum system voltage regulation                                                                                |                              | 9.0                                                                                                                                                                                                                                                                                                  | 08    | V    |  |

| V <sub>(MAXSYS_REG_ACC)</sub> | accuracy                                                                                                         | MaxChargVoltage() = 0x2330H  | -3%                                                                                                                                                                                                                                                                                                  | 3%    |      |  |

|                               |                                                                                                                  | MaxChargVoltage() = 0x1130H  | 4                                                                                                                                                                                                                                                                                                    | 1.4   | V    |  |

|                               |                                                                                                                  |                              | -3%                                                                                                                                                                                                                                                                                                  | 3%    |      |  |

# **Electrical Characteristics (continued)**

$4.5V \le V_{(VCC)} \le 24V$ ,  $-20^{\circ}C \le T_{J} \le 125^{\circ}C$ , typical values are at  $T_{A} = 25^{\circ}C$ , with respect to GND (unless otherwise noted)

|                             | PARAMETER                                                                                                            | TEST CONDITION                                               | MIN   | TYP    | MAX   | UNIT |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|--------|-------|------|

| CHARGE VOLTAG               | E REGULATION (0x15 REGISTER, CHARG                                                                                   | E ENABLE)                                                    |       |        |       |      |

| V <sub>(BAT_RGN)</sub>      | Battery voltage range                                                                                                |                                                              | 1.024 |        | 19.2  | V    |

|                             |                                                                                                                      | ChargeVoltage() = 0x41A0H                                    |       | 16.8   |       | V    |

|                             |                                                                                                                      |                                                              | -0.5% |        | 0.5%  |      |

|                             |                                                                                                                      | ChargeVoltage() = 0x3130H                                    |       | 12.592 |       | V    |

| V <sub>(BAT_REG_ACC)</sub>  | Battery voltage regulation accuranc (0°C -                                                                           |                                                              | -0.5% |        | 0.5%  |      |

| (2,11_120_100)              | 85°C)                                                                                                                | ChargeVoltage() = 0x20D0H                                    |       | 8.4    |       | V    |

|                             |                                                                                                                      |                                                              | -0.6% |        | 0.6%  | .,   |

|                             |                                                                                                                      | ChargeVoltage() = 0x1070H                                    | 40/   | 4.208  | 40/   | V    |

| CHARGE CURREN               |                                                                                                                      |                                                              | -1%   |        | 1%    |      |

| CHARGE CORREN               | Charge current regulation differential                                                                               |                                                              |       |        |       |      |

| $V_{(IREG_CHG_RNG)}$        | voltage range                                                                                                        | $V_{(IREG\_CHG)} = V_{(SRP)} - V_{(SRN)}$                    | 0     |        | 81.28 | mV   |

|                             |                                                                                                                      |                                                              |       | 4096   |       | mA   |

|                             |                                                                                                                      | ChargeCurrent() = 0x1000H                                    | -2%   |        | 2%    |      |

|                             |                                                                                                                      | CharaeCurrent() = 0x0800H                                    |       | 2048   |       | mA   |

|                             | Charge current regulation accuracy 10 $\Omega$<br>current sensing resistor, V <sub>BAT</sub> > V <sub>(SYSMIN)</sub> | ChargeCurrent() = 0x0800H                                    | -4%   |        | 3%    |      |

| I(CHRG_REG_ACC)             | (0°C - 85°C)                                                                                                         | ChargeCurrent() = 0x0400H                                    |       | 1024   |       | mA   |

|                             |                                                                                                                      |                                                              | -6%   |        | 5%    |      |

|                             |                                                                                                                      | ChargeCurrent() = 0x0200H                                    |       | 512    |       | mA   |

|                             |                                                                                                                      |                                                              | -12%  |        | 10%   |      |

|                             | Pre-charge current clamp (2s-4s)                                                                                     | CELL = Float or High, BAT below 0x3E(), in LDO mode          |       | 384    |       | mA   |

| I <sub>(CLAMP)</sub>        | Pre-charge current clamp (1s only)                                                                                   | CELL = LOW, BAT below BATLOWV threshold                      |       | 384    |       | mA   |

|                             | Fast charge current clamp (1s only)                                                                                  | CELL = LOW, BAT above BATLOWV threshold,<br>but below 0x3E() |       | 2      |       | А    |

| PRECHARGE CUR               | RENT REGULATION IN LDO MODE                                                                                          |                                                              |       |        |       |      |

|                             | Precharge current regulation accuracy,<br>V <sub>BAT</sub> > V <sub>(SYSMIN)</sub> (0°C - 85°C)                      | ChargeCurrent() = 0x0180H                                    |       | 384    |       | mA   |

|                             |                                                                                                                      |                                                              | -15%  |        | 15%   |      |

|                             |                                                                                                                      | ChargeCurrent() = 0x0100H                                    |       | 256    |       | mA   |

|                             |                                                                                                                      |                                                              | -20%  |        | 20%   |      |

| (PRECHRG_REG_ACC)           |                                                                                                                      | ChargeCurrent() = 0x00C0H<br>ChargeCurrent() = 0x0080H       |       | 192    |       | mA   |

|                             |                                                                                                                      |                                                              | -25%  |        | 25%   |      |

|                             |                                                                                                                      |                                                              |       | 128    |       | mA   |

|                             |                                                                                                                      |                                                              | -30%  |        | 30%   |      |

| I(LEAK_SRP_SRN)             | SRP, SRN leakage current mismatch                                                                                    |                                                              | -21   |        | 21    | μA   |

| LDO MODE TO FA              | ST CHARGE COMPARATOR                                                                                                 | Ι                                                            |       |        |       |      |

| V <sub>(BAT_SYSMIN)</sub>   | LDO mode to fast charge mode threshold, $V_{\text{BAT}}$ rising                                                      | as percentage of 0x3E()                                      | 94%   | 96%    | 99%   |      |

| V(BAT_SYSMIN_HYST)          | Fast charge mode to LDO mode threshold hysteresis                                                                    | as percentage of 0x3E()                                      |       | 4%     |       |      |

| INPUT CURRENT I             | REGULATION                                                                                                           |                                                              |       |        |       |      |

| V <sub>(IREG_DPM_RNG)</sub> | Input current regulation differential voltage range                                                                  | $V_{(IREG_DPM)} = V_{(ACP)} - V_{(ACN)}$                     | 0     |        | 81.28 | mV   |

|                             |                                                                                                                      | ChargeCurrent() = 0x1000H                                    |       | 4096   |       | mA   |

|                             |                                                                                                                      |                                                              | -2    |        | 2%    |      |

|                             |                                                                                                                      | ChargeCurrent() = 0x0800H                                    |       | 2048   |       | mA   |

| Lanu ar                     | Input current regulation accuracy                                                                                    |                                                              | -3    |        | 3%    |      |

| (DPM_REG_ACC)               |                                                                                                                      | ChargeCurrent() - 0x040011                                   |       | 1024   |       | mA   |

|                             |                                                                                                                      | ChargeCurrent() = 0x0400H                                    | -5    |        | 5%    |      |

|                             |                                                                                                                      | ChargeCurrent() = 0x0200H                                    | L     | 512    |       | mA   |

|                             |                                                                                                                      |                                                              | -10   |        | 10%   |      |

ZHCSDO3C - AUGUST 2014 - REVISED DECEMBER 2016

www.ti.com.cn

# **Electrical Characteristics (continued)**

| $4.5V \le V_{(VCC)} \le 24V$ , $-20^{\circ}C \le T_{J} \le 125^{\circ}C$ , typical va | lues are at $T_A = 25^{\circ}C$ , with respect to GNI | D (unless otherwise note | d) |

|---------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------|----|

|                                                                                       |                                                       |                          |    |

|                               | PARAMETER                                                                                                                                                                                       | TEST CONDITION                                                                             | MIN   | TYP  | MAX        | UNIT |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------|------|------------|------|

| I(LEAK_ACP_ ACN)              | ACP, ACN leakage current mismatch                                                                                                                                                               |                                                                                            | —11   |      | 20         | μA   |

| INPUT CURRENT                 | SENSE AMPLIFIER                                                                                                                                                                                 |                                                                                            |       |      |            |      |

| V <sub>(ACP/N_OP)</sub>       | Input common mode range                                                                                                                                                                         | Voltage on ACP/ACN                                                                         | 4.5   |      | 24         | V    |

| V(IADP_CLAMP)                 | IADP output clamp voltage                                                                                                                                                                       |                                                                                            | 3.1   | 3.2  | 3.3        | V    |

| I <sub>(IADP)</sub>           | IADP output current                                                                                                                                                                             |                                                                                            |       |      | 1          | mA   |

|                               |                                                                                                                                                                                                 | V <sub>(IADP)</sub> /V <sub>(ACP-ACN</sub> ), ChargeOption0[4]=0, (770/773)                |       | 40   |            |      |

| A <sub>(IADP)</sub>           | Input current sense gain                                                                                                                                                                        | V <sub>(IADP)</sub> /V <sub>(ACP-ACN</sub> ), ChargeOption0[4]=1, (770/773)                |       | 80   |            | V/V  |

|                               |                                                                                                                                                                                                 | V <sub>(ACP-ACN)</sub> = 40.96 mV                                                          | -2%   |      | 2%         |      |

|                               |                                                                                                                                                                                                 | $V_{(ACP-ACN)} = 20.48 \text{ mV}$                                                         | -3%   |      | 4%         |      |

| V(IADP_ACC)                   | Input current monitor accuracy                                                                                                                                                                  | V <sub>(ACP-ACN)</sub> = 10.24 mV                                                          | -6%   |      | 7%         |      |

|                               |                                                                                                                                                                                                 | $V_{(ACP-ACN)} = 5.12 \text{ mV}$                                                          | -10%  |      | 18%        |      |

| C <sub>(IADP_MAX)</sub>       | Maximum output load capacitance                                                                                                                                                                 |                                                                                            |       |      | 100        | pF   |

|                               | ENT AND DISCHARGE CURRENT SENSE AN                                                                                                                                                              | MPLIFIER                                                                                   |       |      |            |      |

| V <sub>(SRP/N OP)</sub>       | Battery common mode range                                                                                                                                                                       | Voltage on SRP/SRN                                                                         | 2.8   |      | 18         | V    |

| V(IBAT CLAMP)                 | IBAT output clamp voltage                                                                                                                                                                       |                                                                                            | 3.1   | 3.2  | 3.3        | V    |

|                               | IBAT output current                                                                                                                                                                             |                                                                                            |       |      | 1          | mA   |

| <u></u>                       | Discharge current sensing gain on IBAT                                                                                                                                                          | V <sub>(IBAT)</sub> /V <sub>(SRN-SRP</sub> ), ChargeOption0[3]=0                           |       | 8    |            |      |

| A <sub>(IBAT_DCHG)</sub>      | pin                                                                                                                                                                                             | V <sub>(IBAT)</sub> /V <sub>(SRN-SRP</sub> ), ChargeOption0[3]=1                           |       | 16   |            | V/V  |

|                               |                                                                                                                                                                                                 | $V_{(SRN-SRP)} = 40.96 \text{ mV}$                                                         | -2%   | -    | 2%         |      |

|                               | Discharge current monitor accuracy on                                                                                                                                                           | V <sub>(SRN-SRP)</sub> = 20.48 mV                                                          | -3%   |      | 3%         |      |

| I(IBAT_DCHG_ACC)              | IBAT pin                                                                                                                                                                                        | $V_{(SRN-SRP)} = 10.24 \text{ mV}$                                                         | -5%   |      | 5%         |      |

|                               |                                                                                                                                                                                                 | $V_{(SRN-SRP)} = 5.12 \text{ mV}$                                                          | -10%  |      | 10%        |      |

|                               | Charge current sensing gain on IBAT pin                                                                                                                                                         | V(IBAT)/V(SRN-SRP)                                                                         | .070  | 20   |            | V/V  |

| A <sub>(IBAT_CHG)</sub>       | Charge carrent sensing gain on 15/17 pin                                                                                                                                                        | V <sub>(IBA1)</sub> V <sub>(SRN-SRP)</sub> = 40.96 mV                                      | -2%   | 20   | 2%         | •/•  |

|                               | Charge current monitor accuracy on IBAT<br>pin (0°C - 85°C)                                                                                                                                     | V <sub>(SRN-SRP)</sub> = 40.50 mV<br>V <sub>(SRN-SRP)</sub> = 20.48 mV                     | -3%   |      | 4%         |      |

| I(IBAT_CHG_ACC)               |                                                                                                                                                                                                 | $\frac{V_{(SRN-SRP)} = 20.46 \text{ mV}}{V_{(SRN-SRP)} = 10.24 \text{ mV}}$                | -5%   |      | 7%         |      |

|                               |                                                                                                                                                                                                 | $\frac{V_{(SRN-SRP)} = 10.24 \text{ mV}}{V_{(SRN-SRP)} = 5.12 \text{ mV}}$                 | -10%  |      | 15%        |      |

| C                             | Maximum output load capacitance                                                                                                                                                                 | V(SRN-SRP) - 3.12 111V                                                                     | -1070 |      | 100        | pF   |

| C(IBAT_MAX)                   | R SENSE AMPLIFIER                                                                                                                                                                               |                                                                                            |       |      | 100        | рі   |

|                               |                                                                                                                                                                                                 | Voltage on ACP/ACN                                                                         | 4.5   |      | 24         | V    |

| V <sub>(ACP/N_OP)</sub>       | Input common mode range                                                                                                                                                                         | Voltage on SRP/SRN                                                                         | 2.8   |      | 18         | V    |

| V <sub>(SRP/N_OP)</sub>       | Battery common mode range                                                                                                                                                                       |                                                                                            | 2.0   |      |            | V    |

| V <sub>(PMON)</sub>           | Power buffer output voltage                                                                                                                                                                     |                                                                                            | 3     | 2.0  | 3.3<br>3.3 | V    |

| V <sub>(PMON_CLAMP)</sub>     | Power buffer clamp voltage                                                                                                                                                                      |                                                                                            | 3     | 3.2  |            | -    |

| (PMON)                        | Power buffer output current                                                                                                                                                                     |                                                                                            |       | 0.05 | 105        | μΑ   |

| A <sub>(PMON)</sub>           | System power sense gain,<br>V <sub>(PMON</sub> )/(V <sub>(ACP-ACN)</sub> x V <sub>(ACN)</sub> + V <sub>(SRN-SRP)</sub> x                                                                        | ChargeOption1[9]=0                                                                         |       | 0.25 |            | µA/V |

| 、,                            | V <sub>(SRP)</sub> )                                                                                                                                                                            | ChargeOption1[9]=1                                                                         |       | 1    |            | µA/V |

| V(PMON ACC)                   | PMON output accuracy                                                                                                                                                                            | Input 19.5 V, 65W, 1 µA/W                                                                  | -5%   |      | 5%         |      |

| • (FMUN_ACC)                  |                                                                                                                                                                                                 | Battery 11 V, 44W, 1 µA/W                                                                  | -6%   |      | 6%         |      |

| REGN REGULAT                  | OR                                                                                                                                                                                              | 1                                                                                          |       |      |            |      |

| V <sub>(REGN_REG)</sub>       | REGN Regulator voltage (0 mA - 40 mA)                                                                                                                                                           | $V_{(VCC)}$ > 10 V, $V_{(ACDET)}$ > 0.6 V (0 - 50 mA load)                                 | 5     | 5.5  | 6          | V    |

| V <sub>(DROPOUT)</sub>        | REGN Voltage in drop out mode                                                                                                                                                                   | $V_{(VCC)} = 5 \text{ V}, \text{ I}_{(LOAD)} = 20 \text{ mA}$                              | 4.4   | 4.6  | 4.7        | V    |

|                               | REGN Current Limit when converter is disabled or in $\rm T_{(SHUT)}$ (no charging)                                                                                                              | $V_{(\text{REGN})}$ = 4 V, $V_{(\text{ACP})}$ > $V_{(\text{UVLO})},$ 0.6 V < ACDET < 2.4 V | 6.5   |      |            | mA   |

| I(REGN_LIM)                   | REGN Current Limit when converter is enabled (charging)                                                                                                                                         | $V_{(REGN)} = 4 V, V_{(ACP)} > V_{(UVLO)}$                                                 | 50    | 65   |            | mA   |

| C <sub>(REGN)</sub>           | REGN Output Capacitor Required for<br>Stability                                                                                                                                                 | $I_{LOAD} = 100 \ \mu A$ to 50 mA                                                          |       | 1    |            | μF   |

| QUIESCENT CUP                 | RRENT                                                                                                                                                                                           |                                                                                            |       |      |            |      |

| I <sub>(BAT_BATFET_OFF)</sub> | Standby mode. System powered by battery. BATFET off (0°C - 85°C).<br>$I_{(SRN)} + I_{(SRN)} + I_{(SRP)} + I_{(PHASE)} + I_{(BTST)} + I_{(ACP)} + I_{(ACN)} + I_{BAT} + I_{(CMSRC)} + I_{(VCC)}$ | $V_{BAT} = 16.8 V$<br>$V_{(VCC)} < V_{(UVLO)}$ , ACDET < 0.6 V                             |       | 20   | 27         | μΑ   |

# **Electrical Characteristics (continued)**

$4.5V \le V_{(VCC)} \le 24V, -20^{\circ}C \le T_{J} \le 125^{\circ}C$ , typical values are at  $T_{A} = 25^{\circ}C$ , with respect to GND (unless otherwise noted)

|                              | PARAMETER                                                                                                                                                                             | TEST CONDITION                                                                                                                                                                                                      | MIN  | TYP  | MAX  | UNIT |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|