CSD88584Q5DC

ZHCSG78E - MAY 2017 - REVISED JUNE 2024

## CSD88584Q5DC 40V 半桥 NexFET™ 电源块

### 1 特性

• 半桥电源块

**TEXAS**

INSTRUMENTS

- 高密度 SON 5mm × 6mm 封装

- 低 R<sub>DS(ON)</sub>,可更大限度地降低传导损耗

在 35A 下, P<sub>Loss</sub> 为 2.4W

- DualCool<sup>™</sup> 散热增强型封装

- 超低电感封装

- 符合 RoHS

- 无卤素

- 无铅端子镀层

### 2 应用

- 用于无刷直流电机控制的三相桥

- 具有多达 8 节串联电池的电动工具

- 其他半桥和全桥拓扑

Copyright © 2017, Texas Instruments Incorporated

## 3 说明

CSD88584Q5DC 40V 电源块是一款针对手持设备、无 绳园艺工具和电动工具等高电流电机控制应用进行了优 化的设计。该器件利用 TI 获得专利的堆叠裸片技术来 最大限度地减小寄生电感,同时采用节省空间的热增强 型 DualCool<sup>™</sup> 5mm × 6mm 封装,提供完整的半桥。 利用外露的金属顶部,该电源块器件允许简单散热应用 通过封装顶部散发 PCB 热量,从而在许多电机控制应 用所要求的较高电流下,实现出色的热性能。

| 66   | <i>h</i> L. | ~~ | - <b>Ľ</b> |

|------|-------------|----|------------|

| 器    | л           | 1= |            |

| 1117 |             |    | 10.5       |

|      |             |    |            |

| 器件            | 数量   | 介质      | 封装                      | 运输  |

|---------------|------|---------|-------------------------|-----|

| CSD88584Q5DC  | 2500 | 13 英寸卷带 | SON                     | 卷带包 |

| CSD88584Q5DCT | 250  | 7 英寸卷带  | 5.00mm × 6.00mm<br>塑料封装 | 装   |

## **Table of Contents**

| 1 | 特性                                              | 1              |

|---|-------------------------------------------------|----------------|

| 2 | 应用                                              | 1              |

| 3 | 说明                                              | 1              |

| 4 | Specifications                                  | 3              |

|   | 4.1 Absolute Maximum Ratings                    | 3              |

|   | 4.2 Recommended Operating Conditions            |                |

|   | 4.3 Power Block Performance                     | 3              |

|   | 4.4 Thermal Information                         | 4              |

|   | 4.5 Electrical Characteristics                  | 4              |

|   | 4.6 Typical Power Block Device Characteristics  | <mark>6</mark> |

|   | 4.7 Typical Power Block MOSFET Characteristics  |                |

| 5 | Application and Implementation                  | 9              |

|   | 5.1 Application Information                     | 9              |

|   | 5.2 Brushless DC Motor With Trapezoidal Control |                |

|   | 5.3 Power Loss Curves                           | 11             |

|   | 5.4 Safe Operating Area (SOA) Curve             |                |

|   | 5.5 Normalized Power Loss Curves                | 12             |

|   |                                                 |                |

| 5.6 Design Example – Regulate Current to          |    |

|---------------------------------------------------|----|

| Maintain Safe Operation                           | 12 |

| 5.7 Design Example - Regulate Board and Case      |    |

| Temperature to Maintain Safe Operation            | 13 |

| 6 Layout                                          | 15 |

| 6.1 Layout Guidelines                             | 15 |

| 6.2 Layout Example                                | 17 |

| 7 Device and Documentation Support                | 18 |

| 7.1 接收文档更新通知                                      | 18 |

| 7.2 支持资源                                          | 18 |

| 7.3 Trademarks                                    | 18 |

| 7.4 静电放电警告                                        | 18 |

| 7.5 术语表                                           |    |

| 8 Revision History                                |    |

| 9 Mechanical, Packaging, and Orderable Informatio |    |

## **4** Specifications

### 4.1 Absolute Maximum Ratings

#### $T_{.1} = 25^{\circ}C$ (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                                             | CONDITIONS                                      | MIN   | MAX | UNIT |

|-------------------------------------------------------|-------------------------------------------------|-------|-----|------|

|                                                       | V <sub>IN</sub> to P <sub>GND</sub>             | - 0.8 | 40  |      |

| Voltage                                               | V <sub>SW</sub> to P <sub>GND</sub>             | - 0.3 | 40  | v    |

| Voltage                                               | GH to SH                                        | - 20  | 20  |      |

|                                                       | GL to P <sub>GND</sub>                          | - 20  | 20  |      |

| Pulsed current rating, I <sub>DM</sub> <sup>(2)</sup> |                                                 | 400   | A   |      |

| Power dissipation, P <sub>D</sub>                     |                                                 | 12    | W   |      |

| Avalanche energy, E <sub>AS</sub>                     | High-side FET, I <sub>D</sub> = 103A, L = 0.1mH |       | 525 | – mJ |

| Avalariche energy, LAS                                | Low-side FET, I <sub>D</sub> = 103A, L = 0.1mH  |       | 525 |      |

| Operating junction temperature, T <sub>J</sub>        |                                                 | - 55  | 150 | °C   |

| Storage temperature, T <sub>stg</sub>                 |                                                 | - 55  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Single FET conduction, max R  $_{\theta$  JC = 1.1°C/W, pulse duration  $\leq$  100  $\mu$  s, single pulse.

### 4.2 Recommended Operating Conditions

$T_J = 25^{\circ}C$  (unless otherwise noted)

|                  | PARAMETER                           | CONDITIONS                     | MIN | MAX | UNIT |

|------------------|-------------------------------------|--------------------------------|-----|-----|------|

| V <sub>GS</sub>  | Gate drive voltage                  |                                | 4.5 | 16  | V    |

| V <sub>IN</sub>  | Input supply voltage <sup>(1)</sup> |                                |     | 36  | V    |

| f <sub>sw</sub>  | Switching frequency                 | C <sub>BST</sub> = 0.1µF (min) | 5   | 50  | kHz  |

| I <sub>OUT</sub> | RMS motor winding current           |                                |     | 50  | А    |

| TJ               | Operating temperature               |                                |     | 125 | °C   |

(1) Up to 32V input use one capacitor per phase, MLCC 10nF, 100V, X7S, 0402, PN: C1005X7S2A103K050BB from V<sub>IN</sub> to GND return. Between 32V to 36V input operation, add RC switch-node snubber as described in the #6.1.1 section of this data sheet.

### 4.3 Power Block Performance

T<sub>J</sub> = 25°C (unless otherwise noted)

|                   | PARAMETER                 | CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>LOSS</sub> | Power loss <sup>(1)</sup> | $V_{IN} = 24V, V_{GS} = 10V,$<br>$I_{OUT} = 35A, f_{SW} = 20kHz,$<br>$T_J = 25^{\circ}C, duty cycle = 50%,$<br>$L = 480\mu H$  |     | 2.4 |     | W    |

| P <sub>LOSS</sub> | Power loss                | $V_{IN} = 24V, V_{GS} = 10V,$<br>$I_{OUT} = 35A, f_{SW} = 20kHz,$<br>$T_J = 125^{\circ}C, duty cycle = 50%,$<br>$L = 480\mu H$ |     | 3.5 |     | W    |

(1) Measurement made with eight 10μF, 50V, ±10% X5R (TDK C3225X5R1H106K250AB or equivalent) ceramic capacitors placed across V<sub>IN</sub> to P<sub>GND</sub> pins and using UCC27210DDAR 100V, 4A driver IC.

#### 4.4 Thermal Information

T<sub>J</sub> = 25°C (unless otherwise stated)

|                   | THERMAL METRIC                                                           |  |  | MAX | UNIT  |

|-------------------|--------------------------------------------------------------------------|--|--|-----|-------|

| P                 | Junction-to-ambient thermal resistance (min Cu) <sup>(2)</sup>           |  |  | 125 | °C/W  |

| R <sub>0JA</sub>  | Junction-to-ambient thermal resistance (max Cu) <sup>(2) (1)</sup>       |  |  | 50  | C/ VV |

| Б                 | Junction-to-case thermal resistance (top of package) <sup>(2)</sup>      |  |  | 2.1 | °C/W  |

| R <sub>θ JC</sub> | Junction-to-case thermal resistance (V <sub>IN</sub> pin) <sup>(2)</sup> |  |  | 1.1 | C/vv  |

(1) Device mounted on FR4 material with 1in<sup>2</sup> (6.45cm<sup>2</sup>) Cu.

(2) R<sub>θ JC</sub> is determined with the device mounted on a 1in<sup>2</sup> (6.45cm<sup>2</sup>), 2oz (0.071mm) thick Cu pad on a 1.5in × 1.5in (3.81cm × 3.81cm), 0.06in (1.52mm) thick FR4 board. R<sub>θ JC</sub> is specified by design while R<sub>θ JA</sub> is determined by the user's board design.

#### **4.5 Electrical Characteristics**

$T_J = 25^{\circ}C$  (unless otherwise stated)

|                     | PARAMETER                        | TEST CONDITIONS                                             | MIN | TYP  | MAX   | UNIT |

|---------------------|----------------------------------|-------------------------------------------------------------|-----|------|-------|------|

| STATIC CH           | IARACTERISTICS                   |                                                             |     |      |       |      |

| BV <sub>DSS</sub>   | Drain-to-source voltage          | V <sub>GS</sub> = 0V, I <sub>DS</sub> = 250µA               | 40  |      |       | V    |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 32V                 |     |      | 1     | μA   |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | V <sub>DS</sub> = 0V, V <sub>GS</sub> = 20V                 |     |      | 100   | nA   |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>DS</sub> = 250µA | 1.2 | 1.7  | 2.3   | V    |

| P                   | Drain to acurac on registeres    | V <sub>GS</sub> = 4.5V, I <sub>DS</sub> = 30A               |     | 1.0  | 1.5   |      |

| R <sub>DS(on)</sub> | Drain-to-source on resistance    | V <sub>GS</sub> = 10V, I <sub>DS</sub> = 30A                |     | 0.68 | 0.95  | mΩ   |

| g <sub>fs</sub>     | Transconductance                 | V <sub>DS</sub> = 4V, I <sub>DS</sub> = 30A                 |     | 149  |       | S    |

| DYNAMIC             | CHARACTERISTICS                  |                                                             | 1   |      |       |      |

| C <sub>ISS</sub>    | Input capacitance                |                                                             |     | 9540 | 12400 | pF   |

| C <sub>OSS</sub>    | Output capacitance               | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 20V,<br>f = 1MHz    |     | 957  | 1240  | pF   |

| C <sub>RSS</sub>    | Reverse transfer capacitance     |                                                             |     | 474  | 616   | pF   |

| R <sub>G</sub>      | Series gate resistance           |                                                             |     | 1.0  | 2.0   | Ω    |

| Q <sub>g</sub>      | Gate charge total (4.5 V)        |                                                             |     | 68   | 88    | nC   |

| Qg                  | Gate charge total (10 V)         |                                                             |     | 137  | 178   | nC   |

| Q <sub>gd</sub>     | Gate charge gate-to-drain        | V <sub>DS</sub> = 20V,<br>I <sub>DS</sub> = 30A             |     | 26   |       | nC   |

| Q <sub>gs</sub>     | Gate charge gate-to-source       |                                                             |     | 24   |       | nC   |

| Q <sub>g(th)</sub>  | Gate charge at V <sub>th</sub>   |                                                             |     | 16   |       | nC   |

| Q <sub>OSS</sub>    | Output charge                    | V <sub>DS</sub> = 20V, V <sub>GS</sub> = 0V                 |     | 42   |       | nC   |

| t <sub>d(on)</sub>  | Turnon delay time                |                                                             |     | 11   |       | ns   |

| t <sub>r</sub>      | Rise time                        | V <sub>DS</sub> = 20V, V <sub>GS</sub> = 10V,               |     | 24   |       | ns   |

| t <sub>d(off)</sub> | Turnoff delay time               | $I_{DS} = 30A, R_G = 0\Omega$                               |     | 53   |       | ns   |

| t <sub>f</sub>      | Fall time                        |                                                             |     | 17   |       | ns   |

| DIODE CH            | ARACTERISTICS                    |                                                             |     |      | I     |      |

| V <sub>SD</sub>     | Diode forward voltage            | I <sub>DS</sub> = 30A, V <sub>GS</sub> = 0V                 |     | 0.75 | 1.0   | V    |

| Q <sub>rr</sub>     | Reverse recovery charge          | V <sub>DS</sub> = 20V, I <sub>F</sub> = 30A,                |     | 34   |       | nC   |

| t <sub>rr</sub>     | Reverse recovery time            | di/dt = 300A/µs                                             |     | 24   |       | ns   |

|                     |                                  |                                                             |     |      |       |      |

Max R  $_{\theta \ JA}$  = 50°C/W when mounted on 1in² (6.45cm²) of 2oz (0.071mm) thick Cu.

Max R  $_{\theta$  JA = 125°C/W when mounted on minimum pad area of 2oz (0.071mm) thick Cu.

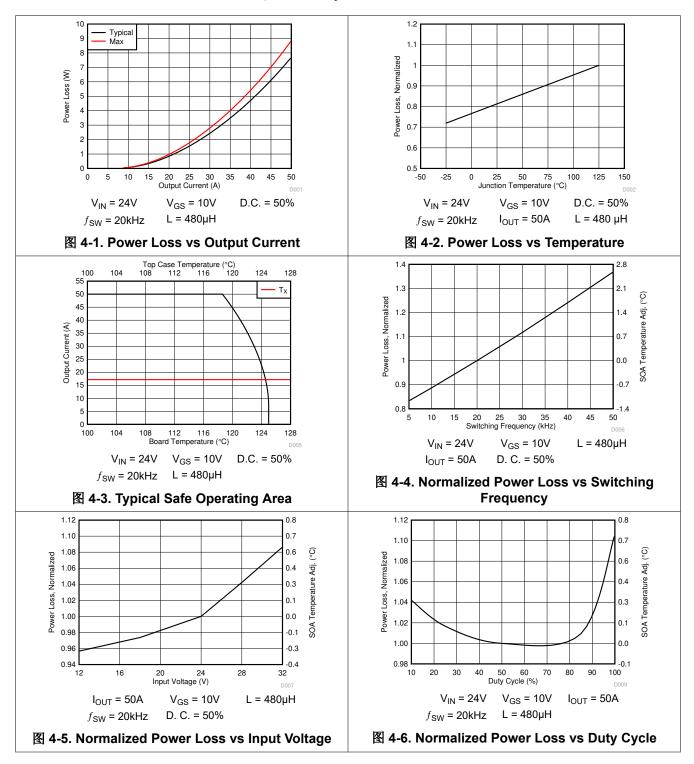

### 4.6 Typical Power Block Device Characteristics

The typical power block system characteristic curves ( $\mathbb{X}$  4-1 through  $\mathbb{X}$  4-6) are based on measurements made on a PCB design with dimensions of 4in (W) × 3.5in (L) × 0.062in (H) and 6 copper layers of 2oz copper thickness. See # 5 section for detailed explanation. T<sub>J</sub> = 125°C, unless stated otherwise.

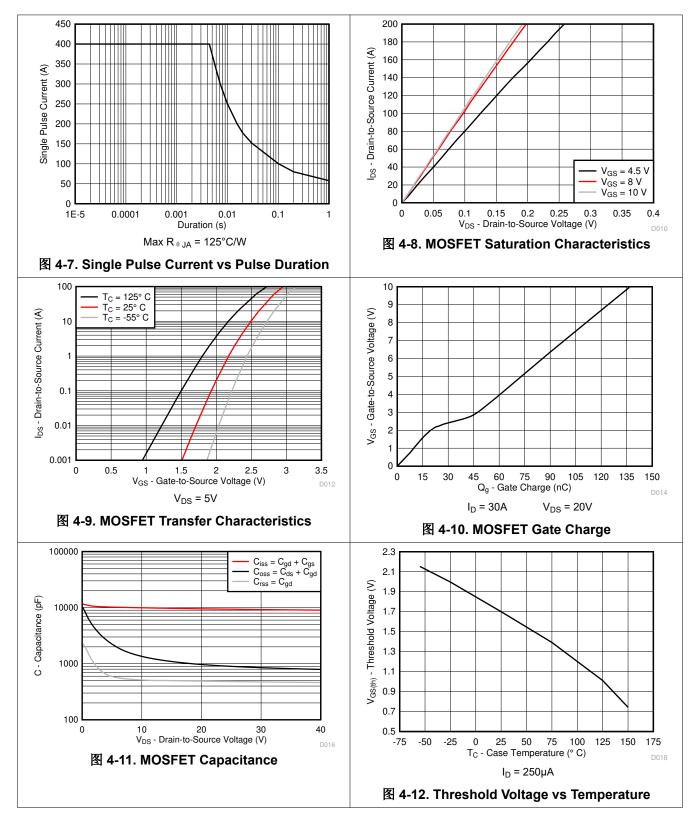

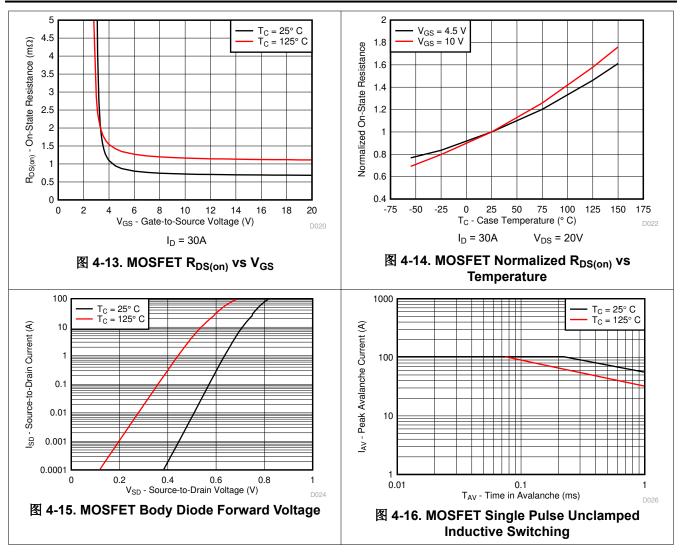

### 4.7 Typical Power Block MOSFET Characteristics

$T_J$  = 25°C, unless stated otherwise.

CSD88584Q5DC

ZHCSG78E - MAY 2017 - REVISED JUNE 2024

## **5** Application and Implementation

备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

#### **5.1 Application Information**

Historically, battery powered tools have favored brushed DC configurations to spin their primary motors, but more recently, the advantages offered by brushless DC operation (BLDC) operation have brought about the advent of popular designs that favor the latter. Those advantages include, but are not limited to higher efficiency and therefore longer battery life, superior reliability, greater peak torque capability, and smooth operation over a wider range of speeds. However, BLDC designs put increased demand for higher power density and current handling capabilities on the power stage responsible for driving the motor.

The CSD88584Q5DC is part of TI's power block product family and is a highly optimized product designed explicitly for the purpose driving higher current DC motors in power and gardening tools. It incorporates TI's latest generation silicon which has been optimized for low resistance to minimize conduction losses and offer excellent thermal performance. The power block utilizes TI's stacked die technology to offer one complete half bridge vertically integrated into a single 5mm × 6mm package with a DualCool exposed metal case. This feature allows the designer to apply a heatsink to the top of the package and pull heat away from the PCB, thus maximizing the power density while reducing the power stage footprint by up to 50%.

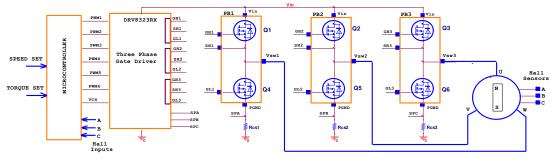

#### 5.2 Brushless DC Motor With Trapezoidal Control

The trapezoidal commutation control is simple and has fewer switching losses compared to sinusoidal control.

Copyright © 2017, Texas Instruments Incorporated

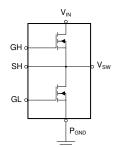

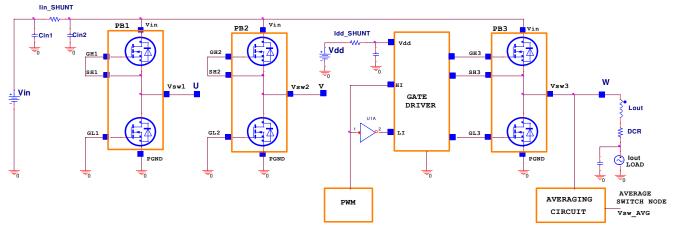

#### 图 5-1. Functional Block Diagram

The block diagram shown in 🕅 5-1 offers a simple instruction of what is required to drive a BLDC motor: one microcontroller, one three-phase driver IC, 3 power blocks (historically 6 power MOSFETs) and 3 Hall effect sensors. The microcontroller responsible for block commutation must always know the rotor orientation or its position relative to the stator coils. This is easy achieved with a brushed DC motor due to the fixed geometry and position of the rotor windings, shaft and commutator.

A three-phase BLDC motor requires three Hall effect sensors or a rotary encoder to detect the rotor position in relation to stator armature windings. Combining these three Hall effect sensors output signals, the microcontroller can determine the proper commutation sequence. The three Hall sensors named A, B, and C are mounted on the stator core at 120° intervals and the stator phase windings are implemented in a star configuration. For every 60° of motor rotation, one Hall sensor changes its state. Based on the Hall sensor outputs code, at the end of each block commutation interval the ampere conductors are commutated to the next position. There are 6 steps needed to complete a full electrical cycle. The number of block commutation cycles to complete a full mechanical rotation is determined by the number of rotor pole pairs.

CSD88584Q5DC ZHCSG78E - MAY 2017 - REVISED JUNE 2024

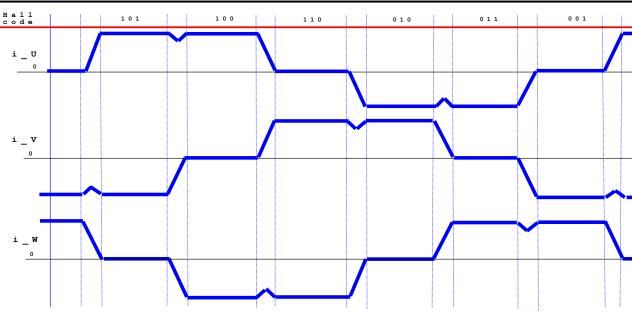

图 5-2. Winding Current Waveforms on a BLDC Motor

图 5-2 above shows the three phase motor winding currents i\_U, i\_V, and i\_W when running at 100% duty cycle.

Trapezoidal commutation control offers the following advantages:

- Only two windings in series carry the phase winding current at any time while the third winding is open.

- Only one current sensor is necessary for all 3 windings U, V, and W.

- The position of the current sensor allows the use of low-cost shunt resistors.

However, trapezoidal commutation control has the disadvantage of commutation torque ripple. The current sense on a three-phase inverter can be configured to use a single-shunt or three different sense resistors. For cost sensitive applications targeting sensorless control, the three Hall effect sensors can be replaced with BEMF voltage feedback dividers.

To obtain faster motor rotations and higher revolutions per minute (RPM), shorter periods and higher  $V_{IN}$  voltage are necessary. Contrarily, to reduce the rotational speed of the motor, it is necessary to lower the RMS voltage applied across stator windings. This can easily be easily achieved by modulating the duty cycle, while maintain a constant switching frequency. Frequency for the three-phase inverter chosen is usually low between 10kHz to 50kHz to reduce winding losses and to avoid audible noise.

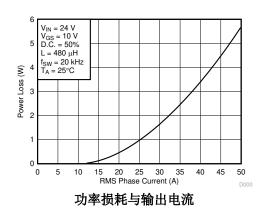

#### 5.3 Power Loss Curves

CSD88584Q5DC was designed to operate up to 7-cell Li-Ion battery voltage applications ranging from 18V to 32V, typical 24V. For 8s, input voltages between 32V to 36V, RC snubbers are required for each switch-node U, V, and W. To reduce ringing, refer to the # 6.1.1 section. In an effort to simplify the design process, Texas Instruments has provided measured power loss performance curves over a variety of typical conditions.

方程式 1 is used to generate the power loss curve:

Power loss (W) =

$$(V_{IN} \times I_{IN SHUNT}) + (V_{DD} \times I_{DD SHUNT}) - (V_{SW AVG} \times I_{OUT})$$

(1)

The power loss measurements were made on the circuit shown in ⊠ 5-3, power block devices for legs U and V, PB1 and PB2 were disabled by shorting the CSD88584Q5DC high-side and low-side FETs gate-to-source terminals. Current shunt lin\_shunt provides Input current and Idd\_SHUNT provides driver supply current measurements. The winding current is measured from the DC load. An averaging circuit provides switch node W equivalent RMS voltage.

Copyright © 2017, Texas Instruments Incorporated

#### 图 5-3. Power Loss Test Circuit

The RMS current on the CSD88584Q5DC device depends on the motor winding current. For trapezoidal control, the MOSFET RMS current is calculated using 方程式 2.

$$I_{RMS} = I_{OUT} \times \sqrt{2}$$

(2)

Taking into consideration system tolerances with the current measurement scheme, the inverter design needs to withstand a 20% overload current.

| Winding RMS Current (A) | CSD88584Q5DC I <sub>RMS</sub> (A) | Overload 120% × I <sub>RMS</sub> (A) |  |  |  |  |

|-------------------------|-----------------------------------|--------------------------------------|--|--|--|--|

| 30                      | 42                                | 51                                   |  |  |  |  |

| 40                      | 56                                | 68                                   |  |  |  |  |

| 50                      | 70                                | 85                                   |  |  |  |  |

Copyright © 2024 Texas Instruments Incorporated

#### 5.4 Safe Operating Area (SOA) Curve

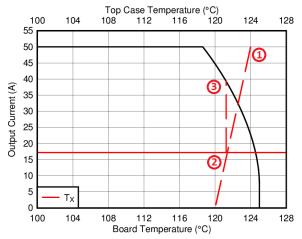

The SOA curve in 🕅 4-3 provide guidance on the temperature boundaries within an operating system by incorporating the thermal resistance and system power loss. This curve outlines the board and case temperatures required for a given load current. The area under the curve dictates the safe operating area. This curve is based on measurements made on a PCB design with dimensions of 4in (W) × 3.5in (L) × 0.062in (H) and 6 copper layers of 2oz copper thickness.

#### 5.5 Normalized Power Loss Curves

The normalized curves in the CSD88584Q5DC data sheet provide guidance on the power loss and SOA adjustments based on application specific needs. These curves show how the power loss and SOA temperature boundaries will adjust for different operation conditions. The primary Y-axis is the normalized change in power loss while the secondary Y-axis is the change in system temperature required in order to comply with the SOA curve. The change in power loss is a multiplier for the typical power loss. The change in SOA temperature is subtracted from the SOA curve.

#### 5.6 Design Example - Regulate Current to Maintain Safe Operation

If the case and board temperature of the power block are known, the SOA can be used to determine the maximum allowed current that will maintain operation within the safe operating area of the device. The following procedure outlines how to determine the RMS current limit while maintaining operation within the confines of the SOA, assuming the temperatures of the top of the package and PCB directly underneath the part are known.

- 1. Start at the maximum current of the device on the Y-axis and draw a line from this point at the known top case temperature to the known PCB temperature.

- 2. Observe where this point intersects the  $T_X$  line.

- 3. At this intersection with the T<sub>X</sub> line, draw vertical line until you hit the SOA current limit. This intercept is the maximum allowed current at the corresponding power block PCB and case temperatures.

In the example below, we show how to achieve this for the temperatures  $T_C = 124^{\circ}C$  and  $T_B = 120^{\circ}C$ . First we draw from 50 A on the Y-axis at 124°C to 120°C on the X-axis. Then, we draw a line up from where this line crosses the  $T_X$  line to see that this line intercepts the SOA at 39A. Thus we can assume if we are measuring a PCB temperature of 124°C, and a top case temperature of 120°C, the power block can handle 39A RMS, at the normalized conditions. At conditions that differ from those in  $\mathbb{R}$  4-1, the user may be required to make an SOA temperature adjustment on the  $T_X$  line, as shown in the next section.

图 5-4. Regulating Current to Maintain Safe Operation

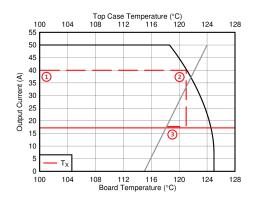

#### 5.7 Design Example - Regulate Board and Case Temperature to Maintain Safe Operation

In the previous example we showed how given the PCB and case temperature, the current of the power block could be limited to ensure operation within the SOA. Conversely, if the current and other application conditions are known, one can determine from the SOA what board or case temperature the user will need to limit their design to. The user can estimate product loss and SOA boundaries by arithmetic means (see # 5.7.1 section). Though the power loss and SOA curves in this data sheet are taken for a specific set of test conditions, the following procedure outlines the steps the user should take to predict product performance for any set of system conditions.

#### 5.7.1 Operating Conditions

- Winding output current (I<sub>OUT</sub>) = 40A

- Input voltage (V<sub>IN</sub>) = 32V

- Switching frequency (F<sub>SW</sub>) = 40kHz

- Duty cycle (D.C.) = 95%

#### 5.7.2 Calculating Power Loss

- Power loss at 40A  $\approx$  4.7W ( $\boxtimes$  4-1)

- Normalized power loss for switching frequency  $\approx$  1.24 ( $\boxtimes$  4-4)

- Normalized power loss for input voltage  $\approx$  1.09 ( $\boxtimes$  4-5)

- Normalized power loss for duty cycle  $\approx$  1.06 ( $\boxtimes$  4-6)

- Final calculated power loss = 4.7W × 1.24 × 1.09 × 1.06  $\approx$  6.7W

#### 5.7.3 Calculating SOA Adjustments

- SOA adjustment for switching frequency  $\approx$  1.7°C ( $\boxtimes$  4-4)

- SOA adjustment for input voltage  $\approx$  0.6°C ( $\boxtimes$  4-5)

- SOA adjustment for duty cycle  $\approx$  0.4°C ( $\boxtimes$  4-6)

- Final calculated SOA adjustment = 1.7 + 0.6 + 0.4  $\approx$  2.7°C

In the # 5.6 section above, the estimated power loss of the CSD88584Q5DC would increase to 6.7W. In addition, the maximum allowable board temperature would have to increase by 2.7°C. In 🖄 5-5, the SOA graph was adjusted accordingly.

- 1. Start by drawing a horizontal line from the application current (40A) to the SOA curve.

- 2. Draw a vertical line from the SOA curve intercept down to the  $T_X$  line.

- 3. Adjust the intersection point by subtracting the temperature adjustment value.

In this design example, the SOA board/ambient temperature adjustment yields a decrease of allowed junction temperature of 2.7°C from 121.0°C to 118.3°C. Now it is known that the intersection of the case and PCB temperatures on the  $T_X$  line must stay below this point. For instance, if the power block case is observed operating at 124°C, the PCB temperature must in turn be kept under 115°C to maintain this crossover point.

图 5-5. Regulate Temperature to Maintain Safe Operation

## 6 Layout

The two key system-level parameters that can be optimized with proper PCB design are electrical and thermal performance. A proper PCB layout will yield maximum performance in both areas. Below are some tips for how to address each.

#### 6.1 Layout Guidelines

#### 6.1.1 Electrical Performance

The CSD88584Q5DC power block has the ability to switch at voltage rates greater than 1kV/µs. Special care must be then taken with the PCB layout design and placement of the input capacitors; high-current, high dl/dT switching path; current shunt resistors; and GND return planes. As with any high-power inverter operated in hard switching mode, there will be voltage ringing present on the switch nodes U, V, and W. Switch-node ringing appears mainly at the HS FET turnon commutation with positive winding current direction. The U, V, and W phase connections to the BLDC motor can be usually excluded from the ringing behavior since they are subjected to high-peak currents but low dl/dT slew-rates. However, a compact PCB design with short and low-parasitic loop inductances is critical to achieve low ringing and compliance with EMI specifications.

For safe and reliable operation of the three-phase inverter, motor phase currents have to be accurately monitored and reported to the system microcontroller. One current sensor needs to be connected on each motor phase winding U, V, and W. This sensing method is best for current sensing as it provides good accuracy over a wide range of duty cycles, motor torque, and winding currents. Using current sensors is recommended because it is less intrusive to the  $V_{IN}$  and GND connections.

Copyright © 2017, Texas Instruments Incorporated

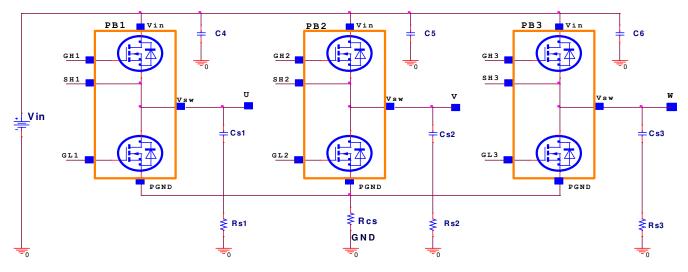

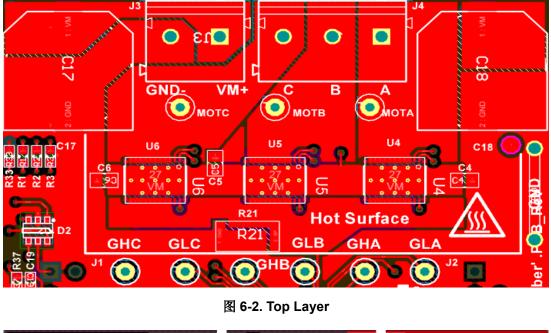

#### 图 6-1. Recommended Ringing Reduction Components

However, for cost sensitive applications, current sensors are generally replaced with current sense resistors.

- For designs using the 60V three-phase smart gate driver DRV8320SRHBR, current sense resistor R<sub>CS</sub> can be placed between common source terminals for all 3 power block devices CSD88584Q5DC to P<sub>GND</sub> and measured using an external current sense amplifier as depicted in 图 6-1 above.

- For designs using the 60V three-phase gate driver DRV8323RSRGZT, three current sense resistors R<sub>CS1</sub>, R<sub>CS2</sub> and R<sub>CS3</sub> can be used between each CSD88584Q5DC source terminal to GND and measured by the included DRV8323 current sense amplifiers. The three-phase driver IC should be placed as close as possible to the power block gate GL and GH terminals.

Breaking the high-current flow path from the source terminals of the power block to GND by introducing the  $R_{CS}$  current shunt resistors introduces parasitic PCB inductance. In the event the switch node waveforms exhibits peak ringing that reaches undesirable levels, the ringing can be reduced by using the following ringing reduction components:

- The use of a high-side gate resistor in series with the GH pin is one effective way to reduce peak ringing. The recommended HS FET gate resistor value will range between 4.7Ω to 10Ω depending on the driver IC output characteristics used in conjunction with the power block device. The low-side FET gate pin GL should connect directly to the driver IC output to avoid any parasitic cdV/dT turnon effect.

- Low inductance MLCC caps C4, C5, and C6 can be used across each power block device from V<sub>IN</sub> to the source terminal P<sub>GND</sub>. MLCC 10nF, 100V, ±10%, X7S, 0402, PN: C1005X7S2A103K050BB are recommended.

- Ringing can be reduced via the implementation of RC snubbers from each switch node U, V, and W to GND. Recommended snubber component values are as follows:

- Snubber resistors Rs1, Rs2, Rs3: 2.21 <sup>Ω</sup>, 1%, 0.125W, 0805, PN: CRCW08052R21FKEA

- Snubber caps Cs1, Cs2, and Cs3: MLCC 4.7nF, 100V, X7S, 0402, PN: C1005X7S2A472M050BB

With a switching frequency of 20kHz on the three-phase inverter, the power dissipation on the RC snubber resistor is 80mW per channel. As a result, 0805 package size for resistors Rs1, Rs2, and Rs3 is adequate.

#### 6.1.2 Thermal Considerations

The CSD88584Q5DC power block device has the ability to utilize the PCB copper planes as the primary thermal path. As such, the use of thermal vias included in the footprint is an effective way to pull away heat from the device and into the system board. Concerns regarding solder voids and manufacturability issues can be addressed through the use of three basic tactics to minimize the amount of solder attach that will wick down the via barrel:

- Intentionally space out the vias from one another to avoid a cluster of holes in a given area.

- Use the smallest drill size allowed by the design. The example in 🗏 6-2 uses vias with a 10mil drill hole and a 16mil solder pad.

- Tent the opposite side of the via with solder-mask. Ultimately the number and drill size of the thermal vias should align with the end user's PCB design rules and manufacturing capabilities.

To take advantage of the DualCool thermally enhanced package, an external heatsink can be applied on top of the power block devices. For low EMI, the heatsink is usually connected to GND through the mounting screws to the PCB. Gap pad insulators with good thermal conductivity should be used between the top of the package and the heatsink. The Bergquist Sil-Pad 980 is recommended which provides excellent thermal impedance of 1.07°C/W at 50psi.

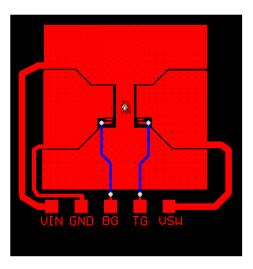

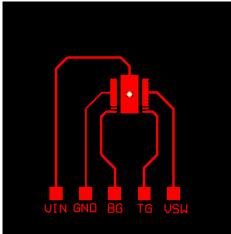

### 6.2 Layout Example

.14 <u>VM+</u> GND С в TP5 TP6 TP4 мотс мотв мота U4 U5 C18 C6 C4 C5 GND Hot Surface Rev GLB GHA GHC GLC G РСВ TF 9 тга TDG

图 6-3. Bottom Layer

The placement of the input capacitors C4, C5, and C6 relative to V<sub>IN</sub> and P<sub>GND</sub> pins of CSD88584Q5DC device should have the highest priority during the component placement routine. It is critical to minimize the VIN to GND parasitic loop inductance. A shunt resistor R21 is used between all three U4, U5, and U6 power block source terminals to the input supply GND return pin.

Input RMS current filtering is achieved via two bulk caps C17 and C18. Based on the RMS current ratings, the recommended part number for input bulk is CAP AL, 330µF, 63V, ±20%, PN: EMVA630ADA331MKG5S.

### 7 Device and Documentation Support

#### 7.1 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*通知*进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 7.2 支持资源

TI E2E<sup>™</sup> 中文支持论坛是工程师的重要参考资料,可直接从专家处获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题,获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的使用条款。

#### 7.3 Trademarks

NexFET<sup>™</sup> and DualCool<sup>™</sup> are trademarks of TI. TI E2E<sup>™</sup> is a trademark of Texas Instruments. 所有商标均为其各自所有者的财产。

#### 7.4 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 7.5 术语表

TI术语表 本术语表列出并解释了术语、首字母缩略词和定义。

## **8 Revision History**

| С | hanges from Revision D (December 2018) to Revision E (June 2024) | Page |

|---|------------------------------------------------------------------|------|

| • | 通篇更新了表格、图和交叉参考的编号格式                                              | 1    |

|   | 向"顶视图"引脚排列图中添加了 PGND                                             |      |

| С | Changes from Revision C (January 2018) to Revision D (December 2018) |    |  |  |  |  |  |

|---|----------------------------------------------------------------------|----|--|--|--|--|--|

| • | Updated current sense resistor description in applications section   | 15 |  |  |  |  |  |

| С | hanges from Revision B (September 2017) to Revision C (January 2018)                                                    | Page |

|---|-------------------------------------------------------------------------------------------------------------------------|------|

| • | 将功率损耗与输出电流 <i>功率损耗与输出电流</i> 图表上的 V <sub>DD</sub> = 10V 改为 V <sub>GS</sub> = 10V                                         | 1    |

| • | Changed V <sub>DD</sub> to V <sub>GS</sub> in sections Recommended Operating Conditions, Block Performance, and Typical |      |

|   | Power Block Device Characteristics                                                                                      | 3    |

| • | Changed I <sub>DSS</sub> test condition from 20V to 32V in the <i>Electrical Characteristics</i> table                  | 4    |

| Changes from Revision A (May 2017) to Revision B (September 2017) | Page |

|-------------------------------------------------------------------|------|

| Updated 图 4-3 to extend to 50A                                    | 6    |

| • | 更新了 <i>典型电路</i> 图中的栅极驱动器器件型号1 |  |

|---|-------------------------------|--|

|   |                               |  |

Page

### 9 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

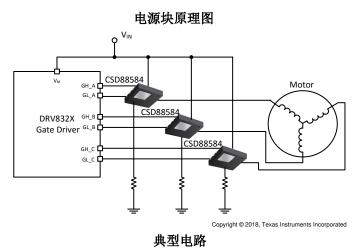

| 表 9-1. Pin Configuration Table |                  |                       |  |  |  |  |  |  |  |

|--------------------------------|------------------|-----------------------|--|--|--|--|--|--|--|

| POSITION                       | PIN NAME         | DESCRIPTION           |  |  |  |  |  |  |  |

| 1                              | GH               | High Side Gate        |  |  |  |  |  |  |  |

| 2                              | SH               | High Side Gate Return |  |  |  |  |  |  |  |

| 3-11                           | V <sub>SW</sub>  | Switch Node           |  |  |  |  |  |  |  |

| 12-20                          | P <sub>GND</sub> | Power Ground          |  |  |  |  |  |  |  |

| 21                             | NC               | No Connect            |  |  |  |  |  |  |  |

| 22                             | GL               | Low Side Gate         |  |  |  |  |  |  |  |

| 23-26                          | NC               | No Connect            |  |  |  |  |  |  |  |

| 27                             | V <sub>IN</sub>  | Input Voltage         |  |  |  |  |  |  |  |

#### = 0 4 D' 0 0 0 \_ . .

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)        | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|------------------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                        | (6)                           |                      |              |                         |         |

| CSD88584Q5DC     | ACTIVE        | VSON-CLIP    | DMM                | 22   | 2500           | RoHS-Exempt<br>& Green | SN                            | Level-1-260C-UNLIM   | -55 to 150   | 88584                   | Samples |

| CSD88584Q5DCT    | ACTIVE        | VSON-CLIP    | DMM                | 22   | 250            | RoHS-Exempt<br>& Green | SN                            | Level-1-260C-UNLIM   | -55 to 150   | 88584                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

11-Jul-2024

www.ti.com

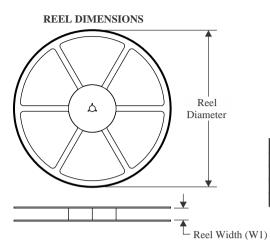

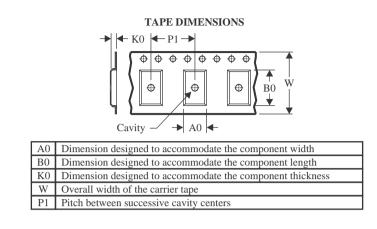

### TAPE AND REEL INFORMATION

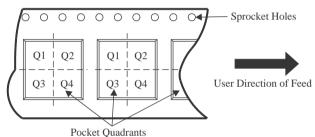

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal | h               |                    |    |      | 0                        |                          |            |            |            |            |           | t.               |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| CSD88584Q5DC                | VSON-<br>CLIP   | DMM                | 22 | 2500 | 330.0                    | 15.4                     | 6.3        | 5.3        | 1.2        | 8.0        | 12.0      | Q2               |

| CSD88584Q5DCT               | VSON-<br>CLIP   | DMM                | 22 | 250  | 178.0                    | 12.4                     | 6.3        | 5.3        | 1.2        | 8.0        | 12.0      | Q2               |

www.ti.com

## PACKAGE MATERIALS INFORMATION

25-Sep-2024

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CSD88584Q5DC  | VSON-CLIP    | DMM             | 22   | 2500 | 333.2       | 345.9      | 28.6        |

| CSD88584Q5DCT | VSON-CLIP    | DMM             | 22   | 250  | 180.0       | 180.0      | 79.0        |

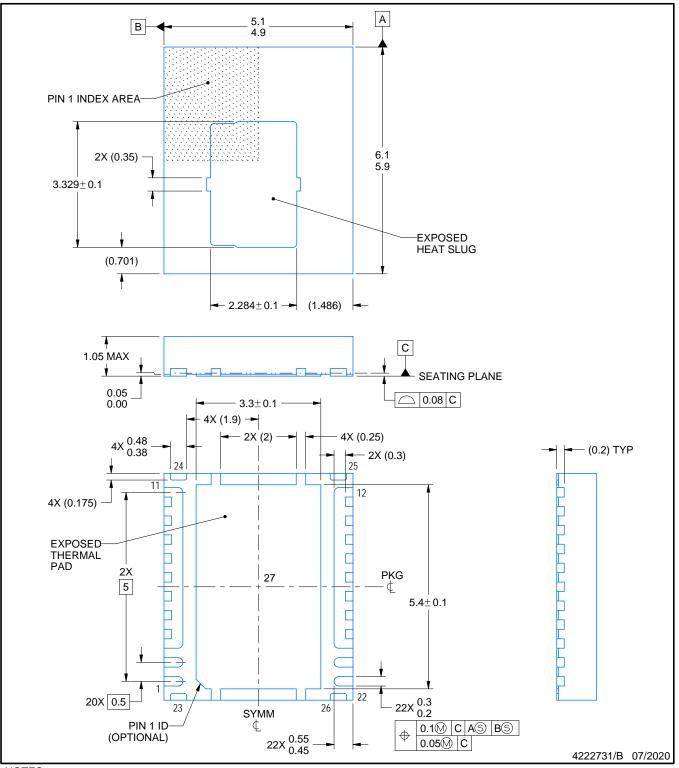

## DMM0022A

## **PACKAGE OUTLINE**

## LSON-CLIP - 1.05 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

- 4. Tie bar size and position may vary.

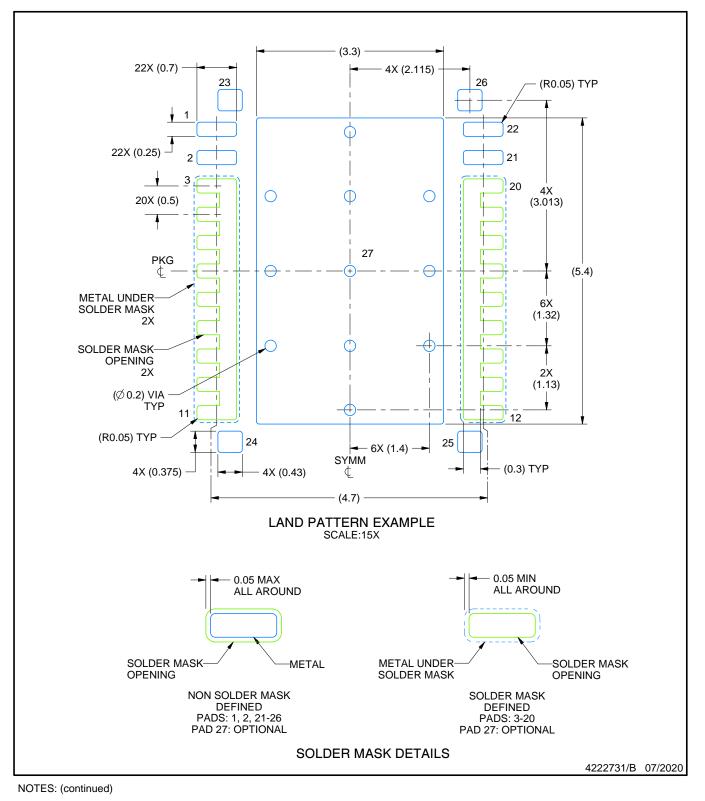

## DMM0022A

# **EXAMPLE BOARD LAYOUT**

## LSON-CLIP - 1.05 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

5. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature

number SLUA271 (www.ti.com/lit/slua271).

6. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

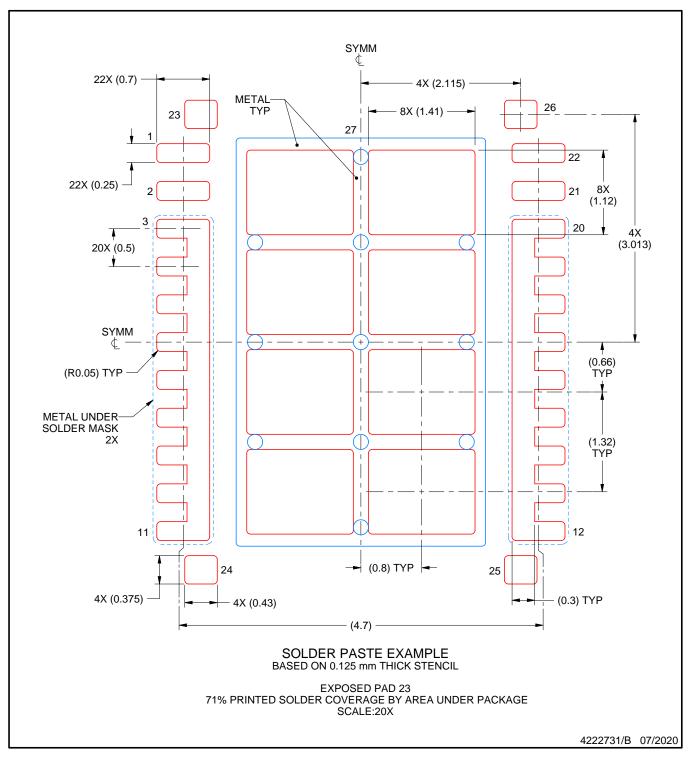

# DMM0022A

# **EXAMPLE STENCIL DESIGN**

## LSON-CLIP - 1.05 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司