# Memory addressing & CPU addressing modes

**TI Precision Labs – Microcontrollers**

**Presented by Brandon Fisher**

**Prepared by Evan Lew**

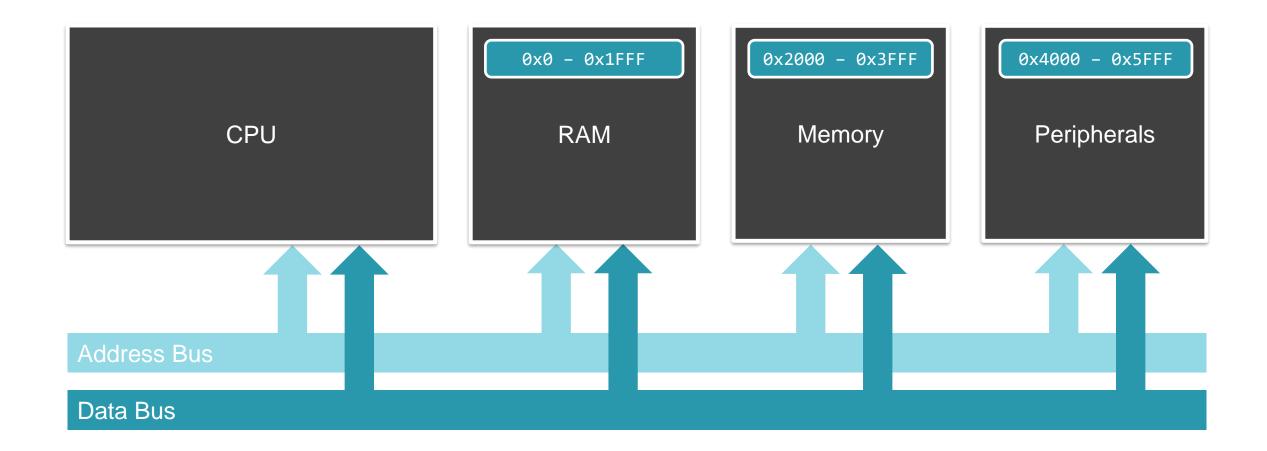

## **Memory addressing review**

## **Memory addressing review**

3

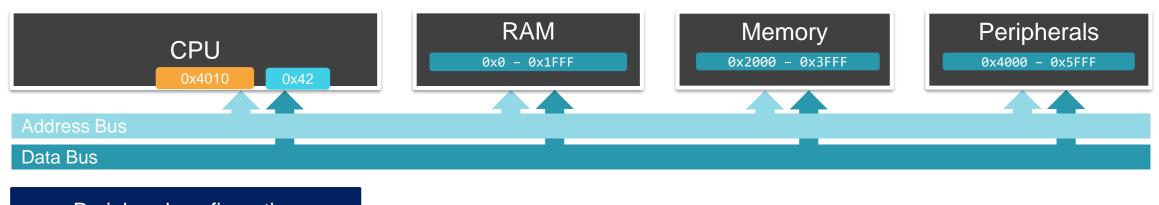

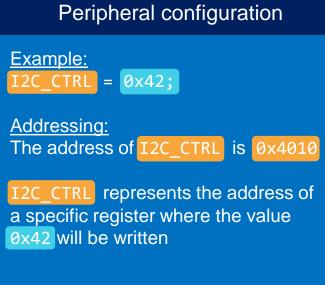

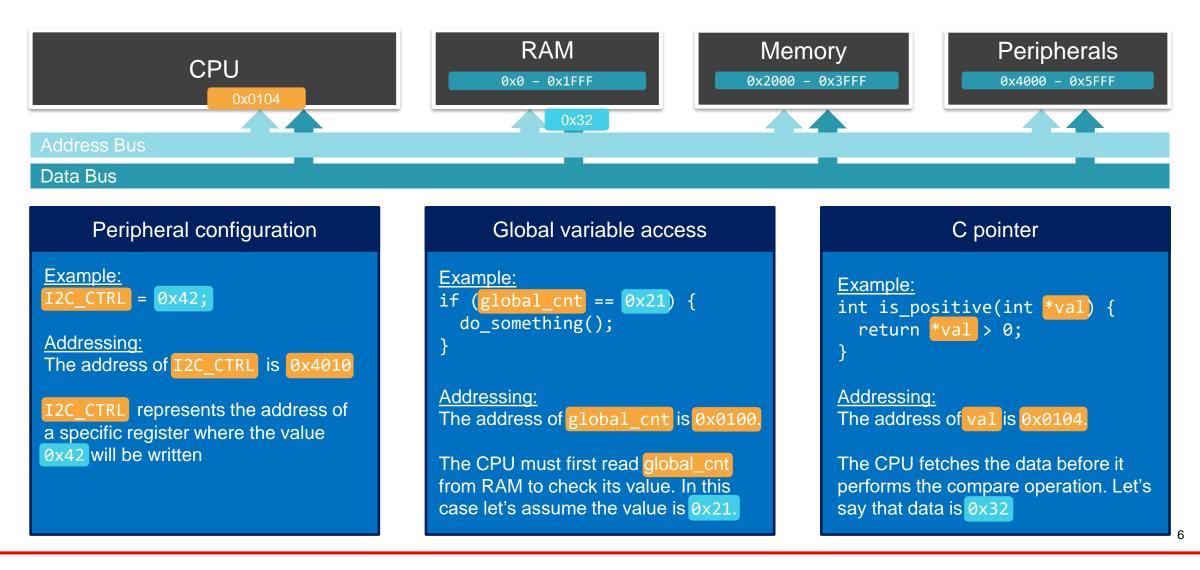

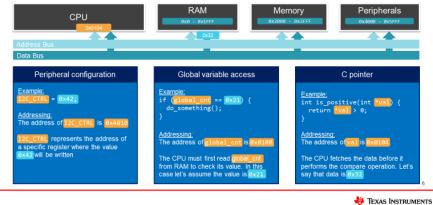

## **Examples of addressing**

## **Examples of addressing**

## **Examples of addressing**

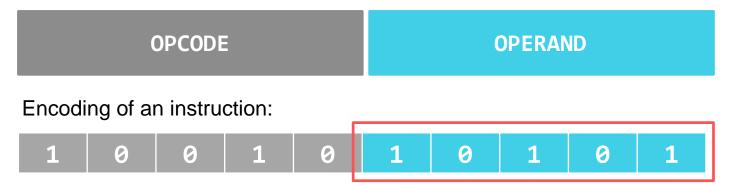

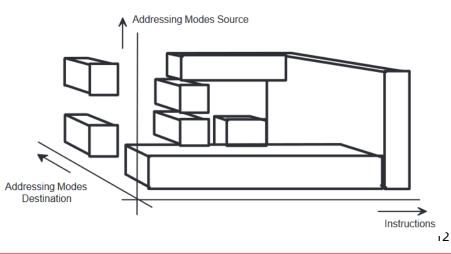

## **CPU addressing modes**

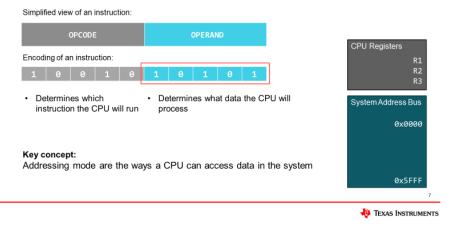

Simplified view of an instruction:

- Determines which instruction the CPU will run

- Determines what data the CPU will process

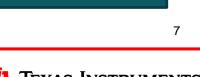

| CPU Registers      |      |

|--------------------|------|

|                    | R1   |

|                    | R2   |

|                    | R3   |

| System Address Bus |      |

|                    | 0000 |

## Key concept:

Addressing mode are the ways a CPU can access data in the system

0x5FFF

# **Register addressing mode**

$\rightarrow$  Register contents are operand

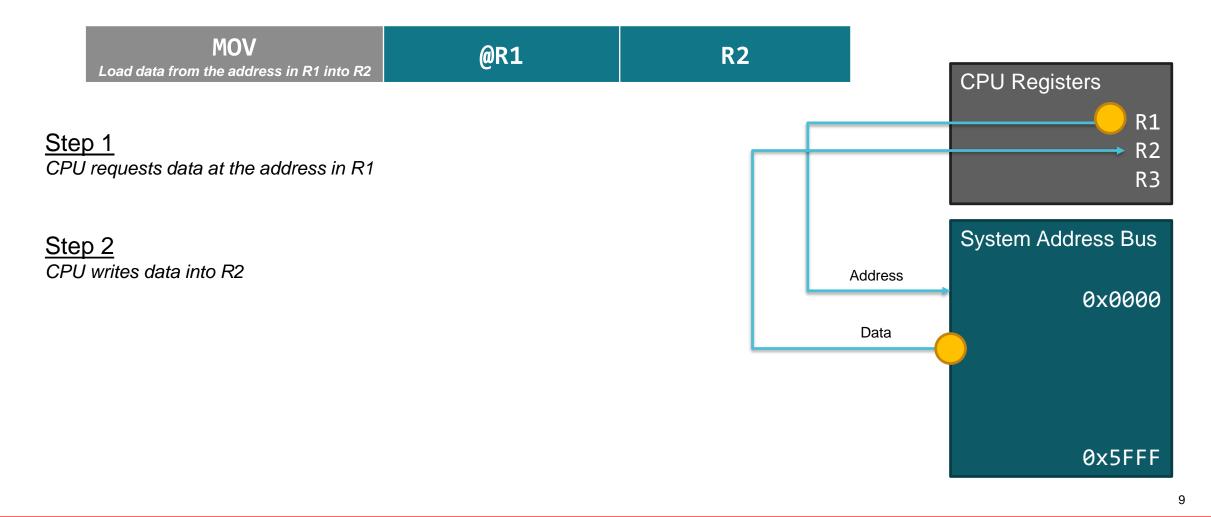

## Indirect register addressing mode

$\rightarrow$  Register contents is an address pointer to the operand

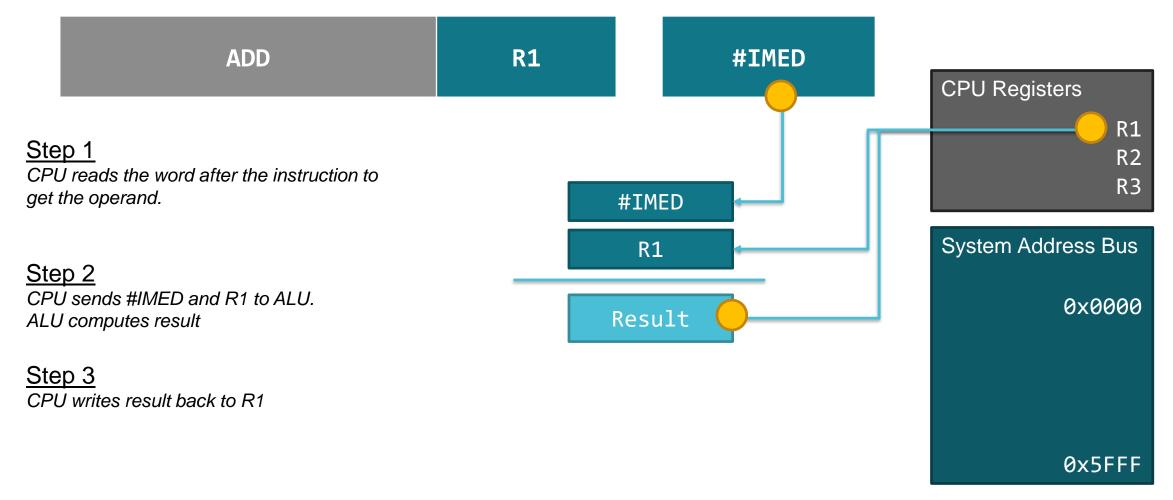

## Immediate addressing mode

$\rightarrow$  Data following instruction is the operand

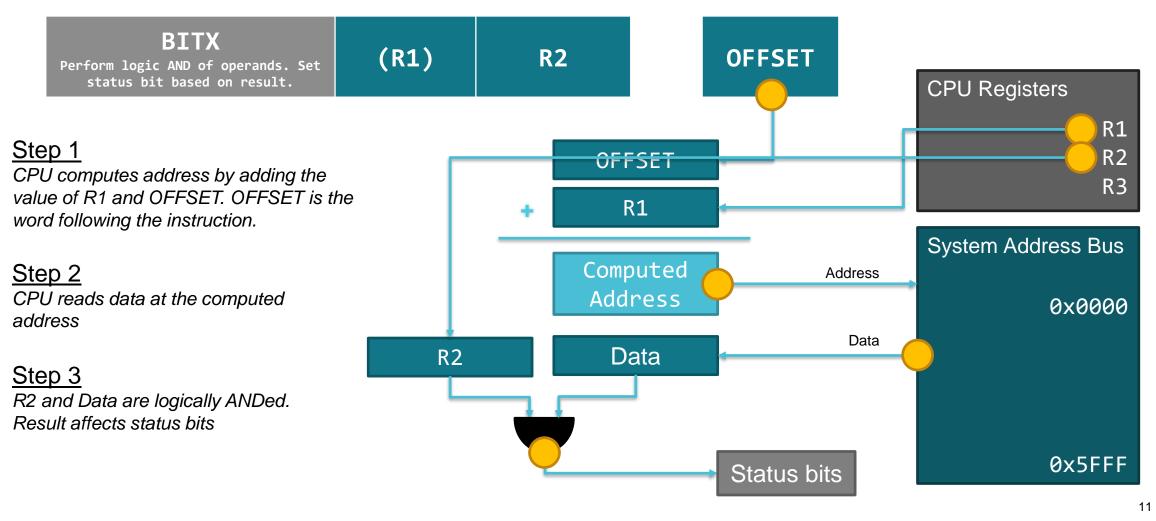

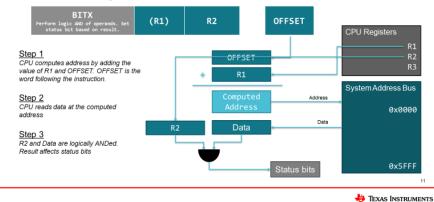

## Indexed addressing mode

$\rightarrow$  Data at address in the register plus an offset

# Addressing mode description

| Addressing<br>Mode     | Syntax | Description                                                                                                          |

|------------------------|--------|----------------------------------------------------------------------------------------------------------------------|

| Register Mode          | Rn     | Register contents are operand                                                                                        |

| Indexed Mode           | X(Rn)  | (Rn + X) points to the operand. X is stored in the next word                                                         |

| Symbolic Mode          | ADDR   | (PC + X) points to the operand. X is<br>stored in the next word. Indexed Mode<br>X(PC) is used                       |

| Absolute Mode          | &ADDR  | The word following the instruction contains the absolute address                                                     |

| Indirect Register      | @Rn    | Rn is used as a pointer to the operand                                                                               |

| Indirect Autoincrement | @Rn+   | Rn is used as a pointer to the operand.<br>Rn is incremented afterwards                                              |

| Immediate Mode         | #N     | The word following the instruction<br>contains the immediate constant N.<br>Indirect Autoincrement Mode @PC+<br>used |

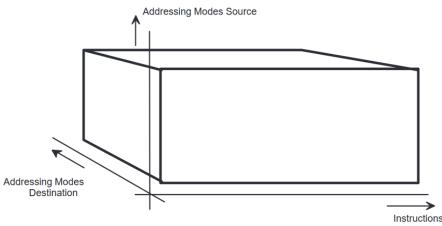

## Orthogonal architecture:

Instructions implement all addressing modes for all operands

## Non-Orthogonal architecture:

Instructions implement a subset of addressing modes

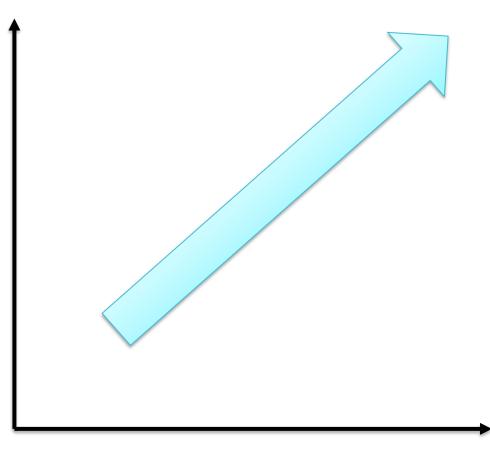

## Addressing mode speed comparison

| Addressing Mode                            |                 |              |  |

|--------------------------------------------|-----------------|--------------|--|

| Source                                     | Destination     | Clock Cycles |  |

| Register                                   | Register        | 1            |  |

|                                            | Program counter | 3            |  |

|                                            | Indexed         | 4            |  |

|                                            | Absolute        | 4            |  |

| Indirect register                          | Register        | 2            |  |

|                                            | Program counter | 4            |  |

|                                            | Indexed         | 5            |  |

|                                            | Absolute        | 5            |  |

| Indirect register<br>with<br>autoincrement | Register        | 2            |  |

|                                            | Program counter | 4            |  |

|                                            | Indexed         | 5            |  |

|                                            | Absolute        | 5            |  |

| Immediate                                  | Register        | 2            |  |

|                                            | Program counter | 3            |  |

|                                            | Indexed         | 5            |  |

|                                            | Absolute        | 5            |  |

Number of clock cycles

Addressing mode complexity

13

# Addressing modes in practice

C Code:

```

int is_odd(int *val) {

if (*val & 0x1) {

return 1;

} else

return 0;

}

```

Assembly:

| DECD.W | SP             |

|--------|----------------|

| MOV.W  | R12,0x0000(SP) |

| MOV.W  | #1,R15         |

| BIT.W  | @R12,R15       |

| JEQ    | (\$C\$L1)      |

| MOV.W  | #1,R12         |

| JMP    | (\$C\$L2)      |

| CLR.W  | R12            |

| INCD.W | SP             |

| RETA   |                |

|        |                |

DescriptionLoad the value '1' into R15Source operand addressing modeImmediateDestination addressing modeRegister

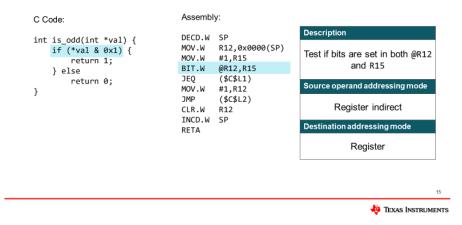

# Addressing modes in practice

## C Code:

```

int is_odd(int *val) {

if (*val & 0x1) {

return 1;

} else

return 0;

}

```

Assembly:

| DECD.W | SP             |

|--------|----------------|

| MOV.W  | R12,0x0000(SP) |

| MOV.W  | #1,R15         |

| BIT.W  | @R12,R15       |

| JEQ    | (\$C\$L1)      |

| MOV.W  | #1,R12         |

| JMP    | (\$C\$L2)      |

| CLR.W  | R12            |

| INCD.W | SP             |

| RETA   |                |

|        |                |

Description

Test if bits are set in both @R12

and R15

Source operand addressing mode

**Register indirect**

Destination addressing mode

Register

## **Addressing mode review**

#### **Examples of addressing**

V IEXAS INSTRUM

#### Indexed addressing mode

→ Data at address in the register plus an offset

#### **CPU addressing modes**

#### Addressing modes in practice

To find more microcontrollers technical resources and search products, visit **ti.com/microcontrollers**.