# PDK (Platform Development Kit) Getting Started

**Automotive Processors**

# **Agenda**

- PDK Overview

- PDK Software Architecture

- PDK Directory structure

- PDK Pre-requisite and Build instructions

- Running Examples

- Important Links

# PDK Overview (1/2)

- Platform Development Kit (PDK) is a single scalable software driver package to offer streamlined development across different TDA processors

- Provides peripheral programming interface Easy to use SW interface

- Provides software portability across devices for a given peripheral

- Provides stand-alone examples to demonstrate the capabilities of the peripherals

- Product is designed to scale for each SoC. Single package is used to support more than one SoC. The product packaging/folder takes care of scalability for new IPs of new SoCs.

- MISRA-C compliant

# PDK Overview (2/2)

- All required libraries and drivers provided are OS agnostic with few additional TI-RTOS drivers.

- Can be used stand-alone

- Not a middleware complete solution

- Supports following devices

- TDA2xx

- TDA2Ex

- TDA3xx

- TDA2Px

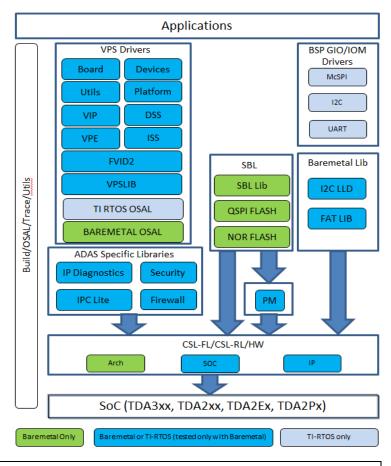

## **PDK Software Architecture**

CSL Libraries: UART, 12C

GPIO, Mailbox, Spinlock, EDMA, GPMC, McASP, McSPI, OCMC, QSPI,

SBL, MMU, Timer, MMCSD, WDTIMER, PCIe

**Driver libraries:** I2C, QSPI, FAT, NOR, VPS (VIP/DSS/VPE)

SD, NOR and QSPI bootmodes

**UART** console utility

#### PDK Software Architecture

## Software Modules – CSL Module

- Chip Support Library contains

- APIs to configure and access peripherals

- Simple, consistent and intuitive to use APIs

- Logical group of register reads and writes to get a functional layer for a given IP

- Stateless functions; blocking and runs to completion

- System Configuration Code:

- Provides functions specific to SoC level System Configuration.

- Provides the following functionalities:

- Start-up Code

- Interrupt-vector initialization

- Low level CPU specific code

- May involve assembly code and hence can be tools specific

- Sub module to further abstract and group the functionality.

## **Software Modules – CSL Module**

| Sub Modules      | Description                                                                                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arch             | This sub module contains the core specific functionality and initialization code for the system and cores. The interrupt controller API's to configure and enable/disable the interrupt is also part of this sub module. Source code is available under 'csl/arch' folder. |

| SoC              | SoC specific defines are abstraction under this sub module. SoC specific base address, macros and cross bar configuration code is available under this sub module. Source code is available under 'csl/soc' folder.                                                        |

| IP Specific Code | API to use the functionality of different IP's is available as part of this sub module. Source code is available under 'csl/src/ip' folder.                                                                                                                                |

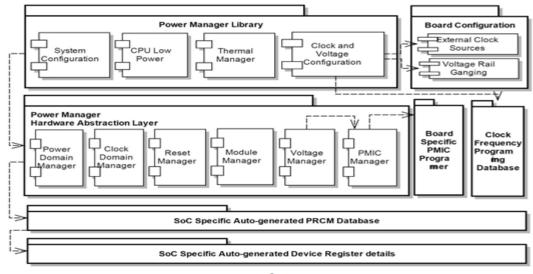

## **Software Modules – PM**

#### PM Module

- Provides API to configure

Power domain and Clock

domain

- Set power state for different modules

- Set clock rate for different module

- Supports Dynamic Power Management

- Supports SoftwareThermal Management

**Power Management Software Components**

## **Software Modules – PM**

- PM Module types

- Master Standby

- Valid for Initiators to the Interconnect

- When Master does not want clocks configure IP level SYSCONFIG MIDLEMODE or STANDBYMODE

- Slave Idle

- Valid for modules which respond to requests.

- Configure PRCM register CLKCTRL. MODULEMODE.

- Configure IP level SYSCONFIG SIDLEMODE or IDLEMODE

- PM Module can be further split into

- PRCM Database: Abstracts the SOC specific PRCM details.

- PMLIB: Library which can be used by application to initialize the system

- PMHAL: Contains board specific PMIC functions

## **Software Modules – SBL**

#### SBL

- Initializes the execution environment for multi-core application

- Configure the Voltage rails (AVS Class 0)

- Initialize the Interrupt Controller

- Setup the ADPLL values

- Power on I/O peripherals

- Power on slave cores

- Configure required PADs

- Initialize DDR

- Load the multicore application image into DDR

- Bring slave cores out of Reset

- Boot Modes: QSPI, QSPI\_SD, NOR and MMCSD application images

## **Software Modules – ADAS Libraries**

#### Diagnostic Library

- Contains set of software function to diagnosing the health of various modules and interfaces of the device.

- Supports ECC, CRC, ADC, CAN and SPI modules.

- Initializes the modules the verify the functionality in different configurations

#### IPC Lite Library

- OS agnostic library to provide two way communication between hosts

- Built on top of mailbox

- Supports 32bit or 64bit value to be transferred

- Supports event multiplexing

## **Software Modules – ADAS Libraries**

#### Firewall

- Provides set of function to configure the system to prevent unauthorized access to the modules

- Supports L3 and L4 interconnect

#### Security

- Provides no-OS platform support for security specific features

- Required to work with TDA3xx GP prime variant of devices

- Provide code for AES128-CBC and SHA256 encryptions

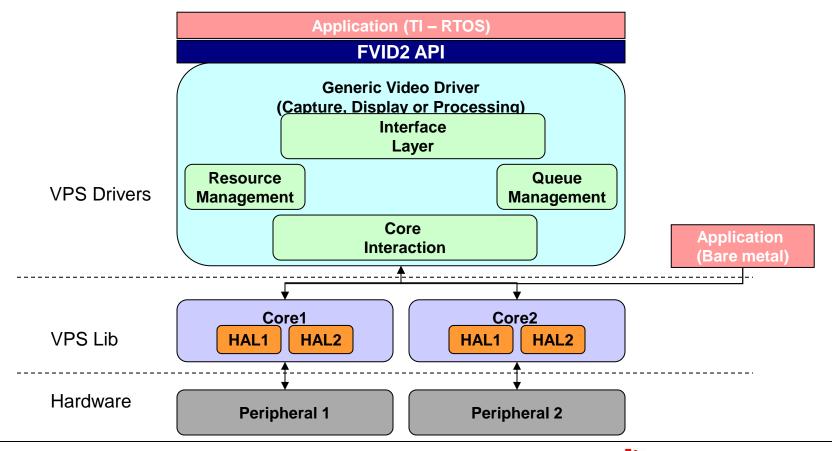

## **Software Modules – VPS**

- VPS Module

- Provides set of API's to allow users to make use of all video hardware features.

- VPS drivers are based on FVID2 interface

- Platform interface: SoC specific functionality

- Board interface: Board-specific functionality

- Decoder/Encoder interfaces: Interfaces to use different decoders or encoders

- VPS consists of following modules

- Video Input Port (VIP)

- Video Processing Engine (VPE)

- Display Sub System (DSS)

- Imaging sub system (ISS) includes CAL, ISP, SIMCOP

# **Software Partition – VPS Diver Stack**

## Software Modules – BSP LLD

- Drives based on the sysbios operating system.

- Implemented in the GIO models of the sysbios.

- Polled, interrupt and DMA mode of transfers are supported.

- Supports master and slave mode for McSPI and I2C

- Supports

- I2C:

- UART:

- McSPI:

# **Software Modules – Examples, Utility and tools**

| Tools/Utilities           | Description                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mFlash                    | mFlash tool is used provide a way to flash the binary images to QSPI Flash memory using the UART interface. Tool is available @ "packages/ti/boot/sbl_auto/tools/mflash"                                                                                                                                                                                                |

| Multicore Image generator | These are the scripts provided bmFlash tool is used provide a way to flash the binary images to QSPI Flash memory using the UART interface. Tool is available @ "packages/ti/boot/sbl_auto/tools/mflash" y the TI to generate the multicore app images using individual core binaries. Tool is available @ "packages/ti/boot/sbl_auto\tools/MulticoreImageGen_xxxx.bat" |

| QSPI/Nor flash writer     | QSPI or NOR flash writer are required to flash the SBL AppImage in QSPI/NOR flash. Tool is available @ Packages/ti/boot/sbl_auto/qspiflash/examples Packages/ti/boot/sbl_auto/norflash/examples                                                                                                                                                                         |

| UART console              | Standard API to configure, read and write data on the UART interface. Packages/ti/csl/example/utils/uart_console                                                                                                                                                                                                                                                        |

|                           | TEXAS                                                                                                                                                                                                                                                                                                                                                                   |

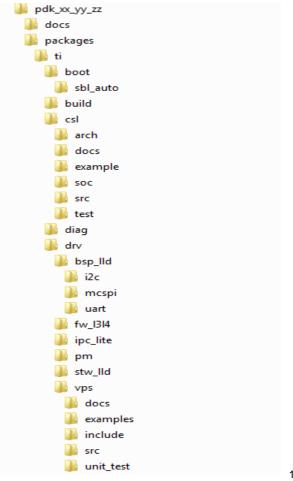

# **Directory Structure**

- Uses simple and intuitive directory structure

- Provides scope to accommodate new SoCs in the same directory structure

- Build folder contains all the make rules for building PDK

- Each module/library has Include folder containing the corresponding header files

- Drivers and libraries are separated from low level driver, categorized and under single directory.

- Examples and sample applications are part of corresponding module

# **PDK Pre-requisite**

- Code Composer Studio (v 5.4.0.00091 or above)

- Compiler and Tool chains

- TMS470

- TI Compiler C6000

- TI Compiler ARP32

- Linaro GCC tool chain for A15

- BIOS/XDC

- EDMA LLD

- Flash tools:

- NOR Flash Writer

- QSPI Flash Writer

- Development Board

- PDK package

- PDK package is available as part of Processor SDK.

- PDK package will be available at "vision\_sdk\_xx\_yy\_zz/ti\_components/driv ers/pdk"

- Emulator

- XDS560v2

- XDS200

- SD Card

### **PDK Build**

- Supports Makefile based build

- PDK will be automatically build while building Vision SDK. PDK can be build independently also and command's the should be issued from "<pdk>/packages/ti/build" folder

- Following steps application for building PDK independently

- Makerules for different cores are specified in packages/ti/build/makerules

- Environment variables are specified in packages/ti/build/makerules/env.mk

- gmake allcore BOARD=<BOARD> builds all the components

- gmake <example/module> BOARD=<BOARD> builds specific module or example

<BOARD> can be tda3xx-evm, tda2xx-evm, tda2ex-evm or tda2px-evm

Refer to <a href="http://processors.wiki.ti.com/index.php/PDK/PDK">http://processors.wiki.ti.com/index.php/PDK/PDK</a> TDA Building The Package

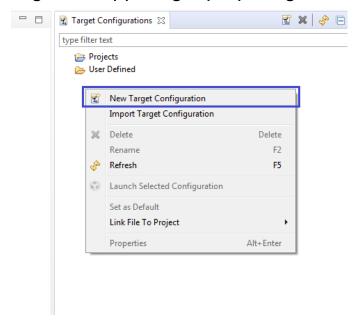

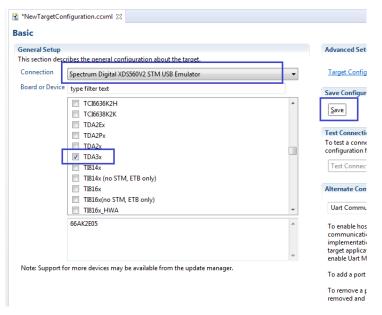

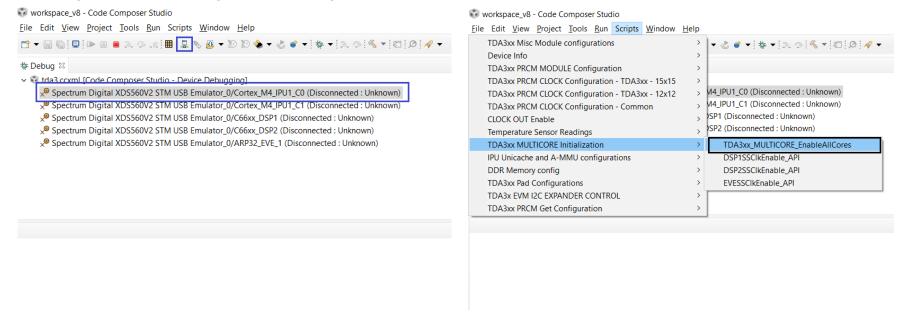

# **Running Examples (1/2)**

Examples can be run either in Debug mode using CCS or SD boot mode using SD card or QSPI/NOR boot mode using on-board flash. Refer to SBL user-guide for more details about flashing SBL, appimage, preparing SD etc.

# **Running Examples (2/2)**

Examples can be run either in Debug mode using CCS or SD boot mode using SD card or QSPI/NOR boot mode using on-board flash. Refer to SBL user-guide for more details about flashing SBL, appimage, preparing SD etc.

# **Important links**

- PDK Software Developer Guide:

<a href="http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_Software\_Developer\_Guide">http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_Software\_Developer\_Guide</a>

- STW/BSP to PDK Migration Guide: <u>http://processors.wiki.ti.com/index.php/PDK/BSP\_STW\_To\_PDK\_Migration\_Guide</u>

- VPS User Guide: <a href="http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_VPS\_User\_Guide">http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_VPS\_User\_Guide</a>

- VPS training: Available at <PDK>/packages/ti/drv/vps/docs/training/

- PM User Guide: <a href="http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_PM\_User\_Guide">http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_PM\_User\_Guide</a>

- SBL User Guide: <a href="http://processors.wiki.ti.com/images/b/b7/TDA\_SBL\_UserGuide.pdf">http://processors.wiki.ti.com/images/b/b7/TDA\_SBL\_UserGuide.pdf</a>

- Application Notes: <a href="http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_Application\_notes">http://processors.wiki.ti.com/index.php/PDK/PDK\_TDA\_Application\_notes</a>

© Copyright 2018 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com