# Programmable Real-time Unit for Gigabit Industrial Communication Subsystem (PRU\_ICSSG)

**Overview**

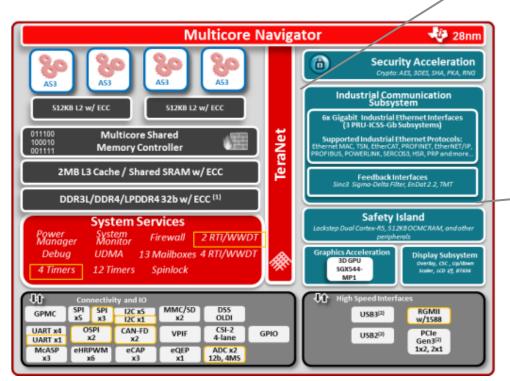

Industrial Communication

Subsystem

6x Gigabit Industrial Ethernet Interfaces

(3 PRU-ICSS-Gb Subsystems)

Supported Industrial Ethernet Protocols:

TSN, Ethernet MAC, EtherCAT, PROFINET, EtherNET/IP,

PROFIBUS, POWERLINK, SERCOS3, HSR, PRP and more...

Feedback Interfaces

Sinc3 Sigma-Delta Filter, EnDat 2.2, TMT

AM6548 diagram shown

## What is the PRU\_ICSSG?

# The Programmable Real-time Unit and Industrial Communication Subsystem Gigabit (PRU\_ICSSG) is a low-latency microcontroller subsystem:

- Builds on capabilities introduced in PRU-ICSS

- Has access to pins, events and all system-on-chip (SoC) resources

- Provides flexibility to implement the following:

- Fast, real-time responses

- Specialized data handling operations

- Custom peripheral interfaces

- Offloading of tasks from the other processor cores of the SoC

## Feature comparison: PRU\_ICSSG vs. PRU-ICSS

| Feature                            | PRU ICSSG                                | PRU-ICSS           |

|------------------------------------|------------------------------------------|--------------------|

| Cores                              | 1112-1112                                |                    |

| PRU cores                          | 4                                        | 2                  |

| Max frequency                      | 250 MHz                                  | 225 MHz or 200 MHz |

| Memory per PRU core                | IRAM, DRAM, BS RAM                       | IRAM, DRAM         |

| Shared DRAM                        | Yes                                      | Yes                |

| General Purpose Inputs             |                                          |                    |

| Direct Input                       | Yes                                      | Yes                |

| 16-bit Parallel Capture            | Yes                                      | Yes                |

| 28-bit Shift                       | Upgraded                                 | Yes                |

| 3 Ch. Peripheral Interface (EnDAT) | Yes                                      | Device dependent   |

| 9 Ch. Sigma Delta                  | Upgraded (not 100% backwards compatible) | Device dependent   |

| General Purpose Outputs            |                                          |                    |

| Direct Output                      | Upgraded                                 | Yes                |

| Shift out                          | Upgraded                                 | Yes                |

| Interrupt Controller / Manager     |                                          |                    |

| INTC                               | Upgraded                                 | Yes                |

| Task Manager                       | New                                      |                    |

New to PRU\_ICSSG

Upgraded in PRU\_ICSSG

| Feature                       | PRU_ICSSG                                         | PRU-ICSS         |  |

|-------------------------------|---------------------------------------------------|------------------|--|

| Accelerators: Data Processing |                                                   |                  |  |

| MPY/MAC                       | Upgraded                                          | Yes              |  |

| CRC 16/32                     | Upgraded                                          | Device dependent |  |

| Scratch Pad                   | <b>4 banks</b> (PRU), <b>2 banks</b><br>(RTU_PRU) | 3 banks          |  |

| IPC Scratch Pad               | New                                               |                  |  |

| Byte Swap                     | New                                               |                  |  |

| SUM32                         | New                                               |                  |  |

| Spinlock                      | New                                               |                  |  |

| Filter Data Base (FDB)        | New                                               |                  |  |

| Accelerators: Data Movement   |                                                   |                  |  |

| XFR2VBUS                      | New                                               |                  |  |

| PSI TX & RX                   | New                                               |                  |  |

| XFR2TR                        | New                                               |                  |  |

| Peripherals                   |                                                   |                  |  |

| UART                          | Yes                                               | Yes              |  |

| eCAP                          | Yes                                               | Yes              |  |

| IEP                           | 2, Upgraded                                       | 1                |  |

| MII_RT or MII_G_RT            | Upgraded                                          | Yes              |  |

| MDIO                          | Yes                                               | Yes              |  |

| SGMII                         | New                                               |                  |  |

| PWM                           | New                                               |                  |  |

# **PRU-ICSS** sample applications

#### **Industrial Networking**

- Industrial Ethernet

- Serial Fieldbus

- Custom Interfaces

#### **Feedback Interfaces / Motor Control**

- Encoder Feedback

- Sigma Delta filter

#### **General Purpose**

- Signal Processing

- Application Synchronization

- Backplane Communication

# PRU\_ICSSG sample applications

#### **Industrial Networking**

Industrial Ethernet

1Gb Ethernet

Serial Fieldbus

- 1Gb Time Sensitive Networking

Custom Interfaces

#### **Feedback Interfaces / Motor Control**

Encoder Feedback

Integrated PWM

Sigma Delta filter

#### **General Purpose**

- Signal Processing

Pre-emptible software execution

- Application Synchronization

- Backplane Communication

#### For more information

- PRU Training Series: <a href="https://training.ti.com/pru-training-series">https://training.ti.com/pru-training-series</a>

- PRU-ICSS Feature Comparison: <a href="http://www.ti.com/lit/sprac90">http://www.ti.com/lit/sprac90</a>

- PRU\_ICSSG Getting Starting Guide on Linux: <a href="http://www.ti.com/lit/sprace9">http://www.ti.com/lit/sprace9</a>

- PRU Read Latencies: http://www.ti.com/lit/sprace8

- PRU-ICSS / PRU\_ICSSG Migration Guide <a href="http://www.ti.com/lit/spraci">http://www.ti.com/lit/spraci</a>

- For questions about this training, refer to the E2E Community Forums at <a href="http://e2e.ti.com">http://e2e.ti.com</a>