Prepared by David Liu, Ikechukwu Anyiam

Presented by Nicholaus Malone

# DisplayPort (DP) signal interface

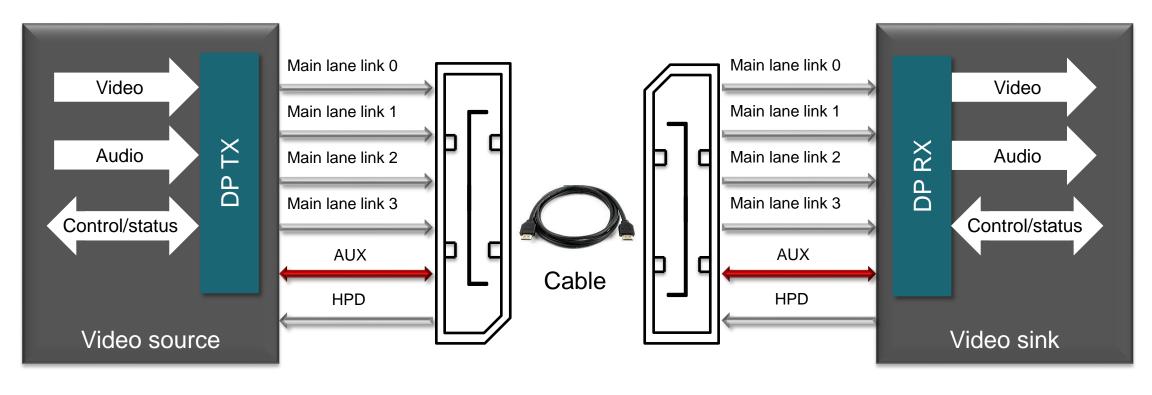

## **DP Hot Plug Detect (HPD) and AUX**

#### **HPD**

- Indicate the presence of the sink

- Serves as an interrupt from the sink to the source

#### **AUX**

- AC coupled Bi-directional signal path

- 1 Mbps transfer rate either direction Manchester encoded

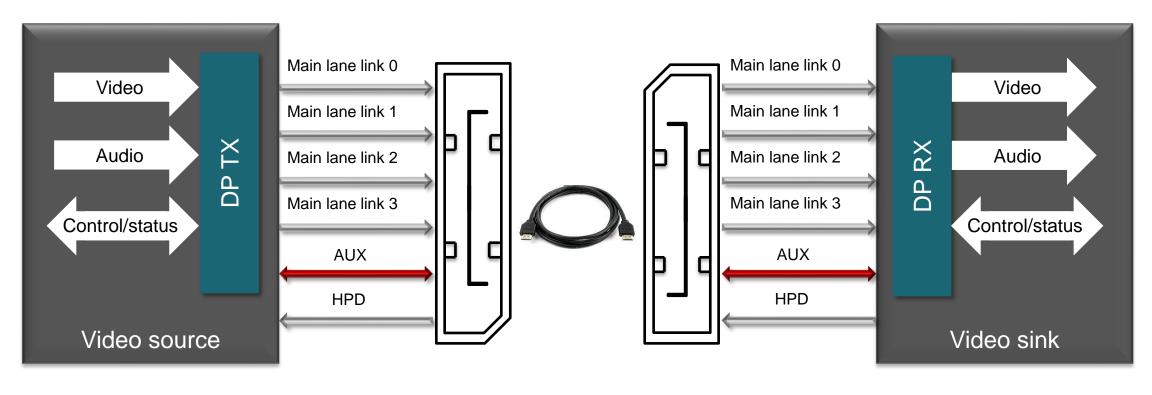

## **DP** main link signaling characteristic

## **DP** main link signaling characteristic

- 1.62Gbps per lane (reduced bit rate (RBR))

- 2.7Gbps per lane (high bit rate (HBR))

- 5.4Gbps per lane (high bit rate 2 (HBR2))

- 8.1Gbps per lane (high bit rate 3 (HBR3))

- 10Gbps per lane (ultra high bit rate 10 (UHBR10))

- 13.5Gbps per lane (ultra high bit rate 13.5 (UHBR13.5))

- 20Gbps per lane (ultra high bit rate 20 (UHBR20))

- Three possible lanes configuration

- 1 lane

- 2 lanes

- 4 lanes

- Data rate and supported lane configuration are communicated over AUX between the source and sink

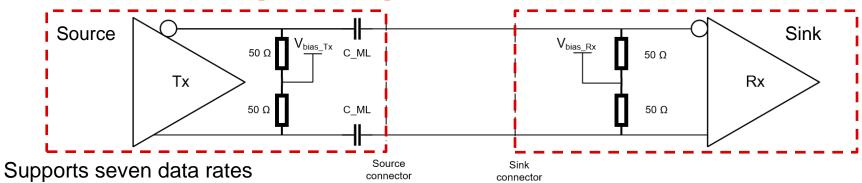

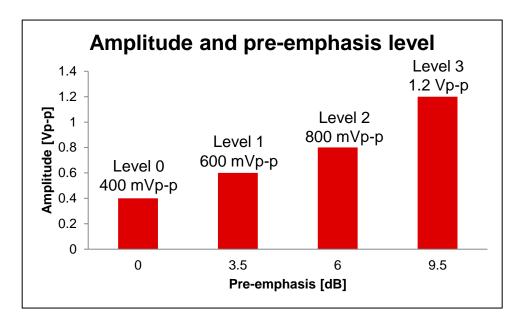

## **DP** main link signaling characteristic

- Amplitude and pre-emphasis defined as levels

- Default signal amplitude at source is 400mVp-p

- Default signal pre-emphasis at source is 0dB

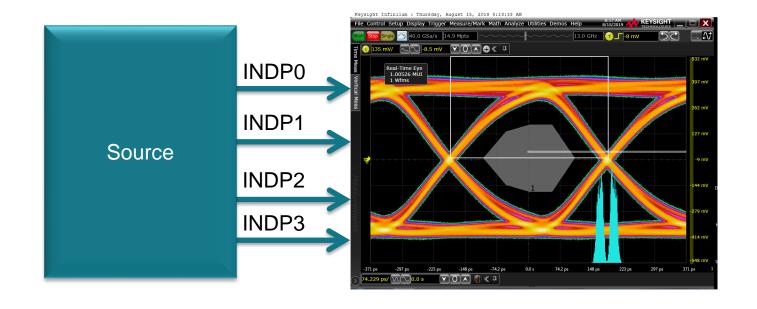

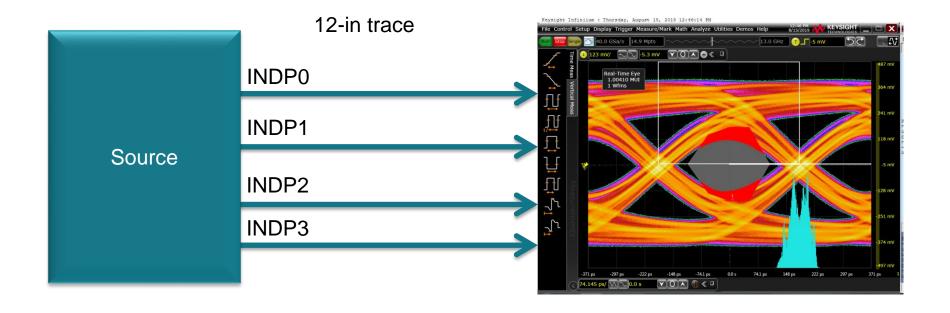

### DP source TX and sink RX design challenge

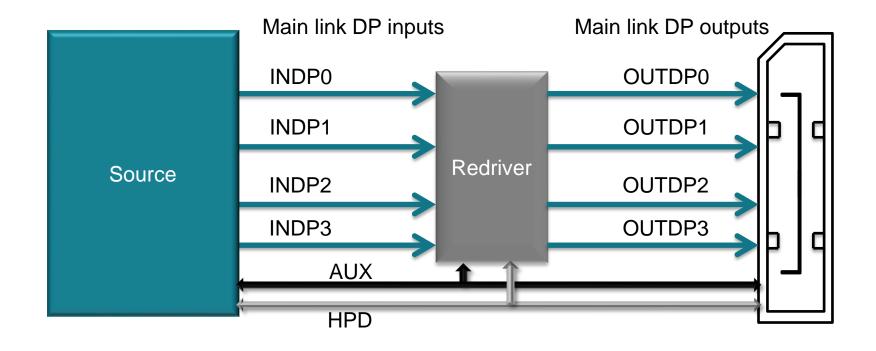

#### Placement of the DP redriver

- Re-driver placement depends on total insertion loss of the system

- Insertion loss:

- PCB trace

- Via

- Connector

- Silicon package, etc.

#### Placement of the DP redriver

Insertion Loss

$$(dB/in) \cong \frac{f^{1/2}}{w} + 2.3 \times f \times D_f \times D_k^{1/2}$$

- w = trace width [mils]

- f = Nyquist frequency [GHz] → DP data rate / 2

- Df = the PCB dissipation factor

- Dk = the PCB dielectric constant

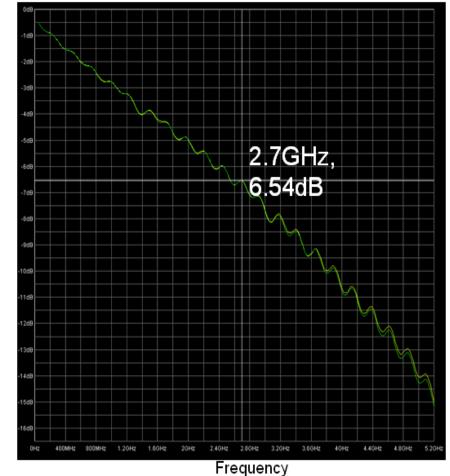

#### Placement of the DP redriver

Insertion Loss

$$\left(\frac{dB}{in}\right) \cong \frac{f^{1/2}}{w} + 2.3 \times f \times D_f \times D_k^{1/2}$$

- f = 2.7

- W = 6

- Df = 0.02

- Dk = 4.3

Insertion Loss

$$\left(\frac{dB}{in}\right) \cong \frac{2.7^{1/2}}{6} + 2.3 \times 2.7 \times 0.02 \times 4.3^{1/2}$$

$$\cong 0.53^{dB}/_{in}$$

12in trace =  $12 \times -0.53$ dB/in =  $\sim 6.36$ dB

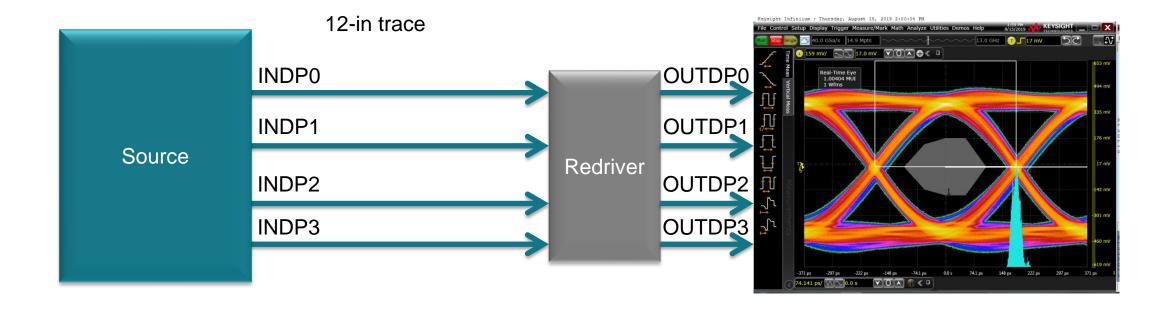

### Placement of the redriver

### Placement of the redriver

#### Placement of the redriver

# **Short quiz**

1. True or false: DP is a DC-coupled interface

- 3. True or false: Hot Plug Detect is used for configuring DP lanes

- 4. True or false: The insertion loss is the same regardless the DP data rate

- 5. True or false: A DP redriver can help improve the DP main link signal quality

- 6. True or false: The correct placement of the DP redriver is important for the design of system

### Thank you

- Future video sessions

- Details on DisplayPort 2.0 standard

- TI's signal conditioning devices

- Tl.com/e2e

© Copyright 2019 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com