### How to solve design challenges on interfacing Ethernet PHY with application processor or microcontrollers

# Thomas Mauer, SEM, Factory Automation and Control 2019

## Agenda

- Introduction

- Part 1 Ethernet design fundamentals

- Part 2 TIDA-010010: Integration example with AM5728 with DP83867

- Part 3 Ethernet PHY integration compression between TIDA-010010 and standard AM5728 EVM

- Summary and Outlook

## **Design challenges with Ethernet PHYs using MPU/MCU**

- Multi-protocol industrial Ethernet (2 ports).

- Standard Ethernet for uplink, edge and cloud connection, configuration and diagnostics data.

- Ethernet speed: 10/100/1000 Gbit.

- MAC to PHY Interface.

- Ethernet topology: Line, ring, star.

- New evolution for Ethernet in Industrial

- T1: Single twisted pair Ethernet for industrial.

- Power of Data Line: PoDL, APL, PoE

## Part 1

**Ethernet design fundamentals**

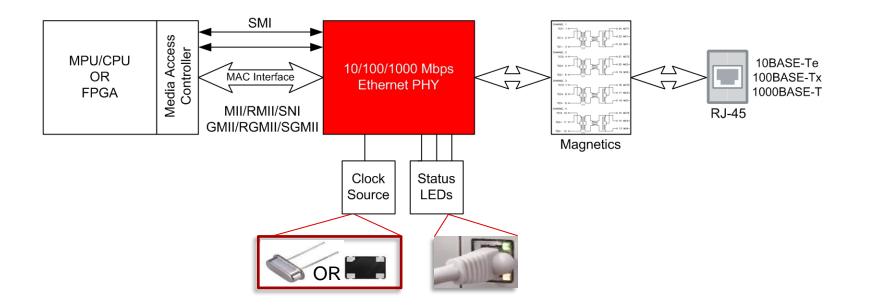

## Ethernet PHY common terminology

- PHY (Physical layer transceiver/device) provides a way to transfer digital data from one node (processor, FPGA, ASIC...) to another node via analog signaling over either copper or fiber optic cable.

- Three important processes a PHY handles:

- PCS, physical coding sublayer.

- PMA, physical medium attachment.

- PMD, physical medium dependent.

- Other key terms and functions:

- MDI, medium dependent interface (TD±/RD±).

- MII, media independent interface (Digital pins, TX\_D[3:0]/RX[3:0] etc...).

- Start of Frame Detection (SOF) for timestamping.

- Fast link-down detection (<15 μs)

- Cable Diagnostics (TDR, link quality, ...)

## **Connecting PHY to MAC: Typical application circuit**

## **MAC interfaces – used for data transfer**

Ē

| Interface Details | MII                                             | RMII                                   | SNI                          |

|-------------------|-------------------------------------------------|----------------------------------------|------------------------------|

| Full Name         | Media Independent<br>Interface                  | Reduced-Media<br>Independent Interface | Serial Network<br>Interface  |

| Pin Count         | 15                                              | 9                                      | 7                            |

| Clock Speed       | 25MHz – 100Mbps<br>2.5MHz – 10Mbps              | 50MHz – 10Mbps<br>and 100Mbps          | 10MHz – 10Mbps               |

| Transmit Pins     | TX_D[3:0], TX_EN,<br>TX_CLK                     | TX_D[1:0], TX_EN                       | TX_D[0], TX_EN,<br>TX_CLK    |

| Receive Pins      | RX_D[3:0], RX_DV,<br>RX_ER, COL, CRS,<br>RX_CLK | RX_D[1:0], CRS_DV                      | RX_D[0], CRS,<br>COL, RX_CLK |

## **MAC interfaces – used for data transfer**

Ē

| Interface Details | GMII                                            | RGMII                                          | SGMII                                         |

|-------------------|-------------------------------------------------|------------------------------------------------|-----------------------------------------------|

| Full Name         | Gigabit Media<br>Independent Interface          | Reduced-Gigabit Media<br>Independent Interface | Serial Gigabit Media<br>Independent Interface |

| Pin Count         | 24                                              | 12                                             | 4                                             |

| Clock Speed       | 125MHz – 1Gbps                                  | 125MHz – 1Gbps<br>DDR                          | 625MHz – 1.25Gbaud<br>data, DDR               |

| Transmit Pins     | TX_D[7:0], TX_EN,<br>TX_CLK, GTX_CLK,<br>TX_ER  | TX_D[4:0],<br>TXEN_ER, TCK                     | TX_P, TX_N                                    |

| Receive Pins      | RX_D[7:0], RX_DV,<br>RX_ER, COL, CRS,<br>RX_CLK | RX_D[4:0],<br>RXDV_ER, RCK                     | RX_P, RX_N                                    |

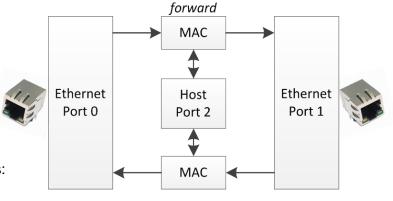

## **Industrial Ethernet MAC and frame processing**

- Media Access Controller (MAC)

- Industrial Ethernet uses 3-port switch: Two physical Ethernet ports and one host port

- Specialized MAC is required for following frame handling methods

- MAC requirements depend on industrial Ethernet protocol and master/slave

- Frame processing methods:

- Cut-through: Receives the Ethernet header, performs header analyzes and takes forwarding decision; frame is not modified by MAC. Examples: Profinet, Ethernet/IP, Powerlink, Sercos in UCC/NRT channels

- Delay Time: 3-4 µs

- On-the-fly: Frame is forwarded to second Ethernet port; MAC can perform read and write access to the frame while its runs through MAC; CRC is updated to reflect frame modifications by MAC. Examples: EtherCAT, Sercos

- Delay Time: <1 µs</li>

- Store and forward: Legacy mode used by all standard Ethernet MACs; store frame in memory, perform header analyzes first before taking forwarding decision; frame is not modified by MAC.

- Delay Time: 6.7 μs (64 Bytes) to 125 μs (1500 Bytes)

backward

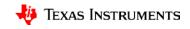

Integration example: TIDA-010010 Sitara™ AM5728 processor with DP83867IR

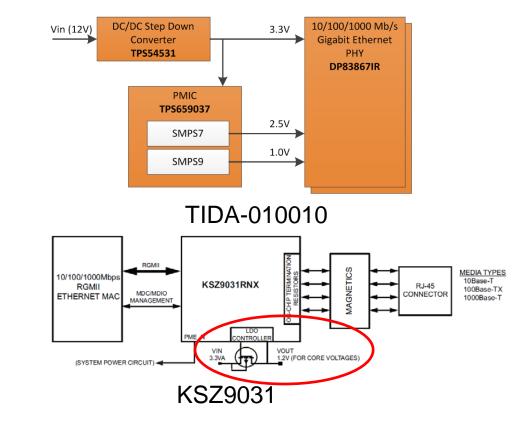

### TIDA-010010 system block diagram

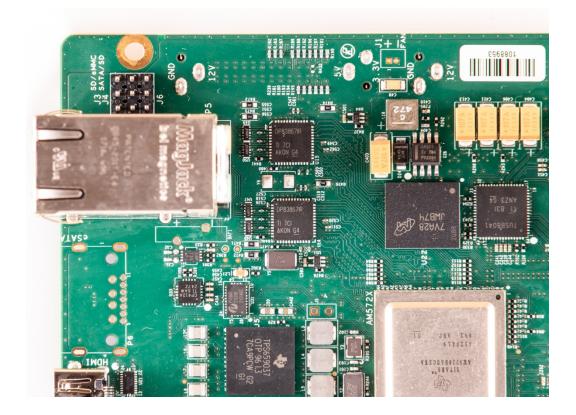

## **TIDA-010010 top and bottom PCB**

### **TIDA-010010 Ethernet PHY PCB section**

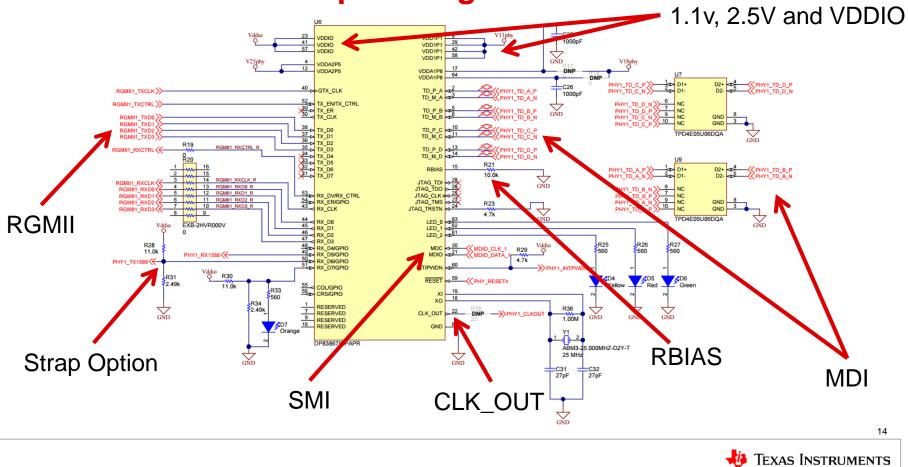

## **DP83867IR PHY example design**

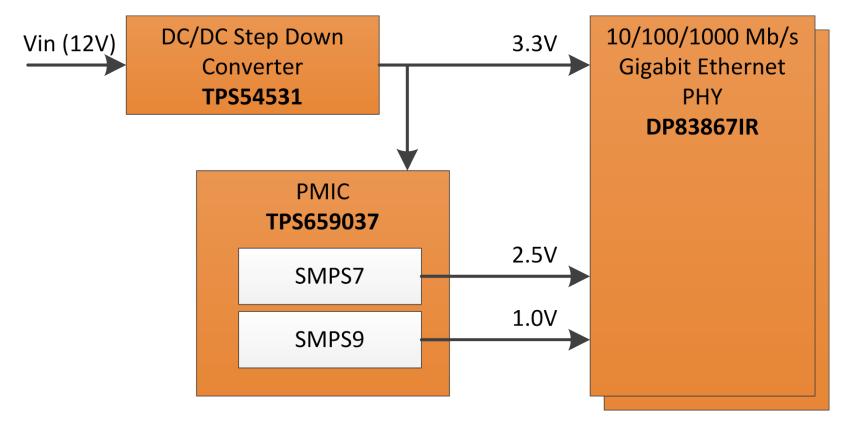

## **Power generation**

## **Bootstrap pins**

- DP83867 configured through bootstrap during power-on-reset.

- Examples: MDIO address, Full-duplex, RGMII mode.

- 4 voltage levels.

- 0 V Mode 1

- 1.4 V Mode 2 (mid-voltage level)

- 2.4 V Mode 3 (mid-voltage level)

- 3.3 V Mode 4

- AM5728 should not get exposed to mid-voltage level during power up.

- Effect on POH lifetime

- Options

- 1. Configure only Mode 1 and 4, avoid Mode 2 and 3

- Use MDIO after power up to configure the PHY

- 2. Buffer to isolate signals between AM5728 and DP83867 during power up

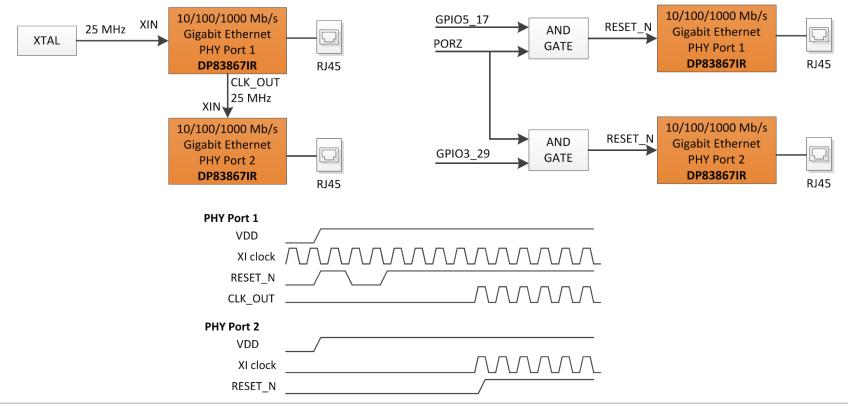

## **Clocking and reset generation**

## Ethernet PHY integration compression between TIDA-010010 and the standard AM5728 EVM

## DP83867IR vs. Microchip/Micrel KSZ9031

| Parameter           | DP83867                                                  | KSZ9031                                                                              |

|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|

| Size                | 48-pin QFN, 7mm x 7mm<br>64-pin QFP, 10mm x 10mm         | 48-pin QFN, 7mm x 7mm<br>64-pin QFP, 10mm x 10mm                                     |

| Current consumption | 457mW (RGZ)<br>490mW (PAP)                               | 538mW (1G, no traffic)<br>972mW (1G, no traffic + MOSFET losses)<br>621mW (1G, 100%) |

| Voltage Rails       | 3.3V, 2.5V, 1.1V or 1.0V                                 | 3.3V, 1.2V                                                                           |

| Voltage generation  | external                                                 | P-channel MOSFET for 1.2V<br>NOTE: Uses +441mW in MOSFET                             |

| Temperature         | -40°C to +85°C                                           | -40°C to +85°C                                                                       |

| Features            | Fast link drop (ECAT, IE)<br>Cable Diagnostics TDR, ALCD | n/a<br>LinkMD Cable Diagnostics TDR                                                  |

| TX/RX Delay         | 88ns / 288ns                                             | Not specified                                                                        |

| PCB / BOM area      | See next slides                                          | See next slides                                                                      |

## **Power supply solution**

- Using PMIC with AM5728

- Alternative suggestions from the TIDA-010010 reference design guide

- WCSP package option with 0.35-mm pitch enables smaller PCB board space area

- From 5-V or 3.3-V source voltage to 2.5-V supply voltage: TPS62802

- From 5-V or 3.3-V or 2.5-V source voltage to 1.0-V supply voltage: TPS62801

- QFN package option

- From 5-V or 3.3-V voltage to 2.5-V supply voltage: TPS62230

- 5-V or 3.3-V or 2.5-V voltage to 1.0 V: TPS62239

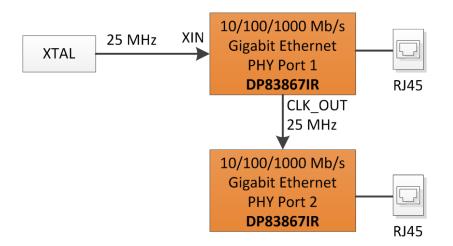

## Clocking

- TIDA-010010 uses daisy chain clocking:

XTAL → PHY1 → PHY2

- DP83867 supports CLK\_OUT pin

Configurable: 25MHz clock output

- KSZ9032 does not support 25 MHZ CLK\_OUT

## Layout area - DP83867 vs KSZ9031

╘┯╴

DP83867

KSZ9031

## **Summary and outlook**

## Industrial Ethernet Physical Layer Transceiver (PHY)

- Part number DP83848

- "Gold Standard" 10/100Mbps Industrial Ethernet PHY

- Supports 100BASE-TX

- Part number DP83822

- 10/100Mbps Industrial Ethernet PHY with IEEE 1588 SFD

- Supports 100BASE-TX and 100BASE-FX

- Fast-Link-Down detection

#### • Part number DP83TC811

- 100Mbps Ethernet PHY for single twisted pair cable

- Supports 100BASE-T1 Ethernet PHY

- Part number DP83630

- 10/100Mbps Industrial Ethernet PHY with integrated IEEE 1588 HW Timestamping support

- Supports 100BASE-TX and 100BASE-FX

- Part number DP83867

- 10/100/1000Mbps Industrial Ethernet Gigabit PHY with IEEE 1588 SFD

- Supports 100BASE-TX and 1000BASE-T

- Fast-Link-Down detection

- Part number DP83869

- 10/100/1000Mbps Industrial Ethernet Gigabit PHY with IEEE 1588 SFD

- Supports IEEE 802.3 1000Base-T, 100Base-TX, 10Base-Te,1000Base-X, 100Base-FX

- Fast-Link-Down detection

## **Processors with PRU-ICSS and EMAC/GMAC**

### PRU-ICSS (10/100Mbps)

#### Features

- 10/100 Ethernet Speeds

- Capable of supporting Industrial Ethernet protocols, Interface protocols, and Ethernet communication protocols

- EnDat, Hiperface DSL, BiSS, HSR, PRP, 1588, plus list below

### **Protocols Supported**

### PRU-ICSS-G (10/100/1000Mbps)

#### Products

### New and Upgraded Features

- 1Gb Ethernet Speeds

- Retains FW Compatibility with previous PRU-ICSS versions

- New features enable Time Sensitive Networking (TSN), and 1Gb rates on Industrial Ethernet and redundancy protocols

### **Current Status**

- 3x PRU\_ICSS\_G inside AM65xx

- Supports legacy industrial Ethernet protocols from AM3/4/5

- TSN integration into PRU-ICSS\_G

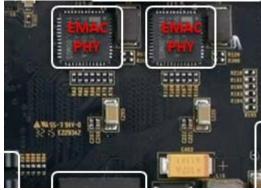

## **Processors with PRU-ICSS and EMAC/GMAC cont'd**

### Features

- 10/100/1000 Ethernet Speeds

- Switching fabric

- Capable of supporting standard Ethernet and <u>some</u> industrial Ethernet protocols

### **Protocols Supported**

## **Get Started Today!**

Visit links below for the latest documentation and product information

- <u>TIDA-00204 Reference Design Page</u>

- <u>TIDA-00299 Reference Design Page</u>

- <u>TIDA-00207 Design Page</u>

- DP83867 RGMII Linux Drivers

- Looking for a 10/100/1000 PHY Ethernet solution?

Refer to the AM5728 with DP83867 reference design

- <u>TIDA-010010 Reference Design Page</u>

© Copyright 2019 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com