# Dynamic Headroom Controller with Thermal Control Interface and Individual Channel Dimming Control

Check for Samples: LM3463

#### **FEATURES**

- Dynamic Headroom Control Output to Maximize Efficiency

- 6 Channels Current Regulated LED Driver

- High Precision Analog Dimming Control Interface

- 4 Individual PWM Dimming Control Input

- · Dimming Control via Digital Data Bus

- Built-In Maximum MOSFET Power Limiting Mechanism

- Allows Cascade Operation to Extend the Output Channels

- Fault Indicator Output

- Thermal Shutdown

- UVLO With Hysteresis

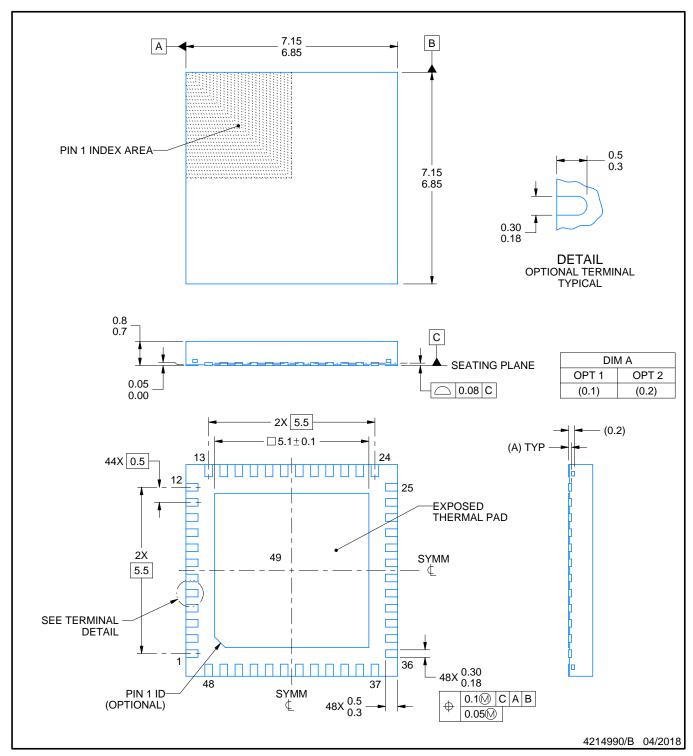

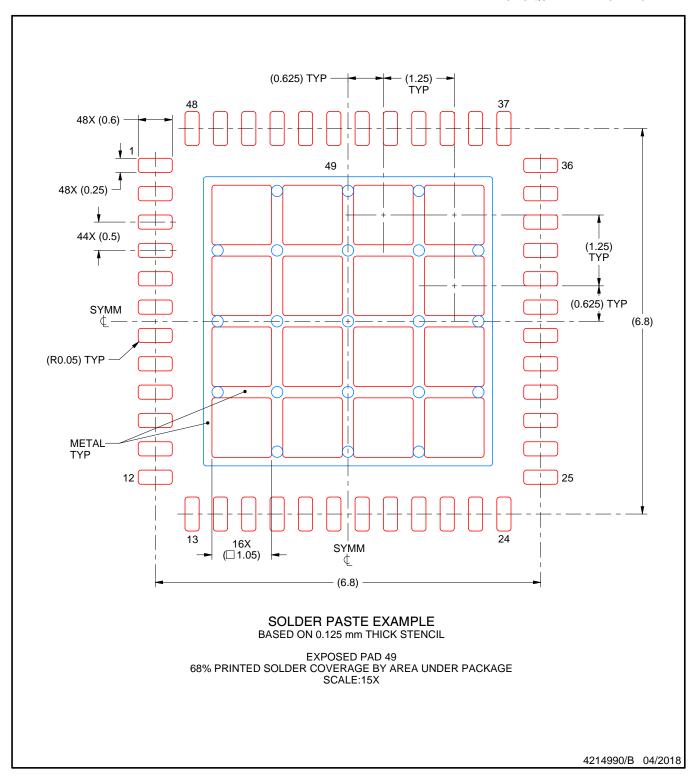

- 48L WQFN Package

#### **KEY SPECIFICATIONS**

- Wide supply voltage range (12V-95V)

- Thermal fold-back dimming control

- DHC regulates the lowest MOSFET drain voltage to 1V

#### **APPLICATIONS**

- Streetlights

- Solid State Lighting Solutions

#### DESCRIPTION

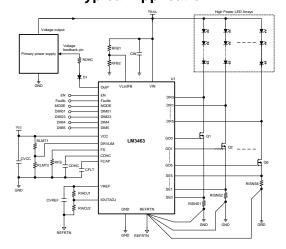

The LM3463 is a six channel linear LED driver with Dynamic Headroom Control (DHC) interface that is specialized for high power LED lighting applications. The variation of the output current of every output channel in the temperature range of -40°C to 125°C is well controlled to less than  $\pm 1\%$ . The output current of every channel is accurately matched to each other with less than  $\pm 1\%$  difference as well.

By interfacing the LM3463 to the output voltage feedback node of a switching power supply via the DHC interface, the system efficiency is optimized automatically. The dynamic headroom control circuit in the LM3463 minimizes power dissipation on the external MOSFETs by adjusting the output voltage of the primary switching power supply according to the changing forward voltage of the LEDs. Comprising the advantages of linear and switching converters, the LM3463 delivers accurately regulated current to LEDs while maximizing the system efficiency.

The dimming control interface of the LM3463 accepts both analog and PWM dimming control signals. The analog dimming control input controls the current of all LEDs while the PWM control inputs control the dimming duty of output channels individually.

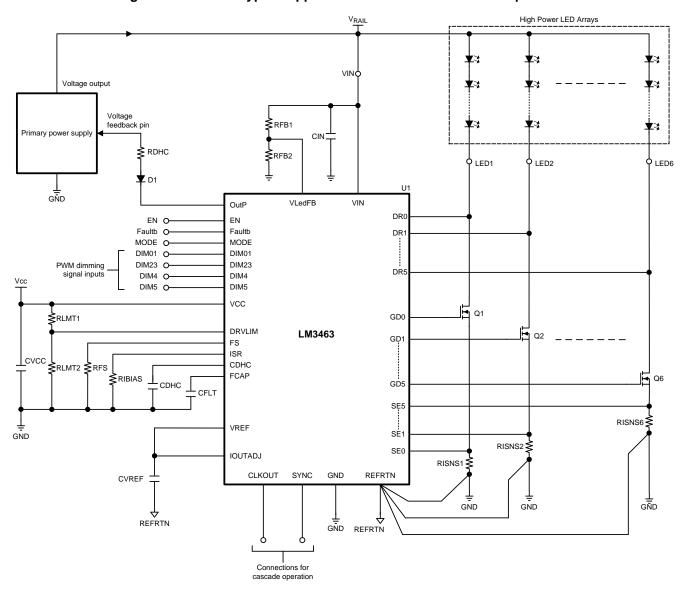

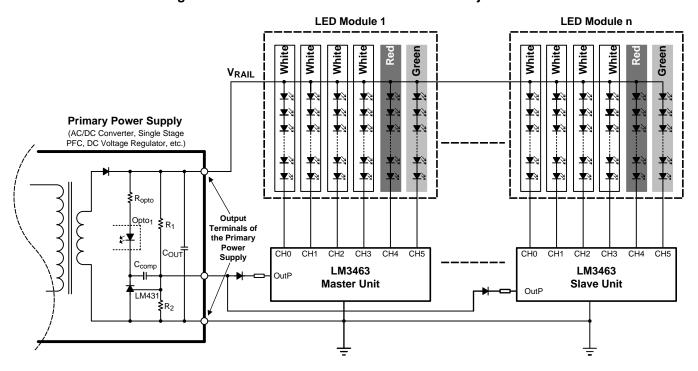

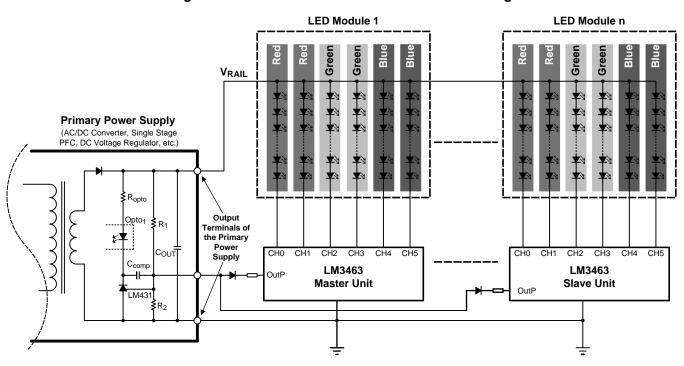

# **Typical Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **DESCRIPTION CONTINUED**

The LM3463 provides a sophisticated protection mechanism that secures high reliability and stability of the lighting system. The protection features include  $V_{\text{IN}}$  Under-Voltage–Lock-Out (UVLO), thermal shut-down, LED short / open circuit protection and MOSFET drain voltage limiting. The LED short circuit protection protects both the LED and MOSFETS by limiting the power dissipation on the MOSFETS.

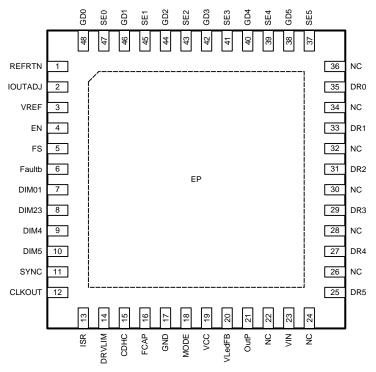

## **Connection Diagram**

Figure 1. TOP VIEW 48-Lead Plastic WQFN Package Number RHS

#### PIN DESCRIPTIONS

| Pin | Name                                    | Description                                                                                                | Application information                                                                                                                                                                                  |

|-----|-----------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | REFRTN                                  | 0V reference for small signal return paths                                                                 | This pin should connect to the end points of current sensing resistors with individual connections to ensure channel to channel current accuracy.                                                        |

| 2   | IOUTADJ                                 | Output current level adjust pin                                                                            | The current of all output channels (defined by R <sub>ISNSn</sub> ) reduces according to the voltage at this pin. This pin should connect to the VREF pin when output current reduction is not required. |

| 3   | VREF                                    | Precision reference voltage output                                                                         | This pin is the output of a precision reference voltage regulator. This pin must be bypassed through a ceramic capacitor to REFRTN.                                                                      |

|     |                                         | Enable input                                                                                               | Device enable pin with internal pull-up                                                                                                                                                                  |

| 4   | EN                                      |                                                                                                            | Enable: V <sub>EN</sub> = Floating                                                                                                                                                                       |

|     |                                         |                                                                                                            | Disable: V <sub>EN</sub> = GND                                                                                                                                                                           |

| 5   | Internal oscillator control or external | Frequency setting pin. Connect a resistor across this pin to GND to set the internal oscillator frequency. |                                                                                                                                                                                                          |

| 5   | FS                                      | clock input pin                                                                                            | The internal clock frequency can be defined by forcing an external clock signal to this pin.                                                                                                             |

| 6   | Faultb                                  | Fault indicator output                                                                                     | Fault indicator output. This pin is an open-drain output and is pulled low when an open circuit of LED string is identified.                                                                             |

Product Folder Links: LM3463

# PIN DESCRIPTIONS (continued)

| Pin | Name   | Description                                                                        | Application information                                                                                                                                                                                                                                                                                                                 |

|-----|--------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        | Multi-function input pin.                                                          | The function of this pin differs depending on the selected operation mode that sets by the MODE pin.                                                                                                                                                                                                                                    |

| 7   | DIM01  | Channel 0/1 PWM dimming control                                                    | Direct PWM mode: Apply a bi-level PWM signal (TTL logic high and low) to this pin to enable/disable ch0 and ch1. Apply logic high to this pin to enable channel 0 and 1.                                                                                                                                                                |

|     |        | Serial data input                                                                  | In serial interface mode, this pin is configured as the serial data input.                                                                                                                                                                                                                                                              |

|     |        | DC voltage dimming control                                                         | In DC interface mode, the voltage on this pin is converted into PWM dimming duty for channel 0 and 1.                                                                                                                                                                                                                                   |

|     |        | Multi-function input pin.                                                          | The function of this pin differs depending on the selected operation mode that sets by the MODE pin.                                                                                                                                                                                                                                    |

| 8   | DIM23  | Channel 2/3 PWM dimming control                                                    | Direct PWM mode: apply bi-level PWM signal (TTL logic high and low) to this pin to enable/disable ch2 and ch3. Apply a logic high to this pin to enable both channel 2 and 3.                                                                                                                                                           |

|     |        | Serial clock input                                                                 | In serial interface mode, this pin is configured as the serial clock signal input.                                                                                                                                                                                                                                                      |

|     |        | DC voltage dimming control                                                         | In DC interface mode, the voltage on this pin is converted into PWM dimming duty for channel 2 and 3.                                                                                                                                                                                                                                   |

|     |        | Multi-function input pin.                                                          | The function of this pin differs depending on the selected operation mode that sets by the MODE pin.                                                                                                                                                                                                                                    |

|     |        | Channel 4 dimming control                                                          | Direct PWM mode: apply bi-level PWM signal to this pin to enable/disable channel 4. Apply logic high to this pin to enable channel 4.                                                                                                                                                                                                   |

| 9   | DIM4   | Load data control pin                                                              | In serial interface mode, this pin is configured as load pulse input, pulling this pin low will latch the shifted-in data into internal register of the LM3463. This pin is pulled low if the requested load operation is not completed. User should check the status of this pin before writing data into the LM3463 through this pin. |

|     |        | DC voltage dimming control                                                         | In DC interface mode, the voltage on this pin is converted into PWM dimming duty for channel 4.                                                                                                                                                                                                                                         |

|     |        | Multi-function input pin.                                                          | The function of this pin differs depending on the selected operation mode that sets by the MODE pin.                                                                                                                                                                                                                                    |

| 10  | DIM5   | Channel 5 dimming control                                                          | Direct PWM mode: Apply a bi-level PWM signal (TTL logic high and low) to this pin to enable/disable channel 5. Apply a logic high to this pin to enable channel 5.                                                                                                                                                                      |

|     |        | Serial operation mode                                                              | This pin should connect to GND when serial operation mode is selected.                                                                                                                                                                                                                                                                  |

|     |        | DC voltage dimming control                                                         | In DC interface mode, the voltage on this pin is converted into PWM dimming duty for channel 5.                                                                                                                                                                                                                                         |

| 11  | SYNC   | Serial data output for cascade operation                                           | Serial control signal output pin for cascade operation. This signal synchronizes with the rising edge of the CLKOUT signal and carries information to the slave devices to turn on LEDs.                                                                                                                                                |

|     |        | Sync. pulse input in direct PWM mode                                               | This is a synchronization signal input pin for the slave device to perform LED pretest upon system startup.                                                                                                                                                                                                                             |

| 12  | CLKOUT | Dimming clock output for cascade operation / Sync pulse output for Direct PWM mode | Dimming clock output for cascade operation. The frequency at this pin equal to 1/2 of the internal clock or externally applied clock frequency.                                                                                                                                                                                         |

| 13  | ISR    | Start up current control pin                                                       | Connect a resistor from this pin to GND to set the additional bias current to the $C_{DHC}$ upon system startup.                                                                                                                                                                                                                        |

|     |        |                                                                                    | The voltage on this pin defines the threshold of the drain voltage of the external MOSFETs ( $V_{DRn}$ ) to begin output current reduction.                                                                                                                                                                                             |

| 14  | DRVLIM | MOSFET power limit setting input                                                   | As the $V_{DRn}$ exceeds $V_{DRVLIM}$ , the LED driving current reduces according to the increasing of $V_{DRn}$ at certain fixed rate. This function prevents the MOSFET from over-heating. The maximum power dissipation is limited to $V_{DRVLIM}$ * $I_{LED}$ (per ch.).                                                            |

| 15  | CDHC   | Dynamic headroom control time constant capacitor                                   | Connect a capacitor ( $C_{\text{DHC}}$ ) from this pin to ground to program the DHC loop response.                                                                                                                                                                                                                                      |

| 16  | FCAP   | Fault de-bounce capacitor                                                          | Connect a capacitor, $C_{\text{FLT}}$ from this pin to ground to program the fault debounce time.                                                                                                                                                                                                                                       |

| 17  | GND    | System ground                                                                      | This pin should connect to the system ground                                                                                                                                                                                                                                                                                            |

Copyright © 2012–2013, Texas Instruments Incorporated

# PIN DESCRIPTIONS (continued)

| Pin | Name   | Description                                              | Application information                                                                                                                                                                                 |

|-----|--------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        | эттем на             | Operation mode selection input pin. Bias this pin externally to set the                                                                                                                                 |

|     |        |                                                          | LM3463 in different operation mode.                                                                                                                                                                     |

| 18  | MODE   | Mode select input pin                                    | Direct PWM mode: V <sub>MODE</sub> = GND                                                                                                                                                                |

|     |        |                                                          | Serial interface mode: V <sub>MODE</sub> = No Connection                                                                                                                                                |

|     |        |                                                          | DC interface mode: V <sub>MODE</sub> = VCC                                                                                                                                                              |

| 19  | VCC    | Internal regulator output                                | Output terminal of the internal voltage regulator. This pin should be bypassed to GND through a 1uf ceramic capacitor.                                                                                  |

| 20  | VLedFB | Rail voltage detection input pin                         | This pin detects the output voltage of the primary power supply (V <sub>RAIL</sub> ). LEDs will be turned on when the voltage at this pin reaches 2.5V.                                                 |

|     |        |                                                          | Connect this pin to VCC to set a device as a slave.                                                                                                                                                     |

| 21  | OutP   | DHC output Driver                                        | This pin is an open drain output (current sink) which should connect to the output voltage feedback node of the primary power supply through a resistor and a diode to realize rail voltage adjustment. |

| 22  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 23  | VIN    | System supply                                            | Supply voltage input pin. This pin should be bypassed to GND using a 1uF ceramic capacitor.                                                                                                             |

| 24  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 25  | DR5    | Channel 5 drain voltage feedback input to facilitate DHC | Connect to the junction of the drain terminal of the external MOSFET and the cathode of the LED string. This pin is connected to the internal comparator to facilitate DHC.                             |

| 26  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 27  | DR4    | Channel 4 drain voltage feedback input to facilitate DHC | Connect to the junction of the drain terminal of the external MOSFET and the cathode of the LED string. This pin is connected to the internal comparator to facilitate DHC.                             |

| 28  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 29  | DR3    | Channel 3 drain voltage feedback input to facilitate DHC | Connect to the junction of the drain terminal of the external MOSFET and the cathode of the LED string. This pin is connected to the internal comparator to facilitate DHC.                             |

| 30  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 31  | DR2    | Channel 2 drain voltage feedback input to facilitate DHC | Connect to the junction of the drain terminal of the external MOSFET and the cathode of the LED string. This pin is connected to the internal comparator to facilitate DHC.                             |

| 32  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 33  | DR1    | Channel 1 drain voltage feedback input to facilitate DHC | Connect to the junction of the drain terminal of the external MOSFET and the cathode of the LED string. This pin is connected to the internal comparator to facilitate DHC.                             |

| 34  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 35  | DR0    | Channel 0 drain voltage feedback input to facilitate DHC | Connect to the junction of the drain terminal of the external MOSFET and the cathode of the LED string. Voltage on this pin is being fed to the internal comparator to facilitate DHC.                  |

| 36  | NC     |                                                          | No connection                                                                                                                                                                                           |

| 37  | SE5    | Channel 5 LED driver sense input pin                     | Connect to the junction of the source terminal of the external MOSFET and the sense resistor to facilitate current regulation for channel 5.                                                            |

| 38  | GD5    | channel 5 gate drive output pin                          | Gate driver output. Connect to the gate terminal of the external MOSFET.                                                                                                                                |

| 39  | SE4    | Channel 4 LED driver sense input pin                     | Connect to the junction of the source terminal of the external MOSFET and the sense resistor to facilitate current regulation for channel 4.                                                            |

| 40  | GD4    | channel 4 gate drive output pin                          | Gate driver output. Connect to the gate terminal of the external MOSFET.                                                                                                                                |

| 41  | SE3    | Channel 3 LED driver sense input pin                     | Connect to the junction of the source terminal of the external MOSFET and the sense resistor to facilitate current regulation for channel 3.                                                            |

| 42  | GD3    | channel 3 gate drive output pin                          | Gate driver output. Connect to the gate terminal of the external MOSFET.                                                                                                                                |

| 43  | SE2    | Channel 2 LED driver sense input pin                     | Connect to the junction of the source terminal of the external MOSFET and the sense resistor to facilitate current regulation for channel 2.                                                            |

| 44  | GD2    | channel 2 gate drive output pin                          | Gate driver output. Connect to the gate terminal of the external MOSFET.                                                                                                                                |

| 45  | SE1    | Channel 1 LED driver sense input pin                     | Connect to the junction of the source terminal of the external MOSFET and the sense resistor to facilitate current regulation for channel 1.                                                            |

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

# PIN DESCRIPTIONS (continued)

| Pin | Name | Description                          | Application information                                                                                                                                      |

|-----|------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46  | GD1  | channel 1 gate drive output pin      | Gate driver output. Connect to the gate terminal of the external MOSFET.                                                                                     |

| 47  | SE0  | Channel 0 LED driver sense input pin | Connect to the junction of the source terminal of the external MOSFET and the sense resistor to facilitate current regulation for channel 0.                 |

| 48  | GD0  | channel 0 gate drive output pin      | Gate driver output. Connect to the gate terminal of the external MOSFET.                                                                                     |

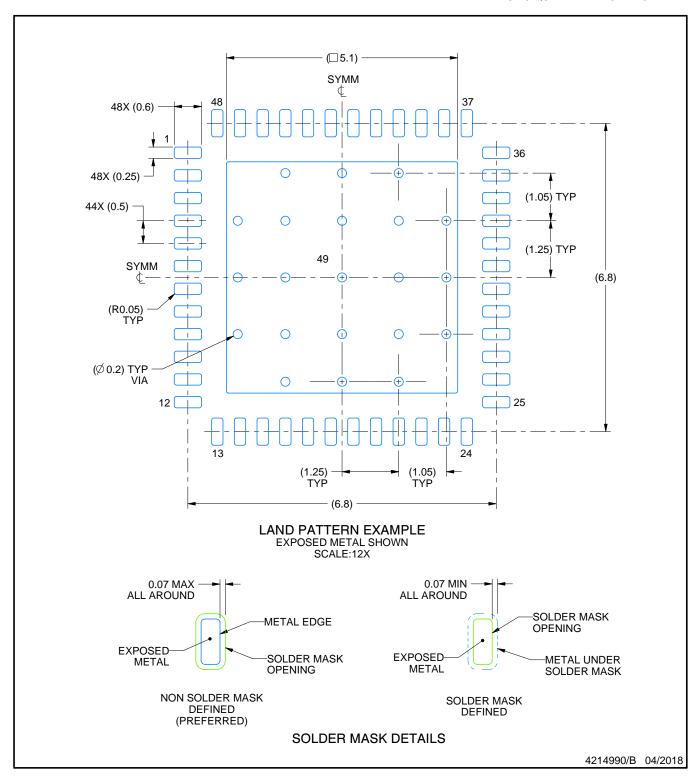

|     | EP   | Thermal Pad                          | Connect to the GND pin. The EP has no internal connection to ground and must connect to the GND pin externally. Place 9 vias from EP to copper ground plane. |

Product Folder Links: LM3463

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

|                                        | 1               |

|----------------------------------------|-----------------|

| VIN to GND                             | -0.3V to 100V   |

| DR0, DR1, DR2, DR3, DR4, DR5 to GND    | -0.3V to 100V   |

| EN                                     | -0.3V to 5.5V   |

| DRVLIM                                 | -0.3V to 6V     |

| Faultb                                 | -0.3V to 20V    |

| All other pins                         | -0.3V to 7V     |

| ESD Rating, Human Body Model (3)       | ±2 kV           |

| Storage Temperature                    | -65°C to +150°C |

| Junction Temperature (T <sub>J</sub> ) | -40°C to +125°C |

- (1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see the Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) Human Body Model, applicable std. JESD22-A114-C.

# **Operating Ratings**

| _ 1                                                  |                  |

|------------------------------------------------------|------------------|

| Supply Voltage Range (VIN)                           | 12V to 95V       |

| Junction Temperature Range (T <sub>J</sub> )         | -40°C to + 125°C |

| Thermal Resistance (θ <sub>JA</sub> )                | 24°C/W           |

| Thermal Resistance (θ <sub>JC</sub> ) <sup>(1)</sup> | 2.5°C/W          |

<sup>⊕&</sup>lt;sub>JC</sub> measurements are performed in general accordance with Mil-Std 883B, Method 1012.1 and utilize the copper heat sink technique. Copper Heat Sink @ 60°C.

#### **Electrical Characteristics**

Specification with standard type are for  $T_A = T_J = +25^{\circ}\text{C}$  only; limits in **boldface** type apply over the full Operating Junction Temperature  $(T_J)$  range. Minimum and Maximum are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = +25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{IN} = 48V$ .

| Symbol               | Parameter                          | Conditions                              | Min   | Тур   | Max   | Units |

|----------------------|------------------------------------|-----------------------------------------|-------|-------|-------|-------|

| Supply               | •                                  |                                         |       |       |       |       |

| I <sub>IN</sub>      | V <sub>IN</sub> Quiescent Current  | V <sub>EN</sub> pin floating            |       | 9.75  | 15    | mA    |

| I <sub>SD</sub>      | V <sub>IN</sub> Shut-Down Current  | V <sub>EN</sub> = 0V                    |       | 550   | 800   | μΑ    |

| VIN UVLO             |                                    |                                         |       |       |       |       |

| V <sub>IN-UVLO</sub> | V <sub>IN</sub> Turn-on Threshold  |                                         |       | 7.4   | 10    | V     |

|                      | V <sub>IN</sub> Turn-off Threshold |                                         | 4.5   | 7.1   |       | V     |

|                      | V <sub>IN</sub> UVLO Hysteresis    |                                         |       | 300   |       | mV    |

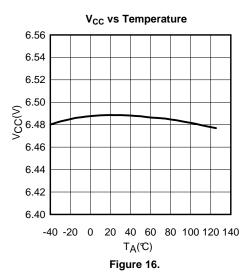

| VCC Regulator        |                                    |                                         |       |       |       |       |

| V <sub>CC</sub>      | V <sub>CC</sub> Regulated Voltage  | $C_{VCC} = 1 \mu F, I_{VCC} = 1 mA$     | 6.240 | 6.475 | 6.760 | V     |

|                      |                                    | I <sub>CC</sub> = 10 mA                 | 6.230 | 6.462 | 6.741 | V     |

| I <sub>VCC-LIM</sub> | V <sub>CC</sub> Current Limit      | V <sub>CC</sub> = 0V                    |       | 28    | 45    | mA    |

| V <sub>CC-UVLO</sub> | V <sub>CC</sub> Turn-on Threshold  |                                         |       | 4.5   | 4.7   | V     |

|                      | V <sub>CC</sub> Turn-off Threshold |                                         | 3.75  | 4.20  |       | V     |

|                      | V <sub>CC</sub> UVLO hysteresis    | V <sub>CC</sub> Decreasing              |       | 300   |       | mV    |

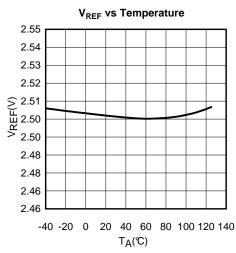

| Internal Refere      | nce Voltage Regulator              |                                         |       |       |       |       |

| V <sub>VREF</sub>    | Reference Voltage Regulator Output | C <sub>VREF</sub> = 0.47 μF, No Load    | 2.453 | 2.499 | 2.564 | V     |

|                      | Voltage                            | I <sub>VREF</sub> = 2mA                 | 2.443 | 2.496 | 2.545 | V     |

| I <sub>VREF-SC</sub> | VREF Pin Short-Circuit Current     | V <sub>VREF</sub> = V <sub>REFRTN</sub> | 7.0   | 8.2   | 10.5  | mA    |

Product Folder Links: LM3463

# **Electrical Characteristics (continued)**

Specification with standard type are for  $T_A = T_J = +25^{\circ}\text{C}$  only; limits in **boldface** type apply over the full Operating Junction Temperature  $(T_J)$  range. Minimum and Maximum are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = +25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{IN} = 48V$ .

| Symbol                             | Parameter                                      | Conditions                                                         | Min   | Тур   | Max   | Units |

|------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|-------|

| Dimming Control I                  | nterfaces                                      |                                                                    |       |       |       |       |

| Analog Mode                        |                                                |                                                                    |       |       |       |       |

| V <sub>DIMn-MAX</sub>              | DIMn Voltage at 100% Output Duty Cycle         | MODE = VCC                                                         |       | 5.65  |       | V     |

| V <sub>DIMn-MIN</sub>              | DIMn Voltage at 0% Output Duty Cycle           | MODE = VCC                                                         |       | 807   |       | mV    |

| V <sub>DIMn-001H</sub>             | DIMn Voltage at data code = 001h               | MODE = VCC                                                         |       | 826   |       | mV    |

| PWM Mode                           |                                                |                                                                    | Ш     |       | I     |       |

| V <sub>DIM-LED-ON</sub>            | DIMn Voltage Threshold at LED ON               | MODE = GND                                                         |       | 1.50  | 1.75  | V     |

| V <sub>DIM-LED-OFF</sub>           | DIMn Voltage Threshold at LED OFF              |                                                                    | 1.1   | 1.4   |       | V     |

| V <sub>DIM-LED-HYS</sub>           | DIMn Voltage Hysteresis at LED ON to OFF       |                                                                    |       | 100   |       | mV    |

| System Clock Gen                   | erator                                         |                                                                    |       |       |       |       |

| V <sub>FS</sub>                    | FS Pin Voltage                                 | FS Pin = Open                                                      | 1.173 | 1.235 | 1.297 | V     |

| I <sub>FS-SC</sub>                 | FS Pin Short-Circuit Current                   | V <sub>FS</sub> = 0V                                               |       | 110   | 140   | μΑ    |

| f <sub>OSC</sub>                   | System Clock Frequency                         | $R_{FS} = 14 \text{ k}\Omega$                                      | 0.90  | 1.00  | 1.15  | MHz   |

| Bus Interface Mod                  | е                                              |                                                                    |       |       |       |       |

| V <sub>SCLK-HIGH</sub> (DIM23)     | SCLK (Serial CLK) Logic High Threshold         | MODE = Hi-Z                                                        |       | 1.50  | 1.75  | V     |

| V <sub>SCLK-LOW</sub> (DIM23)      | SCLK (Serial CLK) Logic Low Threshold          | MODE = Hi-Z                                                        | 1.1   | 1.4   |       | V     |

| V <sub>SCLK-HYS</sub> (DIM23)      | SCLK (Serial CLK) Hysteresis                   | MODE = Hi-Z                                                        |       | 100   |       | mV    |

| V <sub>SDA-HIGH</sub> (DIM01)      | SDA (Serial Data) Logic High Threshold         | MODE = Hi-Z                                                        |       | 1.50  | 1.75  | V     |

| V <sub>SDA-LOW</sub> (DIM01)       | SDA (Serial Data) Logic Low Threshold          | MODE = Hi-Z                                                        | 1.1   | 1.4   |       | V     |

| V <sub>SDA-HYS</sub> (DIM01)       | SDA (Serial Data) Hysteresis                   | MODE = Hi-Z                                                        |       | 100   |       | mV    |

| Dynamic headroor                   | n Control                                      |                                                                    |       |       |       |       |

| $V_{DRn\text{-}DHC\text{-}STDEAY}$ | The lowest VDRn when DHC is under steady state | Measure at DRn pin                                                 |       | 0.95  |       | V     |

| $V_{VLedFB-TH}$                    | VLedFB Voltage Threshold for Turning LEDs ON   | V <sub>VLedFB</sub> Increasing                                     | 2.325 | 2.500 | 2.625 | V     |

| V <sub>VLedFB-HYS</sub>            | VLedFB Voltage Hysteresis                      | V <sub>VLedFB</sub> decreasing                                     |       | 1.21  |       | V     |

| V <sub>VLedFBEN-SLAVE</sub>        | VLedFB Pin Voltage Threshold for Slave Mode    | Measure at VLedFB pin                                              | 5.15  | 5.39  | 5.60  | V     |

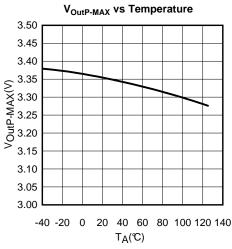

| $V_{OutP\text{-MAX}}$              | OutP Max. Output Voltage                       | $I_{OutP} = 1mA$<br>Current Sink<br>$V_{CDHC} = 0.5V$              | 2.90  | 3.10  | 3.25  | V     |

| V <sub>OutP-MIN</sub>              | OutP Min. Output Voltage                       | I <sub>OutP</sub> =1mA<br>Current Sink<br>V <sub>CDHC</sub> = 3.5V | 0.050 | 0.120 | 0.235 | V     |

| V <sub>ISR</sub>                   | ISR Pin Voltage                                | I <sub>ISR</sub> = 1μA<br>Current Sink to GND                      | 1.226 | 1.307 | 1.382 | V     |

|                                    |                                                | I <sub>ISR</sub> = 10μA<br>Current Sink to GND                     | 1.195 | 1.240 | 1.285 | V     |

|                                    |                                                | I <sub>ISR</sub> = 100μA<br>Current Sink to GND                    | 1.075 | 1.125 | 1.175 | V     |

| I <sub>CDHC-SOURCE</sub>           | CDHC Pin Max. Sourcing Current                 | Any V <sub>DRn</sub> < 0.9V                                        | 15    | 26    | 35    | μΑ    |

| I <sub>CDHC-SINK</sub>             | CDHC Pin Max. Sinking Current                  | Any V <sub>DRn</sub> > 0.9V                                        | 20    | 33    | 45    | μΑ    |

| R <sub>CDHC-SOURCE</sub>           | CDHC Pin Output Impedance                      | Sourcing current from CDHC pin                                     | 1.20  | 1.70  | 2.25  | МΩ    |

| R <sub>CDHC-SINK</sub>             | CDHC Pin Output Impedance                      | Sinking current from CDHC pin                                      | 0.7   | 1.1   | 1.4   | МΩ    |

| gm <sub>CDHC-OTA</sub>             | CDHC Pin OTA Transconductance                  | V <sub>DRn</sub> ≥ 0.9V                                            |       | 75    |       | μmho  |

|                                    |                                                | V <sub>DRn</sub> < 0.9V                                            |       | 17    |       | μmho  |

# **Electrical Characteristics (continued)**

Specification with standard type are for  $T_A = T_J = +25^{\circ}\text{C}$  only; limits in **boldface** type apply over the full Operating Junction Temperature  $(T_J)$  range. Minimum and Maximum are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = +25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{IN} = 48V$ .

| Symbol                        | Parameter                                                | Conditions                                   | Min  | Тур  | Max  | Units |

|-------------------------------|----------------------------------------------------------|----------------------------------------------|------|------|------|-------|

| LED Current Regu              | lator                                                    |                                              |      |      |      |       |

| $V_{\text{GDn-MAX}}$          | GDn Gate Driver Maximum Output Voltage                   | V <sub>SEn</sub> = 0V                        | 5.30 | 5.75 | 6.20 | V     |

| I <sub>GDn-MAX</sub>          | GDn Gate Driver Short Circuit Current                    | V <sub>GDn</sub> = 0V                        |      | 10   | 16   | mA    |

| I <sub>DRn-MAX</sub>          | DRn pin Maximum Input Current                            | V <sub>DRn</sub> = 80V                       | 35   | 50   | 65   | μΑ    |

| V <sub>SEn</sub>              | Output Current Sensing Reference                         | $V_{IOUTADJ} = V_{VREF}$                     | 190  | 200  | 210  | mV    |

|                               | Voltage w.r.t V <sub>REFRTN</sub>                        | V <sub>IOUTADJ</sub> = V <sub>VREF</sub> / 2 | 85   | 100  | 115  | mV    |

|                               |                                                          | $V_{IOUTADJ} = V_{REFRTN}$                   | 2.0  | 4.6  | 6.5  | mV    |

| Fault Detection an            | d Handling                                               |                                              |      |      |      |       |

| V <sub>SEn-LED-OPEN-FLT</sub> | LED Open Fault Detection Voltage<br>Threshold at SEn Pin | Measure at SEn pin                           |      | 43   |      | mV    |

| I <sub>SEn-LED-OPEN-FLT</sub> | LED Open Fault Detection Current<br>Threshold at SEn Pin | Measure at SEn pin                           | 15   | 22   | 30   | μΑ    |

| V <sub>DRn-LED-NORMAL</sub>   | LED Open Fault Detection Voltage<br>Threshold at DRn Pin | Measure at DRn pin                           |      | 330  |      | mV    |

| I <sub>FCAP-CHG</sub>         | Fault Cap. Charging Current                              | Fault = True                                 | 20   | 28   | 40   | μΑ    |

| V <sub>FCAP-FLT-TH</sub>      | FCAP Pin Fault Confirm Voltage<br>Threshold              | Measure at FCAP pin                          | 3.3  | 3.6  | 3.9  | V     |

| V <sub>FCAP-RST-TH</sub>      | FCAP Pin Fault Reset Voltage Threshold                   | Measure at FCAP pin                          | 85   | 157  | 230  | mV    |

| Device Enable                 |                                                          |                                              |      |      |      |       |

| V <sub>EN-ENABLE</sub>        | EN Pin Voltage Threshold for Device Enable               |                                              |      | 2.6  | 3.3  | ٧     |

| V <sub>EN-DISABLE</sub>       | EN Pin Voltage Threshold for Device Disable              |                                              | 1.9  | 2.5  |      | ٧     |

| V <sub>EN-HYS</sub>           | Device Enable Hysteresis                                 |                                              |      | 100  |      | mV    |

| Thermal Protection            | 1                                                        |                                              |      | •    | •    |       |

| T <sub>SD</sub>               | Thermal shutdown temperature                             | T <sub>J</sub> Rising                        |      | 165  |      | °C    |

| T <sub>SD-HYS</sub>           | Thermal shutdown temperature hysteresis                  | T <sub>J</sub> Falling                       |      | 20   |      | °C    |

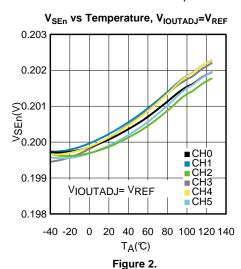

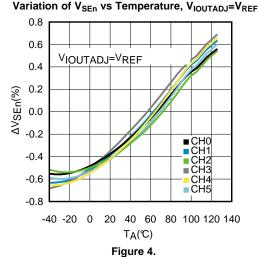

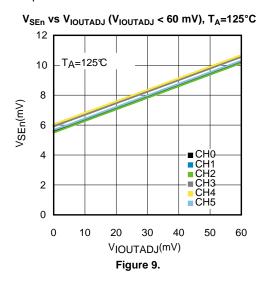

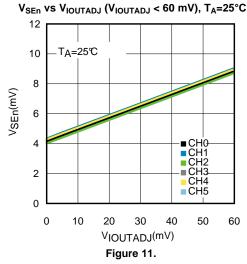

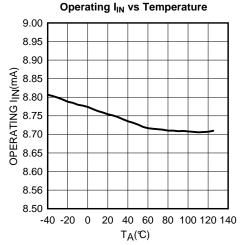

# **Typical Performance Characteristics**

All curves taken at  $V_{IN}$  = 48V with configuration in typical application for driving twelve power LEDs with six output channels active and 350 mA output current per channel.  $T_A$  = 25°C, unless otherwise specified.

n of V ... Tomoroustum V V

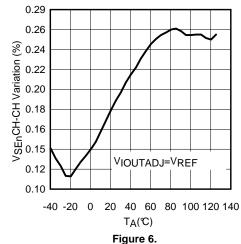

CH-CH Variation of V<sub>SEn</sub> vs Temperature, V<sub>IOUTADJ</sub>=V<sub>REF</sub>

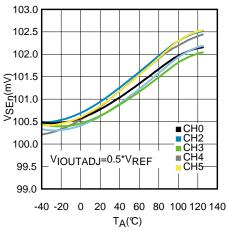

V<sub>SEn</sub> vs Temperature, V<sub>IOUTADJ</sub>=0.5 V<sub>REF</sub>

Figure 3.

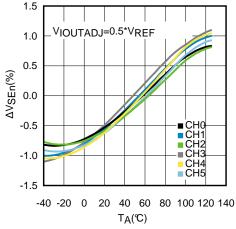

#### Variation of V<sub>SEn</sub> vs Temperature, V<sub>IOUTADJ</sub>=0.5 V<sub>REF</sub>

Figure 5.

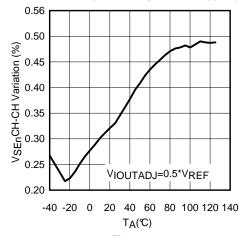

CH-CH Variation of V<sub>SEn</sub> vs Temperature, V<sub>IOUTADJ</sub>=0.5 V<sub>REF</sub>

Figure 7.

# **Typical Performance Characteristics (continued)**

All curves taken at  $V_{IN}$  = 48V with configuration in typical application for driving twelve power LEDs with six output channels active and 350 mA output current per channel.  $T_A$  = 25°C, unless otherwise specified.

# **Typical Performance Characteristics (continued)**

All curves taken at  $V_{IN}$  = 48V with configuration in typical application for driving twelve power LEDs with six output channels active and 350 mA output current per channel.  $T_A$  = 25°C, unless otherwise specified.

Figure 14.

Figure 15.

Figure 17.

Texas Instruments

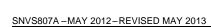

# **Block Diagram**

#### Overview

The LM3463 is a six channel linear current regulator which designed for LED lighting applications. The use of the Dynamic Headroom Control (DHC) method secures high system power efficiency and prolongs system operation lifetime by minimizing the power stress on critical components. The output currents of the LM3463 driver stage are regulated by six individual low-side current regulators.

The current regulators are accompanied by a high precision current sensing circuit. In order to ensure excellent current matching among output channels, the current sensing inputs are corresponding to a dedicated reference point, the REFRTN pin to insulate the ground potential differences due to trace resistances. With this current sensing circuit, the channel to channel output current difference is well controlled below ±10% when the output current is reduced (DC LED current reduction) to 5%.

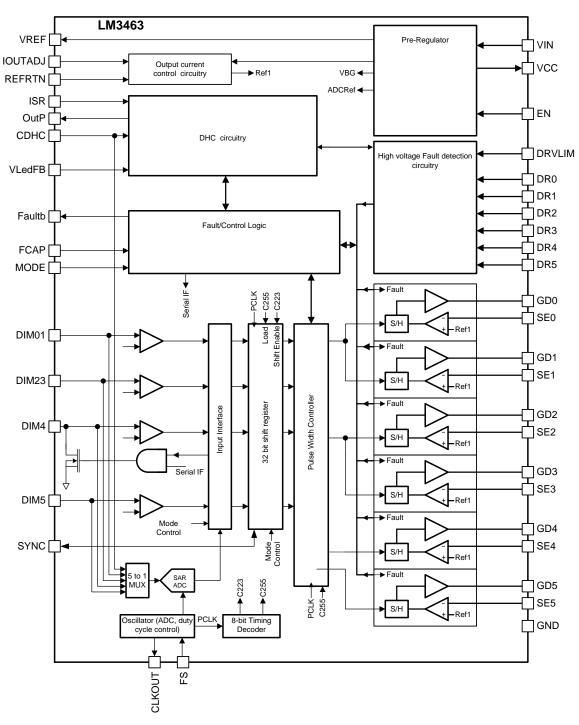

# **LED Current Regulators and Analog Dimming Control**

The LM3463 provides six individual linear current regulators to perform LED current regulation. Each current regulator includes an internal MOSFET driver and error amplifier and an external MOSFET and current sensing resistor. The output current of every output channel is defined by the value of an external current sensing resistor individually. The reference voltage of the regulators can be adjusted by changing the bias voltage at the IOUTADJ pin.

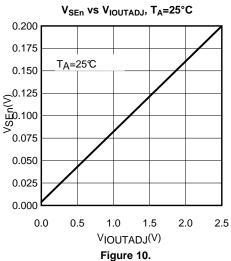

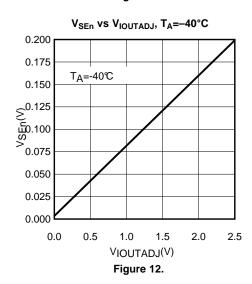

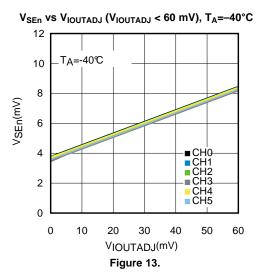

When analog dimming control applies, the output current of all channels reduces proportional to the voltage being applied to the IOUTADJ pin. Figure 18 shows the simplified block diagram of a current regulator.

Figure 18. Block diagram of a linear current regulator

Since the driving current of a LED string is determined by the resistance of the current sensing resistor  $R_{\text{ISNSn}}$  individually, every channel can have different output current by using different value of  $R_{\text{ISNSn}}$ . The LED current,  $I_{\text{OUTn}}$  is calculated using the following expression:

$$V_{SEn} = [(V_{IOUTADJ} \times 0.0782) + 4.3 \times 10^{-3}]$$

(1)

AND since:

$$I_{OUTn} = \left(\frac{V_{SEn}}{R_{ISNSn}}\right) A \tag{2}$$

Thus,

$$I_{OUTn} = \frac{[(V_{IOUTADJ} \times 0.0782) + 4.3 \times 10^{-3}]}{R_{ISNSn}}$$

(3)

The above equations apply when  $V_{IOUTADJ}$  is equal to or below  $V_{REF}$  (2.5V). Generally the  $V_{IOUTADJ}$  should not be set higher than  $V_{REF}$ . Applying a voltage high than  $V_{REF}$  to the IOUTADJ pin could result in inaccurate LED driving currents which fall out of the specification. Figure 19 shows the relationship of  $V_{IOUTADJ}$  and  $V_{SEn}$ .

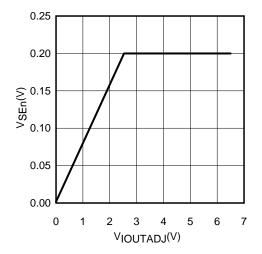

Figure 19. V<sub>SEn</sub> versus V<sub>IOUTADJ</sub>

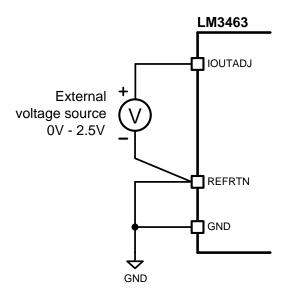

Since the analog dimming control interface is designed for slow brightness control only, the rate of change of the voltage at the IOUTADJ pin must not be higher than 1.25V/sec to allow good tracking of the output current and changing of the  $V_{IOUTADJ}$ . The voltage at the IOUTADJ pin can be provided by an external voltage source as shown in Figure 20.

Figure 20. Adjust V<sub>SEn</sub> by external voltage

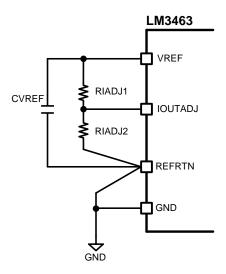

To secure high accuracy and linearity of dimming control, the voltage of the IOUTADJ pin can be provided by a voltage divider connecting across the VREF and REFRTN pins as shown in Figure 21.

Figure 21. Biasing IOUTADJ from VREF

# **V<sub>cc</sub>** Regulator

The  $V_{CC}$  regulator accepts an input voltage in the range of 12V to 95V from the VIN pin and delivers a 6.5V typical constant voltage at the VCC pin to provide power and bias voltages to the internal circuits. The VCC pin should be bypassed to ground by a low ESR capacitor across the VCC and GND pins. A 1uF 10V X7R capacitor is suggested.

The output current of the VCC regulator is limited to 20 mA which includes the biasing currents to the internal circuit. When using the VCC regulator to bias external circuits, it is suggested to sink no more than 10 mA from the VCC regulator to prevent over-heating of the device.

# **VREF Regulator**

The VREF regulator is used to provide precision reference voltage to internal circuits and the IOUTADJ pin. Other than providing bias voltage to the IOUTADJ pin, the VREF pin should not be used to provide power to external circuit. The VREF pin must be bypassed to ground by a low ESR capacitor across the VREF and RETRTN pins. A 0.47uF 10V X7R capacitor is suggested.

Figure 22. Individual connections to REFRTN

#### **REFRTN and GND**

The REFRTN pin is the reference point for the high precision and low noise internal circuits. The pins which referenced to the REFRTN are VREF, IOUTADJ, SE0, SE1, SE2, SE3, SE4 and SE5. To secure accurate current regulations, the current sensing resistors,  $R_{\rm ISNSn}$  should connect to the REFRTN pin directly using dedicated connections. And the REFRTN and GND pins should be connected together using dedicated connection as shown in Figure 22.

#### **Device Enable**

The LM3463 can be disabled by pulling the EN pin to ground. The EN pin is pulled up by an internal weak-pull-up circuit, thus the LM3463 is enabled by default. Pulling the EN pin to ground will reset all fault status. A system restart will be undertaken when the EN pin is released from pulling low.

#### Open Circuit of LED String(s)

When a LED string is disconnected, the LM3463 pulls the Faultb low to indicate a fault condition. The Faultb is an open-drain output pin. An open circuit of a LED string is detected when a  $V_{\text{SEn}}$  is below 43 mV and the  $V_{\text{DRn}}$  of the corresponding channel is below 300mV simultaneously. When the fault conditions are fulfilled, the LM3463 waits for a delay time to recognize whether there is a disconnected LED or not. If the conditions of open circuit of LED is sustained longer than the delay time, a real fault is recognized. The delay time for fault recognition is defined by the value of an external capacitor,  $C_{\text{FLT}}$ , and governed by the following equation:

$$t_{\text{FLT-RECOG}} = \left(\frac{3.62 \text{V} \times \text{C}_{\text{FLT}}}{28.1 \,\mu\text{A}}\right) \text{second}$$

(4)

The fault indication can be reset by either applying a falling edge to the EN pin or performing a system repowering.

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

#### **System Clock Generator**

The LM3463 includes an internal clock generator which is used to provide clock signal to the internal digital circuits. The clock frequency at the CLKOUT pin is equal to 1/2 of the frequency of the internal system clock generator. The system clock generator governs the rate of operation of the following functions:

- PWM dimming frequency in Serial Interface Mode

- · PWM dimming frequency in DC Interface Mode

- Clock frequency in cascade operation (CLKOUT pin)

The system clock frequency is defined by the value of an external resistor, R<sub>FS</sub> following the equation:

$$f_{\text{CLKOUT}} = \left[ \frac{15.44 \times 10^6}{R_{\text{FS}} + 548.6} + 10.08 \right] \text{kHz}$$

(5)

| Operation Mode        | CLKOUT Freq. | Dimming Freq.      | R <sub>FS</sub> |

|-----------------------|--------------|--------------------|-----------------|

| Serial Interface Mode | 125 kHz      | 488. 3Hz           | 125 kΩ          |

| DC Interface Mode     | 625 kHz      | 488.3Hz            | 62.2 kΩ         |

| Direct PWM Mode       | 625 kHz      | Virtually no limit | 62.2 kΩ         |

#### **Dynamic Headroom Control (DHC)**

The Dynamic Headroom Control (DHC) is a control method which aimed at minimizing the voltage drops on the linear regulators to optimize system efficiency. The DHC circuit inside the LM3463 controls the output voltage of the primary power supply ( $V_{RAIL}$ ) until the voltage at any drain voltage sensing pin ( $V_{DRn}$ ) equals 1V. The LM3463 interacts with the primary power supply through the OutP pin in a slow manner which determined by the capacitor,  $C_{DHC}$ . Generally, the value of the  $C_{DHC}$  defines the frequency response of the LM3463. The higher the capacitance of the  $C_{DHC}$ , the lower the frequency response of the DHC loop, and vice versa. Since the  $V_{RAIL}$  is controlled by the LM3463 via the DHC loop, the response of the LM3463 driver stage must be set one decade lower than the generic response of the primary power supply to secure stable operation.

The cut-off frequency of the DHC loop is governed by the following equation:

$$f_{C(LM3463)} = \left(\frac{1}{2\Pi \times CDHC \times R_{CDHC-SOURCE}}\right) Hz$$

(6)

Practically, the frequency response of the primary power supply might not be easily identified (e.g. off-the-shelf AC/DC power supply). For the situations that the primary power supply has an unknown frequency response, it is suggested to use a 2.2 uF 10V X7R capacitor for CDHC as an initial value and decrease the value of the  $C_{DHC}$  to increase the response of the whole system as needed.

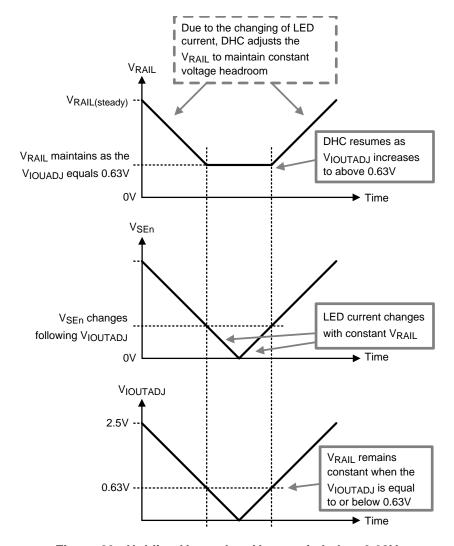

#### **Holding V<sub>RAIL</sub> In Analog Dimming Control**

Due to the V-I characteristic of the LED, the forward voltage of the LED strings decreases when the forward current is decreased. In order to compensate the rising of the voltage drop on the linear regulators when performing analog dimming control (due to the reduction of LED forward voltages), the DHC circuit in the LM3463 reduces the rail voltage ( $V_{RAIL}$ ) to maintain minimum voltage headroom (i.e. minimum  $V_{DRn}$ ).

In order to ensure good response of analog dimming control, the  $V_{RAIL}$  is maintained at a constant level to provide sufficient voltage headroom when the output currents are adjusted to a very low level. When the voltage at the IOUTADJ pin is decreased from certain level to below 0.63V, the DHC circuit stops to react to the changing of  $V_{DRn}$  and maintains the  $V_{RAIL}$  at the level while  $V_{IOUTADJ}$  equals 0.63V. DHC resumes when the  $V_{IOUTADJ}$  is increased to above 0.63V. Figure 23 shows the relationship of the  $V_{RAIL}$ ,  $V_{SEn}$  and  $V_{IOUTADJ}$ .

Product Folder Links: *LM3463*

Figure 23. Holding V<sub>RAIL</sub> when V<sub>IOUTADJ</sub> is below 0.63V

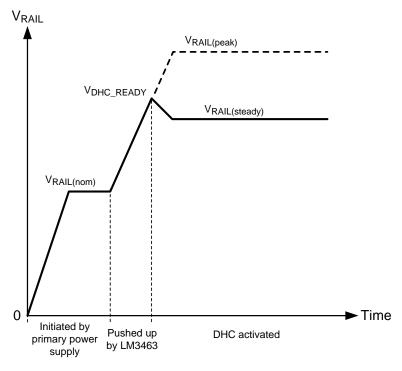

#### System Startup

When the LM3463 is powered, the internal Operational Transconductance Amplifier (OTA) charges the capacitor  $C_{DHC}$  through the CDHC pin. As the voltage at the CDHC pin increases, the voltage at the OutP pin starts to reduce from  $V_{CC}$ . When the voltage of the OutP pin falls below  $V_{FB} + 0.7V$ , the OutP pin sinks current from the  $V_{FB}$  node and eventually pulls up the output voltage of the primary power supply ( $V_{RAIL}$ ). As the  $V_{RAIL}$  reaches  $V_{DHC\_READY}$ , the LM3463 performs a test to identify the status of the LED strings (short / open circuit of LED strings). The  $V_{DHC\_REDAY}$  is defined by an external voltage divider which consists of  $R_{FB1}$  and  $R_{FB2}$ . The  $V_{DHC\_READY}$  is calculated following the equation:

$$V_{DHC\_READY} = \left(\frac{RFB1 + RFB2}{RFB2}\right) \times 2.5V$$

(7)

After the test is completed, the LM3463 turns on the LED strings with regulated output currents. At the moment that the LM3463 turns the LEDs on, the OutP pin stops sinking current from the  $V_{FB}$  node and in turn  $V_{RAIL}$  slews down. Along with the decreasing of  $V_{RAIL}$ , the voltage at the  $V_{DRn}$  pins falls to approach 1V. When a  $V_{DRn}$  is decreased to 1V, the DHC loop enters a steady state to maintain the lowest  $V_{DRn}$  to 1V average at a slow manner defined by  $C_{DHC}$ . Figure 24 presents the changes of  $V_{RAIL}$  from system power up to DHC loop enters steady state.

Figure 24. Changes of V<sub>RAIL</sub> during system startup

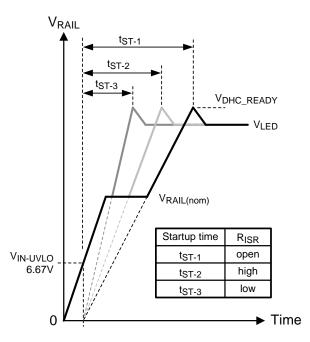

# **Shortening System Startup Time**

The system startup time can be shortened by sinking current from the ISR pin to ground through a resistor,  $R_{ISR}$ . The lower resistance the  $R_{ISR}$  carries, the shorter time the system startup takes. Sinking current from the ISR pin increases the charging current to the capacitor,  $C_{DHC}$  and eventually increases the rate of the increasing of  $V_{RAIL}$  during startup ( $V_{RAIL}$  ramps up from  $V_{RAIL(nom)}$  to  $V_{DHC\_READY}$ ). Figure 25 shows how the system startup time is shortened by using different value of  $R_{ISR}$ .

Figure 25. Setting different startup time using different R<sub>ISR</sub>

Generally, the system startup time  $t_{ST}$  is the longest when the ISR pin is left open ( $t_{ST-1}$ ). The amount of the decreasing of the startup time is inversely proportional to the current being drawn from the ISR pin, thus determined by the value of the resistor,  $R_{ISR}$ . The rate of decreasing of the startup time is governed by the following equation.

$$t_{ST} = \left[\frac{1}{\left(1 + \frac{170503}{R_{ISR}}\right)}\right] \times t_{ST-1}$$

(8)

The practical startup time varies according to the settings of the  $V_{DHC\_READY}$ ,  $V_{FB}$ ,  $C_{DHC}$  and  $R_{ISR}$  with respect to the following equations.

$$t_{ST} = \left[ \frac{3.6V - V_{OutP}}{\left( 7.33 \,\mu A + \frac{1.25V}{R_{ISR}} \right)} \right] \times C_{CDHC} \text{ in sec.}$$

(9)

where

$$V_{\text{OutP}} = \left[ V_{\text{FB}} - 0.6V - R_{\text{DHC}} \times \left( \frac{V_{\text{DHC-READY}} - V_{\text{FB}}}{R_1} - \frac{V_{\text{FB}}}{R_2} \right) \right]$$

(10)

Sinking higher than 100  $\mu$ A from the ISR pin could damage the device. The value of the R<sub>ISR</sub> should be no lower than 13 k $\Omega$  to prevent potential damages.

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

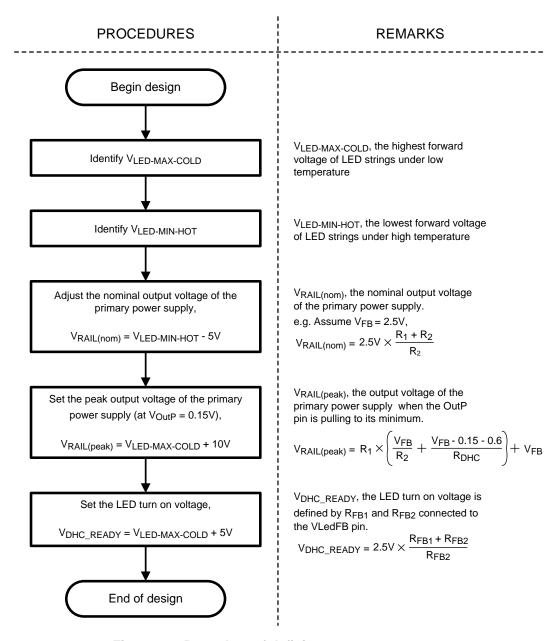

Figure 26. Procedure of defining startup parameters

# Setting the R<sub>DHC</sub> and V<sub>RAIL</sub>

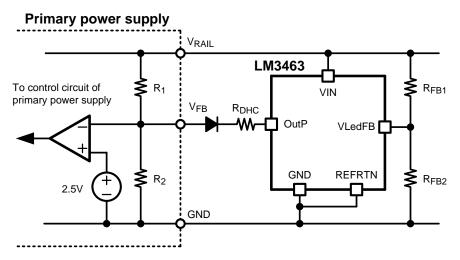

Prior to defining the parameters for the operations in steady state, the value of the  $R_{DHC}$  and different levels of the supply rail voltage ( $V_{RAIL}$ ) during system startup must be determined. Figure 26 illustrates the procedures of determining the value of the  $R_{DHC}$  and voltage levels of the  $V_{RAIL(nom)}$ ,  $V_{RAIL(peak)}$  and  $V_{DHC\_READY}$ .

In Figure 26, the  $V_{\text{LED-MAX-COLD}}$  and  $V_{\text{LED-MIN-HOT}}$  are the maximum and minimum forward voltages of the LED strings under the required lowest and highest operation temperatures respectively. In order to ensure all the LED string are supplied with adequate forward current when turning on the LEDs, the  $V_{\text{DHC\_READY}}$  must be set higher than the  $V_{\text{LED-MAX-COLD}}$ . For most applications, the  $V_{\text{DHC\_READY}}$  can be set 5 V higher than the  $V_{\text{LED-MAX-COLD}}$ .

In order to reserve voltage headroom to perform DHC under high operation temperature, the nominal output voltage of the primary power supply must be set lower than the  $V_{LED-MIN-HOT}$ . For most applications, the  $V_{RAIL(nom)}$  can be set 5 V lower than the  $V_{LED-MIN-HOT}$ . Figure 27 shows an example connection diagram of interfacing the LM3463 to a power supply of 2.5V feedback reference voltage.

Figure 27. Connecting the LM3463 to a power supply

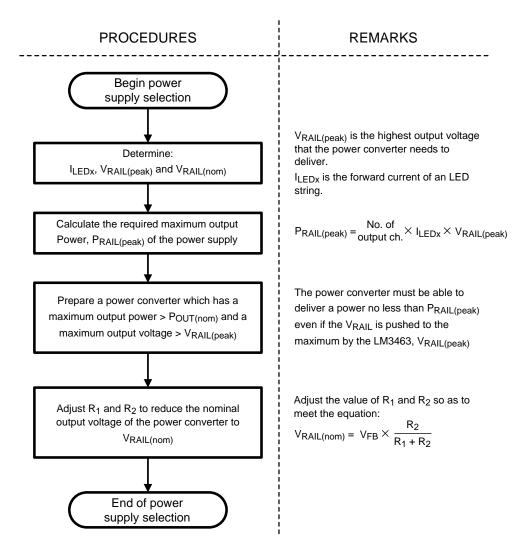

Figure 28. Procedures of selecting the primary power supply

#### **Choosing the proper Primary Power Supply**

If the primary power supply is an off-the-shelf power converter, it is essential to make certain that the power converter is able to withstand the  $V_{RAIL(peak)}$ . In order to allow DHC, the nominal output voltage of the primary power supply needs to be adjusted to below  $V_{LED-MIN-HOT}$  as well. The suggested procedures for selecting the proper power supply are as shown in Figure 28.

#### Selection of External MOSFET

The selection of external MOSFET is dependent on the highest current and the highest voltage that could be applied to the drain terminal of the MOSFET. Generally, the Drain-to-Source breakdown voltage ( $V_{DSS}$ ) and the continuous drain current ( $I_D$ ) of the external MOSFET must be higher than the defined peak supply rail voltage ( $V_{RAIL(peak)}$ ) and the maximum output LED current ( $I_{OUTn}$ ) respectively.

# **Testing LEDs at System Startup**

As  $V_{RAIL}$  increases to  $V_{DHC\_READY}$ , the voltage at the VLedFB pin equals 2.5V. When the voltage at the VLedFB pin rises to 2.5V, the LM3463 sinks 100  $\mu$ A through every LED strings from the supply rail into the DRn pins for certain period of time to determine the status of the LED strings. The time for checking LED strings is defined by the value of the external capacitor,  $C_{FLT}$  and is governed by the following equation:

$$t_{LED-TEST} = \left(\frac{3.62V \times C_{FLT}}{28.1 \,\mu\text{A}}\right) \text{second}$$

(11)

If the voltage at any DRn pin is detected lower than 350 mV in the LED test period, that particular output channel will be disabled and excluded from the DHC loop. All disabled output channels will remain in OFF state until a system restarting is undertaken. The LED test performs only once after the voltage at VLedFB pin hits 2.5V. The disabled channel can be re-enabled by pulling the EN pin to GND for 10 ms (issuing a system restart) or repowering the entire system.

#### **MOSFET Power Dissipation Limit**

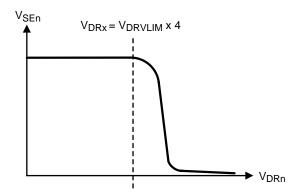

In order to protect the MOSFETs from thermal break down when a short circuit of the LED sting(s) is encountered, the LM3463 reduces the output current according to the increment of the drain voltage of the MOSFET ( $V_{DRn}$ ) when the drain voltage exceeds a certain preset threshold voltage to limit the power dissipation on the MOSFETs. This threshold voltage is defined by the voltage being applied to the DRVLIM pin,  $V_{DRVLIM}$  and is roughly four times the voltage of the  $V_{DRVLIM}$ . For example, if the desired drain threshold voltage to perform output current reduction is 16V, the DRVLIM pin voltage should be biased to 4V. Figure 29 shows the relation between  $V_{SEn}$ ,  $V_{DRn}$  and  $V_{DRVLIM}$ .

Figure 29.  $V_{SEn}$  reduces as  $V_{DRn}$  exceeds  $V_{DRVLIM}$  x4

#### **Dimming Mode Control**

The LM3463 provides three modes of PWM dimming control. The three modes are: Direct PWM dimming mode, Serial interface mode and DC interface mode. Selection of the mode of dimming mode is made by leaving the MODE pin open or connecting the MODE pin to GND or VCC. Regardless of the selection of the mode of PWM dimming control, the output channels 0 and 1 are controlled commonly by the signal at the DIM01 pin and the output channels 2 and 3 are controlled commonly by the PWM signal at the DIM23 pin. The dimming duty of the channel 4 and 5 are controlled by the signals on DIM4 and DIM5 pins respectively.

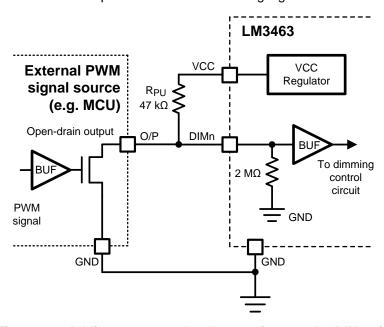

The DIM01, DIM23, DIM4 and DIM5 pins are pulled down by an internal 2 M $\Omega$  weak pull-downs to prevent the pins from floating. Thus the dimming control input pins are default to 'LED OFF' state and need external pulled up resistors when the pins are connected to open collector/drain signal sources. Figure 30 shows a suggested circuit for connecting the LM3463 to an open collector/drain dimming signal sources.

Figure 30. Adding an external pull-up resistor to the DIMn pin

#### **Direct PWM Dimming Mode**

Connecting the MODE pin to ground enables direct PWM dimming mode. Every dimming control pin (DIM01 to DIM5) in direct PWM control mode accepts active high TTL logic level signal. In direct PWM dimming mode, the six output channels are separated into four individual groups to accept external PWM dimming signals. The configuration of output channels are as listed in the following table:

| Group A | CH0 and CH1, controlled by DIM01 pin |

|---------|--------------------------------------|

| Group B | CH2 and CH3, controlled by DIM23 pin |

| Group C | CH4, controlled by DIM4 pin          |

| Group D | CH5, controlled by DIM5 pin          |

In order to secure accurate current regulation, the pull-up time of every dimming control input must not be shorter than 8  $\mu$ s. If a 256 level (8-bit resolution) brightness control is needed, the PWM dimming frequency should be no higher than 488Hz.

#### **Serial Interface Mode**

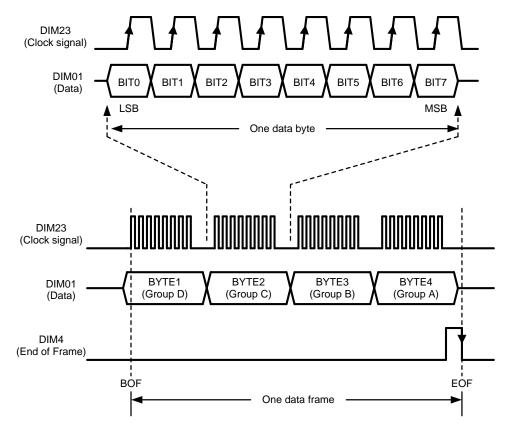

Leaving MODE pin floating enables serial interface mode. In serial interface mode, the DIM01, DIM23 and DIM4 pins are used together as a serial data interface to accept external dimming control data frames serially. The following table presents the functions of the DIM01, DIM23 and DIM4 pins in serial interface mode:

| DIM01 | Serial data packet input (8-bit packet size)            |  |

|-------|---------------------------------------------------------|--|

| DIM23 | Clock signal input for data bit latching                |  |

| DIM4  | End Of Frame (EOF) signal input for data packet loading |  |

The DIM5 pin is not used in this mode and should connect to GND. Every data frame contains four 8-bit wide data byte for PWM dimming control. Every data byte controls the PWM dimming duty of its corresponding output channel(s): A hexadecimal 000h gives 0% dimming duty; a hexadecimal 0FFh gives 100% dimming duty. Respectively, the first byte being loaded into the LM3463 controls the dimming duty of CH0 and CH1, the second byte controls the dimming duty of CH2 and CH3, the third byte controls the dimming duty of CH4 and the forth byte controls the dimming duty of CH5.

In serial interface mode, the six output channels are separated into four individual groups as listed in the following table:

| Group A | CH0 and CH1, controlled by the first byte  |

|---------|--------------------------------------------|

| Group B | CH2 and CH3, controlled by the second byte |

| Group C | CH4, controlled by the third byte          |

| Group D | controlled by the forth byte               |

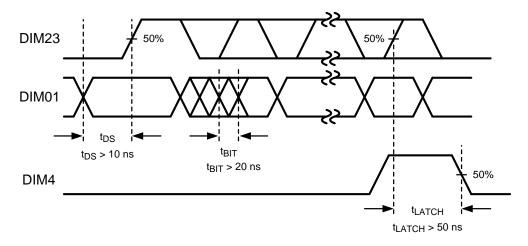

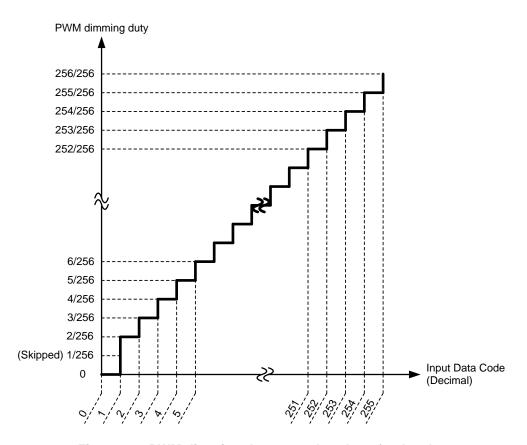

A data bit is latched into the LM3463 by applying a rising edge to the DIM02 pin. After clocking 32 bits (4 data bytes) into the LM3463, a falling edge should be applied to the DIM4 pin to indicate an EOF and load data bytes from data buffer to output channels accordingly. Figure 31 shows the serial input waveforms to the LM3463 to facilitate in serial interface mode. Figure 32 shows the timing parameters of the serial data interface. The PWM dimming duty in the serial interface mode is governed by the following equation:

$$D_{SERIAL-DIM} = \left(\frac{\text{data byte value} + 1}{256}\right) \times 100\%$$

(12)

The PWM dimming duty at decimal data codes 01 (001h) and 02 (002h) are rounded up to 2/256. Thus the minimum dimming duty in the serial interface mode is 2/256 or 0.781%. Figure 33 shows the relationship of the PWM dimming duty and the code value of a data byte in the serial interface mode. The PWM dimming frequency in serial interface mode is defined by the system clock of the LM3463. The dimming frequency in the serial interface mode is equal to the system clock frequency divided by 256 which follows the equation below:

$$f_{\text{SERIAL-DIM}} = \frac{f_{\text{CLKOUT}}}{256} = \left[ \frac{15.44 \times 10^6}{R_{\text{FS}} + 548.6} + 10.08 \right] \times \frac{1}{256}$$

(13)

In order to achieve a 256 level (8-bit resolution) brightness control, the minimum on time of every channel  $(1/(f_{SERIAL-DIM}*256))$  should be no shorter than 8us, thus a dimming frequency of 488Hz is suggested to use.

Figure 31. Input waveform to the LM3463 in serial interface mode

Figure 32. Timing parameters of the serial data interface

Figure 33. PWM dimming duty vs code value of a data byte

#### **DC Interface Mode**

Connecting the MODE pin to VCC enables DC interface mode. In this mode the LM3463 converts the voltage on the dimming signal input pins into PWM dimming duty to the corresponding output channels. The six output channels are separated into four individual groups to accept external PWM dimming signals as listed in the following table:

| Group A | CH0 and CH1, controlled by the voltage at DIM01 pin |

|---------|-----------------------------------------------------|

| Group B | CH2 and CH3, controlled by the voltage at DIM23 pin |

| Group C | CH4, controlled by the voltage at DIM4 pin          |

| Group D | CH5, controlled by the voltage at DIM5 pin          |

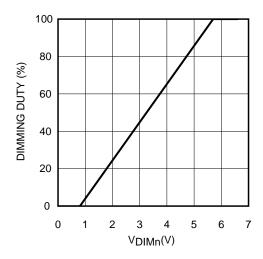

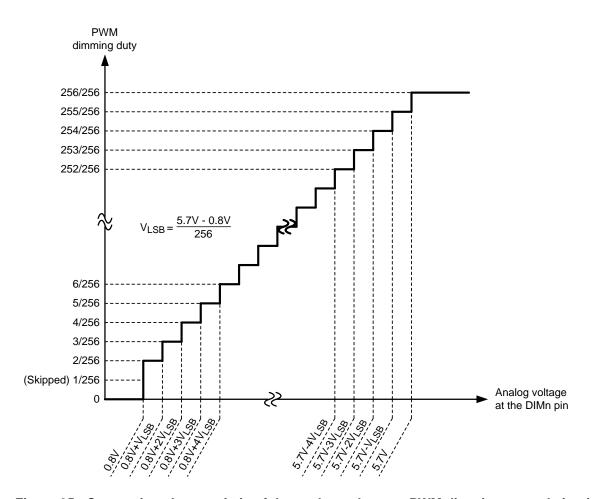

In DC interface mode, the DIM01, DIM23, DIM4 and DIM5 pins accept DC voltages in the range of 0.8V to 5.7V to facilitate PWM dimming control. The voltage at the DIMn pins ( $V_{DIMn}$ ) and the PWM dimming duty in the DC interface mode ( $D_{DC-DIM}$ ) are governed by the following equation. Figure 34 shows the correlation of  $V_{DIMn}$  and  $D_{DC-DIM}$ . The conversion characteristic is shown in Figure 35.

$$D_{DC-DIM} = [(V_{DIMn} - 0.8V) \times 20.4082]\%$$

where

•

$$0.8V < V_{DIMn} < 5.7V$$

(14)

The PWM dimming frequency in the DC interface mode is defined by the system clock of the LM3463. The dimming frequency in the DC interface mode is equal to the system clock frequency divided by 1280 which follows the equation below:

$$f_{\text{DC-DIM}} = \frac{f_{\text{CLKOUT}}}{256} = \left[ \frac{15.44 \times 10^6}{R_{\text{FS}} + 548.6} + 10.08 \right] \times \frac{1}{256}$$

(15)

In order to achieve a 256 level (8–bit resolution) brightness control, the minimum on time of every channel  $(1/(f_{SERIAL-DIM}*256))$  should be no shorter than 8 us, thus a dimming frequency of 488Hz is suggested to use.

The LM3463 samples the analog voltage at the DIMn pins and updates the dimming duty of each output channel at a rate of 1280 system clock cycle (1280/f<sub>CLKOUT</sub>). In order to ensure correct conversion of analog voltage to PWM dimming duty, the slew rate of the analog voltage for dimming control is limited the following equation:

$$\frac{dV_{\text{DIMn(DC-DIM)}}}{dt} = < V_{\text{LSB}} \times \frac{f_{\text{CLKOUT}}}{1280}$$

(16)

Figure 34. Dimming Duty vs VDIMn in DC interface mode

8 Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

Figure 35. Conversion characteristic of the analog voltage to PWM dimming control circuit

#### **Using Less than Six Output Channels**

If less than 6 output channels are needed, the unused output channel(s) of the LM3463 can be disabled by not installing the external MOSFET and current sensing resistor. The drain voltage sensing pin (DRn), gate driver output pin (GDn) and current sensing input pin (SEn) of a disabled channel must be left floating to secure proper operation. The output channel(s) which has no external MOSFET and current sensing resistor installed is disabled and excluded from DHC loop at system startup while the  $V_{RAIL}$  reaches  $V_{DHC\_READY}$ .

A total of five output channels of the LM3463 can be disabled. The channel 0 must be in use regardless of the number of disabled channel. This feature also applies in cascade operation.

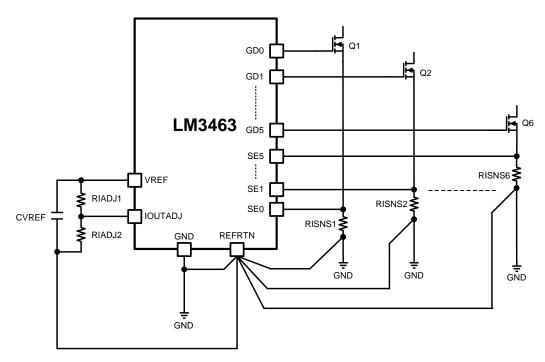

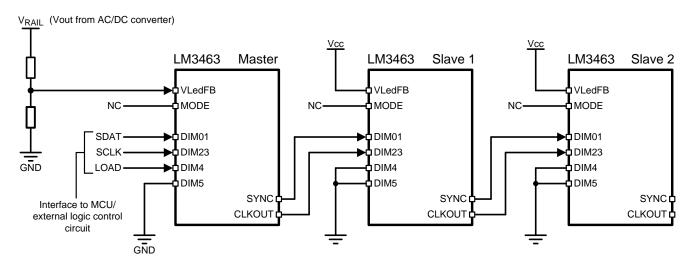

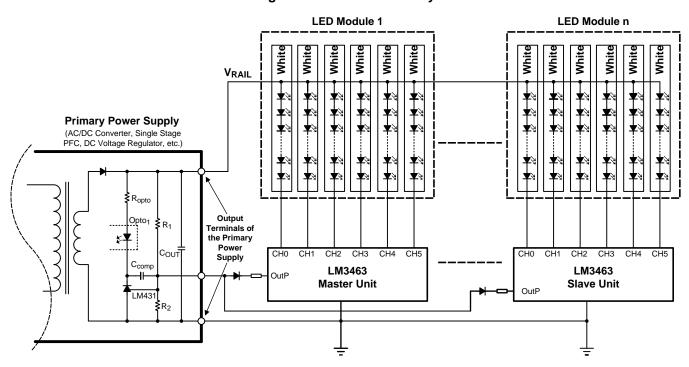

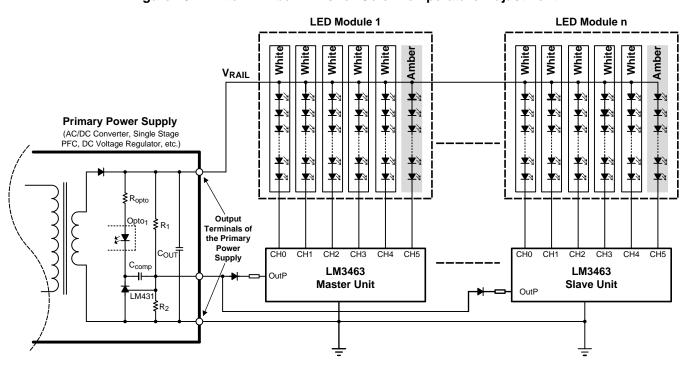

# Cascading of LM3463

For the applications that require more than six output channels, two or more pieces of LM3463 can be cascaded to expand the number of output channel. Dimming control is allowed in cascade operation. The connection diagrams for cascade operation in different modes of dimming control are as shown in Figure 36.

#### Serial interface mode in cascade operation

In the serial interface mode, the master LM3463 accepts external data frames through the serial data interface which consists of the DIM01, DIM23 and DIM4 pins and passes the frames to the following slave LM3463 through its serial data output interface (SYNC and CLKOUT pins). Every slave unit shifts data in and out bit by bit to its following slave unit.

Copyright © 2012–2013, Texas Instruments Incorporated

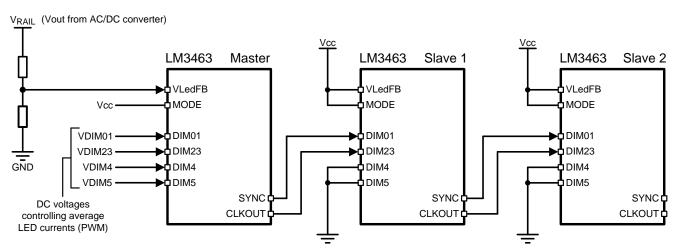

#### DC interface mode in cascade operation

In the DC interface mode, the master unit accepts four individual analog dimming control signals from external signal sources (via the DIM01, DIM23, DIM4 and DIM5 pins) and encodes the analog signals into 8-bit serial dimming control signals. The master LM3463 passes the encoded dimming control signals serially to the following slave unit through its serial data output interface (SYNC and CLKOUT pins). Every slave unit shifts data in and out bit by bit to its following slave unit.

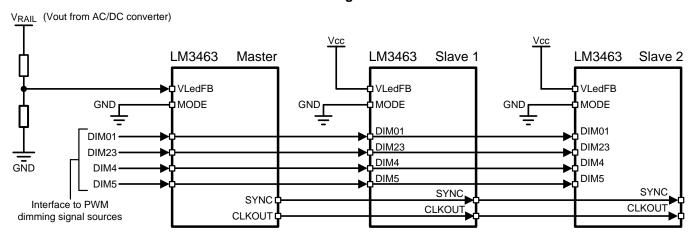

# Direct PWM dimming mode in cascade operation

In the Direct PWM Dimming mode, the master and slave units share the PWM dimming control signals at the DIM01, DIM23, DIM4 and DIM5 pin to facilitate dimming control. In this mode, the SYNC and CLKOUT of all slave units should be connected to the SYNC and CLKOUT pin of the master unit accordingly to perform startup synchronization. Since the dimming control signal inputs of all the LM3464 are connected in parallel to share the control signals, it is essential to ensure the signal source is strong enough to drive all the LM3463 in parallel.

#### **Serial Data Interface**

# **DC Voltage Dimming Control Interface**

#### **Direct PWM Diming Control Interface**

Figure 36. Connect diagram for cascade operations in different modes of dimming control

Product Folder Links: LM3463

#### **APPLICATION EXAMPLES**

Figure 37. LM3463 typical application circuit for stand alone operation

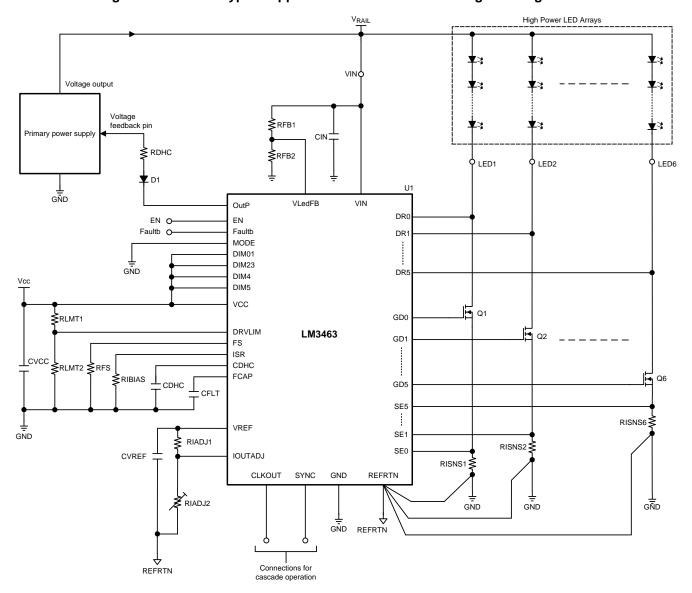

Figure 38. LM3463 typical application circuit for true analog dimming control

Figure 39. White LEDs Only

Figure 40. White + Amber LEDs for Color Temperature Adjustment

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated