# LM5125-Q1, Wide-VIN, Dual-Phase, Automotive, Boost Controller With VOUT Tracking

# **1** Features

- AEC-Q100 qualified for automotive applications

Temperature grade 1: T<sub>A</sub> = -40°C to +125°C

- Functional Safety-Capable

- Documentation available to aid functional safety system design

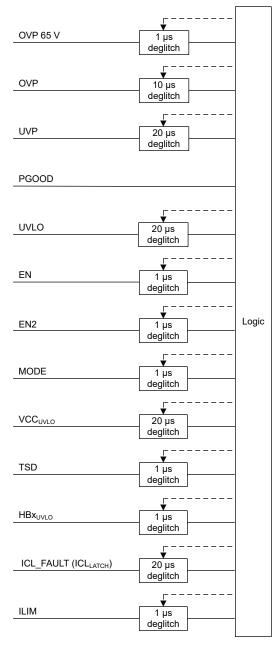

- Input voltage 4.5V to 42V

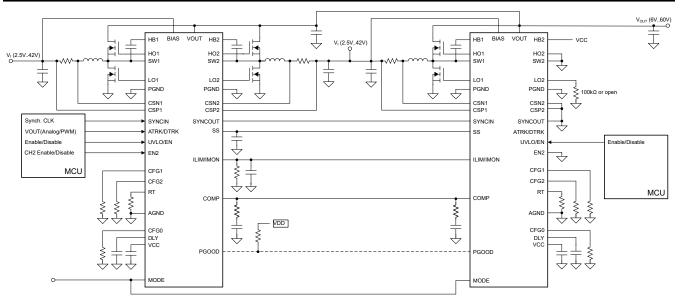

- Minimum 2.5V for  $V_{(BIAS)} \ge 4.5V$  or  $V_{OUT} \ge 6V$

- Output Voltage 6V to 60V

- 2% accuracy, internal feedback resistors

- Bypass operation for V<sub>I</sub> > V<sub>OUT</sub>

- Dynamic output voltage tracking

- Digital PWM tracking (DTRK)

- Analog tracking (ATRK)

- Overvoltage protection (64V, 50V, 35V, 28.5V)

- Low shutdown I<sub>Q</sub> of 2µA typ. (5µA maximum)

- Low operating I<sub>Q</sub> of 1.4mÅ typ. (2mA maximum)

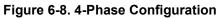

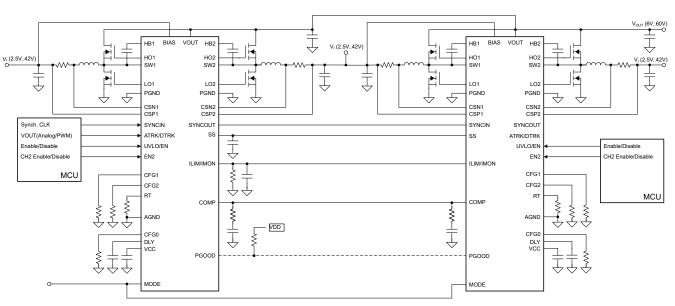

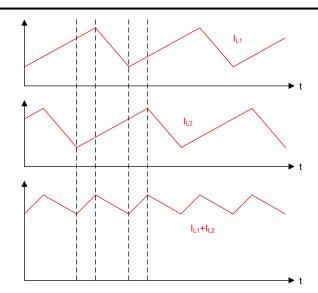

- Stacking with interleaved multiphase operation

- Up to 4-phases without external clock

- Switching frequency from 100kHz to 2.2MHz

- Synchronization to external clock (SYNCIN)

- Dynamically selectable switching modes (FPWM, diode emulation)

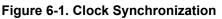

- Spread spectrum (DRSS)

- Selectable dead time (18ns to 200ns)

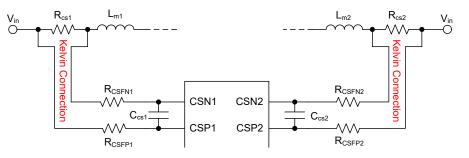

- · Current sense resistor or DCR sensing

- Average inductor current monitor

- Average input current limit

- Programmable current limit

- Selectable delay time

- Power-good indicator

- Programmable V<sub>I</sub> undervoltage lockout (UVLO)

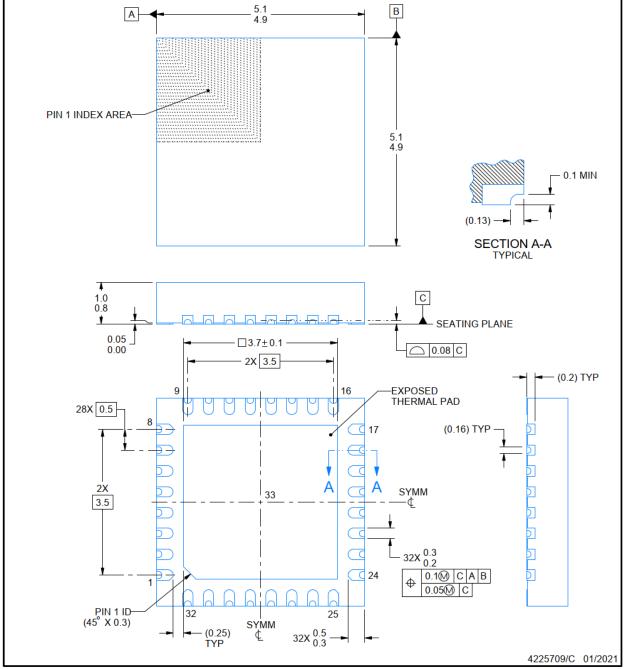

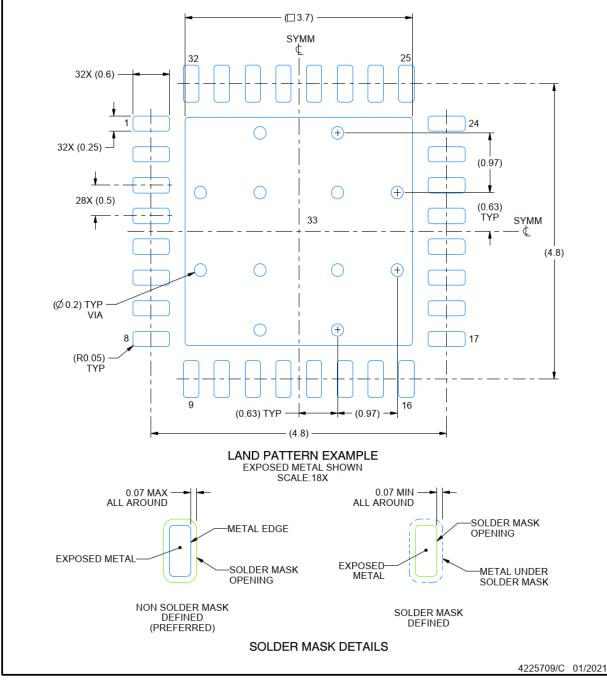

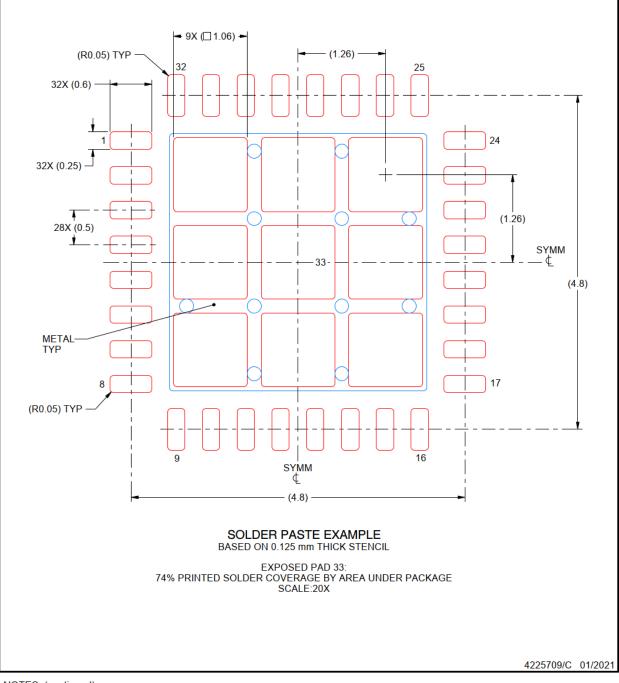

- Lead-less VQFN-32 package with wettable flanks

# 2 Applications

- High-end audio power supply

- Voltage stabilizer module

- Start-stop application

# **3 Description**

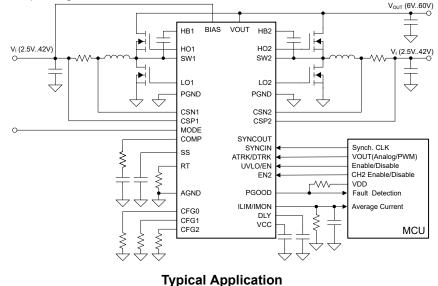

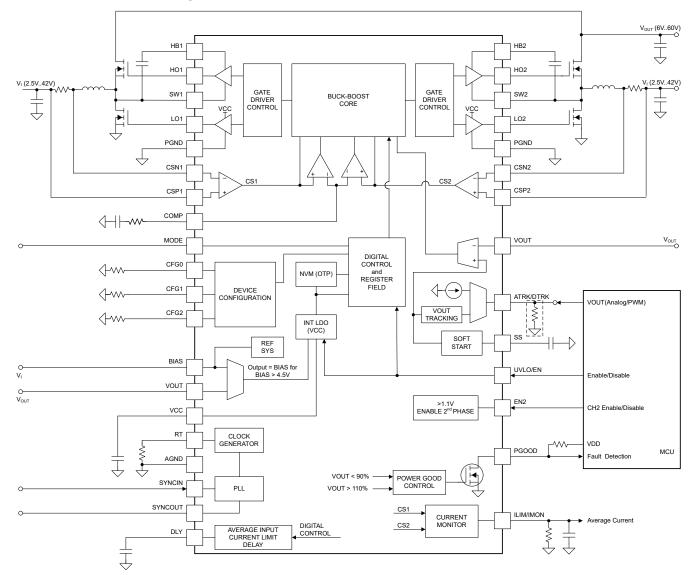

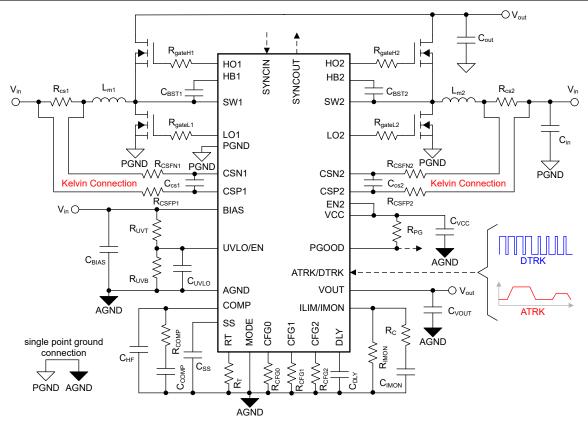

The LM5125-Q1 is a stackable, multiphase, synchronous, boost controller. The device provides a regulated output voltage for lower or equal input voltage also supporting  $V_I$  to  $V_{OUT}$  bypass mode to save power. Two devices can be stacked with or without external clock.

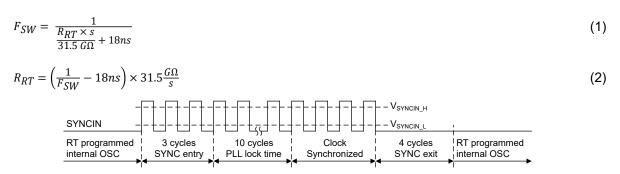

$V_{OUT}$  can be dynamically programmed using the digital or analog ATRK/DTRK function.  $V_1$  can be as low as 2.5V after start-up as the internal VCC supply is automatically switched from  $V_{BIAS}$  to  $V_{OUT}$  for  $V_{BIAS}$  < 4.5V. The fixed switching frequency is set between 100kHz and 2.2MHz through a resistor on the RT pin or the SYNCIN clock. The switching modes, FPWM, or diode emulation can be changed during operation.

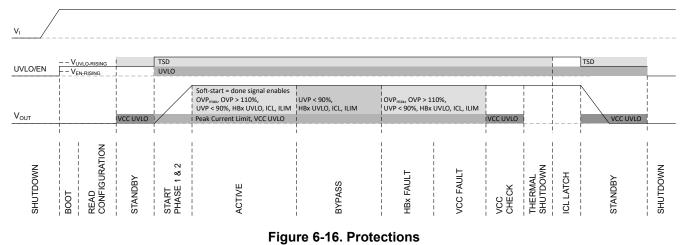

The implemented protections peak current limit, average input current limit, average inductor current monitor, over and undervoltage protection, or the thermal shutdown protect the device and the application.

### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| LM5125-Q1   | RHB (VQFN, 32)         | 5mm × 5mm                   |

(1) For more information, see Section 10.

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

# **Table of Contents**

| 1 Features<br>2 Applications<br>3 Description | 1              |

|-----------------------------------------------|----------------|

| 4 Pin Configuration and Functions             |                |

| 5 Specifications                              | <mark>5</mark> |

| 5.1 Absolute Maximum Ratings                  | <mark>5</mark> |

| 5.2 ESD Ratings                               | 5              |

| 5.3 Recommended Operating Conditions          |                |

| 5.4 Thermal Information                       | <mark>6</mark> |

| 5.5 Electrical Characteristics                | 6              |

| 5.6 Timing Requirements                       | 11             |

| 6 Detailed Description                        | 12             |

| 6.1 Overview                                  |                |

| 6.2 Functional Block Diagram                  | 13             |

| 6.3 Feature Description.                      |                |

| 6.4 Device Functional Modes                   |                |

|                                               |                |

| 7 | Application and Implementation                      | 29   |

|---|-----------------------------------------------------|------|

|   | 7.1 Application Information                         |      |

|   | 7.2 Typical Application                             |      |

|   | 7.3 Power Supply Recommendations                    |      |

|   | 7.4 Layout                                          | . 47 |

| 8 | Device and Documentation Support                    |      |

|   | 8.1 Documentation Support                           |      |

|   | 8.2 Receiving Notification of Documentation Updates |      |

|   | 8.3 Support Resources                               |      |

|   | 8.4 Trademarks                                      |      |

|   | 8.5 Electrostatic Discharge Caution                 |      |

|   | 8.6 Glossary                                        |      |

| 9 | Revision History                                    |      |

|   | 0 Mechanical, Packaging, and Orderable              |      |

|   | Information                                         | 49   |

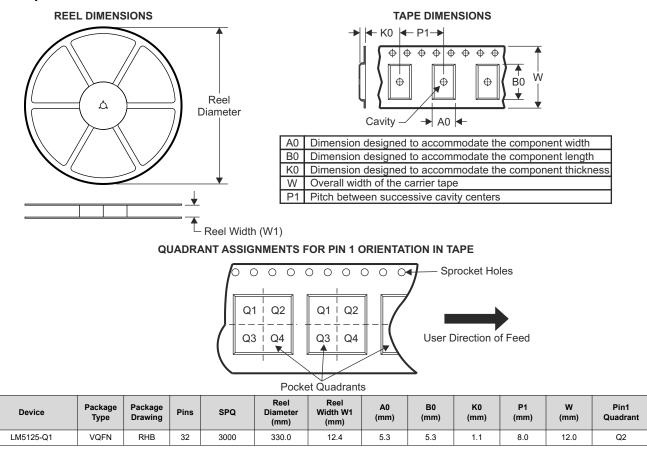

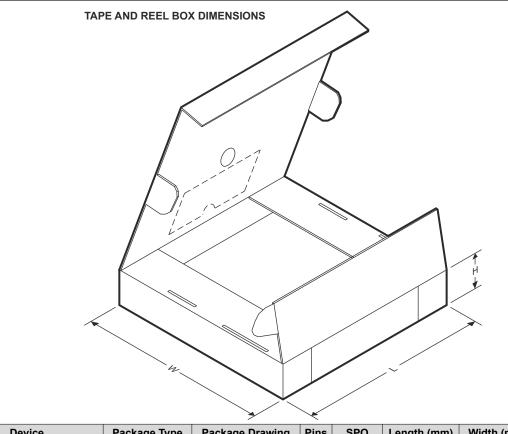

|   | 10.1 Tape and Reel Information                      |      |

**ADVANCE INFORMATION**

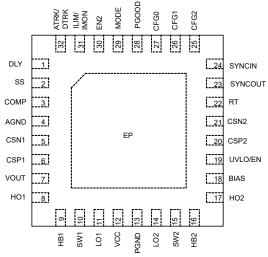

# **4** Pin Configuration and Functions

Figure 4-1. LM5125-Q1 RHB Package, VQFN 32 Pin (Top View)

#### Table 4-1. Pin Functions

| PIN  | l . | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                    |  |  |

|------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | NO. |                     | DESCRIPTION                                                                                                                                                                                                                    |  |  |

| DLY  | 1   | 0                   | Average input current limit delay setting pin. A capacitor from DLY to AGND sets the delay from when $V_{IMON}$ reaches 1V until the average input current limit is enabled.                                                   |  |  |

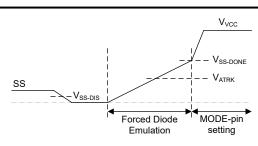

| SS   | 2   | 0                   | Soft-start time programming pin. An external capacitor and an internal current source set the ramp rate of the internal error amplifier reference during soft start. The device forces diode emulation during soft-start time. |  |  |

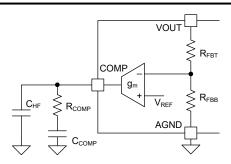

| COMP | 3   | 0                   | Output of the internal transconductance error amplifier. Connect the loop compensation components between the pin and AGND.                                                                                                    |  |  |

| AGND | 4   | G                   | Analog ground pin. Connect to the analog ground plane through a wide and short path.                                                                                                                                           |  |  |

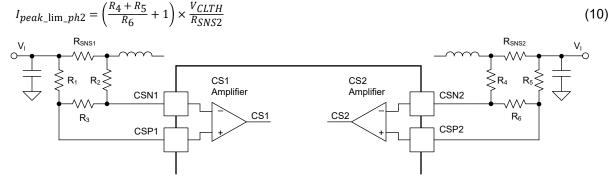

| CSN1 | 5   | I                   | Current sense amplifier input of phase 1. The pin operates as the negative input pin.                                                                                                                                          |  |  |

| CSP1 | 6   | I                   | Current sense amplifier input of phase 1. The pin operates as the positive input pin. Input to the internal undervoltage lockout for the input voltage.                                                                        |  |  |

| VOUT | 7   | I                   | Output voltage sensing pin. An internal feedback resistor voltage divider is connected f the pin to AGND. Connect a $0.1\mu$ F local VOUT capacitor from the pin to ground.                                                    |  |  |

| HO1  | 8   | 0                   | High-side gate driver output for phase 1. Connect directly to the gate of the high-side N-channel MOSFET through a short, low inductance path.                                                                                 |  |  |

| HB1  | 9   | Р                   | High-side driver supply for bootstrap gate drive for phase 1. Boot diode is internally connected from VCC to the pin. Connect a $0.1\mu$ F capacitor between the pin and SW1.                                                  |  |  |

| SW1  | 10  | Р                   | Switching node connection for phase 1. Connect directly to the source of the phase 1 high-side N-channel MOSFET.                                                                                                               |  |  |

| LO1  | 11  | 0                   | Low-side gate driver output for phase 1. Connect directly to the gate of the low-side N-channel MOSFET through a short, low inductance path.                                                                                   |  |  |

| VCC  | 12  | Р                   | Output of the internal VCC regulator and supply voltage input of the internal MOSFET drivers. Connect a $10\mu$ F capacitor between the pin and PGND.                                                                          |  |  |

| PGND | 13  | G                   | Power ground connection pin for low-side gate drivers and VCC bias supply.                                                                                                                                                     |  |  |

| LO2  | 14  | 0                   | Low-side gate driver output for phase 2. Connect directly to the gate of the low-side N-channel MOSFET through a short, low inductance path.                                                                                   |  |  |

| SW2  | 15  | Р                   | Switching node connection for phase 2. Connect directly to the source of the phase 2 high-side N-channel MOSFET.                                                                                                               |  |  |

| HB2  | 16  | Р                   | High-side driver supply for bootstrap gate drive for phase 2. Boot diode is internally connected from VCC to the pin. Connect a $0.1\mu$ F capacitor between the pin and SW2.                                                  |  |  |

#### Table 4-1. Pin Functions (continued)

| PI        | N   |                     |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                            |  |

| HO2       | 17  | 0                   | High-side gate driver output for phase 2. Connect directly to the gate of the high-side N-channel MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                         |  |

| BIAS      | 18  | Р                   | Supply voltage input to the VCC regulator. Connect a $1\mu F$ local BIAS capacitor from the pin to ground.                                                                                                                                                                                                                                                                                             |  |

| UVLO/EN   | 19  | I                   | Undervoltage lockout programming pin. The converter start-up and shutdown levels can be programmed by connecting this pin to the supply voltage through a resistor divider. If greater than $V_{\text{UVLO-RISING}}$ , phase 1 is enabled.                                                                                                                                                             |  |

| CSP2      | 20  | I                   | Current sense amplifier input of phase 2. The pin operates as the positive input pin.                                                                                                                                                                                                                                                                                                                  |  |

| CSN2      | 21  | I                   | Current sense amplifier input of phase 2. The pin operates as the negative input pin.                                                                                                                                                                                                                                                                                                                  |  |

| RT        | 22  | 0                   | Switching frequency setting pin. The switching frequency is programmed by a single resistor between the pin and AGND. Switching frequency is dynamically programmable during operation.                                                                                                                                                                                                                |  |

| SYNCOUT   | 23  | 0                   | Clock output pin. SYNCOUT provides a phase shifted clock output, set by the CFG2.pin. SYNCOUT pin can be left floating when not used.                                                                                                                                                                                                                                                                  |  |

| SYNCIN    | 24  | I                   | External clock synchronization pin. Input for an external clock that overrides the free-<br>running internal oscillator. Connect the SYNCIN pin to ground when not used.                                                                                                                                                                                                                               |  |

| CFG2      | 25  | I/O                 | Device configuration pin. Sets if the device is configured as single, primary or second                                                                                                                                                                                                                                                                                                                |  |

| CFG1      | 26  | I                   | Device configuration pin. Sets the overvoltage protection level, spread spectrum mode, PGOOD configuration and 120% peak current limit latch off.                                                                                                                                                                                                                                                      |  |

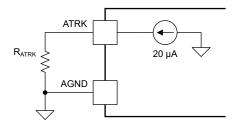

| CFG0      | 27  | I                   | Device configuration pin. Sets the dead time and enables the 20µA ATRK current.                                                                                                                                                                                                                                                                                                                        |  |

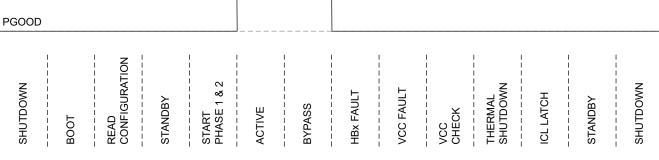

| PGOOD     | 28  | 0                   | Power-good indicator with open-drain output stage. The pin is pulled low when the output voltage is less than the undervoltage threshold or great than the overvoltage threshold based on the CFG1-pin setting. The pin is also pulled low indicating faults (see Power-Good Indicator (PGOOD-pin)). The pin can be left floating if not used.                                                         |  |

| MODE      | 29  | I                   | Operation mode selection pin selecting DEM or FPWM.                                                                                                                                                                                                                                                                                                                                                    |  |

| EN2       | 30  | I                   | Enable pin for phase 2.                                                                                                                                                                                                                                                                                                                                                                                |  |

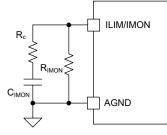

| ILIM/IMON | 31  | 0                   | Input current monitor and average input current limit setting pin. Sources a current proportional to phase 1 and phase 2 differential current sense voltage. A resistor is connected from this pin to AGND.                                                                                                                                                                                            |  |

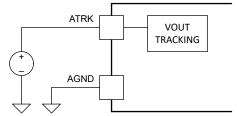

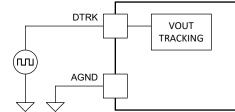

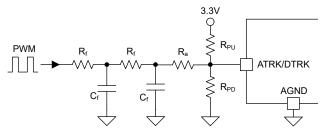

| ATRK/DTRK | 32  | I                   | Output regulation target programming pin. The output voltage regulation target can be programmed by connecting the pin through a resistor to AGND, or by controlling the pin voltage directly with a voltage in the recommended operating range of the pin from 0.2V to 2.0V. A digital PWM signal between 8% to 80% duty cycle sets the output voltage regulation in the recommended operating range. |  |

| EP        | -   | G                   | Exposed pad of the package. The Exposed pad must be connected to AGND and soldered to a large ground plane to reduce thermal resistance.                                                                                                                                                                                                                                                               |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# **5** Specifications

# 5.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range (unless otherwise specified)<sup>(1)</sup>

|                                                                                                                  |                                                                                                          | MIN  | MAX                | UNIT |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|--------------------|------|

|                                                                                                                  | BIAS to AGND                                                                                             | -0.3 | 50                 |      |

|                                                                                                                  | UVLO/EN to AGND                                                                                          | -0.3 | BIAS + 0.3         |      |

|                                                                                                                  | CSPx to AGND                                                                                             | -0.3 | 50                 |      |

|                                                                                                                  | CSPx to CSNx                                                                                             | -0.3 | 0.3                |      |

|                                                                                                                  | VOUT to AGND                                                                                             | -0.3 | 65                 |      |

|                                                                                                                  | HBx to AGND                                                                                              | -0.3 | 71                 |      |

| Input <sup>(2)</sup>                                                                                             | HBx to SWx                                                                                               | -0.3 | 5.8 <sup>(3)</sup> | V    |

| Input <sup>(2)</sup>                                                                                             | SWx to AGND                                                                                              | -0.3 | 65                 |      |

|                                                                                                                  | SWx to AGND (100ns)                                                                                      | -5   |                    |      |

|                                                                                                                  | CFG1, CFG2, SYNCIN, ATRK/DTRK, DLY, MODE, EN2, CFG0 to AGND                                              | -0.3 | 5.5                |      |

|                                                                                                                  | RT to AGND                                                                                               | -0.3 | 2.5                |      |

| Output <sup>(2)</sup>                                                                                            | PGND to AGND                                                                                             | -0.3 | 0.3                |      |

|                                                                                                                  | VCC to AGND                                                                                              | -0.3 | 5.8 <sup>(3)</sup> |      |

| Input <sup>(2)</sup> HE Input <sup>(2)</sup> HC Output <sup>(2)</sup> Output <sup>(2)</sup> Operating junction t | HOx to SWx (50ns)                                                                                        | -1   |                    | V    |

| Output                                                                                                           | LOx to AGND (50ns)                                                                                       | -1   |                    | V    |

|                                                                                                                  | PGOOD, SYNCOUT, SS, COMP, ILIM/IMON to AGND                                                              | -0.3 | 5.5                |      |

| Operating jur                                                                                                    | PGOOD, SYNCOUT, SS, COMP, ILIM/IMON to AGND<br>ating junction temperature, T <sub>J</sub> <sup>(4)</sup> |      | 150                | °C   |

| Storage temp                                                                                                     | perature, T <sub>STG</sub>                                                                               | -55  | 150                | C    |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) It is not allowed to apply an external voltage directly to CFG0, CFG1, CFG2, COMP, SS, RT, LOx, HOx pins.

(3) Operating lifetime is derated when the pin voltage is greater than 5.5V.

(4) High junction temperatures degrade operating lifetimes. Operating lifetime is derated for junction temperatures greater than 125°C.

# 5.2 ESD Ratings

|                    |                            |                                                         |             | VALUE | UNIT |

|--------------------|----------------------------|---------------------------------------------------------|-------------|-------|------|

|                    |                            | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |             | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per AEC Q100-011            | All pins    | ±500  | V    |

|                    | g_                         | Charged-device model (CDIVI), per AEC Q100-011          | Corner pins | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **5.3 Recommended Operating Conditions**

Over the recommended operating junction temperature range (unless otherwise specified)<sup>(1)</sup>

|                                                                                  |                                                                           | MIN | NOM MAX             | UNIT |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|---------------------|------|

| VI                                                                               | Boost Controller Input Voltage (when BIAS $\geq$ 4.5V or VOUT $\geq$ 6V ) | 2.5 | 42                  | V    |

| V <sub>OUT</sub>                                                                 | Boost Controller Output Voltage                                           | 6   | 60                  | V    |

| V <sub>BIAS</sub>                                                                | BIAS Input Voltage                                                        | 4.5 | 42                  | V    |

| V <sub>UVLO/EN</sub>                                                             | UVLO/EN Input Voltage                                                     | 0   | 42                  | V    |

| V <sub>EN2</sub>                                                                 | EN2 Input Voltage                                                         | 0   | 5.25                | V    |

| V <sub>MODE</sub>                                                                | MODE Input Voltage                                                        | 0   | 5.25                | V    |

| V <sub>CSP1</sub> , V <sub>CSN1</sub> , V <sub>CSP2</sub> ,<br>V <sub>CSN2</sub> | Current Sense Input Voltage                                               | 2.5 | 42                  | V    |

| V <sub>ATRK</sub>                                                                | ATRK Input Voltage                                                        | 0.2 | 2                   | V    |

| V <sub>DTRK</sub>                                                                | DTRK Input Voltage                                                        | 0   | 5.25                | V    |

| V <sub>DLY</sub>                                                                 | DLY Voltage                                                               | 0   | 5.25                | V    |

| V <sub>PGOOD</sub>                                                               | PGOOD Voltage                                                             | 0   | 5.25                | V    |

| V <sub>ILIM/IMON</sub>                                                           | ILIM/IMON Voltage                                                         | 0   | 5.25                | V    |

| V <sub>SYNCIN</sub>                                                              | Synchronization Pulse Input Voltage                                       | 0   | 5.25                | V    |

| f <sub>SW</sub>                                                                  | Switching Frequency Range                                                 | 100 | 2200 <sup>(2)</sup> | kHz  |

| f <sub>SYNCIN</sub>                                                              | Synchronization Pulse Frequency Range                                     | 100 | 2200 <sup>(2)</sup> | kHz  |

| f <sub>DTRK</sub>                                                                | DTRK Frequency Range                                                      | 100 | 2200                | kHz  |

| TJ                                                                               | Operating Junction Temperature                                            | -40 | 150 <sup>(3)</sup>  | °C   |

(1) Operating Ratings are conditions under the device is intended to be functional. For specifications and test conditions, see *Electrical* Characteristics

(2) Maximum switching frequency is programmed by R<sub>RT.</sub> The device supports up to 2200kHz switching.

(3) High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# 5.4 Thermal Information

|                       |                                              | LM5125-Q1 |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHB(VQFN) | UNIT |

|                       |                                              | 32 PINS   | _    |

| R <sub>qJA</sub>      | Junction-to-ambient thermal resistance       | 33.9      | °C/W |

| R <sub>qJC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.8      | °C/W |

| R <sub>qJB</sub>      | Junction-to-board thermal resistance         | 14.1      | °C/W |

| Ујт                   | Junction-to-top characterization parameter   | 0.4       | °C/W |

| Ујв                   | Junction-to-board characterization parameter | 14.0      | °C/W |

| R <sub>qJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.3       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

# **5.5 Electrical Characteristics**

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over  $T_J = -40^{\circ}$ C to  $150^{\circ}$ C. Unless otherwise stated,  $V_I = V_{BIAS} = 12$ V,  $V_{OUT} = 24$ V,  $R_T = 14$ k $\Omega$

|                      | PARAMETER                                                                                                              | TEST CONDITIONS                                                                        | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY CURRE         | ENT (BIAS, VCC, VOUT)                                                                                                  |                                                                                        |     |     |     |      |

| I <sub>SD</sub>      | $V_I$ current in shutdown state (BIAS connected<br>to $V_I$ ). Current into BIAS, CSP1, CSN1, CSP2,<br>CSN2, SW1, SW2. | $V_{EN/UVLO} = 0 V$ , $V_{OUT} = 12V$ , $T_J = -40^{\circ}C$ to $125^{\circ}C$         |     | 2   | 5   | μΑ   |

| I <sub>SD_BIAS</sub> | BIAS-pin current in shutdown state                                                                                     | V <sub>EN/UVLO</sub> = 0V, V <sub>OUT</sub> = 12V, T <sub>J</sub> = –<br>40°C to 125°C |     | 2   | 5   | μA   |

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over  $T_J = -40^{\circ}$ C to  $150^{\circ}$ C. Unless otherwise stated,  $V_I = V_{BIAS} = 12$ V,  $V_{OUT} = 24$ V,  $R_T = 14$ k $\Omega$

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                                                                              | MIN  | TYP   | MAX  | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| I <sub>SD_VOUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VOUT-pin current in shutdown state                                                          | $V_{EN/UVLO} = 0V$ , $V_{OUT} = 12V$ , $T_{J} = -40^{\circ}C$ to $125^{\circ}C$                                                                                              |      | 0.001 | 0.5  | μA   |

| Q_BIAS_FPWM Q_BIAS_DEM Q_UOUT_FPWM Q_UOUT_FPWM Q_UOUT_BYP BIAS VOUT /CC REGULLA /VCC-REG1 /VCC-REG1 /VCC-REG2 /VCC-UVLO- RISING /VCC-REGULU /VCC | BIAS-pin quiescent current in active state,<br>FPWM-Mode, internal clock (not-switching, RT | $\begin{array}{l} \mbox{1-phase, V_{EN/UVLO} = 2.0V, V_{EN2} \\ \mbox{= } 0V, V_{CFG2} = 0V, V_{ATRK} = \\ \mbox{0.667V, } T_J = -40^\circ C \ to \ 125^\circ C \end{array}$ |      | 1     | 1.5  | mA   |

| 'Q_BIAS_FPWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | and IMON current is excluded)                                                               | 2-phase, $V_{EN/UVLO}$ = 2.0V, $V_{EN2}$ = 2V, $V_{CFG2}$ = 0V, $V_{ATRK}$ = 0.667V, $T_J$ = -40°C to 125°C                                                                  |      | 1.4   | 2    | mA   |

| I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BIAS-pin quiescent current in active state,                                                 | 1-phase, $V_{EN/UVLO}$ = 2.0V, $V_{EN2}$ =<br>0V, $V_{CFG2}$ = 0V, $V_{ATRK}$ = 0.667V,<br>$T_J$ = -40°C to 125°C                                                            |      | 1     | 1.5  | mA   |

| <sup>I</sup> Q_BIAS_DEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DEM-Mode, internal clock (not-switching, RT<br>and IMON current is excluded)                | 2-phase, $V_{EN/UVLO} = 2.0V$ , $V_{EN2} = 2V$ , $V_{CFG2} = 0V$ , $V_{ATRK} = 0.667V$ , $T_J = -40^{\circ}$ C to $125^{\circ}$ C                                            |      | 1.6   | 2    | mA   |

| I <sub>Q_VOUT_FPWM</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VOUT-pin quiescent current in active state,<br>FPWM-Mode, internal clock (not-switching)    | 2-phase, $V_{EN/UVLO}$ = 2.0V, $V_{EN2}$ = 2V, $V_{CFG2}$ = 0V, $V_{ATRK}$ = 0.667V, $T_J$ = -40°C to 125°C                                                                  |      | 250   | 300  | μΑ   |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BIAS-pin current in bypass state (RT and IMON current is excluded)                          | 1-phase, $V_{EN/UVLO}$ = 2.0V, $V_{EN2}$ =<br>0V, $V_{CFG2}$ = 0V, $V_{OUT}$ = 12V, $T_J$<br>= -40°C to 125°C                                                                |      | 1     | 1.5  | mA   |

| 'Q_BIAS_BYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BIAS-pin current in bypass state (RT and IMON current is excluded)                          | 2-phase, $V_{EN/UVLO}$ = 2.0V, $V_{EN2}$ = 2V, $V_{CFG2}$ = 0V, $V_{OUT}$ = 12V, $T_J$ = -40°C to 125°C                                                                      |      | 1.5   | 2.0  | mA   |

| I <sub>Q_VOUT_BYP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VOUT-pin current in bypass state                                                            | 2-phase, $V_{EN/UVLO} = 2.0V$ , $V_{EN2} = 2V$ , $V_{CFG2} = 0V$ , $V_{OUT} = 12V$ , $T_J = -40^{\circ}C$ to $125^{\circ}C$ , no resistor between HO and SW.                 |      | 280   | 330  | μA   |

| I <sub>BIAS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BIAS-pin bias current                                                                       | V <sub>BIAS</sub> = 12V, I <sub>VCC</sub> = 200mA                                                                                                                            |      | 200   | 210  | mA   |

| I <sub>VOUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VOUT-pin bias current when VCC is supplied by VOUT                                          | V <sub>BIAS</sub> = 3.3V, I <sub>VCC</sub> = 200mA                                                                                                                           |      | 200   | 210  | mA   |

| VCC REGULLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TOR (VCC)                                                                                   |                                                                                                                                                                              |      |       |      |      |

| V <sub>BIAS-RISING</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Threshold to switch VCC supply from VOUT-<br>pin to BIAS-pin                                | V <sub>BIAS</sub> rising                                                                                                                                                     | 4.25 | 4.35  | 4.45 | V    |

| V <sub>BIAS-FALLING</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Threshold to switch VCC supply from BIAS-pin to VOUT-pin                                    | V <sub>BIAS</sub> falling                                                                                                                                                    | 4.1  | 4.2   | 4.3  | V    |

| V <sub>BIAS-HYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCC supply threshold hysteresis                                                             |                                                                                                                                                                              | 100  | 150   |      | mV   |

| V <sub>VCC-REG1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCC regulation                                                                              | No load                                                                                                                                                                      | 4.75 | 5     | 5.25 | V    |

| V <sub>VCC-REG2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCC regulation during dropout                                                               | V <sub>BIAS</sub> = 4.5V, I <sub>VCC</sub> = 110mA                                                                                                                           | 4    | 4.3   |      | V    |

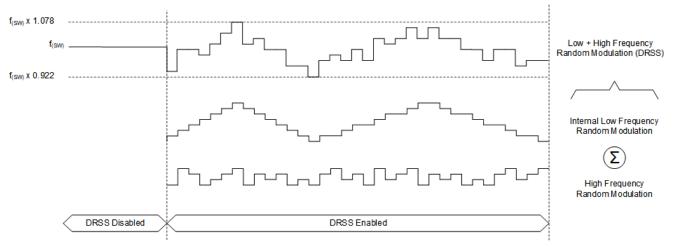

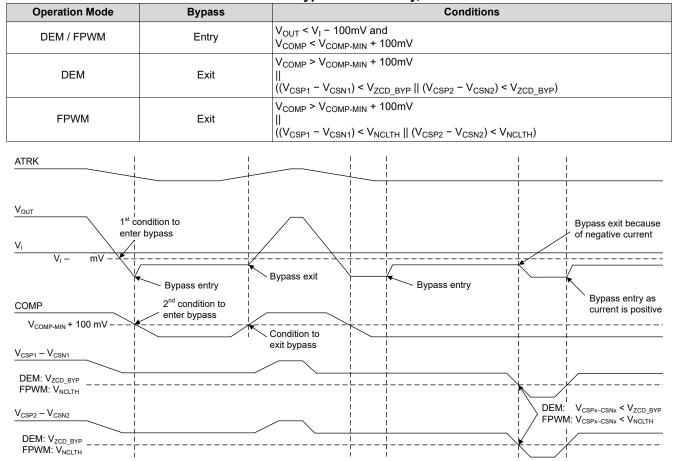

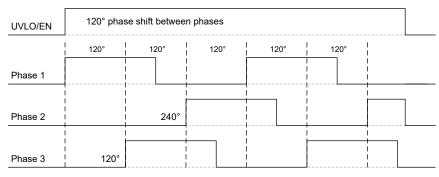

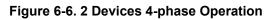

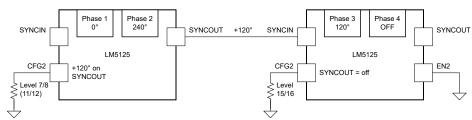

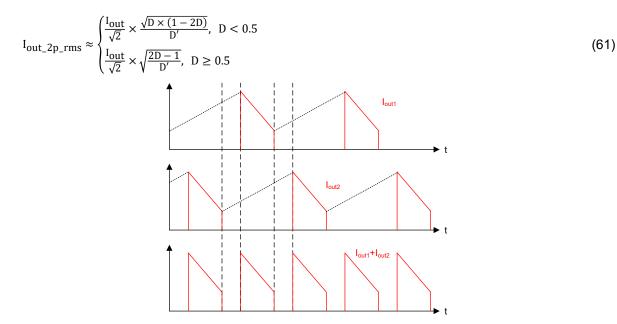

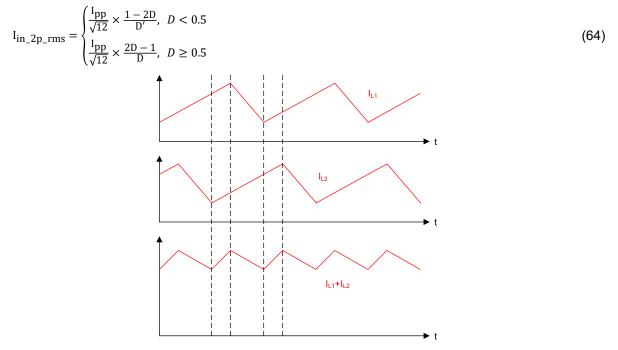

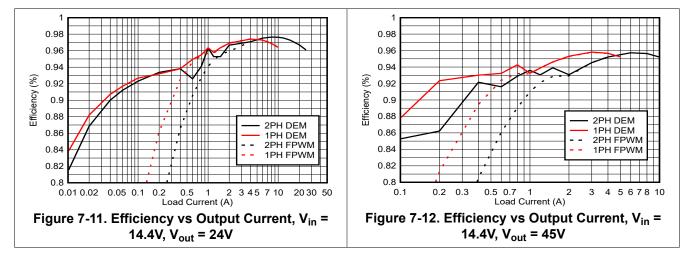

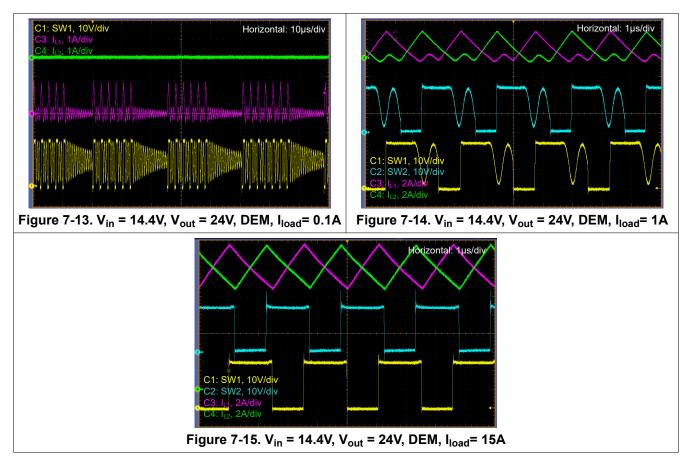

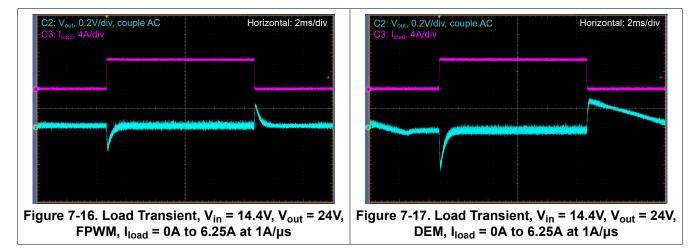

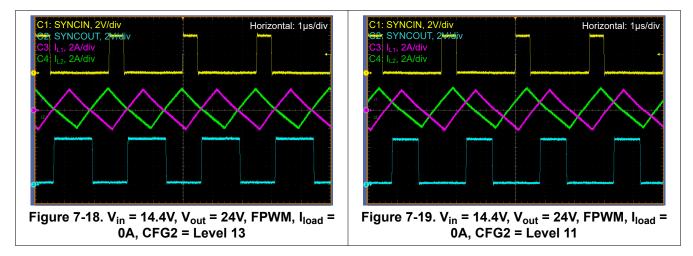

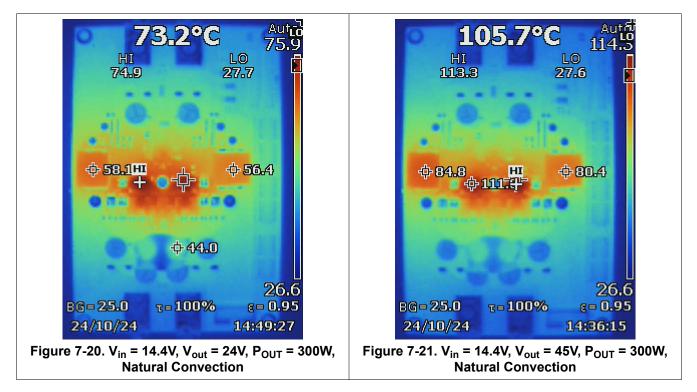

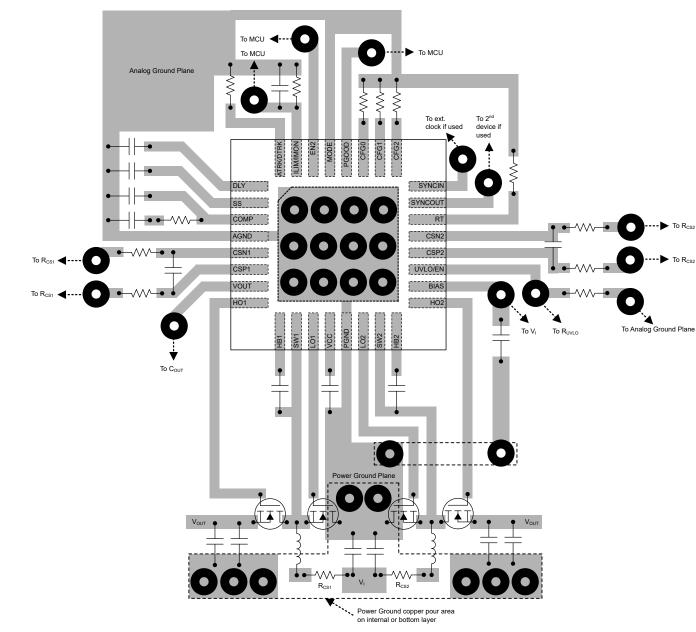

| V <sub>VCC-UVLO-</sub><br>RISING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VCC UVLO threshold                                                                          | VCC rising                                                                                                                                                                   | 3.4  | 3.5   | 3.6  | V    |