TMP104

SBOS564B - NOVEMBER 2011 - REVISED DECEMBER 2018

## TMP104 Low-Power, Digital Temperature Sensor With SMAART Wire™ Interface

### **Features**

- Multiple Device Access (MDA):

- Global Read/Write Operations

- SMAART Wire™ Interface

- Resolution: 8 Bits

- Accuracy: ±0.5°C Typical (-10°C to +100°C)

- Low Quiescent Current:

- 3-μA Active I<sub>O</sub> at 0.25 Hz

- 1-μA Shutdown

- Supply Range: 1.4 V to 3.6 V

- **Digital Output**

- Package: 0.8-mm ( $\pm$ 5%) × 1-mm ( $\pm$ 5%) 4-Ball WCSP (DSBGA)

## **Applications**

- Handsets

- **Notebooks**

## 3 Description

The TMP104 device is a digital output temperature sensor in a four-ball wafer chip-scale package (WCSP). The TMP104 is capable of reading temperatures to a resolution of 1°C.

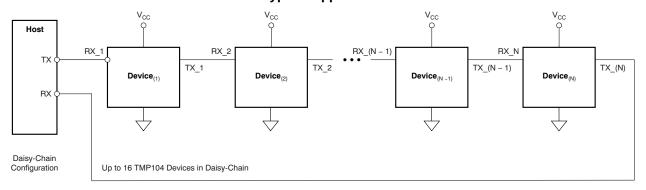

The TMP104 features a SMAART wire™ interface that supports daisy-chain configurations. In addition, the interface supports multiple device access (MDA) commands that allow the master to communicate with multiple devices on the bus simultaneously, eliminating the need to send individual commands to each TMP104 on the bus.

Up to 16 TMP104s can be tied together in parallel and easily read by the host. The TMP104 is especially ideal for space-constrained, powersensitive applications with multiple temperature measurement zones that must be monitored.

The TMP104 is specified for operation over a temperature range of -40°C to +125°C.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TMP104      | DSBGA (4) | 1.20 mm × 1.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Typical Application**

## **Table of Contents**

| 1 | Features                        | 1 |   | 7.1  | Overview                                        | 6   |

|---|---------------------------------|---|---|------|-------------------------------------------------|-----|

|   | Applications                    |   |   |      | Feature Description                             |     |

|   | Description                     |   |   |      | Programming                                     |     |

|   | Revision History                |   |   | 7.4  | Register Maps                                   | 10  |

|   | Pin Configuration and Functions |   | 8 | Dev  | ice and Documentation Support                   | 16  |

| 6 | _                               |   |   | 8.1  | Receiving Notification of Documentation Updates | 16  |

| • | 6.1 Absolute Maximum Ratings    |   |   |      | Community Resources                             |     |

|   | 6.2 ESD Ratings                 |   |   |      | Trademarks                                      |     |

|   | 6.3 Thermal Information         |   |   | 8.4  | Electrostatic Discharge Caution                 | 16  |

|   | 6.4 Electrical Characteristics  |   |   | 8.5  | Glossary                                        | 16  |

|   | 6.5 Typical Characteristics     |   | 9 |      | hanical, Packaging, and Orderable               | 4.0 |

| 7 | Detailed Description            |   |   | into | rmation                                         | 16  |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (November 2011) to Revision B                                                                                                                                                                                    | Page           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| <ul> <li>Added Device Information table, ESD Ratings table, Feature Description section, Device Functional Modes, Device<br/>and Documentation Support section, and Mechanical, Packaging, and Orderable Information section.</li> </ul> |                |

| Changed supply voltage maximum value from: 3.6 V to: 4 V                                                                                                                                                                                 | 3              |

| • Changed input voltage maximum value from: (V+) + 0.3 to:(V+) + 0.5 and ≤ 4 V                                                                                                                                                           | 3              |

| Moved the content in Package/Ordering Information table to the Mechanical, Packaging, and Orderable Information section                                                                                                                  |                |

| Changes from Original (November 2011) to Revision A                                                                                                                                                                                      | Page           |

| Changed one-wire UART-style interface to SMAART wire interface throughout document                                                                                                                                                       | 1              |

| Changed description of protocol in Communication Protocol section                                                                                                                                                                        | <mark>7</mark> |

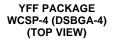

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN |      | DESCRIPTION                               |  |  |  |

|-----|------|-------------------------------------------|--|--|--|

| NO. | NAME | DESCRIPTION                               |  |  |  |

| A1  | V+   | Supply voltage                            |  |  |  |

| A2  | GND  | Ground                                    |  |  |  |

| B1  | TX   | Serial data output pin (push-pull output) |  |  |  |

| B2  | RX   | Serial data input pin                     |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings(1)

|                                       | MIN  | MAX                   | UNIT |

|---------------------------------------|------|-----------------------|------|

| Supply voltage                        |      | 4                     | V    |

| Input voltage                         | -0.3 | (V+) + 0.5<br>and ≤ 4 | V    |

| Operating temperature                 | -55  | 150                   | °C   |

| Junction temperature                  |      | +150                  | °C   |

| Storage temperature, T <sub>stg</sub> | -60  | 150                   | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

#### 6.2 ESD Ratings

|                    |                                                        |                                                                     | VALUE | UNIT |

|--------------------|--------------------------------------------------------|---------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000                                                               |       |      |

| V <sub>(ESD)</sub> | V <sub>(ESD)</sub> Electrostatic discharge             | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±100  | V    |

|                    |                                                        | Machine model (MM)                                                  | 200   |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Thermal Information

|                      |                                              | TMP104      |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                      |                                              | 4 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 188.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 2.1         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 35.1        | °C/W |

| ΨJΤ                  | Junction-to-top characterization parameter   | 10.6        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 35.1        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

## Thermal Information (continued)

|                      |                                              | TMP104      |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                      |                                              | 4 PINS      |      |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

## 6.4 Electrical Characteristics

At  $T_A = +25$ °C and V+ = +1.4 V to +3.6 V, unless otherwise noted.

|                 | PARAMETER                    | TEST CONDITIONS                                                | MIN        | TYP  | MAX        | UNIT   |

|-----------------|------------------------------|----------------------------------------------------------------|------------|------|------------|--------|

| TEMPE           | RATURE INPUT                 |                                                                |            |      | '          |        |

|                 | Range                        |                                                                | -40        |      | +125       | °C     |

|                 |                              | -10°C to +100°C, V+ = 1.8 V                                    |            | ±0.5 | ±2         | °C     |

|                 | Accuracy (temperature error) | -40°C to +125°C, V+ = 1.8 V                                    |            | ±1   | ±3         | °C     |

|                 |                              | vs supply                                                      |            | ±0.2 | ±0.5       | °C/V   |

|                 | Resolution                   |                                                                |            | 1.0  |            | °C     |

| IGITA           | L INPUT/OUTPUT               |                                                                |            |      |            |        |

| ,<br>IH         |                              |                                                                | 0.7 × (V+) |      | V+         | V      |

| İL              | Input logic levels           |                                                                | -0.5       |      | 0.3 × (V+) | V      |

| N               | Input current                | 0 < V <sub>IN</sub> < (V+) + 0.3 V                             |            |      | 1          | μА     |

| ,               |                              | V+ > 2 V, I <sub>OL</sub> = 1 mA                               | 0          |      | 0.4        | V      |

| OL              |                              | V+ < 2 V, I <sub>OL</sub> = 1 mA                               | 0          |      | 0.2 × (V+) | V      |

| r               | Output logic levels          | V+ > 2 V, I <sub>OH</sub> = 1 mA                               | (V+) - 0.4 |      | V+         | V      |

| V <sub>OH</sub> |                              | V+ < 2 V, I <sub>OH</sub> = 1 mA                               | 0.8 × (V+) |      | V+         | V      |

|                 | Resolution                   |                                                                |            | 8    |            | Bit    |

|                 | Conversion time              |                                                                |            | 26   | 35         | ms     |

|                 |                              | CR1 = 0, CR0 = 0 (default)                                     |            | 0.25 |            | Conv/s |

|                 | Commenciar models            | CR1 = 0, CR0 = 1                                               |            | 1    |            | Conv/s |

|                 | Conversion modes             | CR1 = 1, CR0 = 0                                               |            | 4    |            | Conv/s |

|                 |                              | CR1 = 1, CR0 = 1                                               |            | 8    |            | Conv/s |

|                 | Timeout time                 | Interface                                                      |            | 28   |            | ms     |

|                 | SMAART wire interface        | Serial baud rate                                               | 4.8        |      | 114        | kbps   |

| OWER            | SUPPLY                       |                                                                |            |      |            |        |

|                 | Operating supply range       |                                                                | +1.4       |      | +3.6       | V      |

| 2               | Quiescent current            | Serial bus inactive, CR1 = 0,<br>CR0 = 0 (default), V+ = 1.8 V |            | 1.5  | 3          | μА     |

|                 |                              | Serial bus active, CR1 = 0, CR0 = 0, V+ = 1.8 V                |            | 20   |            | μΑ     |

| SD              | Shutdown current             | Serial bus inactive, V+ = 1.8 V                                |            | 0.5  | 1          | μΑ     |

| ЕМРЕ            | RATURE                       |                                                                |            |      |            |        |

|                 | Specified range              |                                                                | -40        |      | +125       | °C     |

|                 | Operating range              |                                                                | -55        |      | +150       | °C     |

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

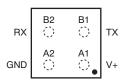

## 6.5 Typical Characteristics

At  $T_A = +25$ °C and V+ = 1.8 V, unless otherwise noted.

Copyright © 2011–2018, Texas Instruments Incorporated

## 7 Detailed Description

#### 7.1 Overview

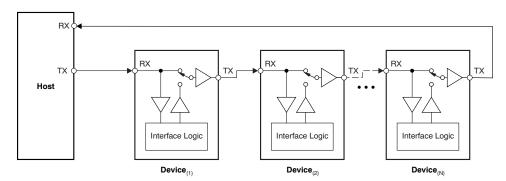

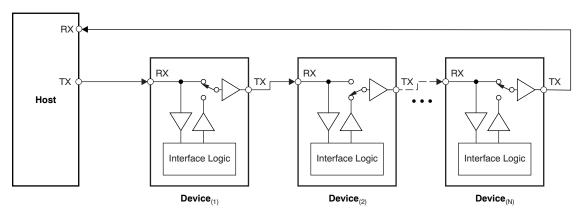

The TMP104 is a digital output temperature sensor in a wafer chip-scale package (WCSP) that is optimal for thermal management and thermal profiling. The TMP104 includes a SMAART wire interface that is capable of communicating in a daisy-chain with up to 16 devices on a single bus. The interface requires two pins from the host; the first device in the daisy-chain receives data from the host and the last device in the daisy-chain returns data to the host. In addition, the TMP104 has the capability of executing multiple device access (MDA) commands that allow multiple TMP104s to respond to a single global bus command. MDA commands reduce communication time and power in a bus that contains multiple TMP104 devices. The TMP104 is specified over a temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

The TMP104 also has the capability of configuring the bus in a transparent mode, where the input from the host is sent directly to the next device in the chain without delay. Additionally, the TMP104 can disconnect the chain and create a serial communication controlled by each TMP104 on the bus, thereby allowing each device to have configurable addressing and interrupt capabilities. The input pin, RX, is a high-impedance node. The output pin, TX, has an internal push-pull output stage that can drive the host to GND or V+.

After an initialization sequence, each device on the bus is programmed with its own interface address that allows it to respond to its own address and also respond to general commands that permit the user to read or write to all of the devices on the bus without having to send its individual address and command to each individual device.

The temperature sensor in the TMP104 is the chip itself. Thermal paths run through the package bumps as well as the package. The lower thermal resistance of metal causes the bumps to provide the primary thermal path. To maintain accuracy in applications that require air or surface temperature measurement, take care to isolate the package from ambient air temperature. A thermally-conductive adhesive can help to achieve accurate surface temperature measurement.

## 7.2 Feature Description

#### 7.2.1 Timeout Function

A timeout mechanism is implemented on the TMP104 to allow for re-synchronization of the SMAART wire interface if synchronization between the host and the TMP104 is lost for 28 ms (typical). If the timeout period expires between the calibration byte and the command byte, or between the command byte and any data byte, or between any data bytes, the TMP104 resets the SMAART wire interface circuitry so that it expects the baud rate calibration command to restart. Every time a byte is transmitted on the SMAART wire interface, this timeout period restarts.

#### 7.2.2 Noise

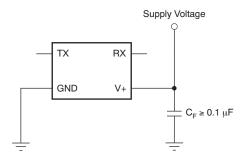

The TMP104 is a very low-power device and generates very low noise on the supply bus. Applying a bypass capacitor to the V+ pin of the TMP104 can further reduce any noise the TMP104 might propagate to other components.  $C_F$  in Figure 5 should be greater than 0.1  $\mu$ F.

Figure 5. Noise Reduction

## **Feature Description (continued)**

#### 7.2.3 SMAART Wire™ Interface Timing Specifications

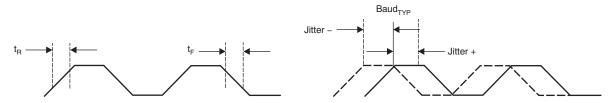

Figure 6 shows the key timing and jitter considerations for the SMAART wire interface. Table 1 lists the timing specifications for ensured, reliable operation. During a transaction, the baud rate must remain within ±1% of its initialization byte value; however, the baud rate can change from transaction to transaction. There is an allowed delay between each byte transfer of less than 28 ms, which is the bus inactivity timeout check for the TMP104 SMAART wire interface.

Figure 6. SMAART Wire™ Timing Diagram

**Table 1. Timing Diagram Definitions**

|                | <del>_</del>         |       |       |        |

|----------------|----------------------|-------|-------|--------|

|                | PARAMETER            | MIN   | MAX   | UNIT   |

| Baud           |                      | 4.8 k | 114 k | Bits/s |

| t <sub>R</sub> | Clock/data rise time |       | 0.5   | %Baud  |

| t <sub>F</sub> | Clock/data fall time |       | 0.5   | %Baud  |

| Jitter         |                      |       | ±1    | %Baud  |

## 7.3 Programming

#### 7.3.1 Communication Protocol

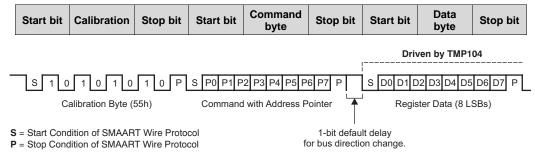

Each communication of the SMAART wire protocol consists of 8-bit words, transferred least significant bit (LSB) first. Each 8-bit word begins with a *Start* bit that is logic low, and ends with a *Stop* bit that is logic high. By using a Start bit and Stop bit for each 8-bit word, the TMP104 can calibrate each word and maintain synchronous communication throughout the process. The host commences the communication by sending a Start bit followed by the calibration byte (55h), allowing the TMP104 to sync to the baud rate of the host, followed by the Stop bit. Then, another Start bit is sent, followed by the command register byte and a Stop bit. Finally, a third Start bit is sent followed by the data byte, where master sends data if the instruction is a write command, or the TMP104 breaks the chain and sends data if the instruction is a read command. The process finishes with a Stop bit. The sequence is shown in Table 2 and Figure 7.

**Table 2. Communication Format**

Figure 7. Generic Communication BitStream

The TMP104 has two dedicated pins for communication: TX and RX. Usually, these two pins are connected internally and the signal on the RX propagates to the TX; that is, the TMP104 works in a transparent mode. The TMP104 breaks this buffer configuration only when it must send data on the bus or during address assignment and alert procedures.

The TMP104 supports unique address assignment and alert interrupt procedures. There are general-call read and write commands that allow simultaneous reads or writes to all devices in the daisy-chain. The interface has built-in time-outs (typically 28 ms) that return the interface to a known state if communication is disrupted.

#### 7.3.2 Command Register

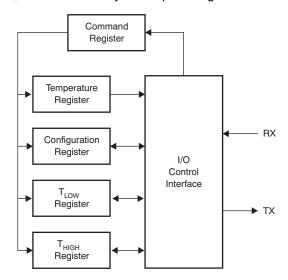

Figure 8 shows the internal register structure of the TMP104. Communications between the registers are transferred through the interface in LSB-first order. The 8-bit Command Register, as shown in Table 3, is used to determine the type of instruction being addressed. These eight bits could either interpret a global instruction or an individual instruction, which is determined by the value of P7. When P7 = 0, the command byte interprets an individual instruction; when P7 = 1, the command byte interprets a global instruction.

Figure 8. Internal Register Structure

**Table 3. Command Register Byte**

| P7  | P6      | P5      | P4      | P3      | P2 | P1 | P0  |

|-----|---------|---------|---------|---------|----|----|-----|

| GLB | IN3/ID3 | IN2/ID2 | IN1/ID1 | IN0/ID0 | P1 | P0 | R/W |

### 7.3.3 Global Initialization and Address Assignment Sequence

At device power-up, every TMP104 in the daisy-chain is connected in transparent mode, as shown in Figure 9. The host must send the initialization command (P7-P0 = 10001100) in order for the bus to program its internal address depending on the number of devices on the bus.

Figure 9. TMP104 Daisy-Chain: Bus Status at Start of Global Initialization

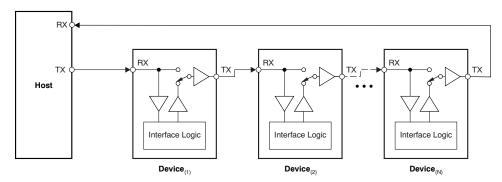

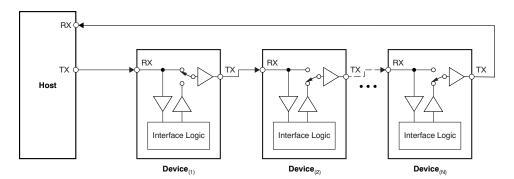

Each TMP104 in the chain interprets the initialization command byte and disconnects the chain, as shown in Figure 10. The host must then send the address assignment command, consisting of P7-P4 = 1001 and P3-P0 = 0000, where P3-P0 represents the address of the first device in the chain; this word is stored internally as its device ID. The first device increments the unit in the device address and then reconnects the bus, as shown in Figure 11. This address is then sent to the next device in the chain. Once all devices on the chain have received the respective addresses, the host receives the last programmed address on the chain + 1. The host can use this information to determine the total number of devices in the chain and the respective address of each device.

After the initialization sequence, every device can be addressed individually or through global commands. This global initialization sequence is a requirement and must be performed before any other communication.

Figure 10. TMP104 Daisy-Chain: Bus Status at Start of Address Assignment

Figure 11. TMP104 Daisy-Chain: Bus Status After First Device Address Assignment

#### 7.3.4 Global Read and Write

The host can initiate a global read or write command to all TMP104s in the daisy-chain by sending the read/write command, consisting of P7-P3 = 11110. P2-P1 indicate the data register pointer, as shown in Table 4, and P0 indicates read/write control. P0 = 0 indicates a global write command. The host must transfer one more byte of data for the register (indicated by bits P2-P1), and every TMP104 in the daisy-chain updates the appropriate register. P0 = 1 indicates a global read command. The TMP104 with the device ID of '0000' then breaks the bus connection, transmits the data from the register indicated by bits P2-P1, and then reconnects the bus. The TMP104 with the device ID of '0001' then repeats the same sequence, followed by the rest of the TMP104 devices in the daisy-chain.

Table 4. Pointer Addresses

| P0 | P0 | REGISTER                                |

|----|----|-----------------------------------------|

| 0  | 0  | Temperature register (read-only)        |

| 0  | 1  | Configuration register (read/write)     |

| 1  | 0  | T <sub>LOW</sub> register (read/write)  |

| 1  | 1  | T <sub>HIGH</sub> register (read/write) |

#### 7.3.5 Global Clear Interrupt

The host can initiate a global clear interrupt command (P7-P0 = 10101001) to all TMP104s in the daisy-chain. Upon receiving this command, the TMP104 disables future interrupts (D7 in the Configuration Register is set to '0'). If a TMP104 has previously broken the bus connection and sent an interrupt (logic low on the bus), it now stops holding the bus low. The device sends the baud rate calibration command and clear interrupt command to the next TMP104 in the chain, and then reconnects the bus. In the case of multiple devices having active interrupts, the clear interrupt command propagates through the daisy-chain, disables all interrupts, and reconnects the bus across all devices.

#### 7.3.6 Global Software Reset

The host can initiate a global software reset command (P7-P0 = 10110100) to all TMP104s in the daisy-chain. Upon receiving this command, the TMP104 resets its internal registers except for the device ID, which is not reset, and reconnects the bus. If the bus is broken before the initiation of this command, all TMP104s before the broken bus point receive the command. If the host intends to initiate a global software reset across all TMP104s in the chain, this command must be transmitted multiple times until it echoes back to the host.

#### 7.3.7 Individual Read and Write

The host can initiate an individual read/write command to a particular TMP104 in the daisy-chain by sending the read/write command. The read/write command consists of these parameters:

- P7 = 0

- P6-P3 = the device ID

- P2-P1 = the data register pointer; see Table 4

- P0 = indicates read/write control

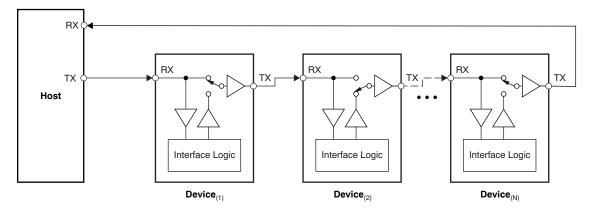

P0 = 0 indicates an individual write command; the host must transfer one more byte of data for the register indicated by bits P2-P1. The TMP104 in the daisy-chain that corresponds to the device ID noted by bits P6-P3 then updates the appropriate register. P0 = 1 indicates an individual read command; as shown in Figure 12, the TMP104 in the daisy-chain that corresponds to the device ID pointed by bits P6-P3 then breaks the bus, transmits the data from the register pointed by bits P2-P1, and reconnects the bus.

Figure 12. TMP104 Daisy-Chain: Bus Status During Individual Read Operation of Second Device

#### 7.4 Register Maps

## 7.4.1 Temperature Register

The Temperature Register of the TMP104 is configured as an 8-bit, read-only register that stores the output of the most recent conversion. A single byte must be read to obtain data, and is described in Table 5. The data format for temperature is summarized in Table 6. One LSB equals 1°C.

## **Table 5. Temperature Register**

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | <b>D0</b> |  |

|----|----|----|----|----|----|----|-----------|--|

| T7 | Т6 | T5 | T4 | Т3 | T2 | T1 |           |  |

Negative numbers are represented in binary twos complement format. Following power-up or reset, the Temperature Register reads 0°C until the first conversion is complete.

Table 6. 8-Bit Temperature Data Format<sup>(1)</sup>

|                  | DIGITAL   | ОИТРИТ |

|------------------|-----------|--------|

| TEMPERATURE (°C) | BINARY    | HEX    |

| 128              | 0111 1111 | 7F     |

| 127              | 0111 1111 | 7F     |

| 100              | 0110 0100 | 64     |

| 80               | 0101 0000 | 50     |

| 75               | 0100 1011 | 4B     |

| 50               | 0011 0010 | 32     |

| 25               | 0001 1001 | 19     |

| 0                | 0000 0000 | 00     |

| -1               | 1111 1111 | FF     |

| -25              | 1110 0111 | E7     |

| -55              | 1100 1001 | C9     |

<sup>(1)</sup> The resolution for the analog-to-digital converter (ADC) is 1°C/count, where count is equal to the digital output of the ADC.

For positive temperatures (for example, +50°C):

Twos complement is not performed on positive numbers. Therefore, simply convert the number to binary code, left-justified format. Denote a positive number with most significant bit (MSB) = 0.

Example:  $(+50^{\circ}C)/(1^{\circ}C/count) = 50 = 32h = 0011 0010$

For negative temperatures (for example, -25°C):

Generate the twos complement of a negative number by complementing the absolute value binary number and adding 1. Denote a negative number with MSB = 1.

Example:  $(|-25^{\circ}C|)/(1^{\circ}C/count) = 25 = 19h = 0001 1001$

Twos complement format: 1110 0110 + 1 = 1110 0111

### 7.4.2 Configuration Register

The Configuration Register is an 8-bit read/write register used to store bits that control the operational modes of the temperature sensor. Read/write operations are performed LSB first. The format and power-up/reset value of the Configuration Register is shown in Table 7.

Table 7. Configuration and Power-Up/Reset Format

| D7     | D6  | D5  | D4 | D3 | D2 | D1 | D0 |  |

|--------|-----|-----|----|----|----|----|----|--|

| INT_EN | CR1 | CR0 | FH | FL | LC | M1 | MO |  |

| 0      | 0   | 0   | 0  | 0  | 0  | 1  | 0  |  |

#### 7.4.2.1 Temperature Watchdog Function (FH, FL)

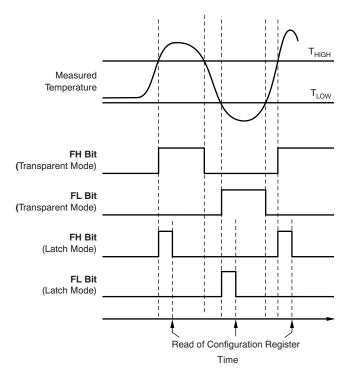

The TMP104 contains a watchdog function that monitors device temperature and compares the result to the values stored in the temperature limit registers ( $T_{HIGH}$  and  $T_{LOW}$ ) in order to determine if the device temperature is within these set limits. If the temperature of the TMP104 becomes greater than the value in the  $T_{HIGH}$  register, then the flag-high bit (FH) in the Configuration Register is set to '1'. If the temperature falls below value in the  $T_{LOW}$  register, then the flag-low bit (FL) is set to '1'. If both flag bits remain '0', then the temperature is within the temperature *window* set by the temperature limit registers, as shown in Figure 13.

Figure 13. Temperature Flag Functional Diagram

The latch bit (LC) in the Configuration Register is used to latch the value of the flag bits (FH and FL) until the master issues a read command to the Configuration Register. The flag bits are set to '0' if a read command is received by the TMP104, or if LC = 0 and the temperature is within the temperature limits. The power-on default values for these bits are FH = 0, FL = 0, and LC = 0.

#### 7.4.2.2 Conversion Rate (CR1, CR0)

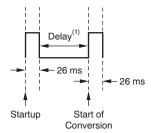

The conversion rate bits (CR1 and CR0), located in the Configuration Register, configure the TMP104 for conversion rates of 8 Hz, 4 Hz, 1 Hz, or 0.25 Hz (default). The TMP104 has a typical conversion time of 26 ms. To achieve different conversion rates, the TMP104 performs a single conversion and then powers down and waits for the appropriate delay set by CR1 and CR0. Table 8 shows the settings for CR1 and CR0.

**Table 8. Conversion Rate Settings**

| CR1 | CR0 | CONVERSION RATE   |  |  |  |  |

|-----|-----|-------------------|--|--|--|--|

| 0   | 0   | 0.25 Hz (default) |  |  |  |  |

| 0   | 1   | 1 Hz              |  |  |  |  |

| 1   | 0   | 4 Hz              |  |  |  |  |

| 1   | 1   | 8 Hz              |  |  |  |  |

After power-up or general-call reset, the TMP104 immediately starts a conversion, as shown in Figure 14. The first result is available after 26 ms (typical). The active quiescent current during conversion is 40  $\mu$ A (typical at +25°C, V+ = 1.8 V). The quiescent current during delay is 1.0  $\mu$ A (typical at +25°C, V+ = 1.8 V).

(1) Delay is set by CR1 and CR0.

Figure 14. Conversion Start

#### 7.4.2.3 Conversion Modes

### 7.4.2.3.1 Shutdown Mode (M1 = 0, M0 = 0)

Shutdown mode saves maximum power by shutting down all device circuitry other than the serial interface, reducing current consumption to typically less than  $0.5~\mu A$ . Shutdown mode is enabled when bits M1 and M0 (in the Configuration Register) read '00'. The device shuts down when the current conversion is completed.

## 7.4.2.3.2 One-Shot Mode (M1 = 0, M0 = 1)

The TMP104 features a One-Shot Temperature Measurement mode. When the device is in Shutdown mode, writing '01' to bits M1 and M0 starts a single temperature conversion. During the conversion, bits M1 and M0 read '01'. The device returns to the shutdown state at the completion of the single conversion. After the conversion, bits M1 and M0 read '00'. This feature is useful for reducing power consumption in the TMP104 when continuous temperature monitoring is not required.

As a result of the short conversion time, the TMP104 can achieve a higher conversion rate. A single conversion typically takes 26 ms and an individual read can take place in less than 300  $\mu$ s. When using One-Shot mode, 30 or more conversions per second are possible.

#### 7.4.2.3.3 Continuous Conversion Mode (M1 = 1)

When the TMP104 is in Continuous Conversion mode (M1 = 1), continuous conversions are performed at a rate determined by the conversion rate bits, CR1 and CR0 (in the Configuration Register). The TMP104 performs a single conversion, and then powers down and waits for the appropriate delay set by CR1 and CR0. See Table 8 for CR1 and CR0 settings.

#### 7.4.2.4 Interrupt Functionality (INT EN)

The TMP104 interrupts the host by disconnecting the bus and issuing an interrupt request by holding the bus low if all of these conditions are met, as shown in Figure 15:

- INT\_EN in the Configuration Register is set to '1';

- The temperature result is higher than the value in the T<sub>HIGH</sub> register or lower than the value in the T<sub>LOW</sub> register (as indicated by a '1' in either FL or FH);

- The bus is logic high and idle for more than 28 ms.

Figure 15. TMP104 Daisy-Chain:

Bus Status During an Interrupt Request (Logic Low) From Second Device

The interrupt on the bus is latched regardless of the status of LC. Writing a '1' to INT\_EN automatically sets the LC bit. The TMP104 holds the bus low until one of the following events happen:

- · Global Interrupt Clear command received;

- Global Software Reset command received;

- · A power-on reset event occurs.

Each of these events clears INT\_EN; the TMP104 does not issue future interrupts until the host writes '1' to bit D7 in the Configuration Register to re-enable future interrupts.

In a system with enabled interrupts, it is possible for a TMP104 on the bus to issue an interrupt at the same time that the host starts a communication sequence. To avoid this scenario, it is recommended that the host should check the status on the receiving side of the bus after transmitting the calibration byte. If it is '1', then the host can continue with the communication. If it is '0', one of the TMP104 devices on the bus is issuing an alert and the host must transmit a Global Interrupt Clear command.

### 7.4.3 Temperature Limit Registers

The  $T_{HIGH}$  and  $T_{LOW}$  registers are used to store the temperature limit thresholds for the TMP104 watchdog function. At the end of each temperature measurement, the TMP104 compares the temperature results to each of these limits. If the temperature result is greater than the  $T_{HIGH}$  limit, then the FH bit in the Configuration Register is set to '1'. If the temperature result is less than the  $T_{LOW}$  limit, then the FL bit in the Configuration Register is set to '1'; see Figure 13.

Table 9 and Table 10 describe the format for the  $T_{HIGH}$  and  $T_{LOW}$  registers. Power-up reset values for  $T_{HIGH}$  and  $T_{LOW}$  are:  $T_{HIGH} = +60^{\circ}\text{C}$  and  $T_{LOW} = -10^{\circ}\text{C}$ . The format of the data for  $T_{HIGH}$  and  $T_{LOW}$  is the same as for the Temperature Register.

Table 9. T<sub>HIGH</sub> Register

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| H7 | H6 | H5 | H4 | Н3 | H2 | H1 | H0 |

Table 10. T<sub>LOW</sub> Register

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| L7 | L6 | L5 | L4 | L3 | L2 | L1 | L0 |

## 8 Device and Documentation Support

## 8.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 8.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 8.3 Trademarks

SMAART Wire, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 8.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 8.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 9 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 20-Aug-2024

#### PACKAGING INFORMATION

| Orderable Device | Status   | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|----------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TMP104YFFR       | ACTIVE   | DSBGA        | YFF                | 4    | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 125   | T4                      | Samples |

| TMP104YFFT       | OBSOLETE | DSBGA        | YFF                | 4    |                | TBD          | Call TI                       | Call TI            | -40 to 125   | T4                      |         |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Feb-2024

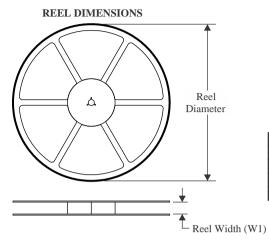

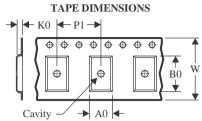

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

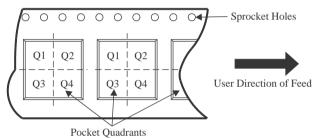

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | U     | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TMP104YFFR | DSBGA | YFF                | 4 | 3000 | 180.0                    | 8.4                      | 0.86       | 1.06       | 0.69       | 4.0        | 8.0       | Q1               |

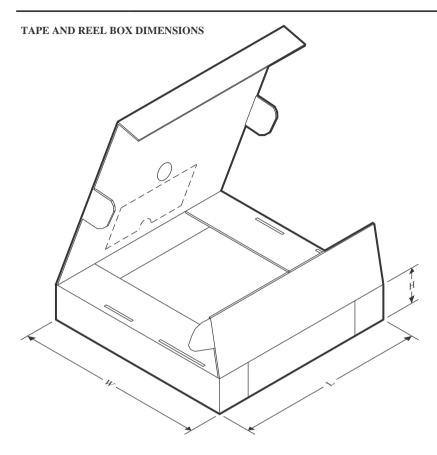

# PACKAGE MATERIALS INFORMATION

www.ti.com 20-Feb-2024

### \*All dimensions are nominal

| Ì | Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ı | TMP104YFFR | DSBGA        | YFF             | 4    | 3000 | 182.0       | 182.0      | 20.0        |  |

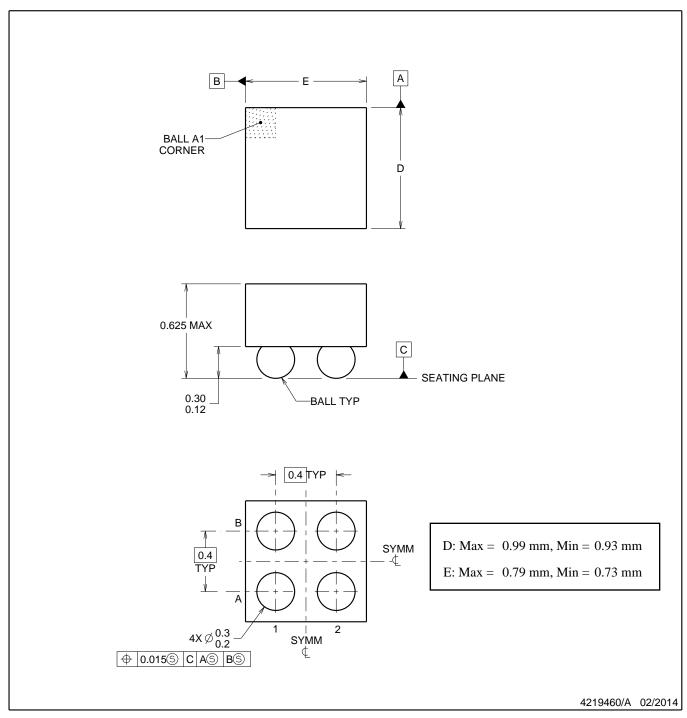

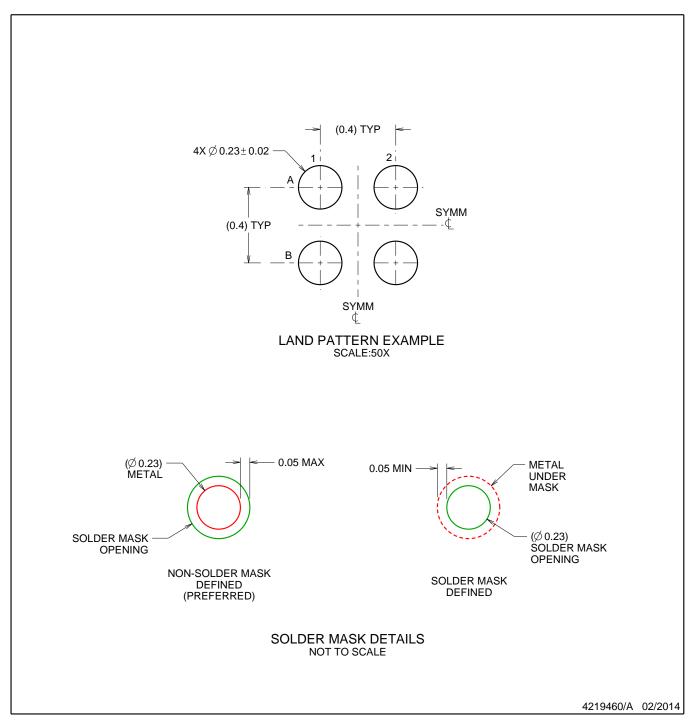

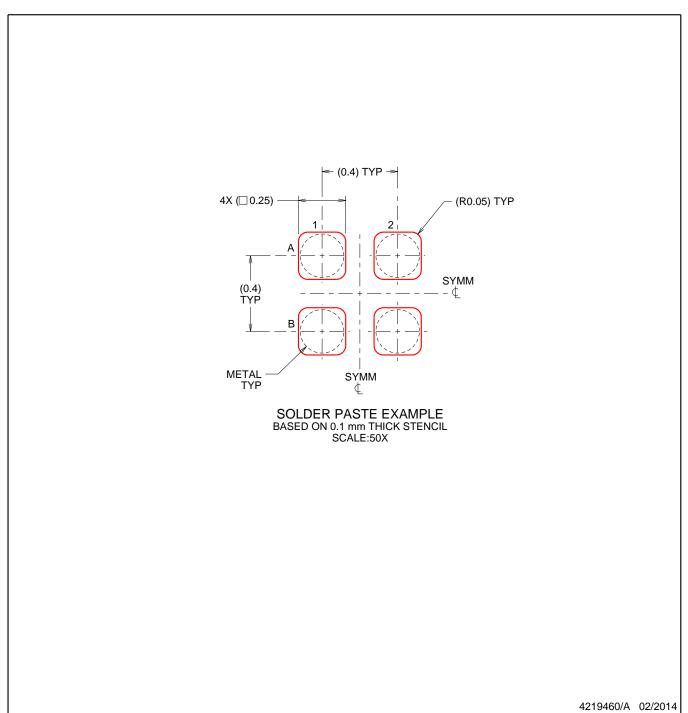

DIE SIZE BALL GRID ARRAY

### NOTES:

NanoFree Is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. NanoFree<sup>™</sup> package configuration.

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

4. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. For more information, see Texas Instruments literature number SBVA017 (www.ti.com/lit/sbva017).

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated