TPSM82830x, Low EMI, 2.25V to 5.5V input, 1A, 2A and 3A Step-Down Power Module With Integrated Inductor in QFN and MagPack<sup>™</sup> Package

### 1 Features

Texas

INSTRUMENTS

- Optimized EMI performance

- Facilitates CISPR 11/32 compliance

- Integrated on-chip noise-filtering capacitors

- Measurements according to CISPR available

- 0.5V to 4.5V adjustable output voltage

- 1% FB voltage accuracy (–40°C to 125°C T<sub>J</sub>)

- 55mΩ dropout resistance

- 2.25V to 5.5V input voltage range

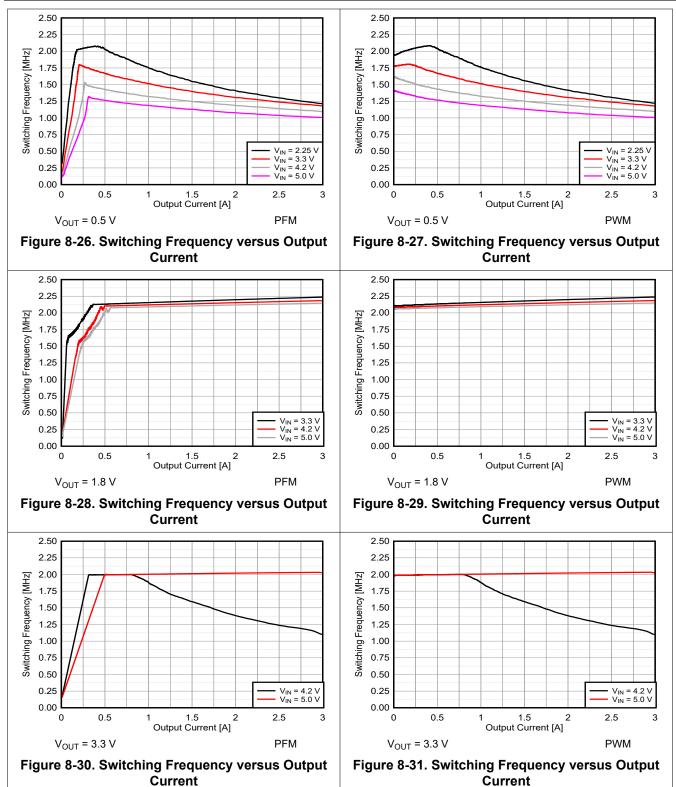

- 2.0MHz switching frequency

- 7µA operating quiescent current

- DCS-Control topology

- · Excellent transient response

- MODE pin selects between forced PWM and power save mode

- Supports 1.2V GPIO

- 100% duty cycle for lowest dropout

- Active output discharge

- Power-good output

- Thermal shutdown protection

- Hiccup or latch-off OCP/OVP

- PSpice and SIMPLIS models available

- Two package options with 0.5mm pitch

- Standard QFN

- Shielded MagPack

- Create a custom design using the TPSM828303 with the WEBENCH® Power Designer

### 2 Applications

- Industrial PC

- LPDDR5 0.5V VDDQ Supply

- ASIC, SoC, and MCU supply

- · Factory automation and control

- Medical patient monitor

- · Generic point of load

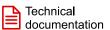

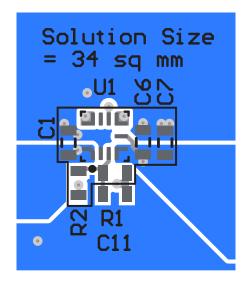

**Typical Application Schematic**

### **3 Description**

The TPSM82830x are an easy-to-use, synchronous, step-down, DC/DC module family with integrated inductor and EMI reduction technologies. Based on the DCS-Control topology, the devices have a fast transient response yet with small output capacitance. The output voltage can be set down to 0.5V with high feedback voltage accuracy of 1% over the full operating junction temperature range. A mode pin selects between power saving and forced-PWM mode. The power save mode prolongs battery life at low output currents and the forced PWM mode maintains continuous conduction in the inductor to reduce ripple at constant switching frequency. An internal soft-start circuit ramps the voltage up tightly controlled and a power-good signal indicates correct output voltage. The devices support 100% mode. HICCUP short-circuit protection combined with thermal shutdown protect device and application. The family is available in a 3.0mm × 3.0mm × 1.95mm QFN package and 2.5mm × 2.6mm × 1.95mm MagPack package.

#### **Device Information**

| PART<br>NUMBER <sup>(3)</sup> | OUTPUT<br>CURRENT | PACKAGE <sup>(1)</sup>       | PACKAGE SIZE <sup>(2)</sup> |

|-------------------------------|-------------------|------------------------------|-----------------------------|

| TPSM828301                    | 1A                |                              |                             |

| TPSM828302                    | 2A                | RDS (QFN, 9) 3.0mm ×         | 3.0mm × 3.0mm               |

| TPSM828303                    | 3A                |                              |                             |

| TPSM828303                    | ЗA                | VCB (QFN, 10) <sup>(4)</sup> | 2.5mm × 2.6mm               |

- (1) For more information, see Section 11.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

- (3) See the *Device Options* table.

- (4) Advance information (not Production Data).

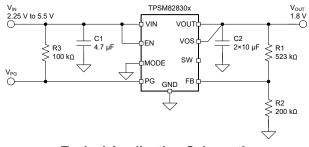

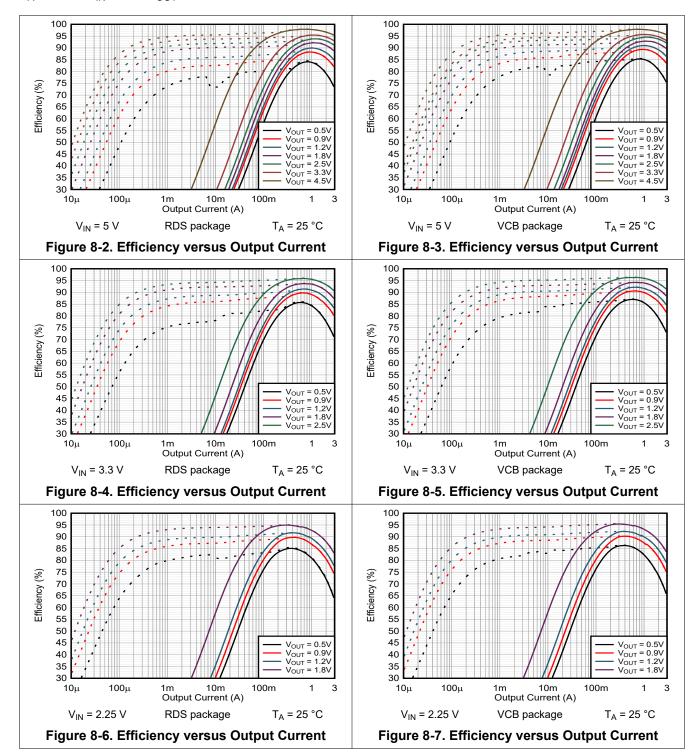

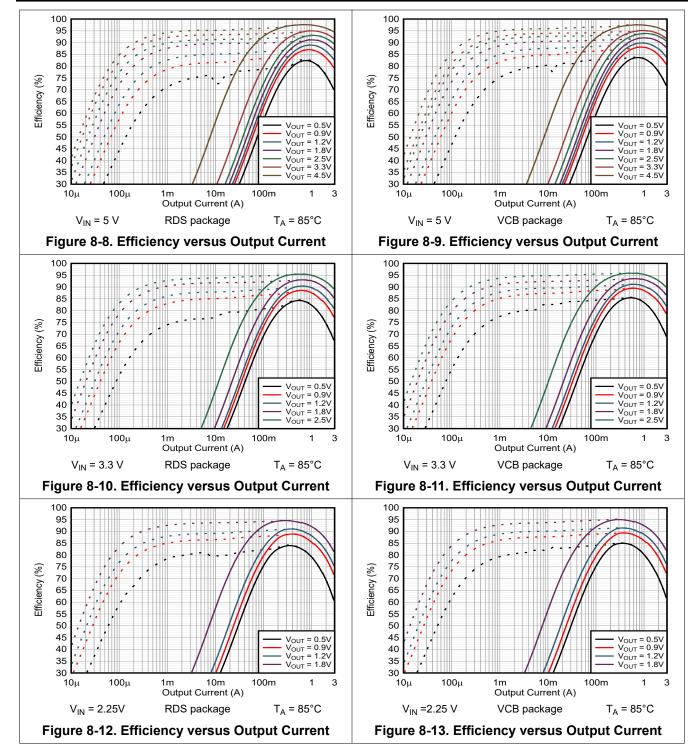

Efficiency at V<sub>IN</sub> = 5V, VCB Package

## **Table of Contents**

| 1 Features                           | 1              |

|--------------------------------------|----------------|

| 2 Applications                       | 1              |

| 3 Description                        | 1              |

| 4 Device Options                     |                |

| 5 Pin Configuration and Functions    | 3              |

| 6 Specifications                     | 5              |

| 6.1 Absolute Maximum Ratings         | 5              |

| 6.2 ESD Ratings                      |                |

| 6.3 Recommended Operating Conditions |                |

| 6.4 Thermal Information RDS Package  | 5              |

| 6.5 Thermal Information VCB Package  | 6              |

| 6.6 Electrical Characteristics       | <mark>6</mark> |

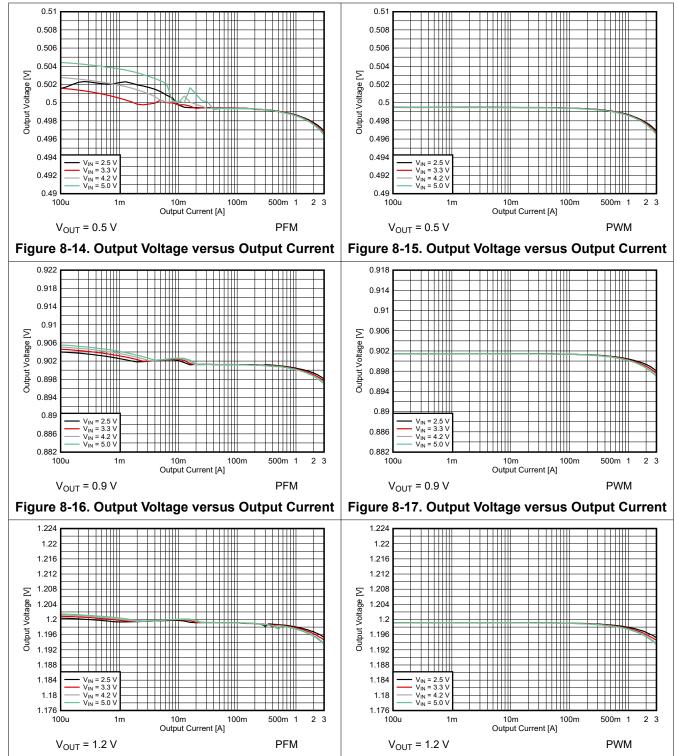

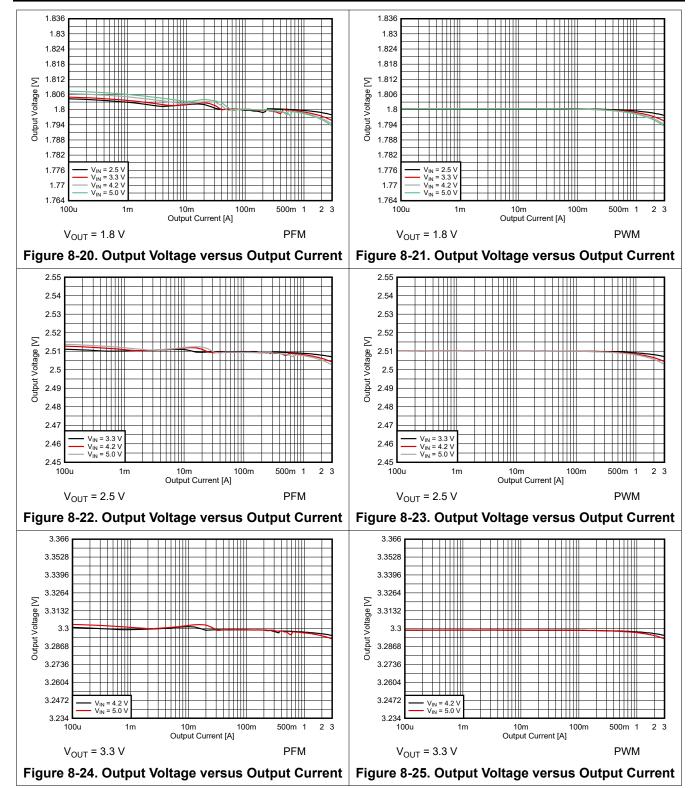

| 6.7 Typical Characteristics          | <mark>8</mark> |

| 7 Detailed Description               |                |

| 7.1 Overview                         | 9              |

| 7.2 Functional Block Diagram         | 10             |

| 7.3 Feature Description              |                |

|                                      |                |

| 7.4 Device Functional Modes             | 14 |

|-----------------------------------------|----|

| 8 Application and Implementation        | 16 |

| 8.1 Application Information             |    |

| 8.2 Typical Application                 |    |

| 8.3 Power Supply Recommendations        |    |

| 8.4 Layout                              |    |

| 9 Device and Documentation Support      |    |

| 9.1 Device Support                      | 30 |

| 9.2 Documentation Support               |    |

| 9.3 Support Resources                   | 30 |

| 9.4 Trademarks                          |    |

| 9.5 Electrostatic Discharge Caution     |    |

| 9.6 Glossary                            |    |

| 10 Revision History                     |    |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             | 31 |

|                                         |    |

Copyright © 2024 Texas Instruments Incorporated

### **4 Device Options**

| PART NUMBER                    | OUTPUT CURRENT | OCP MODE              | PACKAGE | OUTPUT VOLTAGE            |

|--------------------------------|----------------|-----------------------|---------|---------------------------|

| TPSM828301ARDSR                | 1 A            | Hiccup <sup>(2)</sup> | QFN RDS |                           |

| TPSM828302ARDSR                | 2 A            | Hiccup <sup>(2)</sup> | QFN RDS | Adjustable <sup>(1)</sup> |

| TPSM828303ARDSR                | 3 A            | Hiccup <sup>(2)</sup> | QFN RDS | Aujustable                |

| TPSM828303PVCBR <sup>(3)</sup> | 3 A            | Hiccup <sup>(2)</sup> | QFN VCB |                           |

(1) For fixed output voltage versions, please contact Marketing for availability.

(2) For versions with OCP/OVP Latch-off, please contact Marketing for availability.

(3) Advance information (not Production Data).

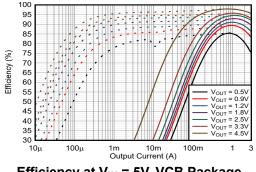

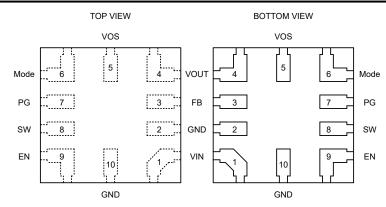

### **5** Pin Configuration and Functions

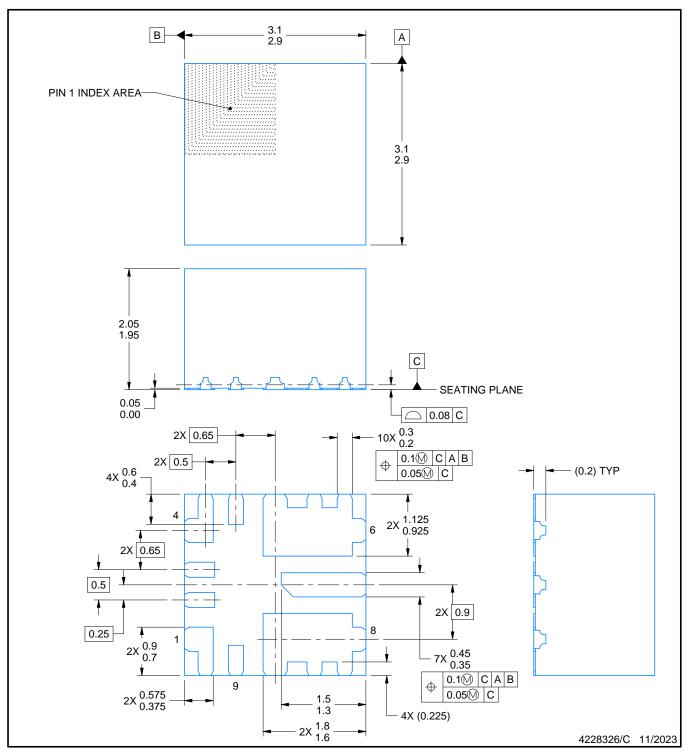

#### Figure 5-1. RDS Package, 9-Pin QFN-FCMOD Top View

#### Table 5-1. Pin Functions: RDS Package

| PIN  |     | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                                              |  |

|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | ITPE | DESCRIPTION                                                                                                                                                                                                                                              |  |

| VIN  | 1   | PWR  | Input voltage pin. Connect the input capacitor as close as possible between $V_{IN}$ and GND.                                                                                                                                                            |  |

| GND  | 2   | PWR  | round pin                                                                                                                                                                                                                                                |  |

| MODE | 3   | I    | he device runs in PSM/PWM mode when this pin pulls low and in forced-PWM mode when<br>ulled high. This action can also be done when the device is in-operation. Do not leave this<br>in floating.                                                        |  |

| FB   | 4   | I    | eedback pin. Connect the resistive output voltage divider to this pin.                                                                                                                                                                                   |  |

| VOS  | 5   | I    | utput voltage sense pin. Connect this pin directly after the inductor.                                                                                                                                                                                   |  |

| VOUT | 6   | PWR  | tput voltage pin                                                                                                                                                                                                                                         |  |

| PG   | 7   | 0    | Power good open-drain output pin. The pullup resistor can be connected to voltages up to 5.5 V. If unused, leave this pin floating.                                                                                                                      |  |

| sw   | 8   | PWR  | Switch pin of the converter, which is connected to the internal power MOSFET and the inductor. Avoid connecting this pin to larger traces as this can increase EMI. this pin can stay unconnected or be soldered to a small pad for thermal improvement. |  |

| EN   | 9   | I    | Device enable pin. To enable the device, pull this pin high. Pulling this pin low disables the device. Do not leave this pin unconnected.                                                                                                                |  |

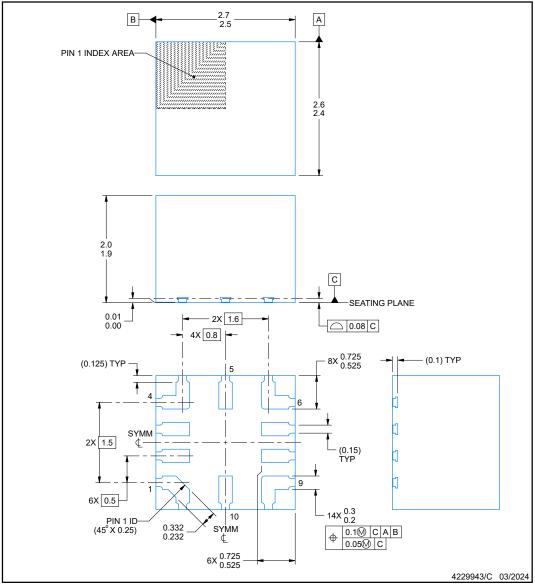

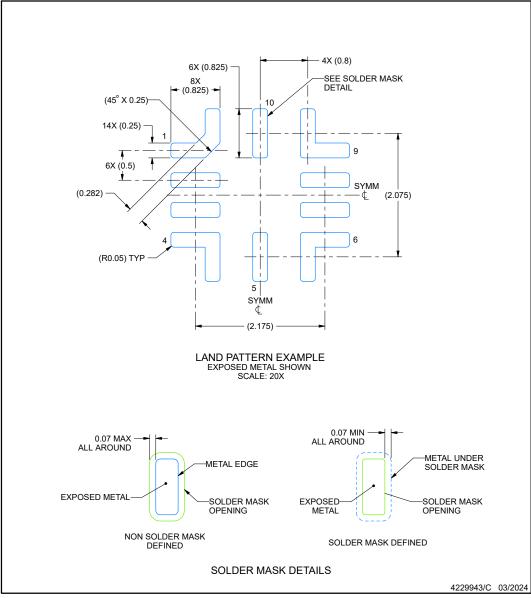

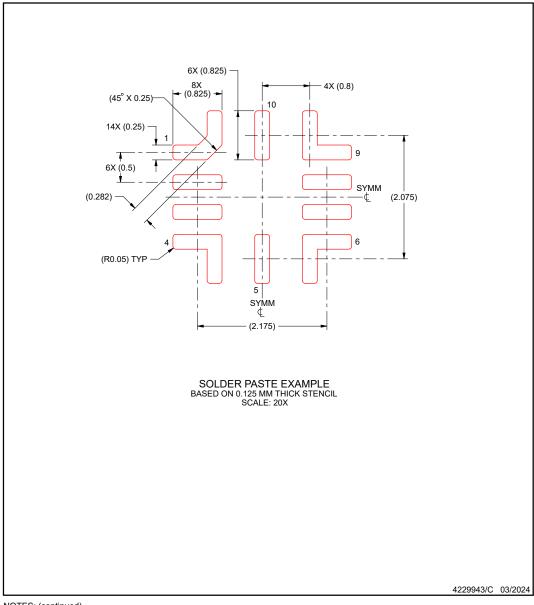

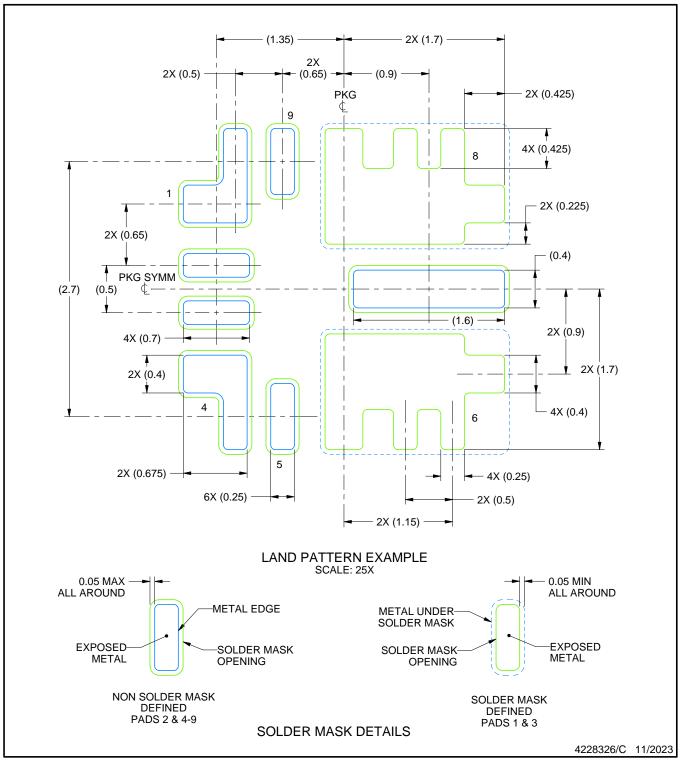

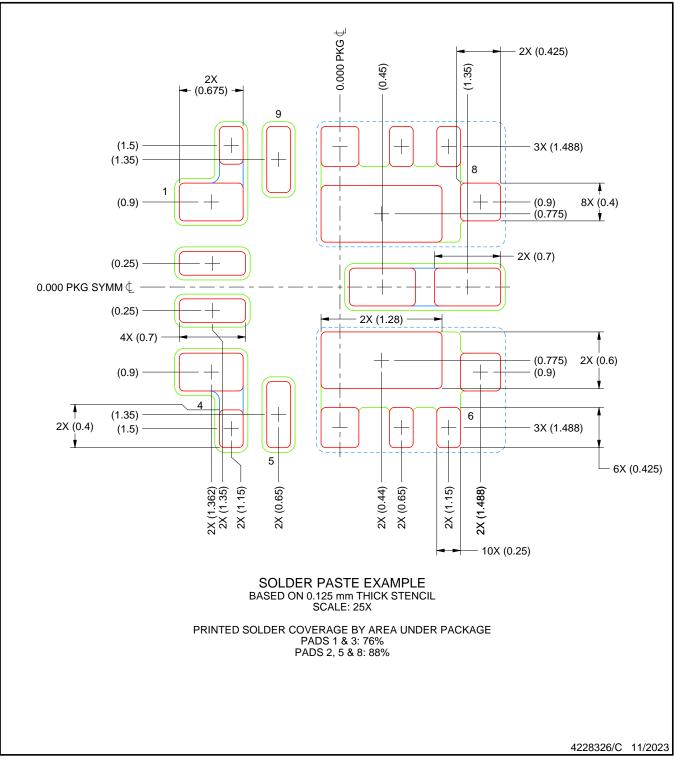

### Figure 5-2. VCB Package, 10-Pin QFN-FCMOD

#### Table 5-2. Pin Functions: VCB Package

| PIN  |       | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                                                     |  |

|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO.   |      | DESCRIPTION                                                                                                                                                                                                                                                     |  |

| VIN  | 1     | PWR  | Input voltage pin. Connect the input capacitor as close as possible between $V_{IN}$ and GND.                                                                                                                                                                   |  |

| GND  | 2, 10 | PWR  | Ground pins                                                                                                                                                                                                                                                     |  |

| FB   | 3     | I    | Feedback pin. Connect the resistive output voltage divider to this pin.                                                                                                                                                                                         |  |

| VOUT | 4     | PWR  | utput voltage pin                                                                                                                                                                                                                                               |  |

| VOS  | 5     | I    | Dutput voltage sense pin. Connect this pin directly after the inductor.                                                                                                                                                                                         |  |

| MODE | 6     | I    | The device runs in PSM/PWM mode when this pin pulls low and in forced-PWM mode when pulled high. This action can also be done when the device is in operation. Do not leave this pin floating.                                                                  |  |

| PG   | 7     | 0    | Power-good open-drain output pin. The pullup resistor can be connected to voltages up to 5.5 V. If unused, leave this pin floating.                                                                                                                             |  |

| sw   | 8     | PWR  | Switch pin of the converter, which is connected to the internal power MOSFET and the inductor. Avoid connecting this pin to larger traces as this action can increase EMI. This pin can stay unconnected or be soldered to a small pad for thermal improvement. |  |

| EN   | 9     | I    | Device enable pin. To enable the device, pull this pin high. Pulling this pin low disables the device. Do not leave this pin unconnected.                                                                                                                       |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

Over operating junction temperature range (unless otherwise noted) (1)

|                        |                                                      | MIN  | MAX | UNIT |

|------------------------|------------------------------------------------------|------|-----|------|

| Voltage <sup>(2)</sup> | V <sub>IN</sub> , EN, MODE, FB, PG, V <sub>OUT</sub> | -0.3 | 6   | V    |

| TJ                     | Operating junction temperature                       | -40  | 125 | °C   |

| T <sub>stg</sub>       | Storage temperature                                  | -55  | 125 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) All voltage values are with respect to the network ground terminal.

### 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE  | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|--------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ± 2000 | V    |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ± 500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating junction temperature range (unless otherwise noted)

|                  |                                               | MIN  | NOM | MAX | UNIT |

|------------------|-----------------------------------------------|------|-----|-----|------|

| V <sub>IN</sub>  | Input voltage range                           | 2.25 |     | 5.5 | V    |

| V <sub>OUT</sub> | Output voltage range                          | 0.5  |     | 4.5 | V    |

| C <sub>IN</sub>  | Effective input capacitance (1)               | 3    |     |     | μF   |

| C <sub>OUT</sub> | Effective output capacitance <sup>(1)</sup>   | 12   |     | 200 | μF   |

| I <sub>OUT</sub> | Output current range; TPSM828301              |      |     | 1   | А    |

| I <sub>OUT</sub> | Output current range; TPSM828302              |      |     | 2   | А    |

| lout             | Output current range; TPSM828303 (2)          |      |     | 3   | А    |

| I <sub>PG</sub>  | Power-good input current capability           |      |     | 1   | mA   |

| TJ               | Operating junction temperature <sup>(2)</sup> | -40  |     | 125 | °C   |

|                  |                                               |      |     |     |      |

(1) The values given for all the capacitors in the table are effective capacitance, which includes the DC bias effect. Due to the DC bias effect of ceramic capacitors, the effective capacitance is lower than the nominal value when a voltage is applied. Please check the manufacturer's DC bias curves for the effective capacitance vs DC voltage applied.

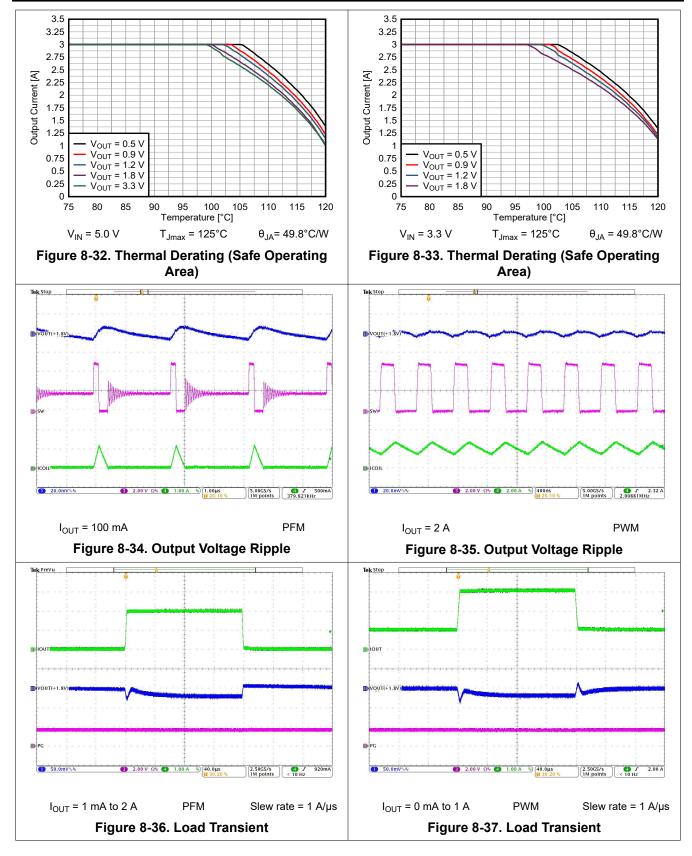

(2) In applications where high power dissipation and high ambient temperatures are present, the maximum output current must be derated to operate the module within its operating temperature range.

#### 6.4 Thermal Information RDS Package

|                       |                                              | TPSM8283             |                    |      |

|-----------------------|----------------------------------------------|----------------------|--------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RI                   | UNIT               |      |

|                       |                                              | 9 pins (JEDEC board) | 9 pins (EVM board) |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 59.4                 | 49.8               | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 66.5                 | n/a <sup>(2)</sup> | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 16.8                 | n/a <sup>(2)</sup> | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.3                  | 0.5                | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 16.7                 | 23.2               | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics report.

(2) Not applicable to an EVM.

#### 6.5 Thermal Information VCB Package

|                       |                                              | TPSM8283              | 303PVCBR              |      |

|-----------------------|----------------------------------------------|-----------------------|-----------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | V                     | UNIT                  |      |

|                       |                                              | 10 pins (JEDEC board) | 10 pins (EVM board)   |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 83.1                  | 66.5                  | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 37.1                  | n/a <sup>(2)</sup>    | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 27.4                  | n/a <sup>(2)</sup>    | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | (-1.7) <sup>(3)</sup> | (-1.6) <sup>(3)</sup> | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 27.2                  | 35.3                  | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics report.

(2) Not applicable to an EVM.

(3) Case top temperature can be higher than temperature of active circuit because of inductor power dissipation. This results in a negative Junction-to-top characterization parameter.

### **6.6 Electrical Characteristics**

$T_J = -40^{\circ}C$  to +125°C,  $V_{IN} = 2.25$  V to 5.5 V. Typical values are at  $T_J = 25^{\circ}C$  and  $V_{IN} = 5$  V (unless otherwise noted)

|                        | PARAMETER                                                  | TEST CONDITIONS                                                                            | MIN   | TYP  | MAX  | UNIT |

|------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------|------|------|------|

| SUPPLY                 |                                                            | · · · · ·                                                                                  |       |      |      |      |

| I <sub>Q</sub>         | Operating quiescent current                                | $      EN = V_{IN}, I_{OUT} = 0 mA, V_{OUT} = 1.8 \\ V, MODE = GND, device not switching $ |       | 7    | 17   | μA   |

| I <sub>SD</sub>        | V <sub>IN</sub> shutdown supply current                    | EN = low, $T_J = -40^{\circ}C$ to $85^{\circ}C$                                            |       | 100  | 700  | nA   |

| V <sub>UVLO(+)</sub>   | Rising UVLO threshold voltage (V <sub>IN</sub> )           |                                                                                            | 2.05  | 2.15 | 2.25 | V    |

| V <sub>UVLO(hys)</sub> | UVLO hysteresis (V <sub>IN</sub> )                         |                                                                                            | 90    | 120  |      | mV   |

| THERMAL SHU            | TDOWN                                                      |                                                                                            |       |      |      |      |

| T <sub>J(SD)</sub>     | Thermal shutdown threshold                                 | T <sub>J</sub> rising                                                                      |       | 150  |      | °C   |

| T <sub>J(HYS)</sub>    | Thermal shutdown hysteresis                                |                                                                                            |       | 20   |      | °C   |

| LOGIC PINs             | ·                                                          |                                                                                            |       |      |      |      |

| V <sub>EN(+)</sub>     | High-level input voltage (EN)                              |                                                                                            | 0.8   |      |      | V    |

| V <sub>EN(-)</sub>     | Low-level input voltage (EN)                               |                                                                                            |       |      | 0.35 | V    |

| V <sub>MODE(+)</sub>   | High-level input voltage (MODE)                            |                                                                                            | 0.8   |      |      | V    |

| V <sub>MODE(-)</sub>   | Low-level input voltage (MODE)                             |                                                                                            |       |      | 0.35 | V    |

| I <sub>EN(LKG)</sub>   | EN Input leakage current                                   | V <sub>EN</sub> = HIGH                                                                     |       | 10   | 100  | nA   |

| MODE(LKG)              | MODE Input leakage current                                 | V <sub>MODE</sub> = HIGH                                                                   |       | 10   | 100  | nA   |

| STARTUP                |                                                            | · · · · · ·                                                                                |       |      |      |      |

| t <sub>ss</sub>        | Internal fixed soft-start time                             | From V <sub>OUT</sub> = 0 to V <sub>OUT</sub> = 95%                                        | 180   | 300  | 440  | μs   |

| t <sub>d(EN)</sub>     | Enable delay time                                          | From EN HIGH to device starts switching                                                    |       | 120  | 220  | μs   |

| REFERENCE VO           | DLTAGE                                                     | · · · · · ·                                                                                |       |      |      |      |

| V <sub>FB</sub>        | Feedback voltage accuracy                                  | PWM mode                                                                                   | 495   | 500  | 505  | mV   |

| V <sub>FB</sub>        | Feedback voltage accuracy                                  | PWM mode                                                                                   | -1    |      | +1   | %    |

| V <sub>FB</sub>        | Feedback voltage accuracy                                  | PFM mode, C <sub>OUT,eff</sub> ≥ 15 μF, L = 0.47 μH                                        | -1    |      | +2   | %    |

| I <sub>FB(LKG)</sub>   | FB input leakage current, adjustable version               | V <sub>FB</sub> = 0.5 V                                                                    |       | 10   | 70   | nA   |

| I <sub>VOS(LKG)</sub>  | VOS input leakage current                                  | V <sub>EN</sub> = low                                                                      |       | 100  | 500  | nA   |

| POWER GOOD             |                                                            | 1                                                                                          |       |      |      |      |

| V <sub>PG,UV(+)</sub>  | Rising power-good threshold voltage (output undervoltage)  | Power Good low, V <sub>FB</sub> rising                                                     | 94    | 96   | 98   | %    |

| V <sub>PG,UV(-)</sub>  | Falling power-good threshold voltage (output undervoltage) | Power Good high, V <sub>FB</sub> falling                                                   | 90    | 92   | 94   | %    |

| V <sub>PG,OV(+)</sub>  | Rising power-good threshold voltage (output overvoltage)   | Power Good high, V <sub>FB</sub> rising                                                    | 108   | 110  | 112  | %    |

| V <sub>PG,OV(-)</sub>  | Falling power-good threshold voltage (output overvoltage)  | Power Good low, V <sub>FB</sub> falling                                                    | 102.5 | 105  | 107  | %    |

| t <sub>d(PG)</sub>     | Power good delay at start-up                               | Low-to-high transition on the PG pin at start up                                           |       | 128  |      | μs   |

### 6.6 Electrical Characteristics (continued)

|                      | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TEST CONDITIONS                                                             | MIN | TYP  | MAX | UNIT |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>d(PG)</sub>   | Power good deglitch delay during operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | High-to-low or low-to-high transition on the PG pin                         | 30  | 45   | 60  | μs   |

| I <sub>PG(LKG)</sub> | PG pin Leakage current when open drain<br>output is high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>PG</sub> = 5.0 V                                                     |     | 10   | 100 | nA   |

| V <sub>PG,OL</sub>   | PG pin low-level output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>PG</sub> = 1 mA                                                      |     |      | 0.4 | V    |

| POWER STAG           | je je stali |                                                                             |     |      |     |      |

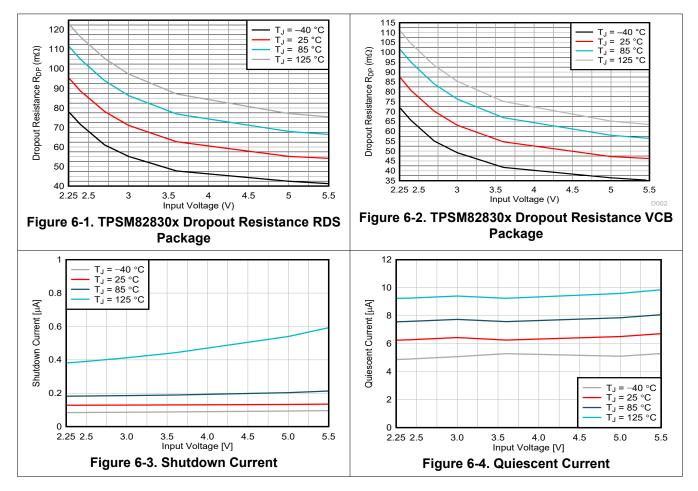

| R <sub>DP</sub>      | Dropout resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TPSM82830x, $V_{IN} \ge 5 V$ , 100% mode, $T_J = 25^{\circ}$ C, VCB package |     | 55   |     | mΩ   |

| R <sub>DP</sub>      | Dropout resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TPSM82830x, $V_{IN} \ge 5 V$ , 100% mode, $T_J = 25^{\circ}C$ , RDS package |     | 61   |     | mΩ   |

| R <sub>DP</sub>      | Dropout resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TPSM82830x, V <sub>IN</sub> = 2.7 V, 100% mode, T <sub>J</sub> = 25°C       |     | 78   | 105 | mΩ   |

| f <sub>SW</sub>      | Switching frequency, PWM mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>OUT</sub> = 1 A, V <sub>OUT</sub> = 1.8 V                            |     | 2.0  |     | MHz  |

| OVERCURRE            | NT PROTECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                             |     |      | ľ   |      |

| I <sub>HS(OC)</sub>  | High-side peak current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TPSM828301                                                                  | 1.8 | 2.1  | 2.6 | А    |

| I <sub>HS(OC)</sub>  | High-side peak current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TPSM828302                                                                  | 2.7 | 3.3  | 3.9 | А    |

| I <sub>HS(OC)</sub>  | High-side peak current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TPSM828303                                                                  | 4.0 | 4.6  | 5.4 | Α    |

| I <sub>LS(NOC)</sub> | Low-side negative current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Sinking current limit on LS FET                                             |     | -1.8 |     | Α    |

| OUTPUT DISC          | CHARGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |     |      |     |      |

| I <sub>DIS</sub>     | Output discharge current on SW pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>IN</sub> > 2 V, V <sub>SW</sub> = 0.4 V, EN = LOW                    | 75  | 400  |     | mA   |

### 6.7 Typical Characteristics

Copyright © 2024 Texas Instruments Incorporated

### 7 Detailed Description

### 7.1 Overview

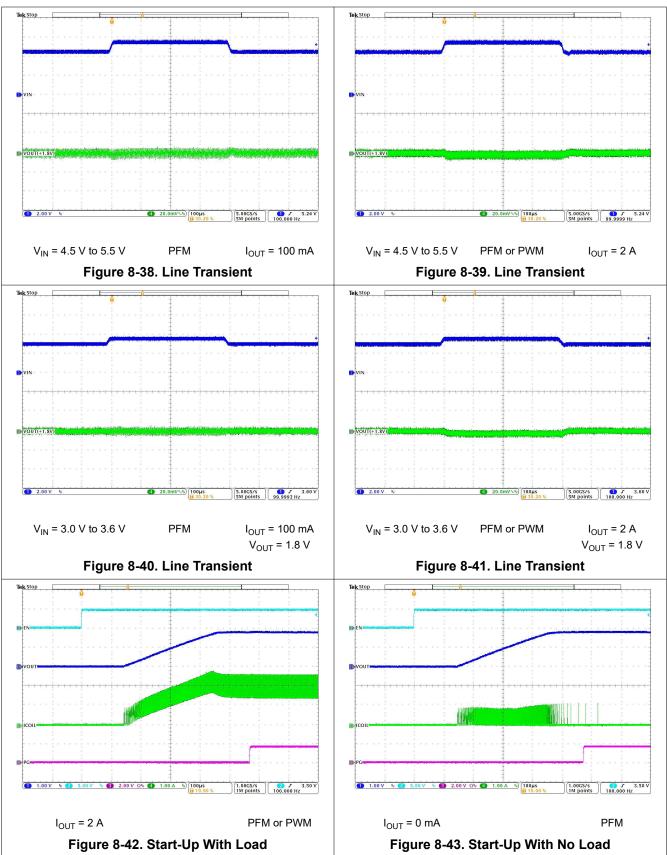

The TPSM82830x is a family of low-voltage step-down modules available in 1-, 2- and 3-A versions. These devices use a DCS-Control scheme which transitions seamlessly from pulse-width modulation (PWM) at medium and high output currents to pulsed-frequency modulation (PFM) at low output currents. During PWM operation, the devices switch at 2 MHz; during PFM operation, the switching frequency varies with the load current and reduces as the load current decreases. For applications that require the lowest possible output voltage ripple or a constant switching frequency, a high logic level on the MODE pin forces the devices to use PWM under all load conditions (at the expense of lower efficiency at low output currents). An external resistor-divider sets the output voltage anywhere from 0.5 V to 4.5 V and the nominal switching frequency is 2 MHz with a controlled variation over the input voltage range.

Device variants are available that support both hiccup and latch-off protection behavior.

The TPSM82830x devices offer two significant advantages compared to previous devices in this series: Transient performance has improved significantly by usage of a fast comparator in both PFM and PWM modes, and EMI is reduced by an optimized gate driver and on-chip decoupling capacitors.

The VCB package version uses MagPack technology for even further EMI reduction. MagPack, a Texas Instruments proprietary integrated-magnetics packaging technology, delivers the highest-performance power module design. Besides EMI reduction, MagPack enhances efficiency and thermal properties of power modules. This feature enables an industry-leading power density.

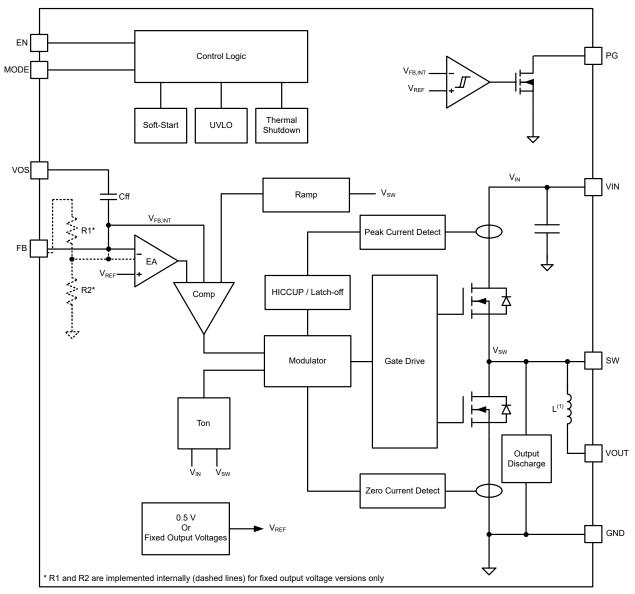

### 7.2 Functional Block Diagram

### 7.3 Feature Description

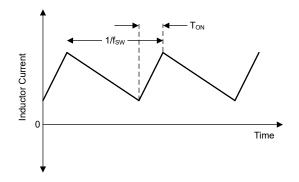

#### 7.3.1 Pulse Width Modulation (PWM) Operation

If the MODE pin is LOW and at load currents larger than half the inductor ripple current, the device operates in pulse width modulation in continuous conduction mode (CCM) as shown in Figure 7-1. The PWM operation is based on an adaptive constant on-time control with stabilized switching frequency. To achieve a stable switching frequency in a steady state condition, the on-time is calculated as:

$$T_{ON} = \frac{V_{OUT}}{V_{IN}} \times 500ns \tag{1}$$

If the MODE pin is HIGH, the converter maintains a forced-PWM operation for all load currents.

Figure 7-1. Continuous Conduction Mode (PWM-CCM) Current Waveform

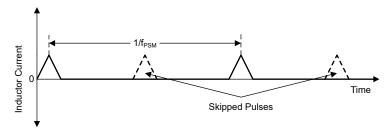

#### 7.3.2 Power Save Mode (PSM) Operation

To maintain high efficiency at light loads, the device enters power save mode (PSM) at the boundary to discontinuous conduction mode (DCM). This event happens when the output current becomes smaller than half of the ripple current of the inductor. The device operates with a fixed on-time, and the switching frequency decreases proportional to the load current as shown in Figure 7-2. Calculate as:

$$f_{PSM} = \frac{2 \times I_{OUT}}{T_{ON}^2 \times \frac{V_{IN}}{V_{OUT}} \left[ \frac{V_{IN} - V_{OUT}}{L} \right]}$$

(2)

Use L=470nH for the RDS package and L=340nH for the VCB package.

Figure 7-2. Discontinuous Conduction Mode (PSM-DCM) Current Waveform

In PSM, the output voltage rises slightly above the nominal target, which can be minimized using larger output capacitance. At duty cycles larger than 90%, the device does not enter PSM and maintains output regulation in PWM mode.

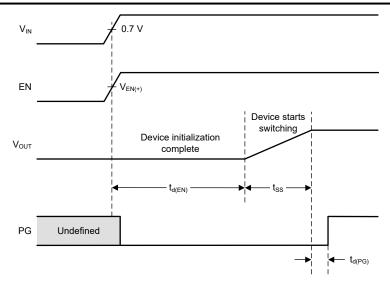

#### 7.3.3 Start-Up and Soft Start

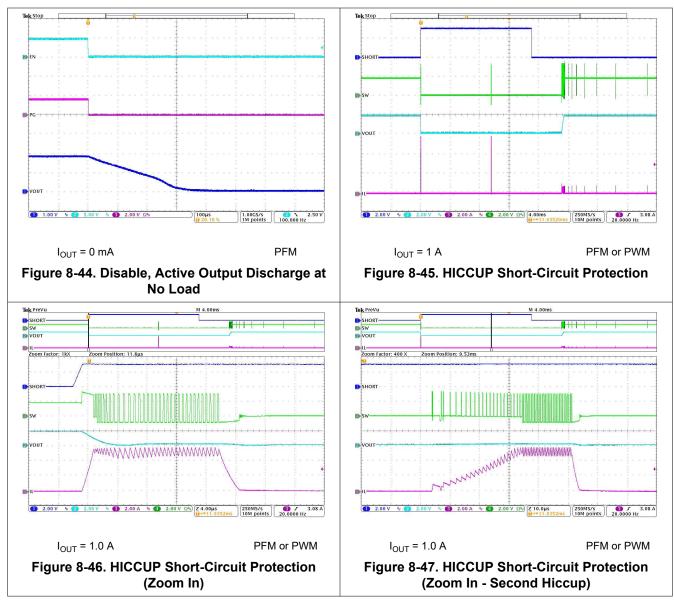

When the EN voltage goes High, the device starts loading the default values into the device registers. This action typically is done within 120  $\mu$ s. After that, the internal soft-start circuitry controls the output voltage during start-up. This control avoids excessive inrush current and makes sure of a controlled output voltage ramp. This control also prevents unwanted voltage drops from high-impedance power sources or batteries. Finally, the PG signal has a delay up to 180  $\mu$ s at start-up. Figure 7-3 shows a start-up sequence, where the EN pin is pulled up to VIN.

Figure 7-3. Start-Up Timing When EN is Pulled Up to VIN

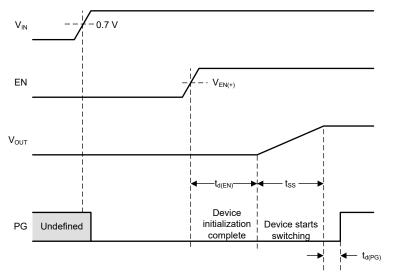

Figure 7-4 shows a start-up sequence, where an external signal is connected to the EN pin.

Figure 7-4. Start-Up Timing When an External Signal is Connected to the EN Pin

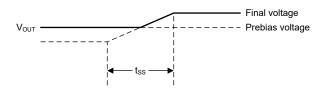

The TPSM82830x can start into a prebiased output if enabled for the first time. For a new prebiased operation, a power cycle is needed to disable the active output discharge. Figure 7-5 shows a start-up into a prebiased output voltage.

Figure 7-5. Start-Up into a Prebiased Output

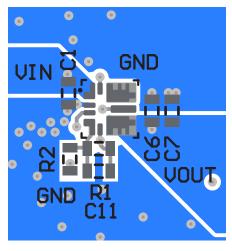

### 7.3.4 Switch Cycle-by-Cycle Current Limit

All the devices in the family have a cycle-by-cycle current limit function. When the device detects that the current in the high-side FET exceeds the high-side current limit, either due to a heavy load or a short-circuit condition,

the device immediately turns off the high-side FET and turns on the low-side FET. The high-side FET turns on again at the start of the next switching cycle. Note that because of the propagation delay in the current limit comparator (typically 60 ns), the current flowing in the high-side FET when the device detects a current limit condition can be slightly higher than the current limit specified in the device Electrical Characteristics.

#### 7.3.5 Undervoltage Lockout

The undervoltage lockout (UVLO) function prevents misoperation of the device if the input voltage drops below the UVLO threshold.

#### 7.3.6 Thermal Shutdown

The junction temperature  $(T_J)$  of the device is monitored by an internal temperature sensor. If  $T_J$  exceeds 150°C (typical), the device goes in thermal shutdown with a hysteresis of typically 20°C. After  $T_J$  has decreased enough, the device resumes normal operation.

#### 7.3.7 Optimized EMI Performance

TPSM82830x devices incorporate advanced techniques to minimize Electromagnetic Interference (EMI) and makes complying with stringent EMI standards simple. By integrating capacitors directly onto the silicon, parasitic elements are reduced and loop area is minimized, effectively reducing high-frequency noise emissions primarily above 450 MHz. The on-chip capacitors ensure low-inductance paths for high-frequency AC switching current and damping voltage ringing.

Additionally to the on-chip capacitors, the gate driver has been improved with advanced slew rate control mechanisms and by smoothing the supply voltage. The switch node voltage is controlled in a way to reduce sharp edges and minimize voltage overshoot, consequently diminishing EMI.

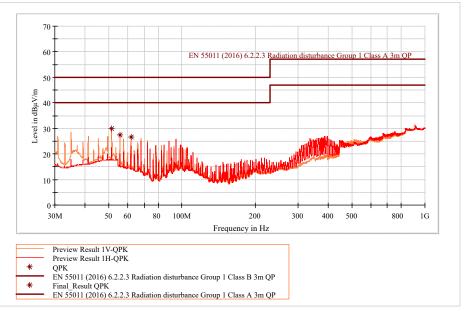

The above plot is measured on the EVM with the TPSM828303ARDSR and standard BOM.

I<sub>OUT</sub> = 3 A V<sub>IN</sub> = 5.5 V V<sub>OUT</sub> = 1.8 V

# Figure 7-6. Radiated EMI Performance (CISPR11 Radiated Emission Test with Class A and Class B Limits)

(3)

### 7.4 Device Functional Modes

#### 7.4.1 Enable, Disable, and Output Discharge

The device starts operation when Enable (EN) is set High. The input threshold levels are typically 0.8 V for rising and 0.35 V for falling signals. Do not leave EN floating. Shutdown is forced if EN is pulled Low with a shutdown current of typically 100 nA. During shutdown, the internal power MOSFETs as well as the entire control circuitry are turned off and the output voltage is actively discharged through the SW pin by a current sink. Therefore VIN must remain present for the discharge to function.

#### 7.4.2 Minimum Duty Cycle and 100% Mode Operation

There is no limitation for small duty cycles because, even at very low duty cycles, the switching frequency is reduced as needed to always make sure of a proper regulation.

If the output voltage ( $V_{OUT}$ ) comes close to the input voltage ( $V_{IN}$ ), the device enters 100% mode. While the high-side switch is constantly turned on, the low-side switch is switched off. This action is particularly useful in battery-powered applications to achieve longest operation time by taking full advantage of the whole battery voltage range. The difference between  $V_{IN}$  and  $V_{OUT}$  is determined by the voltage drop across the high-side FET and the DC resistance of the inductor. The minimum  $V_{IN}$  that is needed to maintain a specific  $V_{OUT}$  value is estimated as:

$$V_{IN,min} = V_{OUT} + I_{OUT,MAX} \times R_{DP}$$

where

- V<sub>IN.min</sub> = Minimum input voltage to maintain an output voltage

- I<sub>OUT.MAX</sub> = Maximum output current

- R<sub>DP</sub> = Resistance from VIN to VOUT, which includes the high-side MOSFET on-resistance and DC resistance of the inductor

#### 7.4.3 Power Good

The TPSM82830x has a built-in power-good (PG) function. The PG pin goes high impedance when the output voltage has reached the nominal value. Otherwise, including when disabled, in UVLO or in thermal shutdown, PG is Low (see Table 7-1). The PG function is formed with a window comparator, which has an upper and lower voltage threshold. The PG pin is an open-drain output and is specified to sink up to 1 mA. The power-good output requires a pullup resistor connecting to any voltage rail less than 5.5 V.

|                      | DEVICE CONDITIONS                                               | LOGIC STATUS |              |  |  |  |  |

|----------------------|-----------------------------------------------------------------|--------------|--------------|--|--|--|--|

|                      | Device conditions                                               | HIGH Z       | LOW          |  |  |  |  |

| Enable               | EN = High, V <sub>FB</sub> ≥ 0.48 V                             | $\checkmark$ |              |  |  |  |  |

|                      | EN = High, $V_{FB} \le 0.56 \text{ V}$                          |              |              |  |  |  |  |

|                      | EN = High, V <sub>FB</sub> ≤ 0.525 V                            | $\checkmark$ |              |  |  |  |  |

|                      | EN = High, $V_{FB} \ge 0.55 \text{ V}$                          |              |              |  |  |  |  |

| Shutdown             | EN = Low                                                        |              |              |  |  |  |  |

| Thermal shutdown     | $T_J > T_{JSD}$                                                 |              | $\checkmark$ |  |  |  |  |

| UVLO                 | $0.7 \text{ V} < \text{V}_{\text{IN}} < \text{V}_{\text{UVLO}}$ |              |              |  |  |  |  |

| Power supply removal | V <sub>IN</sub> < 0.7 V                                         | $\checkmark$ |              |  |  |  |  |

| Table | 7-1. | PG | Pin | Logic |

|-------|------|----|-----|-------|

|-------|------|----|-----|-------|

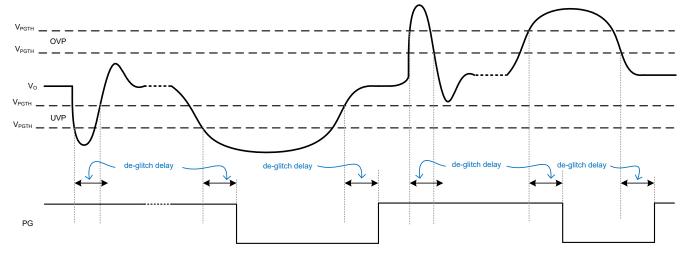

The PG signal can be used for sequencing of multiple rails by connecting the PG signal to the EN pin of other converters. Leave the PG pin unconnected when not used. The PG rising edge and falling edge has a 40 µs blanking time, as shown in Figure 7-7. At start-up, the delay of PG signal is typically 125 µs after soft start is finished.

Figure 7-7. Power-Good Behavior

### 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 8.1 Application Information

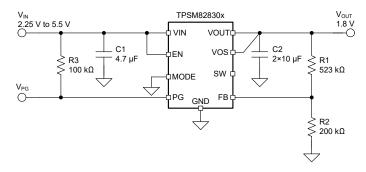

The following section discusses the design of the external components to complete the power supply design for several input and output voltage options by using typical applications as a reference.

The TPSM82830x is a synchronous step-down converter power module, where the required power inductor is integrated inside the package. The inductance value is 0.47 µH with a ±20% tolerance for the RDS package and 0.34 µH with a ±20 % tolerance for the VCB package. The family members within a package category are pin-to-pin and BOM-to-BOM compatible with each other.

#### 8.2 Typical Application

Figure 8-1. Typical Application of TPSM82830x

#### 8.2.1 Design Requirements

For this design example, use the parameters listed in Table 8-1 as the input parameters.

| DESIGN PARAMETER      | EXAMPLE VALUE   |  |  |  |  |  |  |  |  |

|-----------------------|-----------------|--|--|--|--|--|--|--|--|

| Input voltage         | 2.25 V to 5.5 V |  |  |  |  |  |  |  |  |

| Output voltage        | 1.8 V           |  |  |  |  |  |  |  |  |

| Output ripple voltage | < 15 mV         |  |  |  |  |  |  |  |  |

Table 8-1 Design Parameters

Table 8-2 lists the components used for the example.

| REFERENCE | DESCRIPTION                                                            | MANUFACTURER |

|-----------|------------------------------------------------------------------------|--------------|

| C1        | 4.7 μF, Ceramic capacitor, 6.3 V, X7R, size 0603, JMK107BB7475KA-T     | Taiyo Yuden  |

| C2        | 2 × 10 µF, Ceramic capacitor, 10 V, X7R, size 0603, GRM188Z71A106KA73D | Murata       |

| R1        | Depending on the output voltage, 1%, size 0402                         | Std          |

| R2        | 200 kΩ, Chip resistor, 1/16 W, 1%, size 0402                           | Std          |

| R3        | 100 kΩ, Chip resistor, 1/16 W, 1%, size 0402                           | Std          |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPSM82830x device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 8.2.2.2 Setting The Output Voltage

The output voltage is set by an external resistor divider according to Equation 4:

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right) = R2 \times \left(\frac{V_{OUT}}{0.5 V} - 1\right)$$

(4)

R2 can be any value between 200 k $\Omega$  and 600 k $\Omega$  to achieve high efficiency at light load while providing acceptable noise sensitivity.

#### 8.2.2.3 Input Capacitor Selection

The input capacitor is the low-impedance energy source for the converter, which helps provide stable operation. Because the buck converter has a pulsating input current, a low ESR ceramic input capacitor is required for best input voltage filtering to minimize input voltage spikes. Place the capacitor between VIN and GND pins and as close as possible to those pins.

For most applications, a minimum effective input capacitance of 3  $\mu$ F is sufficient, though a larger value reduces input current ripple and is recommended. When operating from a high impedance source, TI recommends a larger input buffer capacitor  $\geq 10 \ \mu$ F to avoid voltage drops during start-up and load transients. Additionally, small de-coupling capacitors can also be used in case of noise at the input if the device. The input capacitor can be increased without any limit for better input voltage filtering.

Table 8-3 shows a list of recommended capacitors.

| NOMINAL CAPACITANCE<br>[µF] | VOLTAGE RATING [V] | DIMENSIONS [mm]   | MFR PART NUMBER <sup>(1)</sup>    |

|-----------------------------|--------------------|-------------------|-----------------------------------|

| 4.7                         | 6.3                | 1.6 × 0.8 × 0.8   | MSASJ168BB7475MTNA01, Taiyo Yuden |

| 4.7                         | 10                 | 2.0 × 1.25 × 1.25 | C2012X7R1A475K125AC, TDK          |