TEXAS INSTRUMENTS

TUSB1021-Q1 SLLSFP2 – SEPTEMBER 2024

# TUSB1021-Q1 Automotive USB Type-C® 10Gbps Linear Redriver MUX and DeMUX

# 1 Features

- USB Type-C<sup>®</sup> 2:1 or 1:2 redriver MUX

- Supports USB 3.2 up to 10Gbps

- Ultra-low-power architecture

- Linear redriver with up to 13.3dB equalization at 5GHz

- Sixteen equalization settings

- Configuration through GPIO or I<sup>2</sup>C

- Supports either 1.8V or 3.3V I<sup>2</sup>C signaling levels

- Hot-plug capable

- No Host/Device side requirement

- Operates from a single 3.3V supply

- Automotive Grade 2 temperature range: –40°C to 105°C

- Package: 5mm × 7mm, 0.5mm pitch VQFN

# 2 Applications

- Automotive testers

- Automotive head units

- Automotive infotainment and cluster

# **3 Description**

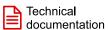

The TUSB1021-Q1 is a linear redriver with 1:2 DeMUX or 2:1 MUX function for USB Type-C<sup>®</sup> applications. The TUSB1021-Q1 is intended to reside between a Host and a USB-C<sup>®</sup> receptacle or between a USB device and a USB-C<sup>®</sup> receptacle. The TUSB1021-Q1 supports USB 3.2 data rates up to 10Gbps and supports USB 3.2 low power states (Disconnect, U1, U2, and U3)

The TUSB1021-Q1 provides sixteen levels of receive linear equalization to compensate for inter symbol interference (ISI) due to cable and board trace loss. The device operates on a single 3.3V supply and comes in an automotive grade 2 temperature range.

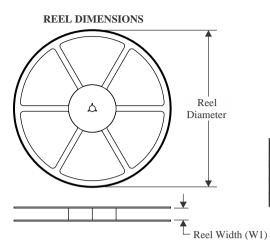

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TUSB1021-Q1 | RGF (VQFN, 40)         | 7mm × 5mm                   |

- (1) For all available packages, see Section 12.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

Simplified Schematic

# **Table of Contents**

| 1 Features                           |                |

|--------------------------------------|----------------|

| 2 Applications                       | 1              |

| 3 Description                        |                |

| 4 Pin Configuration and Functions    | 3              |

| 5 Specifications                     | 6              |

| 5.1 Absolute Maximum Ratings         | 6              |

| 5.2 ESD Ratings                      | 6              |

| 5.3 Recommended Operating Conditions | <mark>6</mark> |

| 5.4 Thermal Information              | <mark>6</mark> |

| 5.5 Electrical Characteristics       | 7              |

| 5.6 Timing Requirements              | 9              |

| 5.7 Switching Characteristics        | 9              |

| 5.8 Typical Characteristics          | 11             |

| 6 Parameter Measurement Information  | 13             |

| 7 Detailed Description               | 14             |

| 7.1 Overview                         | 14             |

| 7.2 Functional Block Diagram         | 15             |

| 7.3 Feature Description              | 15             |

| 7.4 Device Functional Modes          | 16             |

| 7.5 Programming                      | 18             |

| 8 Application and Implementation     | 22             |

| 8.1 Application Information          | 22             |

|                                      |                |

| 8.2 Typical Application                              | . 22 |

|------------------------------------------------------|------|

| 8.3 Power Supply Recommendations                     |      |

| 8.4 Layout                                           |      |

| 9 Register Maps                                      |      |

| 9.1 General Register (address = 0x0A) [reset =       |      |

| 00000011                                             | 27   |

| 9.2 USB3.2 Control/Status Registers (address =       |      |

| 0x20) [reset = 00000000]                             | . 27 |

| 9.3 USB3.2 Control/Status Registers (address =       |      |

| 0x21) [reset = 00000000]                             | . 28 |

| 9.4 USB3.2 Control/Status Registers (address =       |      |

| 0x22) [reset = 00000000]                             | . 28 |

| 10 Device and Documentation Support                  | 30   |

| 10.1 Receiving Notification of Documentation Updates | 30   |

| 10.2 Support Resources                               | . 30 |

| 10.3 Trademarks                                      |      |

| 10.4 Electrostatic Discharge Caution                 | 30   |

| 10.5 Glossary                                        |      |

| 11 Revision History                                  |      |

| 12 Mechanical, Packaging, and Orderable              |      |

| Information                                          | . 30 |

|                                                      |      |

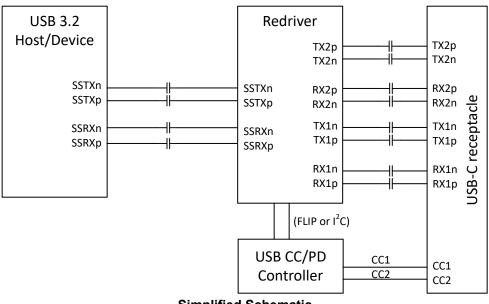

# **4** Pin Configuration and Functions

Figure 4-1. RGF Package, 40-Pin (VQFN) (Top View)

#### **Table 4-1. Pin Functions**

| PIN      |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                               |  |  |

|----------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. |                     | DESCRIPTION                                                                                                               |  |  |

| RSVD1    | 32  | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD2    | 31  | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD3    | 29  | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD4 28 |     | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD5 26 |     | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD6    | 25  | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD7    | 23  | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| RSVD8    | 22  | 0                   | Reserved. Leave unconnected.                                                                                              |  |  |

| TX1n     | 2   | Diff O              | Differential negative output. Connect to the TX1n pin on the Type-C receptacle through an external AC-coupling capacitor. |  |  |

| TX1p     | 1   | Diff O              | Differential positive output. Connect to the TX1p pin on the Type-C receptacle through an external AC-coupling capacitor. |  |  |

| RX1n     | 5   | Diff I              | Differential negative input. Connect to the RX1n pin on the Type-C receptacle through an external AC-coupling capacitor.  |  |  |

| RX1p     | 4   | Diff I              | Differential positive input. Connect to the RX1p pin on the Type-C receptacle through an external AC-coupling capacitor.  |  |  |

| RX2p     | 8   | Diff I              | Differential positive input. Connect to the RX2p pin on the Type-C receptacle through an external AC-coupling capacitor.  |  |  |

Copyright © 2024 Texas Instruments Incorporated

## Table 4-1. Pin Functions (continued)

| PIN      | ı   | TYPE <sup>(1)</sup>             | DESCRIPTION                                                                                                                                                                                                                                                          |  |  |

|----------|-----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. |                                 | DESCRIPTION                                                                                                                                                                                                                                                          |  |  |

| RX2n     | 7   | Diff I                          | Differential negative input. Connect to the RX2p pin on the Type-C receptacle through an external AC-coupling capacitor.                                                                                                                                             |  |  |

| ТХ2р     | 11  | Diff O                          | Differential positive output. Connect to the TX2p pin on the Type-C receptacle through an external AC-coupling capacitor.                                                                                                                                            |  |  |

| TX2n     | 10  | Diff O                          | Differential negative output. Connect to the TX2n pin on the Type-C receptacle through an external AC-coupling capacitor.                                                                                                                                            |  |  |

| SSTXp    | 40  | Diff I                          | Differential positive input. Connect to the USB3.2 Host/Device transmitter through an external AC-coupling capacitor.                                                                                                                                                |  |  |

| SSTXn    | 39  | Diff I                          | Differential negative input. Connect to the USB3.2 Host/Device transmitter through an external AC-coupling capacitor.                                                                                                                                                |  |  |

| SSRXp 37 |     | Diff O                          | Differential positive output. Connect to the USB3.2 Host/Device receiver through an external AC-coupling capacitor.                                                                                                                                                  |  |  |

| SSRXn    | 36  | Diff O                          | Differential negative output. Connect to the USB3.2 Host/Device receiver through an external AC-coupling capacitor.                                                                                                                                                  |  |  |

| EQ1      | 6   | 4 Level I                       | This pin along with EQ0 sets the USB receiver equalizer gain for RX1 and RX2. If not used, this pin can be left unconnected.                                                                                                                                         |  |  |

| EQ0 3    |     | 4 Level I                       | This pin along with EQ1 sets the USB receiver equalizer gain for RX1 and RX2. If not used, this pin can be left unconnected.                                                                                                                                         |  |  |

| EN       | 21  | 2 Level I<br>(PD)               | Device Enable. For normal operation, pull this pin up to 3.3V through a 10k to $50 \text{k}\Omega$ resistor.                                                                                                                                                         |  |  |

| TEST2    | 24  | 2 Level I                       | Test4. Connect directly to GND or pulldown with a 100k or less resistor.                                                                                                                                                                                             |  |  |

| I2C_EN   | 9   | 4 Level I                       | R = 11  lest Mode (I2C enabled at 3.3V)<br>F = I2C enabled at 1.8V<br>1 = I2C enabled at 3.3V.                                                                                                                                                                       |  |  |

| RSVD9    | 16  | I/O, CMOS                       | Reserved. Leave unconnected.                                                                                                                                                                                                                                         |  |  |

| RSVD10   | 17  | I/O, CMOS                       | Reserved. Leave unconnected.                                                                                                                                                                                                                                         |  |  |

| RSVD11   | 18  | I/O, CMOS                       | Reserved. Leave unconnected.                                                                                                                                                                                                                                         |  |  |

| RSVD12   | 19  | I/O, CMOS                       | Reserved. Leave unconnected.                                                                                                                                                                                                                                         |  |  |

| TEST3    | 34  | 4 Level I                       | Test pin. Leave unconnected.                                                                                                                                                                                                                                         |  |  |

| A1       | 27  | 4 Level I                       | When I2C_EN $\neq$ "0", this pin also sets the TUSB1021-Q1 I <sup>2</sup> C address.                                                                                                                                                                                 |  |  |

| SSEQ1    | 35  | 4 Level I                       | Along with SSEQ0, sets the USB receiver equalizer gain for SSTXP/N receiver.                                                                                                                                                                                         |  |  |

| SSEQ0/A0 | 30  | 4 Level I                       | Along with SSEQ1, sets the USB receiver equalizer gain for SSTXP/N receiver. When I2C_EN $\neq$ "0", this pin also sets the TUSB1021-Q1 I <sup>2</sup> C address. If I2C_EN = "F", then this pin must be set to "F" or "0".                                          |  |  |

| FLIP/SCL | 13  | 2 Level I<br>(Failsafe)<br>(PD) | When I2C_EN = "0", this is Flip control pin,<br>L: normal orientation<br>H: flip orientation<br>When I2C_EN != "0", this pin is I <sup>2</sup> C clock. When used for a I <sup>2</sup> C clock, pull up to the VCC<br>I2C supply on the I <sup>2</sup> C controller. |  |  |

| CTL0/SDA | 14  | 2 Level I<br>(Failsafe)<br>(PD) |                                                                                                                                                                                                                                                                      |  |  |

| TEST1    | 15  | 2 Level I<br>(PD)               | Test. Leave unconnected or pulldown to GND.                                                                                                                                                                                                                          |  |  |

| VCC      | 12  | Р                               | 3.3V Power Supply                                                                                                                                                                                                                                                    |  |  |

| VCC      | 20  | Р                               | 3.3V Power Supply                                                                                                                                                                                                                                                    |  |  |

| VCC      | 38  | Р                               | 3.3V Power Supply                                                                                                                                                                                                                                                    |  |  |

#### Table 4-1. Pin Functions (continued)

| PIN  |             | TYPE <sup>(1)</sup> | DESCRIPTION                 |  |

|------|-------------|---------------------|-----------------------------|--|

| NAME |             |                     | DESCRIPTION                 |  |

| NC   | 33          | NC                  | No connect pin. Leave open. |  |

| GND  | Thermal Pad | G                   | Ground                      |  |

Product Folder Links: TUSB1021-Q1

(1) I = input, O = output, Diff = differential, P = power, NC = no connection, G = ground

# **5** Specifications

#### 5.1 Absolute Maximum Ratings

over operating free-air temperature and voltage range (unless otherwise noted)<sup>(1)</sup>

|                      |                                             | MIN  | MAX  | UNIT |

|----------------------|---------------------------------------------|------|------|------|

| V <sub>CC</sub>      | Supply voltage range                        | -0.3 | 4    | V    |

| V <sub>IN_DIFF</sub> | Differential voltage at differential inputs |      | ±2.5 | V    |

| V <sub>IN_SE</sub>   | Input voltage at differential Inputs        | -0.5 | 4    | V    |

| V <sub>IN_CMOS</sub> | Input voltage at CMOS inputs                | -0.3 | 4    | V    |

| TJ                   | Junction temperature                        |      | 125  | °C   |

| T <sub>STG</sub>     | Storage temperature                         | -65  | 150  | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 5.2 ESD Ratings

|                    |                                                                    | VALUE | UNIT |  |

|--------------------|--------------------------------------------------------------------|-------|------|--|

| V                  | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> , all pins | ±4000 | V    |  |

| V <sub>(ESD)</sub> | <br>Charged device model (CDM), per AEC Q100-011, all pins         | ±1500 | v    |  |

(1) AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### **5.3 Recommended Operating Conditions**

over operating free-air temperature and voltage range (unless otherwise noted)

|                      |                                                                 | MIN | NOM | MAX | UNIT |

|----------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>      | Supply voltage                                                  | 3   | 3.3 | 3.6 | V    |

| V <sub>CC_RAMP</sub> | Power supply ramp                                               | 0.1 |     | 100 | ms   |

| V <sub>I2C</sub>     | Supply that external resistors on SDA and SCL are pulled up too | 1.7 |     | 3.6 | V    |

| V <sub>PSN</sub>     | Power supply noise on VCC                                       |     |     | 100 | mV   |

| T <sub>A</sub>       | Ambient temperature                                             | -40 |     | 105 | °C   |

| T <sub>PCB</sub>     | PCB temperature (1mm away from the device)                      | -40 |     | 112 | °C   |

#### **5.4 Thermal Information**

|                       |                                              | Device     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGF (VQFN) | UNIT |

|                       |                                              | 40 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 29.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18.6       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 10.8       | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.3        | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 10.7       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.5        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

## **5.5 Electrical Characteristics**

over operating free-air temperature and voltage range (unless otherwise noted)

|                                    | PARAMETER                                                       | TEST CONDITIONS                                                                                  | MIN  | TYP  | MAX | UNIT  |

|------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|-----|-------|

| Power                              |                                                                 |                                                                                                  |      |      |     |       |

| P <sub>CC-</sub><br>ACTIVE-<br>USB | Average active power in USB-only mode while in U0               | CTL0 = H; Link in U0 at 10Gbps;                                                                  |      | 340  |     | mW    |

| P <sub>CC-NC-</sub><br>USB         | Average power in USB mode while in disconnect state.            | CTL0 = H; No USB device detected;                                                                |      | 2.5  |     | mW    |

| P <sub>CC-U2U3</sub>               | Average power in USB mode while in U2/U3 state                  | CTL0 = H; Link in U2 or U3;                                                                      |      | 2.5  |     | mW    |

| P <sub>CC-</sub><br>shutdow<br>N   | Average power in shutdown mode.                                 | CTL0 = L; I2C_EN = "0";                                                                          |      | 0.7  |     | mW    |

| 4-State C                          | MOS Inputs(EQ[1:0], SSEQ[1:0], I2C_EN)                          | l l                                                                                              |      |      | 1   |       |

| I <sub>IH</sub>                    | High-level input current                                        | V <sub>CC</sub> = 3.6V; V <sub>IN</sub> = 3.6V                                                   | 20   |      | 80  | μA    |

| IIL                                | Low-level input current                                         | V <sub>CC</sub> = 3.6V; V <sub>IN</sub> = 0V                                                     | -160 |      | -40 | μA    |

|                                    | Threshold 0 / R                                                 | V <sub>CC</sub> = 3.3V                                                                           |      | 0.59 |     | V     |

| 4-Level<br>V <sub>TH</sub>         | Threshold R/ Float                                              | V <sub>CC</sub> = 3.3V                                                                           |      | 1.65 |     | V     |

| • 10                               | Threshold Float / 1                                             | V <sub>CC</sub> = 3.3V                                                                           |      | 2.7  |     | V     |

| R <sub>PU</sub>                    | Internal pullup resistance                                      |                                                                                                  |      | 45   |     | kΩ    |

| R <sub>PD</sub>                    | Internal pulldown resistance                                    |                                                                                                  |      | 95   |     | kΩ    |

| 2-State C                          | MOS Input (EN, FLIP, CTL0) CTL0 and FL                          | IP are Failsafe                                                                                  |      |      | I   |       |

| V <sub>IH</sub>                    | High-level input voltage                                        |                                                                                                  | 2.2  |      | 3.6 | V     |

| V <sub>IL</sub>                    | Low-level input voltage                                         |                                                                                                  | 0    |      | 0.8 | V     |

| R <sub>PD</sub>                    | Internal pull-down resistance for FLIP, CTL0, and EN.           |                                                                                                  |      | 500  |     | kΩ    |

| I <sub>IH-EN</sub>                 | High-level input current for EN pin                             | V <sub>IN</sub> = 3.6V                                                                           | 4    |      | 12  | μA    |

| I <sub>IL-EN</sub>                 | Low-level input current for EN pin                              | $V_{IN} = GND, V_{CC} = 3.6V$                                                                    | -1   |      | 1   | μA    |

| I <sub>IH-FLIP</sub>               | High-level input current for FLIP pin                           | V <sub>IN</sub> = 3.6V                                                                           | 4    |      | 12  | μA    |

| I <sub>IL-FLIP</sub>               | Low-level input current for FLIP pin                            | $V_{IN} = GND, V_{CC} = 3.6V$                                                                    | -1   |      | 1   | μA    |

| IIH-CTL0                           | High-level input current for CTL0 pin                           | V <sub>IN</sub> = 3.6V                                                                           | 4    |      | 12  | μA    |

| I <sub>IL-CTL0</sub>               | Low-level input current for CTL0 pin                            | $V_{IN} = GND, V_{CC} = 3.6V$                                                                    | -1   |      | 1   | μA    |

| I2C Contr                          | ol Pins SCL, SDA                                                | · · · · · · · · · · · · · · · · · · ·                                                            |      |      |     |       |

| V <sub>IH</sub>                    | High-level input voltage                                        | I2C_EN = "1" or "R" (3.3V I2C levels)                                                            | 2.2  |      | 3.6 | V     |

| V <sub>IL</sub>                    | Low-level input voltage                                         | I2C_EN = "1" or "R" (3.3V I2C levels)                                                            | 0    |      | 0.8 | V     |

| VIH                                | High-level input voltage                                        | I2C_EN = "F" (1.8V I2C levels)                                                                   | 1.2  |      | 3.6 | V     |

| V <sub>IL</sub>                    | Low-level input voltage                                         | I2C_EN = "F" (1.8V I2C levels)                                                                   | 0    |      | 0.4 | V     |

| V <sub>OL</sub>                    | Low-level output voltage                                        | I2C_EN ! = "0"; I <sub>OL</sub> = 3mA                                                            | 0    |      | 0.4 | V     |

| I <sub>OL</sub>                    | Low-level output current                                        | I2C_EN ! = "0"; V <sub>OL</sub> = 0.4V                                                           | 20   |      |     | mA    |

| I <sub>i_I2C</sub>                 | Input current on SDA pin                                        | 0.1 × V <sub>I2C</sub> < Input voltage < 3.3V                                                    | -10  |      | 10  | μA    |

| C <sub>i_I2C</sub>                 | Input capacitance                                               |                                                                                                  |      |      | 10  | pF    |

|                                    | erential Receiver (RX1P/N, RX2P/N, SSTX                         | P/N)                                                                                             |      |      |     |       |

| V <sub>RX-DIFF-</sub><br>PP        | Input differential peak-peak voltage swing linear dynamic range | AC-coupled differential peak-to-peak<br>signal measured post CTLE through a<br>reference channel |      | 1200 |     | mVppd |

| V <sub>RX-DC-</sub><br>см          | Common-mode voltage bias in the receiver (DC)                   |                                                                                                  |      | 0    |     | V     |

| R <sub>RX-DIFF-</sub><br>DC        | Differential input impedance (DC)                               | Present after a USB3 device is detected on TXP/TXN                                               | 72   |      | 120 | Ω     |

Product Folder Links: TUSB1021-Q1

Copyright © 2024 Texas Instruments Incorporated

# 5.5 Electrical Characteristics (continued)

over operating free-air temperature and voltage range (unless otherwise noted)

| PARAMETER                                           |                                                                                                     | TEST CONDITIONS                                                                                                                             | MIN   | TYP  | TYP MAX | UNIT  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------|-------|

|                                                     |                                                                                                     |                                                                                                                                             | INITY |      | 1117-07 | UNIT  |

| R <sub>RX-CM-</sub><br>DC                           | Receiver DC common mode impedance                                                                   | Present after a USB3 device is detected<br>on TXP/TXN                                                                                       | 18    |      | 30      | Ω     |

| Z <sub>RX-HIGH-</sub><br>IMP-DC-<br>POS             | Common-mode input impedance with termination disabled (DC)                                          | Present when no USB3 device is detected on TXP/TXN. Measured over the range of 0V to 500mV with respect to GND.                             | 25    |      |         | kΩ    |

| V <sub>SIGNAL</sub> -<br>DET-DIFF-<br>PP            | Input differential peak-to-peak signal detect assert level                                          | At 10Gbps, No loss and bit rate PRBS7 pattern                                                                                               |       | 95   |         | mVppd |

| V <sub>RX-IDLE-</sub><br>DET-DIFF-<br>PP            | Input differential peak-to-peak signal detect de-assert level                                       | At 10 Gbps, No loss and bit rate PRBS7 pattern                                                                                              |       | 70   |         | mVppd |

| V <sub>RX-LFPS-</sub><br>DET-DIFF-<br>PP            | Low-frequency periodic signaling (LFPS) detect threshold                                            | $25^{\circ}C \le T_A \le 105^{\circ}C$ ; Below the minimum is squelched. Tested at 25MHz and 300mVppd VIN.                                  | 100   |      | 300     | mVppd |

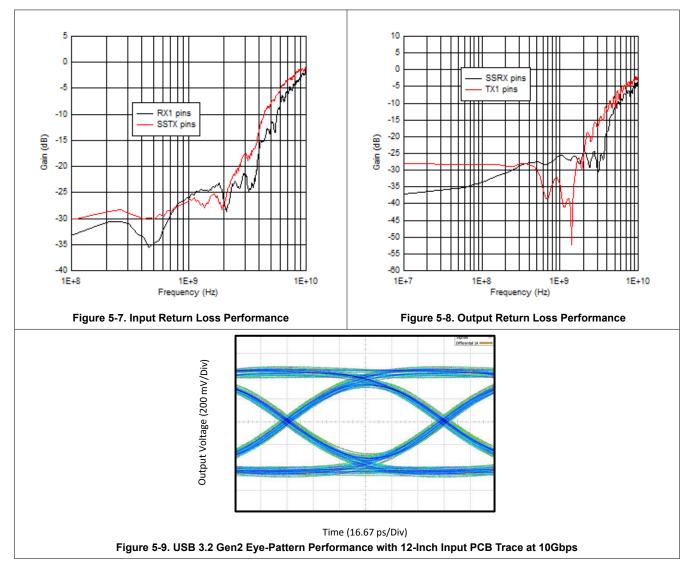

| RL <sub>RX-DIFF</sub>                               | Differential return loss                                                                            | 50MHz to 1.25GHz at 90Ω; Lowest EQ setting; FLIP = L;                                                                                       |       | -23  |         | dB    |

| RL <sub>RX-DIFF</sub>                               | Differential return loss                                                                            | 5GHz at 90Ω; Lowest EQ setting; FLIP = L;                                                                                                   |       | -12  |         | dB    |

| RL <sub>RX-CM</sub>                                 | Common-mode return loss                                                                             | 50MHz to 5GHz at 90 $\Omega$ ; Lowest EQ setting; FLIP = L;                                                                                 |       | -8   |         | dB    |

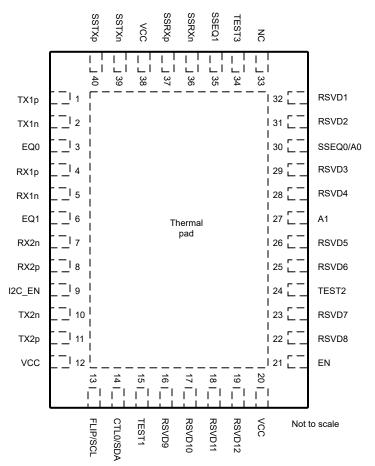

| EQ <sub>SSP</sub>                                   | Receiver equalization for RX1/2 receivers at maximum setting                                        | At 5GHz; FLIP = L;                                                                                                                          |       | 13.3 |         | dB    |

| EQ <sub>SSP</sub>                                   | Receiver equalization for SSTX receiver at maximum setting                                          | At 5GHz; FLIP = L;                                                                                                                          |       | 10.5 |         | dB    |

| USB Diffe                                           | erential Transmitter (TX1P/N, TX2P/N, SS                                                            | RXP/N)                                                                                                                                      |       |      |         |       |

| V <sub>TX-DIFF-</sub><br>PP                         | Transmitter dynamic differential voltage swing range.                                               |                                                                                                                                             |       | 1300 |         | mVppd |

| V <sub>TX-RCV-</sub><br>DETECT                      | Amount of voltage change allowed during Receiver Detection                                          | At 3.3V                                                                                                                                     |       |      | 600     | mV    |

| V <sub>TX-CM-</sub><br>IDLE-DELTA                   | Transmitter idle common-mode voltage<br>change while in U2/U3 and not actively<br>transmitting LFPS | Measured at the connector side of the AC-coupling capacitor with $50\Omega$ load                                                            | -600  |      | 600     | mV    |

| V <sub>TX-DC-</sub><br>см                           | Common-mode voltage bias in the transmitter (DC)                                                    | In U0;                                                                                                                                      | 1.5   |      | 2.1     | V     |

| V <sub>TX-CM-</sub><br>AC-PP-<br>ACTIVE             | TX AC common-mode voltage active                                                                    | At 3.3V; Maximum mismatch from<br>Txp+Txn for both time and amplitude                                                                       |       |      | 100     | mVpp  |

| V <sub>TX-IDLE-</sub><br>DIFF-AC-PP                 | AC electrical idle differential peak-to-peak output voltage                                         | At package pins after high-pass filter<br>(HPF) to remove DC component; HPF =<br>1/LPF; No AC or DC signals are applied<br>at RX terminals; | 0     |      | 10      | mV    |

| V <sub>TX-IDLE-</sub><br>DIFF-DC                    | DC electrical idle differential output voltage                                                      | At package pins after low-pass filter (LPF)<br>to remove AC component; LPF = 1/HPF;<br>No AC or DC signals are applied at RX<br>terminals;  | 0     |      | 10      | mV    |

| V <sub>TX-CM-</sub><br>DC-<br>ACTIVE-<br>IDLE-DELTA | Absolute DC common-mode voltage<br>between U1 and U0                                                | At package pin                                                                                                                              |       |      | 200     | mV    |

| R <sub>TX-DIFF</sub>                                | Differential impedance of the driver                                                                |                                                                                                                                             | 75    |      | 120     | Ω     |

| R <sub>TX-CM</sub>                                  | Common-mode impedance of the driver                                                                 | Measured with respect to AC ground over 0V to 500mV                                                                                         | 18    |      | 30      | Ω     |

## 5.5 Electrical Characteristics (continued)

over operating free-air temperature and voltage range (unless otherwise noted)

|                                | PARAMETER                                             | TEST CONDITIONS                                                                                                       | MIN   | TYP  | MAX | UNIT |

|--------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|

| C <sub>AC-</sub><br>COUPLING   | External AC-coupling capacitor                        |                                                                                                                       | 75    |      | 265 | nF   |

| I <sub>TX-SHORT</sub>          | TX short-circuit current                              | TX+/- shorted to GND                                                                                                  |       |      | 67  | mA   |

| RL <sub>TX-DIFF</sub>          | Differential return loss (SDD22)                      | 50MHz to 1.25GHz at 90Ω; Lowest EQ<br>setting; FLIP = L;                                                              |       | -25  |     | dB   |

| RL <sub>TX-</sub><br>DIFF-5G   | Differential return loss (SDD22)                      | 5GHz at 90Ω; Lowest EQ setting; FLIP = L;                                                                             | -12   |      | dB  |      |

| RL <sub>TX-CM</sub>            | Common-mode return loss (SCC22)                       | 50MHz to 5GHz at $90\Omega$ ; Lowest EQ setting; FLIP = L;                                                            | -9    |      | dB  |      |

| AC Electr                      | ical Characteristics                                  |                                                                                                                       |       |      |     |      |

| Crosstalk                      | Differential crosstalk between TX and RX signal pairs | At 5GHz; FLIP = L;                                                                                                    |       | -39  |     | dB   |

| G <sub>LF</sub>                | Low-frequency voltage gain.                           | At 100MHz, 600mVpp V <sub>ID</sub>                                                                                    | -0.25 | 0.6  | 1.5 | dB   |

| G <sub>LF_LFPS</sub><br>_TX1/2 | Low-frequency voltage gain for SSTX -> TX1/TX2 path   | At 10MHz to 50MHz sine wave; 1.0Vpp $V_{ID}$ ; EQ = 0; FLIP = 0 and 1;                                                | -0.5  | 0.8  | 1.6 | dB   |

| CP <sub>1 dB-LF</sub>          | Low-frequency –1dB compression point                  | At 100MHz, 200mVpp < V <sub>ID</sub> < 2000mVpp                                                                       |       | 1000 |     | mVpp |

| CP <sub>1 dB-HF</sub>          | High-frequency –1dB compression point                 | At 5GHz, 200mVpp < V <sub>ID</sub> < 2000mVpp                                                                         |       | 770  |     | mVpp |

| D <sub>J_10G</sub>             | TX output deterministic jitter                        | 200mVpp < V <sub>ID</sub> < 2000mVpp, PRBS7,<br>10Gbps, 10dB pre-channel and 1dB post-<br>channel, Optimal EQ setting |       | 0.07 |     | Ulpp |

# 5.6 Timing Requirements

|                                 |                                                                                                           | MIN | NOM | MAX | UNIT |

|---------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| USB3                            |                                                                                                           |     |     | I   |      |

| t <sub>IDLEEntry</sub> ,        | Delay from U0 to electrical idle                                                                          |     | 10  |     | ns   |

| t <sub>IDLEExit_U1</sub>        | U1 exit time: break in electrical idle to the transmission of LFPS                                        |     | 6   |     | ns   |

| t <sub>IDLEExit_U2U</sub><br>3  | U2/U3 exit time: break in electrical idle to transmission of LFPS                                         |     | 10  |     | μs   |

| t <sub>RXDET_INTV</sub>         | RX detect interval while in disconnect                                                                    |     |     | 12  | ms   |

| t <sub>IDLEExit_DIS</sub><br>C  | Disconnect exit time                                                                                      |     | 10  |     | μs   |

| t <sub>Exit_SHTDN</sub>         | Shutdown exit time (CTL0 = $V_{CC}/2$ to U2/U3)                                                           |     | 1   |     | ms   |

|                                 | Differential propagation delay (20% to 80% of differential voltage measured 1.7 inch from the output pin) |     |     | 300 | ps   |

| t <sub>PWRUPACTI</sub><br>VE    | Time when Vcc reaches 70% to device active                                                                |     |     | 1   | ms   |

| t <sub>R</sub> , t <sub>F</sub> | Output rise/fall time                                                                                     |     | 40  |     | ps   |

| t <sub>RF-MM</sub>              | Output rise/fall time mismatch (20% to 80% of differential voltage measured 1.7 inch from the output pin) |     |     | 5   | ps   |

# 5.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------|-----------------|-----|-----|-----|------|

| I <sup>2</sup> C (SDA | A and SCL)                                      |                 |     |     |     |      |

| f <sub>SCL</sub>      | I <sup>2</sup> C clock frequency                |                 |     |     | 1   | MHz  |

| t <sub>BUF</sub>      | Bus free time between START and STOP conditions |                 | 0.5 |     |     | μs   |

Copyright © 2024 Texas Instruments Incorporated

## 5.7 Switching Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                                                                             | TEST CONDITIONS | MIN   | TYP MAX | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------------|-----------------|-------|---------|------|

| t <sub>HDSTA</sub> | Hold time after repeated START<br>condition. After this period, the first clock<br>pulse is generated |                 | 0.26  |         | μs   |

| t <sub>LOW</sub>   | Low period of the I <sup>2</sup> C clock                                                              |                 | 0.5   |         | μs   |

| t <sub>HIGH</sub>  | High period of the I <sup>2</sup> C clock                                                             |                 | 0.26  |         | μs   |

| t <sub>SUSTA</sub> | Setup time for a repeated START condition                                                             |                 | 0.26  |         | μs   |

| t <sub>HDDAT</sub> | Data hold time                                                                                        |                 | 0.004 |         | μs   |

| t <sub>SUDAT</sub> | Data setup time                                                                                       |                 | 50    |         | ns   |

| t <sub>R</sub>     | Rise time of both SDA and SCL signals                                                                 |                 |       | 120     | ns   |

| t <sub>F</sub>     | Device output fall time for SDA                                                                       | 30pF load       | 0.7   | 5       | ns   |

| t <sub>SUSTO</sub> | Setup time for STOP condition                                                                         |                 | 0.26  |         | μs   |

| C <sub>b</sub>     | Capacitive load for each bus line                                                                     |                 |       | 100     | pF   |

## **5.8 Typical Characteristics**

# 5.8 Typical Characteristics (continued)

## **6** Parameter Measurement Information

Figure 6-4. Output Rise and Fall Times

# 7 Detailed Description

## 7.1 Overview

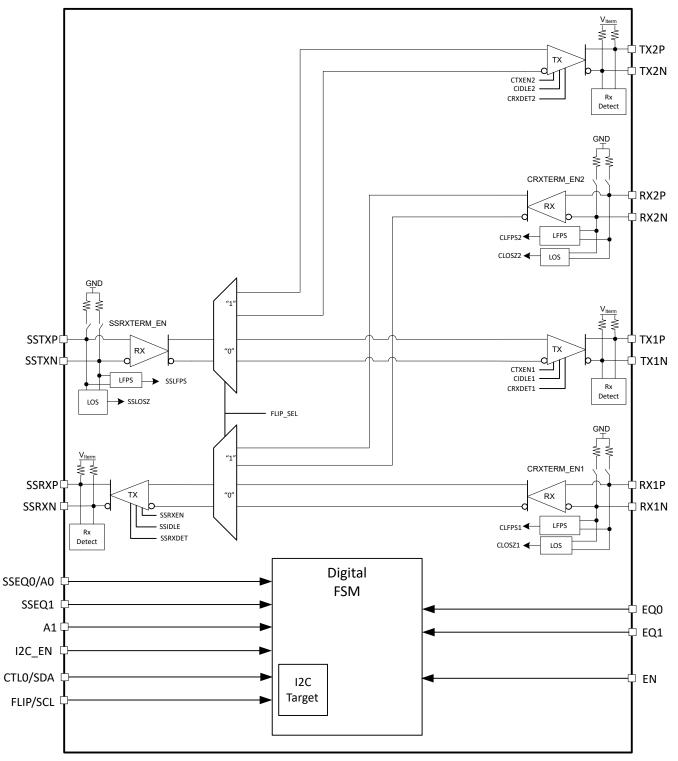

The TUSB1021-Q1 is a linear redriving switch that supports data rates up to 10Gbps. This device uses 5<sup>th</sup> generation USB redriver technology.

The TUSB1021-Q1 provides sixteen levels of receive equalization to compensate for cable and board trace loss which if not equalized causes inter-symbol interference (ISI) when USB 3.2 signals travel across a PCB or cable. This device requires a 3.3V power supply. The device comes in an automotive grade 2 temperature range.

The TUSB1021-Q1 enables the system to pass both transmitter compliance and receiver jitter tolerance tests for USB 3.2. The redriver recovers incoming data by applying equalization that compensates for channel loss, and drives out signals with a high differential voltage. Each channel has a receiver equalizer with selectable gain settings. Set the equalization based on the amount of insertion loss in the channels connected to the TUSB1021-Q1. Independent equalization control for each channel can be set using EQ[1:0] and SSEQ[1:0] pins.

The TUSB1021-Q1 advanced state machine makes the device transparent to hosts and devices. After power up, the TUSB1021-Q1 periodically performs receiver detection on the TX pairs. If the device detects a USB 3.2 receiver, the RX termination is enabled, and the TUSB1021-Q1 is ready to re-drive.

## 7.2 Functional Block Diagram

# 7.3 Feature Description

## 7.3.1 USB 3.2

The TUSB1021-Q1 supports USB 3.2 up to 10Gbps. The TUSB1021-Q1 supports all the USB defined power states (U0, U1, U2, and U3). The TUSB1021-Q1 is a linear redriver, therefore the TUSB1021-Q1 cannot decode

USB3.2 physical layer traffic. The TUSB1021-Q1 monitors the actual physical layer conditions like receiver termination, electrical idle, LFPS, and SuperSpeed signaling rate to determine the USB power state of the USB 3.2 interface.

The TUSB1021-Q1 features an intelligent low-frequency periodic signaling (LFPS) detector. The LFPS detector automatically senses the low-frequency signals and disables receiver equalization functionality. When not receiving LFPS, the TUSB1021-Q1 enables receiver equalization based on the EQ[1:0] and SSEQ[1:0] pins or values programmed into EQ1\_SEL, EQ2\_SEL, and SSEQ\_SEL registers.

#### 7.3.2 4-Level Inputs

The TUSB1021-Q1 has (I2C\_EN, EQ[1:0], and SSEQ[1:0]) 4-level inputs pins that are used to control the equalization gain and place TUSB1021-Q1 into different modes of operation. These 4-level inputs use a resistor divider to help set the four valid levels and provide a wider range of control settings. There is an internal  $35k\Omega$  pullup and a  $95k\Omega$  pulldown. These resistors, together with the external resistor connection combine to achieve the desired voltage level.

| LEVEL | SETTINGS                              |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|

| 0     | Tie 1kΩ 5% to GND                     |  |  |  |  |

| R     | Tie 20kΩ 5% to GND                    |  |  |  |  |

| F     | Float (leave pin open)                |  |  |  |  |

| 1     | Tie 1k $\Omega$ 5% to V <sub>CC</sub> |  |  |  |  |

#### Table 7-1. 4-Level Control Pin Settings

#### Note

All 4-level inputs are latched after the rising edge of internal reset. After  $t_{cfg_hd}$ , the internal pullup and pulldown resistors are isolated to save power.

#### 7.3.3 Receiver Linear Equalization

The purpose of receiver equalization is to compensate for channel insertion loss and the resulting inter-symbol interference in the system before the input or after the output of the TUSB1021-Q1. The receiver overcomes these losses by attenuating the low-frequency components of the signals with respect to the high-frequency components. Select the proper gain setting to match the channel insertion loss. Two 4-level input pins enable up to 16 possible equalization settings. USB3.2 upstream path and USB3.2 downstream path each have two 4-level inputs. The TUSB1021-Q1 also provides the flexibility of adjusting settings through l<sup>2</sup>C registers.

#### 7.4 Device Functional Modes

### 7.4.1 USB 3.2 2:1 MUX Description

The TUSB1021-Q1 implements a 2:1 MUX between the USB-C receptacle and the USB 3.2 host, hub, or device. In pin-strap mode the selection of MUX path is controlled from the FLIP pin. In I<sup>2</sup>C mode, the MUX is controlled by FLIP\_SEL register.

| FLIP PIN OR FLIP_SEL REGISTER | CTL0 PIN OR CTLSEL REGISTER | USB PATH               |

|-------------------------------|-----------------------------|------------------------|

| X                             | 0                           | Disabled               |

| 0                             | 1                           | $RX1 \rightarrow SSRX$ |

| 0                             |                             | $SSTX \rightarrow TX1$ |

| 1                             | 1                           | $RX2 \rightarrow SSRX$ |

|                               | I                           | $SSTX \rightarrow TX2$ |

#### Table 7-2. USB 3.2 MUX Control

#### 7.4.2 Linear EQ Configuration

Each of the TUSB1021-Q1 receiver lanes has individual controls for receiver equalization. The receiver equalization gain value can be controlled either through I<sup>2</sup>C registers or through GPIOs. The following table details the gain value for each available combination when TUSB1021-Q1 is in GPIO mode. These same options are also available in I<sup>2</sup>C mode by updating registers EQ1\_SEL, EQ2\_SEL, and SSEQ\_SEL. Each of the 4-bit EQ configuration registers is mapped to the configuration pins as follows:  $x_SEL = \{x1[1:0], x0[1:0]\}$  where xn[1:0] are the EQ configuration pins with pin levels mapped to 2-bit values as: 0 = 00, R = 01, F = 10, 1 = 11.

| EQUALIZATION |               | RX1 and RX2 PORTS |                         |                 | SSTX PORT       |                      |

|--------------|---------------|-------------------|-------------------------|-----------------|-----------------|----------------------|

| SETTING #    | EQ1 PIN LEVEL | EQ0 PIN LEVEL     | EQ GAIN AT 5GHz<br>(dB) | SSEQ1 PIN LEVEL | SSEQ0 PIN LEVEL | EQ GAIN AT 5GHz (dB) |

| 0            | 0             | 0                 | 0.4                     | 0               | 0               | -2.4                 |

| 1            | 0             | R                 | 2.6                     | 0               | R               | -0.2                 |

| 2            | 0             | F                 | 4.2                     | 0               | F               | 1.3                  |

| 3            | 0             | 1                 | 5.7                     | 0               | 1               | 2.8                  |

| 4            | R             | 0                 | 6.7                     | R               | 0               | 3.8                  |

| 5            | R             | R                 | 7.9                     | R               | R               | 4.9                  |

| 6            | R             | F                 | 8.7                     | R               | F               | 5.8                  |

| 7            | R             | 1                 | 9.5                     | R               | 1               | 6.6                  |

| 8            | F             | 0                 | 10.2                    | F               | 0               | 7.3                  |

| 9            | F             | R                 | 10.9                    | F               | R               | 7.9                  |

| 10           | F             | F                 | 11.4                    | F               | F               | 8.4                  |

| 11           | F             | 1                 | 11.9                    | F               | 1               | 8.9                  |

| 12           | 1             | 0                 | 12.2                    | 1               | 0               | 9.3                  |

| 13           | 1             | R                 | 12.6                    | 1               | R               | 9.7                  |

| 14           | 1             | F                 | 12.9                    | 1               | F               | 10.0                 |

| 15           | 1             | 1                 | 13.3                    | 1               | 1               | 10.5                 |

| Table 7-3. TUSB1021-Q1 Receiver Ed | qualization GPIO Control |

|------------------------------------|--------------------------|

|------------------------------------|--------------------------|

#### 7.4.3 USB3.2 Modes

The TUSB1021-Q1 monitors the physical layer conditions like receiver termination, electrical idle, LFPS, and SuperSpeed signaling rate to determine the state of the USB3.2 interface. Depending on the state of the USB 3.2 interface, the TUSB1021-Q1 can be in one of four primary modes of operation when USB 3.2 is enabled (CTL0 = H or CTLSEL0 = 1b1): Disconnect, U2/U3, U1, and U0.

The Disconnect mode is the state in which TUSB1021-Q1 has not detected far-end termination on upstream facing port (UFP) or downstream facing port (DFP). The Disconnect mode is the lowest power mode of each of the four modes. The TUSB1021-Q1 remains in this mode until far-end receiver termination has been detected on both UFP and DFP. The TUSB1021-Q1 immediately exits this mode and enter U0 after far-end termination is detected.

When in U0 mode, the TUSB1021-Q1 redrives all traffic received on UFP and DFP. U0 is the highest power mode of all USB3.1 modes. The TUSB1021-Q1 remains in U0 mode until electrical idle occurs on both UFP and DFP. Upon detecting electrical idle, the TUSB1021-Q1 immediately transitions to U1.

The U1 mode is the intermediate mode between U0 mode and U2/U3 mode. In U1 mode, the TUSB1021-Q1 UFP and DFP receiver termination remains enabled. The UFP and DFP transmitter DC common mode is maintained. The power consumption in U1 is similar to power consumption of U0.

Next to the Disconnect mode, the U2/U3 mode is next lowest power state. While in this mode, the TUSB1021-Q1 periodically performs far-end receiver detection. Anytime the far-end receiver termination is not detected on either UFP or DFP, the TUSB1021-Q1 leaves the U2/U3 mode and transitions to the Disconnect mode. The device also monitors for a valid LFPS. Upon detection of a valid LFPS, the TUSB1021-Q1 immediately transitions to the U0 mode. In U2/U3 mode, the TUSB1021-Q1 receiver terminations remain enabled but the TX DC common-mode voltage is not maintained.

Copyright © 2024 Texas Instruments Incorporated

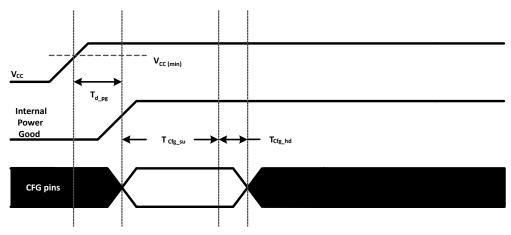

#### 7.4.4 Operation Timing – Power Up

Figure 7-1. Power-Up Timing

#### Table 7-4. Power-Up Timing <sup>(1)</sup> <sup>(2)</sup>

|                       | PARAMETER                                                      | MIN | MAX | UNIT |

|-----------------------|----------------------------------------------------------------|-----|-----|------|

| t <sub>d_pg</sub>     | $V_{\text{CC}}$ (minimum) to Internal Power Good asserted high |     | 500 | μs   |

| t <sub>cfg_su</sub>   | CFG <sup>(1)</sup> pins setup <sup>(2)</sup>                   | 50  |     | μs   |

| t <sub>cfg_hd</sub>   | CFG <sup>(1)</sup> pins hold                                   | 10  |     | μs   |

| t <sub>VCC_RAMP</sub> | V <sub>CC</sub> supply ramp requirement (10% to 90%)           | 0.1 | 50  | ms   |

(1) Following pins comprise CFG pins: I2C\_EN, EQ[1:0], and SSEQ[1:0].

(2) Recommend CFG pins are stable when  $V_{CC}$  is at minimum value.

## 7.5 Programming

For further programmability, the TUSB1021-Q1 can be controlled using  $I^2C$ . The SCL and SDA pins are used for  $I^2C$  clock and  $I^2C$  data respectively.

| A1<br>PIN LEVEL | SSEQ0/A0<br>PIN LEVEL | BIT 7 (MSB) | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 (W/R) |

|-----------------|-----------------------|-------------|-------|-------|-------|-------|-------|-------|-------------|

| 0               | 0                     | 1           | 0     | 0     | 0     | 1     | 0     | 0     | 0/1         |

| 0               | R                     | 1           | 0     | 0     | 0     | 1     | 0     | 1     | 0/1         |

| 0               | F                     | 1           | 0     | 0     | 0     | 1     | 1     | 0     | 0/1         |

| 0               | 1                     | 1           | 0     | 0     | 0     | 1     | 1     | 1     | 0/1         |

| R               | 0                     | 0           | 1     | 0     | 0     | 0     | 0     | 0     | 0/1         |

| R               | R                     | 0           | 1     | 0     | 0     | 0     | 0     | 1     | 0/1         |

| R               | F                     | 0           | 1     | 0     | 0     | 0     | 1     | 0     | 0/1         |

| R               | 1                     | 0           | 1     | 0     | 0     | 0     | 1     | 1     | 0/1         |

| F               | 0                     | 0           | 0     | 1     | 0     | 0     | 0     | 0     | 0/1         |

| F               | R                     | 0           | 0     | 1     | 0     | 0     | 0     | 1     | 0/1         |

| F               | F                     | 0           | 0     | 1     | 0     | 0     | 1     | 0     | 0/1         |

| F               | 1                     | 0           | 0     | 1     | 0     | 0     | 1     | 1     | 0/1         |

| 1               | 0                     | 0           | 0     | 0     | 1     | 1     | 0     | 0     | 0/1         |

| 1               | R                     | 0           | 0     | 0     | 1     | 1     | 0     | 1     | 0/1         |

| 1               | F                     | 0           | 0     | 0     | 1     | 1     | 1     | 0     | 0/1         |

| 1               | 1                     | 0           | 0     | 0     | 1     | 1     | 1     | 1     | 0/1         |

#### Table 7-5. TUSB1021-Q1 I<sup>2</sup>C Target Address

## 7.5.1 TUSB1021-Q1 I<sup>2</sup>C Target Behavior

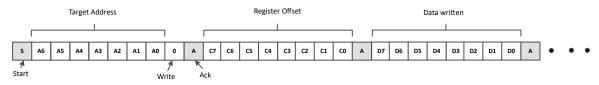

Figure 7-2. I<sup>2</sup>C Write with Data

Use the following procedure to write data to TUSB1021-Q1 I<sup>2</sup>C registers (refer to Figure 7-2):

- 1. The controller initiates a write operation by generating a start condition (S), followed by the TUSB1021-Q1 7-bit address and a zero-value W/R bit to indicate a write cycle.

- 2. The TUSB1021-Q1 acknowledges the address cycle.

- 3. The controller presents the register offset within TUSB1021-Q1 to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB1021-Q1 acknowledges the sub-address cycle.

- 5. The controller presents the first byte of data to be written to the  $I^2C$  register.

- 6. The TUSB1021-Q1 acknowledges the byte transfer.

- 7. The controller can continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the TUSB1021-Q1.

- 8. The controller terminates the write operation by generating a stop condition (P).

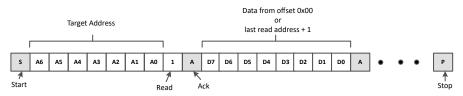

Figure 7-3. I<sup>2</sup>C Read Without Repeated Start

Use the following procedure to read the TUSB1021-Q1 I<sup>2</sup>C registers without a repeated Start (refer Figure 7-3).

- 1. The controller initiates a read operation by generating a start condition (S), followed by the TUSB1021-Q1 7-bit address and a zero-value W/R bit to indicate a read cycle.

- 2. The TUSB1021-Q1 acknowledges the 7-bit address cycle.

- 3. Following the acknowledge the controller continues sending clock.

- 4. The TUSB1021-Q1 transmit the contents of the memory registers MSB-first starting at register 00h or last read register offset+1. If a write to the l<sup>2</sup>C register occurred prior to the read, then the TUSB1021-Q1 shall start at the register offset specified in the write.

- 5. The TUSB1021-Q1 waits for either an acknowledge (ACK) or a not-acknowledge (NACK) from the controller after each byte transfer; the I<sup>2</sup>C controller acknowledges reception of each data byte transfer.

- 6. If an ACK is received, the TUSB1021-Q1 transmits the next byte of data as long as controller provides the clock. If a NAK is received, the TUSB1021-Q1 stops providing data and waits for a stop condition (P).

- 7. The controller terminates the write operation by generating a stop condition (P).

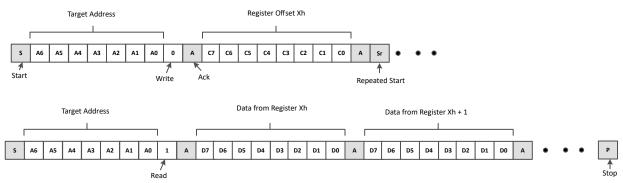

Figure 7-4. I<sup>2</sup>C Read with Repeated Start

Use the following procedure to read the TUSB1021-Q1 I<sup>2</sup>C registers with a repeated Start (refer Figure 7-4).

- 1. The controller initiates a read operation by generating a start condition (S), followed by the TUSB1021-Q1 7-bit address and a zero-value W/R bit to indicate a write cycle.

- 2. The TUSB1021-Q1 acknowledges the 7-bit address cycle.

- 3. The controller presents the register offset within TUSB1021-Q1 to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB1021-Q1 acknowledges the register offset cycle.

- 5. The controller presents a repeated start condition (Sr).

- 6. The controller initiates a read operation by generating a start condition (S), followed by the TUSB1021-Q1 7-bit address and a one-value W/R bit to indicate a read cycle.

- 7. The TUSB1021-Q1 acknowledges the 7-bit address cycle.

- 8. The TUSB1021-Q1 transmit the contents of the memory registers MSB-first starting at the register offset.

- 9. The TUSB1021-Q1 shall wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the controller after each byte transfer; the I<sup>2</sup>C controller acknowledges reception of each data byte transfer.

- 10. If an ACK is received, the TUSB1021-Q1 transmits the next byte of data as long as controller provides the clock. If a NAK is received, the TUSB1021-Q1 stops providing data and waits for a stop condition (P).

- 11. The controller terminates the read operation by generating a stop condition (P).

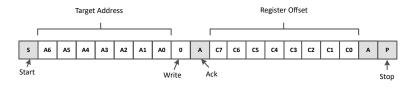

Figure 7-5. I<sup>2</sup>C Write Without Data

Use the following procedure to set a starting sub-address for I<sup>2</sup>C reads (refer to Figure 7-5).

- 1. The controller initiates a write operation by generating a start condition (S), followed by the TUSB1021-Q1 7-bit address and a zero-value W/R bit to indicate a write cycle.

- 2. The TUSB1021-Q1 acknowledges the address cycle.

- 3. The controller presents the register offset within TUSB1021-Q1 to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB1021-Q1 acknowledges the register offset cycle.

- 5. The controller terminates the write operation by generating a stop condition (P).

#### Note

After initial power up, if no register offset is included for the read procedure (refer to Figure 7-3), then reads start at register offset 00h and continue byte by byte through the registers until the  $I^2C$  controller terminates the read operation. During a read operation, the TUSB1021-Q1 auto-increments the  $I^2C$  internal register address of the last byte transferred independent of whether or not an ACK was received from the  $I^2C$  controller.

Software must only access (read or write) addresses detailed in this document. Accessing reserved or undocumented addresses can result in TUSB1021-Q1 entering an undefined state.

# 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 8.1 Application Information

The TUSB1021-Q1 is a linear redriver designed specifically to compensate for intersymbol interference (ISI) jitter causes by signal attenuation through a passive medium like PCB traces or cables. Placing the TUSB1021-Q1 between the USB connector and a USB 3.2 host, hub, and device can correct signal integrity issues resulting in a more robust system.

#### 8.2 Typical Application

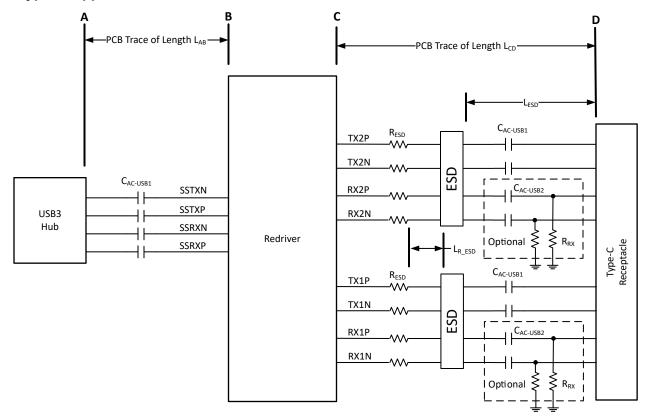

Figure 8-1. TUSB1021-Q1 in a Host Application

#### 8.2.1 Design Requirements

For this design example, use the parameters shown in Table 8-1.

| PARAMETER <sup>(1)</sup>                                                             | VALUE                                                                                                            |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Pre-channel A to B PCB trace length, L <sub>AB</sub> . Refer to Figure 8-1.          | 1 inches $\leq L_{AB} \leq 9$ inches $-L_{CD}$                                                                   |

| Post-channel C to D PCB trace length, L <sub>CD</sub> . Refer to Figure 8-1.         | up to 3 inches                                                                                                   |

| Maximum distance of ESD component from the USB receptacle, $L_{ESD}$                 | 1.0 inches                                                                                                       |

| Maximum distance of series resistor ( $R_{ESD}$ ) from ESD component, $L_{R\_ESD}$ . | 0.25 inches                                                                                                      |

| C <sub>AC-USB1</sub> AC-coupling capacitor (75nF to 265nF)                           | 220nF                                                                                                            |

| C <sub>AC-USB2</sub> AC-coupling capacitor (297nF to 363nF)                          | Options:<br>• RX1 and RX2 are DC-coupled to USB<br>receptacle<br>• 330nF AC-couple with R <sub>RX</sub> resistor |

| Optional $R_{RX}$ resistor (220k $\Omega \pm 5\%$ )                                  | Not used                                                                                                         |

| Optional $R_{ESD}$ (0 $\Omega$ to 2.2 $\Omega$ )                                     | 00                                                                                                               |

| V <sub>CC</sub> supply (3V to 3.6V)                                                  | 3.3V                                                                                                             |

| I <sup>2</sup> C Mode or Pin-strap Mode                                              | l <sup>2</sup> C Mode. (MODE = "F")                                                                              |

| 1.8V or 3.3V I <sup>2</sup> C Interface                                              | 3.3V I <sup>2</sup> C. VIO_SEL pin to Float "F".                                                                 |

#### Table 8-1. Design Parameters

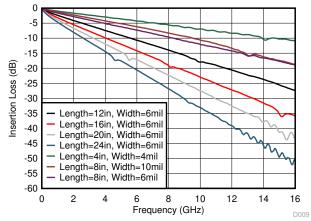

(1) Maximum trace length assumes an insertion loss of 0.2dB/inch/GHz. If insertion loss is more than 0.2dB/inch/GHz, then maximum trace length must be reduced accordingly.

#### 8.2.2 Detailed Design Procedure

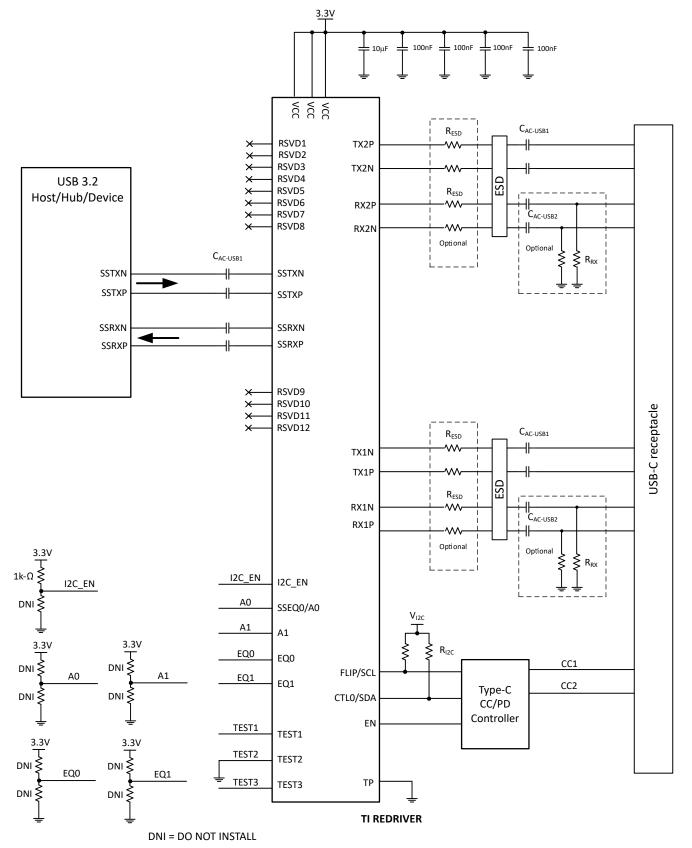

Figure 8-2 shows a typical usage of the TUSB1021-Q1 device. The device can be controlled either through the GPIO pins or the I<sup>2</sup>C interface. In the example shown below, a Type-C PD controller is used to configure the device through the I<sup>2</sup>C interface. In I<sup>2</sup>C mode, the equalization settings for each receiver can be independently controlled through I<sup>2</sup>C registers. For this reason, all of the equalization pins (EQ[1:0], SSEQ[1:0]) can be left unconnected. If these pins are left unconnected, the TUSB1021-Q1 7-bit I<sup>2</sup>C target address is 0x12 because both A1 and SSEQ0/A0 are at pin level "F". If a different I<sup>2</sup>C target address is desired, set the A1 and SSEQ0/A0 pins to a level which produces the desired I<sup>2</sup>C target address.

2Ω

#### 8.2.2.1 ESD Protection

It may be necessary to incorporate an ESD component to protect the TUSB1021-Q1 from electrostatic discharge (ESD). TI recommends following the ESD protection recommendations listed in Table 8-2. A clamp voltage greater than value specified in Table 8-2 may require a R<sub>ESD</sub> on each differential pin. Place the ESD component near the USB connector.

| PARAMETER                                                       | RECOMMENDATION               |

|-----------------------------------------------------------------|------------------------------|

| Breakdown voltage                                               | ≥ 3.5V                       |

| 1/0 line conscitones                                            | Data rates ≤ 5Gbps: ≤ 0.50pF |

| I/O line capacitance                                            | Data rates > 5Gbps: ≤ 0.35pF |

| Delta capacitance between any P and N I/O pins                  | ≤ 0.07pF                     |

| Clamping voltage at 8A I <sub>PP</sub> IO to GND <sup>(1)</sup> | ≤ 4.5V                       |

| Typical dynamic resistance                                      | ≤ 30mΩ                       |

#### Table 8-2. ESD Diodes Recommended Characteristics

#### (1) According to IEC 61000-4-5 (8/20µs current waveform)

| Table 8-3. Recommended ESD Protection Component |                |                                                        |  |  |  |  |  |  |  |

|-------------------------------------------------|----------------|--------------------------------------------------------|--|--|--|--|--|--|--|

| MANUFACTURER                                    | PART NUMBER    | R <sub>ESD</sub> TO SUPPORT IEC 61000-4-2 CONTACT ±8kV |  |  |  |  |  |  |  |

| Nexperia                                        | PUSB3FR4       | 1Ω                                                     |  |  |  |  |  |  |  |

| Nexperia                                        | PESD2V8Y1BSF   | 1Ω                                                     |  |  |  |  |  |  |  |

| Texas Instruments                               | TPD1E04U04DPLR | 2Ω                                                     |  |  |  |  |  |  |  |

TPD4E02B04DQAR

#### 8.2.3 Application Curve

**Texas Instruments**

Figure 8-3. Insertion Loss of FR4 PCB Traces

#### 8.3 Power Supply Recommendations

The TUSB1021-Q1 is designed to operate with a 3.3V power supply. Do not use levels above those listed in *Recommended Operating Conditions*. If using a higher voltage system power supply, a voltage regulator can be used to step down to 3.3V. Use decoupling capacitors to reduce noise and improve power supply integrity. Use a  $0.1\mu$ F capacitor on each power pin.

#### 8.4 Layout

#### 8.4.1 Layout Guidelines

- 1. Reroute the RXP/N and TXP/N with controlled  $90\Omega$  differential impedance (±15%).

- 2. Keep away from other high speed signals.

- 3. Keep the intra-pair routing to within 2 mils.

Copyright © 2024 Texas Instruments Incorporated

- 4. Place length matching near the location of mismatch.

- 5. Separate each pair by at least 3 times the signal trace width.

- 6. Keep the use of bends in differential traces to a minimum. When bends are used, make sure to keep the number of left and right bends as equal as possible and the angle of the bend ≥ 135 degrees. This minimizes any length mismatch causes by the bends and therefore minimizes the impact bends have on EMI.

- 7. Route all differential pairs on the same of layer.

- 8. Keep the number of vias to a minimum. TI recommends to keep the via count to 2 or less.

- 9. Keep traces on layers adjacent to ground plane.

- 10. Do NOT route differential pairs over any plane split.

- 11. Note that adding test points can cause impedance discontinuity, and therefore negatively impact signal performance. If test points are used, place the points in series and symmetrically. The points must not be placed in a manner that causes a stub on the differential pair.

#### 8.4.2 Layout Example

Figure 8-4. Layout Example

# 9 Register Maps

## Table 9-1. Register Legend

| ACCESS TAG | NAME      | MEANING                                                                                |

|------------|-----------|----------------------------------------------------------------------------------------|

| R          | Read      | The field may be read by software                                                      |

| W          | Write     | The field may be written by software                                                   |

| S          | Set       | The field may be set by a write of one. Writes of zeros to the field have no effect.   |

| С          | Clear     | The field may be cleared by a write of one. Write of zero to the field have no effect. |

| U          | Update    | Hardware may autonomously update this field.                                           |

| NA         | No Access | Not accessible or not applicable                                                       |

## 9.1 General Register (address = 0x0A) [reset = 00000001]

## Figure 9-1. General Registers

| 7    | 6       | 5        | 4           | 3        | 2        | 1        | 0      |

|------|---------|----------|-------------|----------|----------|----------|--------|

| Rese | erved   | Reserved | EQ_OVERRIDE | Reserved | FLIP_SEL | Reserved | CTLSEL |

| F    | R R R/W |          | R/W         | R/W      | R/W      | R/       | W      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset