# How to Co-Layout Three Common SOT-563 Package **Pinouts**

Lucia Gao, Bruce Lu, Edwin Zang

#### **ABSTRACT**

Buck converter applications commonly require co-layout between devices with different pinouts due to the design flexibility this provides. This application note focuses on how to co-layout among three types of SOT-563 packages. First, the pinout of TPS56x252/7, TPS56x242/7, TPS56x243/6 and TPS56x203/6 are compared. Next, the schematic design is introduced. Finally, this application design is verified based on experiments.

#### **Table of Contents**

| 10.000 01 00.000                                                |   |

|-----------------------------------------------------------------|---|

| 1 Introduction                                                  |   |

| 2 Comparison of Pinout                                          | 2 |

| 3 Schematic Diagram                                             | 3 |

| 3.1 How to Co-layout Among Three Types of SOT-563               | 3 |

| 3.2 How to Co-Layout Between TPS56x252/7 and TPS56x242/7        | 4 |

| 3.3 How to Co-layout Between TPS56x252/7 and TPS56x203/6        |   |

| 3.4 How to Co-Layout Between TPS56x242/7 and TPS56x203/6        |   |

| 4 Experimental Results                                          |   |

| 5 Summary                                                       | 6 |

| 6 References                                                    | 6 |

| 7 Revision History                                              | 6 |

|                                                                 |   |

| List of Figures                                                 |   |

| Figure 2-1. TPS56x243/6 and TPS56x203/6 Pinout                  | 2 |

| Figure 2-2. TPS56x242/7 Pinout                                  | 2 |

| Figure 2-3. TPS56x252/7 Pinout                                  | 2 |

| Figure 3-1. Co-layout Schematic Among Three Types of SOT-563    |   |

| Figure 3-2. Co-Layout Schematic for TPS56x252/7 and TPS56x242/7 |   |

| Figure 3-3. Co-layout Schematic for TPS56x252/7 and TPS56x203/6 |   |

| Figure 3-4. Co-Layout Schematic for TPS56x242/7 and TPS56x203/6 |   |

| Figure 4-1. TPS564242 12V Input to 1.05V Output at 4A           |   |

| Figure 4-2. TPS563203 12V Input to 1.05V Output at 3A           |   |

| Figure 4-3. TPS563252 12V Input to 1.05V Output at 3A           | 6 |

|                                                                 |   |

| List of Tables                                                  |   |

| Table 2-1. Pin Functions                                        |   |

| Table 3-1. Solder Information for Different Part                |   |

| Table 3-2. Comparison of EN Pin Configuration                   |   |

| Table 3-3. Solder Information for TPS56x252/7 and TPS56x203/6   |   |

| Table 3-4. Solder Information for TPS56x242/7 and TPS56x203/6   | 5 |

| Trademarks                                                      |   |

|                                                                 |   |

D-CAP3<sup>™</sup> is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

The TPS56x252/7, TPS56x242/7, TPS56x243/6 and TPS56x203/6 are all single output, adaptive on-time, D-CAP3<sup>™</sup> control mode, synchronous buck converters that require very low external component count in SOT-563 packages. However, the pinout for each device is slightly different. This application note mainly discusses how to do co-layout among TPS56x252/7, TPS56x242/7, TPS56x243/6 and TPS56x203/6.

# **2 Comparison of Pinout**

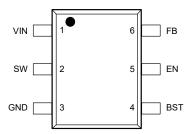

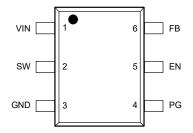

The TPS56x243/6 and TPS56x203/6 pinout with SOT-563 package is shown in Figure 2-1. TPS56x243/6 and TPS56x203/6 pinout is quite common in the industry. The TPS56x242/7 pinout with SOT-563 package, which has been optimized is shown in Figure 2-2. This pinout integrates BST capacitor and adds AGND for pin 4. The TPS56x252/7 pinout with SOT-563 package is shown in Figure 2-3. This pinout integrates BST capacitor and add PG for pin 4. These three device families have the same pin functionality aside from pin 4 as shown in Table 2-1. With compatible external circuitry, co-layout can be achieved for the three packages.

Figure 2-1. TPS56x243/6 and TPS56x203/6 Pinout

Figure 2-2. TPS56x242/7 Pinout

Figure 2-3. TPS56x252/7 Pinout

**Table 2-1. Pin Functions**

| Pin |      | Description                                                                                                |  |  |  |

|-----|------|------------------------------------------------------------------------------------------------------------|--|--|--|

| No. | Name | - Description                                                                                              |  |  |  |

| 1   | VIN  | Input voltage supply pin. Connect the input decoupling capacitors between VIN and GND.                     |  |  |  |

| 2   | SW   | Switch node pin. Connect the output inductor to this pin.                                                  |  |  |  |

| 3   | GND  | GND pin source terminal of the low-side power NFET as well as the ground terminal for controller circuit   |  |  |  |

| 4   | PG   | Open-drain power-good indicator.                                                                           |  |  |  |

|     | AGND | Ground of the internal analog circuitry. Connect AGND to the GND plane.                                    |  |  |  |

|     | BST  | Supply input for the high-side NFET gate driver circuit. Connect 0.1-uF capacitor between BST and SW pins. |  |  |  |

| 5   | EN   | Enable input control. Driving EN high enables the converter.                                               |  |  |  |

| 6   | FB   | Converter feedback input. Connect to the output voltage with a feedback resistor divider.                  |  |  |  |

www.ti.com Schematic Diagram

## 3 Schematic Diagram

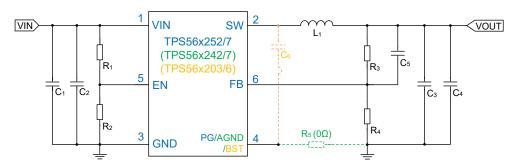

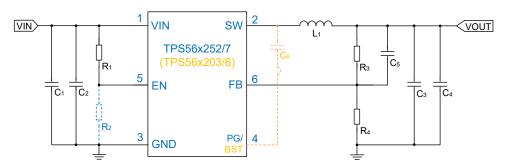

#### 3.1 How to Co-layout Among Three Types of SOT-563

Since pin 4 definitions are different for TPS56x252/7, TPS56x242/7, and TPS56x203/6, the compatible schematic is designed to achieve co-lay. The co-lay schematic is shown in Figure 3-1. There are several differences for the BOM, also note that TPS56x203/6 allows EN pin to connect to Vin by only one pullup resistor. The solder information for different parts is shown in Table 3-1. The comparison of EN pin configuration is shown in Table 3-2.

Figure 3-1. Co-layout Schematic Among Three Types of SOT-563

Table 3-1. Solder Information for Different Part

| Part Number | Description                                                                                                                                                                                                                            |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TPS56x252/7 | <ol> <li>If PG function is not needed, PG can be floating or connected with GND. PG tied to GND can get better thermal performance.</li> <li>C<sub>6</sub> needs to be floating. R<sub>5</sub> can be soldered or floating.</li> </ol> |  |  |

|             | 3. EN pin max voltage is 6V, need two voltage divider resistors.                                                                                                                                                                       |  |  |

| TPS56x242/7 | <ol> <li>R<sub>5</sub> needs to be soldered to connect AGND to GND.</li> <li>C<sub>6</sub> needs to be floating.</li> <li>EN pin max voltage is 6V, need two voltage divider resistors.</li> </ol>                                     |  |  |

| TPS56x203/6 | <ol> <li>C<sub>6</sub> needs to be tied to SW.</li> <li>R<sub>5</sub> needs to be floating.</li> </ol>                                                                                                                                 |  |  |

|             | 3. EN pin max voltage is 6V, allow two voltage resistors or one 100k pullup resistor.                                                                                                                                                  |  |  |

Table 3-2. Comparison of EN Pin Configuration

| · · · · · · · · · · · · · · · · · · ·          |                     |           |             |             |

|------------------------------------------------|---------------------|-----------|-------------|-------------|

| Part Number                                    | TPS56325x/TPS56425x | TPS562242 | TPS56x203/6 | TPS56x242/7 |

| EN Default Status                              | Low                 | High      | Low         | Low         |

| EN ABS Voltage                                 | 6V                  | 6V        | 6V          | 6V          |

| If Have A Zener Diode in<br>Internal EN Pin    | No                  | No        | Yes         | No          |

| Support only 100k top resistor directly to Vin | No                  | No        | Yes         | No          |

Schematic Diagram Www.ti.com

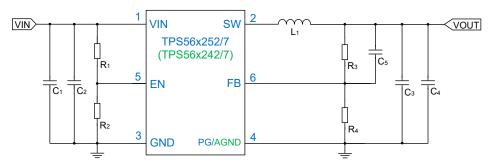

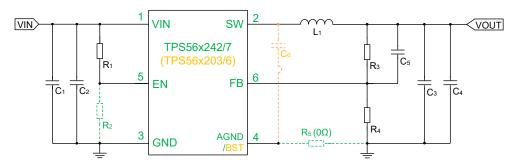

#### 3.2 How to Co-Layout Between TPS56x252/7 and TPS56x242/7

The co-lay schematic for TPS56x252/7 and TPS56x242/7 is shown in Figure 3-2. If PG function of TPS56x252/7 is not used, then PG of TPS56x252/7 can be directly connected with GND and TPS56x252/7 and TPS56x242/7 are exactly pin to pin.

Figure 3-2. Co-Layout Schematic for TPS56x252/7 and TPS56x242/7

#### 3.3 How to Co-layout Between TPS56x252/7 and TPS56x203/6

The co-lay schematic for TPS56x252/7 and TPS56x203/6 is shown in Figure 3-3. The solder information for TPS56x252/7 and TPS56x202/7 is shown in Table 3-3.

Figure 3-3. Co-layout Schematic for TPS56x252/7 and TPS56x203/6

Table 3-3. Solder Information for TPS56x252/7 and TPS56x203/6

| Part Number | Description                                                                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS56x252/7 | <ol> <li>If PG function is not needed, PG can be floating or connected with GND.</li> <li>C<sub>6</sub> needs to be floating.</li> <li>EN pin max voltage is 6V, need two voltage divider resistors.</li> </ol> |

| TPS56x203/6 | <ol> <li>C<sub>6</sub> needs to be tied to SW.</li> <li>EN pin max voltage is 6V, allow two voltage resistors or one 100k pullup resistor.</li> </ol>                                                           |

www.ti.com Schematic Diagram

## 3.4 How to Co-Layout Between TPS56x242/7 and TPS56x203/6

The co-lay schematic for TPS56x242/7 and TPS56x203/6 is shown in Figure 3-4. The solder information for TPS56x242/7 and TPS56x203/6 is shown in Table 3-4.

Figure 3-4. Co-Layout Schematic for TPS56x242/7 and TPS56x203/6

Table 3-4. Solder Information for TPS56x242/7 and TPS56x203/6

| Part Number | Description                                                                           |

|-------------|---------------------------------------------------------------------------------------|

| TPS56x242/7 | 1. R <sub>5</sub> needs to be soldered to connect AGND to GND.                        |

|             | 2. C <sub>6</sub> needs to be floating.                                               |

|             | 3. EN pin max voltage is 6V, need two voltage divider resistors.                      |

| TPS56x203/6 | 1. C <sub>6</sub> needs to be tied to SW.                                             |

|             | 2. R <sub>5</sub> needs to be floating.                                               |

|             | 3. EN pin max voltage is 6V, allow two voltage resistors or one 100k pullup resistor. |

**STRUMENTS** Experimental Results www.ti.com

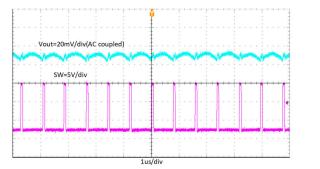

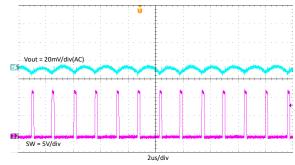

# 4 Experimental Results

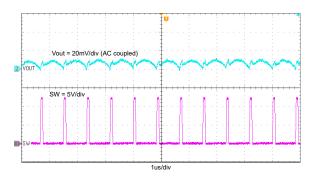

Figure 4-1, Figure 4-2, and Figure 4-3 are tested at 12V input voltage, 1.05V output voltage. All three devices work stably in steady state operation.

Figure 4-1. TPS564242 12V Input to 1.05V Output at Figure 4-2. TPS563203 12V Input to 1.05V Output at

Figure 4-3. TPS563252 12V Input to 1.05V Output at 3A

# **5 Summary**

This application note introduces how to co-layout among TPS56x252/7, TPS56x242/7, and TPS56x203/6 with SOT-563 package, which helps simplify the power design. Pinout is also compared and compatible schematic recommendations are given. Finally, the experiment verification results of the co-layout design proves all three devices can work stably in steady state operation.

#### 6 References

- Texas Instruments, TPS56325x 3V to 16V Input, 3A Synchronous Buck Converters in SOT-563 Package data sheet.

- Texas Instruments, TPS56524x 3V to 16V Input Voltage, 5A Synchronous Buck Converter in SOT-563 Package data sheet.

- Texas Instruments, TPS56424x 3V to 16V Input Voltage, 4A Synchronous Buck Converter in SOT-563 Package data sheet.

- Texas Instruments, TPS56320x 4.2V to 17V Input, 3A Synchronous Buck Converter in SOT563 data sheet.

#### 7 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision A (January 2024) to Revision B (August 2024)

Page

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated