SBASAH6A March 2022 – October 2022 ADS117L11

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements (1.65 V ≤ IOVDD ≤ 2 V)

- 6.7 Switching Characteristics (1.65 V ≤ IOVDD ≤ 2 V)

- 6.8 Timing Requirements (2 V < IOVDD ≤ 5.5 V)

- 6.9 Switching Characteristics (2 V < IOVDD ≤ 5.5 V)

- 6.10 Timing Diagrams

- 6.11 Typical Characteristics

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Registers

- 8.6.1 DEV_ID Register (Address = 0h) [reset = 01h]

- 8.6.2 REV_ID Register (Address = 1h) [reset = xxh]

- 8.6.3 STATUS Register (Address = 2h) [reset = x1100xxxb]

- 8.6.4 CONTROL Register (Address = 3h) [reset = 00h]

- 8.6.5 MUX Register (Address = 4h) [reset = 00h]

- 8.6.6 CONFIG1 Register (Address = 5h) [reset = 00h]

- 8.6.7 CONFIG2 Register (Address = 6h) [reset = 00h]

- 8.6.8 CONFIG3 Register (Address = 7h) [reset = 00h]

- 8.6.9 CONFIG4 Register (Address = 8h) [reset = 08h]

- 8.6.10 OFFSET2, OFFSET1, OFFSET0 Registers (Addresses = 9h, Ah, Bh) [reset = 00h, 00h, 00h]

- 8.6.11 GAIN2, GAIN1, GAIN0 Registers (Addresses = Ch, Dh, Eh) [reset = 40h, 00h, 00h]

- 8.6.12 CRC Register (Address = Fh) [reset = 00h]

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RUK|20

Thermal pad, mechanical data (Package|Pins)

- RUK|20

Orderable Information

9.2.3 Application Curves

The following figures are produced by the TINA-TI™, SPICE-based analog simulation program. The THS4551 SPICE model can be downloaded at the THS4551 product folder.

Figure 9-2 shows the frequency response of the antialias filter and the total response of the antialias filter and the ADC. As shown in this image, the filter provides 90-dB stop-band attenuation from the Nyquist frequency to the 12.8-MHz fMOD frequency.

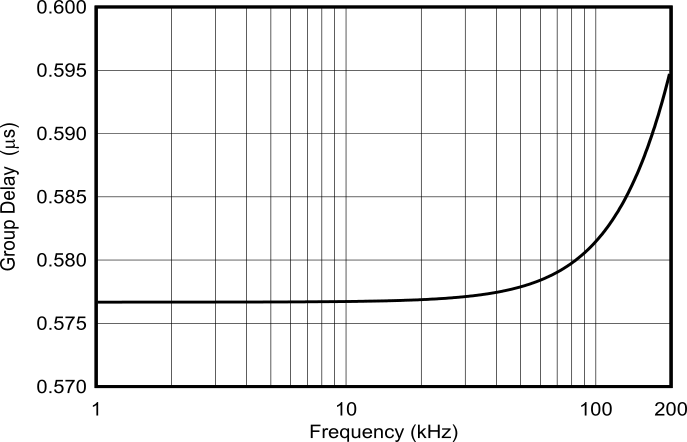

Figure 9-3 shows the analog filter group delay. The 0.575-μs group delay is small in comparison to the 85-μs group delay of the ADC digital filter (34 / fDATA). The analog filter group delay linearity is 0.017 μs, peaking at the edge of the 165-kHz pass band.

Figure 9-3 Antialias Filter Group

Delay

Figure 9-3 Antialias Filter Group

Delay