SBAS499C July 2012 – January 2017 ADS1299 , ADS1299-4 , ADS1299-6

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parametric Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Analog Functionality

- 9.3.2

Digital Functionality

- 9.3.2.1 Digital Decimation Filter

- 9.3.2.2 Clock

- 9.3.2.3 GPIO

- 9.3.2.4 ECG and EEG Specific Features

- 9.4 Device Functional Modes

- 9.5

Programming

- 9.5.1 Data Format

- 9.5.2 SPI Interface

- 9.5.3

SPI Command Definitions

- 9.5.3.1 Sending Multi-Byte Commands

- 9.5.3.2 WAKEUP: Exit STANDBY Mode

- 9.5.3.3 STANDBY: Enter STANDBY Mode

- 9.5.3.4 RESET: Reset Registers to Default Values

- 9.5.3.5 START: Start Conversions

- 9.5.3.6 STOP: Stop Conversions

- 9.5.3.7 RDATAC: Read Data Continuous

- 9.5.3.8 SDATAC: Stop Read Data Continuous

- 9.5.3.9 RDATA: Read Data

- 9.5.3.10 RREG: Read From Register

- 9.5.3.11 WREG: Write to Register

- 9.6

Register Maps

- 9.6.1

User Register Description

- 9.6.1.1 ID: ID Control Register (address = 00h) (reset = xxh)

- 9.6.1.2 CONFIG1: Configuration Register 1 (address = 01h) (reset = 96h)

- 9.6.1.3 CONFIG2: Configuration Register 2 (address = 02h) (reset = C0h)

- 9.6.1.4 CONFIG3: Configuration Register 3 (address = 03h) (reset = 60h)

- 9.6.1.5 LOFF: Lead-Off Control Register (address = 04h) (reset = 00h)

- 9.6.1.6 CHnSET: Individual Channel Settings (n = 1 to 8) (address = 05h to 0Ch) (reset = 61h)

- 9.6.1.7 BIAS_SENSP: Bias Drive Positive Derivation Register (address = 0Dh) (reset = 00h)

- 9.6.1.8 BIAS_SENSN: Bias Drive Negative Derivation Register (address = 0Eh) (reset = 00h)

- 9.6.1.9 LOFF_SENSP: Positive Signal Lead-Off Detection Register (address = 0Fh) (reset = 00h)

- 9.6.1.10 LOFF_SENSN: Negative Signal Lead-Off Detection Register (address = 10h) (reset = 00h)

- 9.6.1.11 LOFF_FLIP: Lead-Off Flip Register (address = 11h) (reset = 00h)

- 9.6.1.12 LOFF_STATP: Lead-Off Positive Signal Status Register (address = 12h) (reset = 00h)

- 9.6.1.13 LOFF_STATN: Lead-Off Negative Signal Status Register (address = 13h) (reset = 00h)

- 9.6.1.14 GPIO: General-Purpose I/O Register (address = 14h) (reset = 0Fh)

- 9.6.1.15 MISC1: Miscellaneous 1 Register (address = 15h) (reset = 00h)

- 9.6.1.16 MISC2: Miscellaneous 2 (address = 16h) (reset = 00h)

- 9.6.1.17 CONFIG4: Configuration Register 4 (address = 17h) (reset = 00h)

- 9.6.1

User Register Description

- 10Applications and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PAG|64

Thermal pad, mechanical data (Package|Pins)

- PAG|64

Orderable Information

9 Detailed Description

9.1 Overview

The ADS1299-x is a low-noise, low-power, multichannel, simultaneously-sampling, 24-bit, delta-sigma (ΔΣ) analog-to-digital converter (ADC) with an integrated programmable gain amplifier (PGA). These devices integrate various EEG-specific functions that makes the family well-suited for scalable electrocardiogram (ECG), electroencephalography (EEG) applications. These devices can also be used in high-performance, multichannel, data acquisition systems by powering down the ECG or EEG-specific circuitry.

The devices have a highly-programmable multiplexer that allows for temperature, supply, input short, and bias measurements. Additionally, the multiplexer allows any input electrodes to be programmed as the patient reference drive. The PGA gain can be chosen from one of seven settings (1, 2, 4, 6, 8, 12, and 24). The ADCs in the device offer data rates from 250 SPS to 16 kSPS. Communication to the device is accomplished using an SPI-compatible interface. The device provides four general-purpose input/output (GPIO) pins for general use. Multiple devices can be synchronized using the START pin.

The internal reference generates a low noise 4.5 V internal voltage when enabled and the internal oscillator generates a 2.048-MHz clock when enabled. The versatile patient bias drive block allows the average of any electrode combination to be chosen in order to generate the patient drive signal. Lead-off detection can be accomplished by using a current source or sink. A one-time, in-band, lead-off option and a continuous, out-of-band, internal lead-off option are available.

9.3 Feature Description

This section contains details of the ADS1299-x internal functional elements. The analog blocks are discussed first, followed by the digital interface. Blocks implementing EEG-specific functions are covered at the end of this section.

Throughout this document, fCLK denotes the CLK pin signal frequency, tCLK denotes the CLK pin signal period, fDR denotes the output data rate, tDR denotes the output data time period, and fMOD denotes the frequency at which the modulator samples the input.

9.3.1 Analog Functionality

9.3.1.1 Input Multiplexer

The ADS1299-x input multiplexers are very flexible and provide many configurable signal-switching options. Figure 18 shows the multiplexer on a single channel of the device. Note that the device has either four (ADS1299-4), six (ADS1299-6) or eight (ADS1299) such blocks, one for each channel. SRB1, SRB2, and BIASIN are common to all blocks. INxP and INxN are separate for each of the four, six, or eight blocks. This flexibility allows for significant device and sub-system diagnostics, calibration, and configuration. Switch setting selections for each channel by writing the appropriate values to the CHnSET[3:0] register (see the CHnSET: Individual Channel Settings section for details) using the BIAS_MEAS bit in the CONFIG3 register and the SRB1 bit in the MISC1 register (see the CONFIG3: Configuration Register 3 subsection of the Register Maps section for details). See the Input Multiplexer section for further information regarding the EEG-specific features of the multiplexer.

9.3.1.1.1 Device Noise Measurements

Setting CHnSET[2:0] = 001 sets the common-mode voltage of [(VVREFP + VVREFN) / 2] to both channel inputs. This setting can be used to test inherent device noise in the user system.

9.3.1.1.2 Test Signals (TestP and TestN)

Setting CHnSET[2:0] = 101 provides internally-generated test signals for use in sub-system verification at power-up. This functionality allows the device internal signal chain to be tested out.

Test signals are controlled through register settings (see the CONFIG2: Configuration Register 2 subsection in the Register Maps section for details). TEST_AMP controls the signal amplitude and TEST_FREQ controls switching at the required frequency.

9.3.1.1.3 Temperature Sensor (TempP, TempN)

The ADS1299-x contains an on-chip temperature sensor. This sensor uses two internal diodes with one diode having a current density 16x that of the other, as shown in Figure 19. The difference in diode current densities yields a voltage difference proportional to absolute temperature.

As a result of the low thermal resistance of the package to the printed circuit board (PCB), the internal device temperature tracks PCB temperature closely. Note that self-heating of the ADS1299-x causes a higher reading than the temperature of the surrounding PCB.

The scale factor of Equation 3 converts the temperature reading to degrees Celsius. Before using this equation, the temperature reading code must first be scaled to microvolts.

Figure 19. Temperature Sensor Measurement in the Input

Figure 19. Temperature Sensor Measurement in the Input

9.3.1.1.4 Supply Measurements (MVDDP, MVDDN)

Setting CHnSET[2:0] = 011 sets the channel inputs to different supply voltages of the device.

For channels 1, 2, 5, 6, 7, and 8, (MVDDP – MVDDN) is [0.5 × (AVDD + AVSS)].

For channels 3 and 4, (MVDDP – MVDDN) is DVDD / 4.

To avoid saturating the PGA when measuring power supplies, set the gain to 1.

9.3.1.1.5 Lead-Off Excitation Signals (LoffP, LoffN)

The lead-off excitation signals are fed into the multiplexer before the switches. The comparators that detect the lead-off condition are also connected to the multiplexer block before the switches. For a detailed description of the lead-off block, see the Lead-Off Detection section.

9.3.1.1.6 Auxiliary Single-Ended Input

The BIASIN pin is primarily used for routing the bias signal to any electrodes in case the bias electrode falls off. However, the BIASIN pin can be used as a multiple single-ended input channel. The signal at the BIASIN pin can be measured with respect to the voltage at the BIASREF pin using any of the eight channels. This measurement is done by setting the channel multiplexer setting to '010' and the BIAS_MEAS bit of the CONFIG3 register to '1'.

9.3.1.2 Analog Input

The analog inputs to the device connect directly to an integrated low-noise, low-drift, high input impedance, programmable gain amplifier. The amplifier is located following the individual channel multiplexer.

The ADS1299-x analog inputs are fully differential. The differential input voltage (VINxP – VINxN) can span from –VREF / gain to VREF / gain. See the Data Format section for an explanation of the correlation between the analog input and digital codes. There are two general methods of driving the ADS1299-x analog inputs: pseudo-differential or fully-differential, as shown in Figure 20, Figure 21, and Figure 22.

Figure 20. Methods of Driving the ADS1299-x: Pseudo-Differential or Fully Differential

Figure 20. Methods of Driving the ADS1299-x: Pseudo-Differential or Fully Differential

Figure 21. Pseudo-Differential Input Mode

Figure 21. Pseudo-Differential Input Mode

Figure 22. Fully-Differential Input Mode

Figure 22. Fully-Differential Input Mode

Hold the INxN pin at a common voltage, preferably at mid supply, to configure the fully differential input for a pseudo-differential signal. Swing the INxP pin around the common voltage –VREF / gain to VREF / gain and remain within the absolute maximum specifications. The common-mode voltage (VCM) changes with varying signal level when the inputs are configured in pseudo-differential mode. Verify that the differential signal at the minimum and maximum points meets the common-mode input specification discussed in the Input Common-Mode Range section.

Configure the signals at INxP and INxN to be 180° out-of-phase centered around a common voltage to use a fully differential input method. Both the INxP and INxN inputs swing from the common voltage + ½ VREF / gain to the common voltage – ½ VREF / gain. The differential voltage at the maximum and minimum points is equal to –VREF / gain to VREF / gain and centered around a fixed common-mode voltage (VCM). Use the ADS1299-x in a differential configuration to maximize the dynamic range of the data converter. For optimal performance, the common voltage is recommended to be set at the midpoint of the analog supplies [(AVDD + AVSS) / 2].

9.3.1.3 PGA Settings and Input Range

The low-noise PGA is a differential input and output amplifier, as shown in Figure 23. The PGA has seven gain settings (1, 2, 4, 6, 8, 12, and 24) that can be set by writing to the CHnSET register (see the CHnSET: Individual Channel Settings subsection of the Register Maps section for details). The ADS1299-x has CMOS inputs and therefore has negligible current noise. Table 5 shows the typical bandwidth values for various gain settings. Note that Table 5 shows small-signal bandwidth. For large signals, performance is limited by PGA slew rate.

Table 5. PGA Gain versus Bandwidth

| GAIN | NOMINAL BANDWIDTH AT ROOM TEMPERATURE (kHz) |

|---|---|

| 1 | 662 |

| 2 | 332 |

| 4 | 165 |

| 6 | 110 |

| 8 | 83 |

| 12 | 55 |

| 24 | 27 |

The PGA resistor string that implements the gain has 39.6 kΩ of resistance for a gain of 12. This resistance provides a current path across the PGA outputs in the presence of a differential input signal. This current is in addition to the quiescent current specified for the device in the presence of a differential signal at the input.

9.3.1.3.1 Input Common-Mode Range

To stay within the linear operating range of the PGA, the input signals must meet certain requirements that are discussed in this section.

The outputs of the amplifiers in Figure 23 cannot swing closer to the supplies (AVSS and AVDD) than 200 mV. If the outputs of the amplifiers are driven to within 200 mV of the supply rails, then the amplifiers saturate and consequently become nonlinear. To prevent this nonlinear operating condition, the output voltages must not exceed the common-mode range of the front-end.

The usable input common-mode range of the front-end depends on various parameters, including the maximum differential input signal, supply voltage, PGA gain, and the 200 mV for the amplifier headroom. This range is described in Equation 4:

where

For example:

If AVDD = 5 V, gain = 12, and VMAX_DIFF = 350 mV

Then 2.3 V < CM < 2.7 V

9.3.1.3.2 Input Differential Dynamic Range

The differential input voltage range (VINxP – VINxN) depends on the analog supply and reference used in the system. This range is shown in Equation 5.

9.3.1.3.3 ADC ΔΣ Modulator

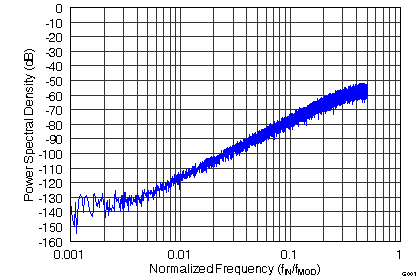

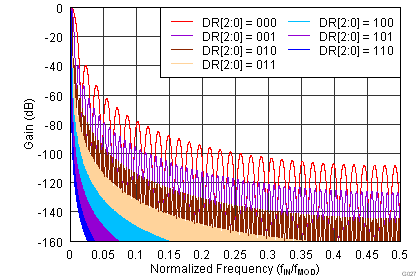

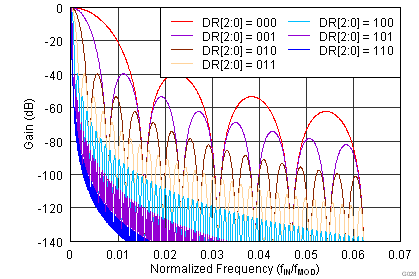

Each ADS1299-x channel has a 24-bit, ΔΣ ADC. This converter uses a second-order modulator optimized for low-noise applications. The modulator samples the input signal at the rate of (fMOD = fCLK / 2). As in the case of any ΔΣ modulator, the device noise is shaped until fMOD / 2, as shown in Figure 24. The on-chip digital decimation filters explained in the next section can be used to filter out the noise at higher frequencies. These on-chip decimation filters also provide antialias filtering. This ΔΣ converter feature drastically reduces the complexity of the analog antialiasing filters typically required with nyquist ADCs.

Figure 24. Modulator Noise Spectrum Up To 0.5 × fMOD

Figure 24. Modulator Noise Spectrum Up To 0.5 × fMOD

9.3.1.3.4 Reference

Figure 25 shows a simplified block diagram of the ADS1299-x internal reference. The 4.5-V reference voltage is generated with respect to AVSS. When using the internal voltage reference, connect VREFN to AVSS.

The external band-limiting capacitors determine the amount of reference noise contribution. For high-end EEG systems, the capacitor values should be chosen such that the bandwidth is limited to less than 10 Hz so that the reference noise does not dominate system noise.

Alternatively, the internal reference buffer can be powered down and an external reference can be applied to VREFP. Figure 26 shows a typical external reference drive circuitry. Power-down is controlled by the PD_REFBUF bit in the CONFIG3 register. This power-down is also used to share internal references when two devices are cascaded. By default, the device wakes up in external reference mode.

Figure 26. External Reference Driver

Figure 26. External Reference Driver

9.3.2 Digital Functionality

9.3.2.1 Digital Decimation Filter

The digital filter receives the modulator output and decimates the data stream. By adjusting the amount of filtering, tradeoffs can be made between resolution and data rate: filter more for higher resolution, filter less for higher data rates. Higher data rates are typically used in EEG applications for ac lead-off detection.

The digital filter on each channel consists of a third-order sinc filter. The sinc filter decimation ratio can be adjusted by the DR bits in the CONFIG1 register (see the Register Maps section for details). This setting is a global setting that affects all channels and, therefore, all channels operate at the same data rate in a device.

9.3.2.1.1 Sinc Filter Stage (sinx / x)

The sinc filter is a variable decimation rate, third-order, low-pass filter. Data are supplied to this section of the filter from the modulator at the rate of fMOD. The sinc filter attenuates the modulator high-frequency noise, then decimates the data stream into parallel data. The decimation rate affects the overall converter data rate.

Equation 6 shows the scaled Z-domain transfer function of the sinc filter.

The frequency domain transfer function of the sinc filter is shown in Equation 7.

where

The sinc filter has notches (or zeroes) that occur at the output data rate and multiples thereof. At these frequencies, the filter has infinite attenuation. Figure 27 shows the sinc filter frequency response and Figure 28 shows the sinc filter roll-off. With a step change at input, the filter takes 3 × tDR to settle. After a rising edge of the START signal, the filter takes tSETTLE time to give the first data output. The settling time of the filters at various data rates are discussed in the Start subsection of the SPI Interface section. Figure 29 and Figure 30 show the filter transfer function until fMOD / 2 and fMOD / 16, respectively, at different data rates. Figure 31 shows the transfer function extended until 4 × fMOD. The ADS1299-x pass band repeats itself at every fMOD. The input R-C antialiasing filters in the system should be chosen such that any interference in frequencies around multiples of fMOD are attenuated sufficiently.

![ADS1299 ADS1299-4 ADS1299-6 Transfer

Function of On-Chip Decimation Filters

Until 4 fMOD for DR[2:0] = 000 and DR[2:0] = 110 ADS1299 ADS1299-4 ADS1299-6 G029_SBAS499.png](/ods/images/SBAS499C/G029_SBAS499.png)

Until 4 fMOD for DR[2:0] = 000 and DR[2:0] = 110

9.3.2.2 Clock

The ADS1299-x provides two methods for device clocking: internal and external. Internal clocking is ideally suited for low-power, battery-powered systems. The internal oscillator is trimmed for accuracy at room temperature. Accuracy varies over the specified temperature range; see the Electrical Characteristics. Clock selection is controlled by the CLKSEL pin and the CLK_EN register bit.

The CLKSEL pin selects either the internal or external clock. The CLK_EN bit in the CONFIG1 register enables and disables the oscillator clock to be output in the CLK pin. A truth table for these two pins is shown in Table 6. The CLK_EN bit is useful when multiple devices are used in a daisy-chain configuration. During power-down, the external clock is recommended be shut down to save power.

Table 6. CLKSEL Pin and CLK_EN Bit

| CLKSEL PIN | CONFIG1.CLK_EN BIT | CLOCK SOURCE | CLK PIN STATUS |

|---|---|---|---|

| 0 | X | External clock | Input: external clock |

| 1 | 0 | Internal clock oscillator | 3-state |

| 1 | 1 | Internal clock oscillator | Output: internal clock oscillator |

9.3.2.3 GPIO

The ADS1299-x has a total of four general-purpose digital I/O (GPIO) pins available in normal mode of operation. The digital I/O pins are individually configurable as either inputs or outputs through the GPIOC bits register. The GPIOD bits in the GPIO register control the pin level. When reading the GPIOD bits, the data returned are the logic level of the pins, whether they are programmed as inputs or outputs. When the GPIO pin is configured as an input, a write to the corresponding GPIOD bit has no effect. When configured as an output, a write to the GPIOD bit sets the output value.

If configured as inputs, these pins must be driven (do not float). The GPIO pins are set as inputs after power-on or after a reset. Figure 32 shows the GPIO port structure. The pins should be shorted to DGND if not used.

Figure 32. GPIO Port Pin

Figure 32. GPIO Port Pin

9.3.2.4 ECG and EEG Specific Features

9.3.2.4.1 Input Multiplexer (Rerouting the BIAS Drive Signal)

The input multiplexer has EEG-specific functions for the bias drive signal. The BIAS signal is available at the BIASOUT pin when the appropriate channels are selected for BIAS derivation, feedback elements are installed external to the chip, and the loop is closed. This signal can either be fed after filtering or fed directly into the BIASIN pin, as shown in Figure 33. This BIASIN signal can be multiplexed into any input electrode by setting the MUX bits of the appropriate channel set registers to '110' for P-side or '111' for N-side. Figure 33 shows the BIAS signal generated from channels 1, 2, and 3 and routed to the N-side of channel 8. This feature can be used to dynamically change the electrode that is used as the reference signal to drive the patient body.

9.3.2.4.2 Input Multiplexer (Measuring the BIAS Drive Signal)

Also, the BIASOUT signal can be routed to a channel (that is not used for the calculation of BIAS) for measurement. Figure 34 shows the register settings to route the BIASIN signal to channel 8. The measurement is done with respect to the voltage on the BIASREF pin. If BIASREF is chosen to be internal, then BIASREF is at [(AVDD + AVSS) / 2]. This feature is useful for debugging purposes during product development.

9.3.2.4.3 Lead-Off Detection

Patient electrode impedances are known to decay over time. These electrode connections must be continuously monitored to verify that a suitable connection is present. The ADS1299-x lead-off detection functional block provides significant flexibility to the user to choose from various lead-off detection strategies. Though called lead-off detection, this is in fact an electrode-off detection.

The basic principle is to inject an excitation current and measure the voltage to determine if the electrode is off. As shown in the lead-off detection functional block diagram in Figure 35, this circuit provides two different methods of determining the state of the patient electrode. The methods differ in the frequency content of the excitation signal. Lead-off can be selectively done on a per channel basis using the LOFF_SENSP and LOFF_SENSN registers. Also, the internal excitation circuitry can be disabled and just the sensing circuitry can be enabled.

Figure 35. Lead-Off Detection

Figure 35. Lead-Off Detection

9.3.2.4.3.1 DC Lead-Off

In this method, the lead-off excitation is with a dc signal. The dc excitation signal can be chosen from either an external pull-up or pull-down resistor or an internal current source or sink, as shown in Figure 36. One side of the channel is pulled to supply and the other side is pulled to ground. The pull-up and pull-down current can be swapped (as shown in Figure 36b and Figure 36c) by setting the bits in the LOFF_FLIP register. In case of a current source or sink, the magnitude of the current can be set by using the ILEAD_OFF[1:0] bits in the LOFF register. The current source or sink gives larger input impedance compared to the 10-MΩ pull-up or pull-down resistor.

Figure 36. DC Lead-Off Excitation Options

Figure 36. DC Lead-Off Excitation Options

Sensing of the response can be done either by searching the digital output code from the device or by monitoring the input voltages with an on-chip comparator. If either electrode is off, the pull-up and pull-down resistors saturate the channel. Searching the output code determines if either the P-side or the N-side is off. To pinpoint which one is off, the comparators must be used. The input voltage is also monitored using a comparator and a 3-bit DAC whose levels are set by the COMP_TH[2:0] bits in the LOFF register. The output of the comparators are stored in the LOFF_STATP and LOFF_STATN registers. These registers are available as a part of the output data stream. (See the Data Output (DOUT) subsection of the SPI Interface section.) If dc lead-off is not used, the lead-off comparators can be powered down by setting the PD_LOFF_COMP bit in the CONFIG4 register.

An example procedure to turn on dc lead-off is given in the Lead-Off section.

9.3.2.4.3.2 AC Lead-Off (One Time or Periodic)

In this method, an in-band ac signal is used for excitation. The ac signal is generated by alternatively providing a current source and sink at the input with a fixed frequency. The frequency can be chosen by the FLEAD_OFF[1:0] bits in the LOFF register. The excitation frequency is chosen to be one of the two in-band frequency selections (7.8 Hz or 31.2 Hz). This in-band excitation signal is passed through the channel and measured at the output.

Sensing of the ac signal is done by passing the signal through the channel to be digitized and then measured at the output. The ac excitation signals are introduced at a frequency that is in the band of interest. The signal can be filtered out separately and processed. By measuring the magnitude of the output at the excitation signal frequency, the electrode impedance can be calculated.

For continuous lead-off, an out-of-band ac current source or sink must be externally applied to the inputs. This signal can then be digitally processed to determine the electrode impedance.

9.3.2.4.4 Bias Lead-Off

BIAS Lead-Off Detection During Normal Operation

During normal operation, the ADS1299-x BIAS lead-off at power-up function cannot be used because the BIAS amplifier must be powered off.

BIAS Lead Off Detection At Power-Up

This feature is included in the ADS1299-x for use in determining whether the bias electrode is suitably connected. At power-up, the ADS1299-x uses a current source and comparator to determine the BIAS electrode connection status, as shown in Figure 37. The reference level of the comparator is set to determine the acceptable BIAS impedance threshold.

Figure 37. BIAS Lead-Off Detection at Power-Up

Figure 37. BIAS Lead-Off Detection at Power-Up

When the BIAS amplifier is powered on, the current source has no function. Only the comparator can be used to sense the voltage at the output of the BIAS amplifier. The comparator thresholds are set by the same LOFF[7:5] bits used to set the thresholds for other negative inputs.

9.3.2.4.5 Bias Drive (DC Bias Circuit)

Use the bias circuitry to counter the common-mode interference in a EEG system as a result of power lines and other sources, including fluorescent lights. The bias circuit senses the common-mode voltage of a selected set of electrodes and creates a negative feedback loop by driving the body with an inverted common-mode signal. The negative feedback loop restricts the common-mode movement to a narrow range, depending on the loop gain. Stabilizing the entire loop is specific to the individual user system based on the various poles in the loop. The ADS1299-x integrates the muxes to select the channel and an operational amplifier. All the amplifier terminals are available at the pins, allowing the user to choose the components for the feedback loop. The circuit in Figure 38 shows the overall functional connectivity for the bias circuit.

The reference voltage for the bias drive can be chosen to be internally generated [(AVDD + AVSS) / 2] or provided externally with a resistive divider. The selection of an internal versus external reference voltage for the bias loop is defined by writing the appropriate value to the BIASREF_INT bit in the CONFIG2 register.

If the bias function is not used, the amplifier can be powered down using the PD_BIAS bit (see the CONFIG3: Configuration Register 3 subsection of the Register Maps section for details). Use the PD_BIAS bit to power-down all but one of the bias amplifiers when daisy-chaining multiple ADS1299-x devices.

The BIASIN pin functionality is explained in the Input Multiplexer section. An example procedure to use the bias amplifier is shown in the Bias Drive section.

9.3.2.4.5.1 Bias Configuration with Multiple Devices

Figure 39 shows multiple devices connected to the bias drive.

Figure 39. BIAS Drive Connection for Multiple Devices

Figure 39. BIAS Drive Connection for Multiple Devices

9.4 Device Functional Modes

9.4.1 Start

Pull the START pin high for at least 2 tCLK periods, or send the START command to begin conversions. When START is low and the START command has not been sent, the device does not issue a DRDY signal (conversions are halted).

When using the START command to control conversions, hold the START pin low. The ADS1299-x features two modes to control conversions: continuous mode and single-shot mode. The mode is selected by SINGLE_SHOT (bit 3 of the CONFIG4 register). In multiple device configurations, the START pin is used to synchronize devices (see the Multiple Device Configuration subsection of the SPI Interface section for more details).

9.4.1.1 Settling Time

The settling time (tSETTLE) is the time required for the converter to output fully-settled data when the START signal is pulled high. When START is pulled high, DRDY is also pulled high. The next DRDY falling edge indicates that data are ready. Figure 40 shows the timing diagram and Table 7 lists the settling time for different data rates. The settling time depends on fCLK and the decimation ratio (controlled by the DR[2:0] bits in the CONFIG1 register). When the initial settling time has passed, the DRDY falling edge occurs at the set data rate, tDR. If data is not read back on DOUT and the output shift register needs to update, DRDY goes high for 4 tCLK before returning back low indicating new data is ready. Table 7 lists the settling time as a function of tCLK. Note that when START is held high and there is a step change in the input signal, 3 × tDR is required for the filter to settle to the new value. Settled data are available on the fourth DRDY pulse.

Table 7. Settling Time for Different Data Rates

| DR[2:0] | NORMAL MODE | UNIT |

|---|---|---|

| 000 | 521 | tCLK |

| 001 | 1033 | tCLK |

| 010 | 2057 | tCLK |

| 011 | 4105 | tCLK |

| 100 | 8201 | tCLK |

| 101 | 16393 | tCLK |

| 110 | 32777 | tCLK |

9.4.2 Reset (RESET)

There are two methods to reset the ADS1299-x: pull the RESET pin low, or send the RESET command. When using the RESET pin, make sure to follow the minimum pulse duration timing specifications before taking the pin back high. The RESET command takes effect on the eighth SCLK falling edge of the command. After a reset, 18 tCLK cycles are required to complete initialization of the configuration registers to default states and start the conversion cycle. Note that an internal reset is automatically issued to the digital filter whenever the CONFIG1 register is set to a new value with a WREG command.

9.4.3 Power-Down (PWDN)

When PWDN is pulled low, all on-chip circuitry is powered down. To exit power-down mode, take the PWDN pin high. Upon exiting from power-down mode, the internal oscillator and the reference require time to wake up. During power-down, the external clock is recommended to be shut down to save power.

9.4.4 Data Retrieval

9.4.4.1 Data Ready (DRDY)

DRDY is an output signal which transitions from high to low indicating new conversion data are ready. The CS signal has no effect on the data ready signal. DRDY behavior is determined by whether the device is in RDATAC mode or the RDATA command is used to read data on demand. (See the RDATAC: Read Data Continuous and RDATA: Read Data subsections of the SPI Command Definitions section for further details).

When reading data with the RDATA command, the read operation can overlap the next DRDY occurrence without data corruption.

The START pin or the START command places the device either in normal data capture mode or pulse data capture mode.

Figure 41 shows the relationship between DRDY, DOUT, and SCLK during data retrieval (in case of an ADS1299). DOUT is latched out at the SCLK rising edge. DRDY is pulled high at the SCLK falling edge. Note that DRDY goes high on the first SCLK falling edge, regardless of whether data are being retrieved from the device or a command is being sent through the DIN pin.

Figure 41. DRDY with Data Retrieval (CS = 0)

Figure 41. DRDY with Data Retrieval (CS = 0)

9.4.4.2 Reading Back Data

Data retrieval can be accomplished in one of two methods:

- RDATAC: the read data continuous command sets the device in a mode that reads data continuously without sending commands. See the RDATAC: Read Data Continuous section for more details.

- RDATA: the read data command requires that a command is sent to the device to load the output shift register with the latest data. See the RDATA: Read Data section for more details.

Conversion data are read by shifting data out on DOUT. The MSB of the data on DOUT is clocked out on the first SCLK rising edge. DRDY returns high on the first SCLK falling edge. DIN should remain low for the entire read operation.

The number of bits in the data output depends on the number of channels and the number of bits per channel. For the 8-channel ADS1299, the number of data outputs is [(24 status bits + 24 bits × 8 channels) = 216 bits]. The format of the 24 status bits is: (1100 + LOFF_STATP + LOFF_STATN + bits[4:7] of the GPIO register). The data format for each channel data are twos complement and MSB first. When channels are powered down using the user register setting, the corresponding channel output is set to '0'. However, the channel output sequence remains the same.

The ADS1299-x also provides a multiple readback feature. Data can be read out multiple times by simply giving more SCLKs in RDATAC mode, in which case the MSB data byte repeats after reading the last byte. The DAISY_EN bit in the CONFIG1 register must be set to '1' for multiple readbacks.

9.4.5 Continuous Conversion Mode

Conversions begin when the START pin is taken high or when the START command is sent. As shown in Figure 42, the DRDY output goes high when conversions are started and goes low when data are ready. Conversions continue indefinitely until the START pin is taken low or the STOP command is transmitted. When the START pin is pulled low or the STOP command is issued, the conversion in progress is allowed to complete. Figure 43 and Table 8 illustrate the required DRDY timing to the START pin or the START and STOP commands when controlling conversions in this mode. The tSDSU timing indicates when to take the START pin low or when to send the STOP command before the DRDY falling edge to halt further conversions. The tDSHD timing indicates when to take the START pin low or send the STOP command after a DRDY falling edge to complete the current conversion and halt further conversions. To keep the converter running continuously, the START pin can be permanently tied high.

When switching from Single-Shot mode to Continuous Conversion mode, bring the START signal low and back high or send a STOP command followed by a START command. This conversion mode is ideal for applications that require a fixed continuous stream of conversions results.

Table 8. Timing Characteristics for Figure 43(1)

| MIN | UNIT | ||

|---|---|---|---|

| tSDSU | START pin low or STOP command to DRDY setup time to halt further conversions | 16 | tCLK |

| tDSHD | START pin low or STOP command to complete current conversion | 16 | tCLK |

9.4.6 Single-Shot Mode

Single-shot mode is enabled by setting the SINGLE_SHOT bit in the CONFIG4 register to '1'. In single-shot mode, the ADS1299-x performs a single conversion when the START pin is taken high or when the START command is sent. As shown in Figure 44, when a conversion is complete, DRDY goes low and further conversions are stopped. Regardless of whether the conversion data are read or not, DRDY remains low. To begin a new conversion, take the START pin low and then back high, or send the START command again. When switching from Continuous Conversion mode to Single-Shot mode, bring the START signal low and back high or send a STOP command followed by a START command.

Figure 44. DRDY with No Data Retrieval in Single-Shot Mode

Figure 44. DRDY with No Data Retrieval in Single-Shot Mode

This conversion mode is ideal for applications that require non-standard or non-continuous data rates. Issuing a START command or toggling the START pin high resets the digital filter, effectively dropping the data rate by a factor of four. This mode leaves the system more susceptible to aliasing effects, requiring more complex analog or digital filtering. Loading on the host processor increases because the processor must toggle the START pin or send a START command to initiate a new conversion cycle.

9.5 Programming

9.5.1 Data Format

The device provides 24 bits of data in binary twos complement format. The size of one code (LSB) is calculated using Equation 8.

A positive full-scale input produces an output code of 7FFFFFh and the negative full-scale input produces an output code of 800000h. The output clips at these codes for signals exceeding full-scale. Table 9 summarizes the ideal output codes for different input signals. All 24 bits toggle when the analog input is at positive or negative full-scale.

Table 9. Ideal Output Code versus Input Signal

| INPUT SIGNAL, VIN

(INxP - INxN) |

IDEAL OUTPUT CODE(1) |

|---|---|

| ≥ FS | 7FFFFFh |

| +FS / (223 – 1) | 000001h |

| 0 | 000000h |

| –FS / (223 – 1) | FFFFFFh |

| ≤ –FS (223 / 223 – 1) | 800000h |

9.5.2 SPI Interface

The SPI-compatible serial interface consists of four signals: CS, SCLK, DIN, and DOUT. The interface reads conversion data, reads and writes registers, and controls ADS1299-x operation. The data-ready output, DRDY (see the Data Ready (DRDY) section), is used as a status signal to indicate when data are ready. DRDY goes low when new data are available.

9.5.2.1 Chip Select (CS)

The CS pin activates SPI communication. CS must be low before data transactions and must stay low for the entire SPI communication period. When CS is high, the DOUT pin enters a high-impedance state. Therefore, reading and writing to the serial interface are ignored and the serial interface is reset. DRDY pin operation is independent of CS. DRDY still indicates that a new conversion has completed and is forced high as a response to SCLK, even if CS is high.

Taking CS high deactivates only the SPI communication with the device and the serial interface is reset. Data conversion continues and the DRDY signal can be monitored to check if a new conversion result is ready. A master device monitoring the DRDY signal can select the appropriate slave device by pulling the CS pin low. After the serial communication is finished, always wait four or more tCLK cycles before taking CS high.

9.5.2.2 Serial Clock (SCLK)

SCLK provides the clock for serial communication. SCLK is a Schmitt-trigger input, but TI recommends keeping SCLK as free from noise as possible to prevent glitches from inadvertently shifting the data. Data are shifted into DIN on the falling edge of SCLK and shifted out of DOUT on the rising edge of SCLK.

The absolute maximum SCLK limit is specified in Figure 1. When shifting in commands with SCLK, make sure that the entire set of SCLKs is issued to the device. Failure to do so can result in the device serial interface being placed into an unknown state requiring CS to be taken high to recover.

For a single device, the minimum speed required for SCLK depends on the number of channels, number of bits of resolution, and output data rate. (For multiple cascaded devices, see the Cascaded Mode subsection of the Multiple Device Configuration section.)

For example, if the ADS1299 is used in a 500-SPS mode (8 channels, 24-bit resolution), the minimum SCLK speed is 110 kHz.

Data retrieval can be accomplished either by placing the device in RDATAC mode or by issuing an RDATA command for data on demand. The SCLK rate limitation in Equation 9 applies to RDATAC. For the RDATA command, the limitation applies if data must be read in between two consecutive DRDY signals. Equation 9 assumes that there are no other commands issued in between data captures.

9.5.2.3 Data Input (DIN)

DIN is used along with SCLK to send data to the device. Data on DIN are shifted into the device on the falling edge of SCLK.

The communication of this device is full-duplex in nature. The device monitors commands shifted in even when data are being shifted out. Data that are present in the output shift register are shifted out when sending in a command. Therefore, make sure that whatever is being sent on the DIN pin is valid when shifting out data. When no command is to be sent to the device when reading out data, send the NOP command on DIN. Make sure that the tSDECODE timing is met in the Sending Multi-Byte Commands section when sending multiple byte commands on DIN.

9.5.2.4 Data Output (DOUT)

DOUT is used with SCLK to read conversion and register data from the device. Data are clocked out on the rising edge of SCLK, MSB first. DOUT goes to a high-impedance state when CS is high. Figure 45 shows the ADS1299 data output protocol.

Figure 45. SPI Bus Data Output

Figure 45. SPI Bus Data Output

9.5.3 SPI Command Definitions

The ADS1299-x provides flexible configuration control. The commands, summarized in Table 10, control and configure device operation. The commands are stand-alone, except for the register read and write operations that require a second command byte plus data. CS can be taken high or held low between commands but must stay low for the entire command operation (especially for multi-byte commands). System commands and the RDATA command are decoded by the device on the seventh SCLK falling edge. The register read and write commands are decoded on the eighth SCLK falling edge. Be sure to follow SPI timing requirements when pulling CS high after issuing a command.

Table 10. Command Definitions

| COMMAND | DESCRIPTION | FIRST BYTE | SECOND BYTE |

|---|---|---|---|

| System Commands | |||

| WAKEUP | Wake-up from standby mode | 0000 0010 (02h) | |

| STANDBY | Enter standby mode | 0000 0100 (04h) | |

| RESET | Reset the device | 0000 0110 (06h) | |

| START | Start and restart (synchronize) conversions | 0000 1000 (08h) | |

| STOP | Stop conversion | 0000 1010 (0Ah) | |

| Data Read Commands | |||

| RDATAC | Enable Read Data Continuous mode. This mode is the default mode at power-up.(2) |

0001 0000 (10h) | |

| SDATAC | Stop Read Data Continuously mode | 0001 0001 (11h) | |

| RDATA | Read data by command; supports multiple read back. | 0001 0010 (12h) | |

| Register Read Commands | |||

| RREG | Read n nnnn registers starting at address r rrrr | 001r rrrr (2xh)(1) | 000n nnnn(1) |

| WREG | Write n nnnn registers starting at address r rrrr | 010r rrrr (4xh)(1) | 000n nnnn(1) |

9.5.3.1 Sending Multi-Byte Commands

The ADS1299-x serial interface decodes commands in bytes and requires 4 tCLK cycles to decode and execute. Therefore, when sending multi-byte commands (such as RREG or WREG), a 4 tCLK period must separate the end of one byte (or command) and the next.

Assuming CLK is 2.048 MHz, then tSDECODE (4 tCLK) is 1.96 µs. When SCLK is 16 MHz, one byte can be transferred in 500 ns. This byte transfer time does not meet the tSDECODE specification; therefore, a delay must be inserted so the end of the second byte arrives 1.46 µs later. If SCLK is 4 MHz, one byte is transferred in 2 µs. Because this transfer time exceeds the tSDECODE specification, the processor can send subsequent bytes without delay. In this later scenario, the serial port can be programmed to move from single-byte transfers per cycle to multiple bytes.

9.5.3.2 WAKEUP: Exit STANDBY Mode

The WAKEUP command exits low-power standby mode; see the STANDBY: Enter STANDBY Mode subsection of the SPI Command Definitions section. Time is required when exiting standby mode (see the Electrical Characteristics for details). There are no SCLK rate restrictions for this command and can be issued at any time. Any following commands must be sent after a delay of 4 tCLK cycles.

9.5.3.3 STANDBY: Enter STANDBY Mode

The STANDBY command enters low-power standby mode. All parts of the circuit are shut down except for the reference section. The standby mode power consumption is specified in the Electrical Characteristics. There are no SCLK rate restrictions for this command and can be issued at any time. Do not send any other commands other than the wakeup command after the device enters standby mode.

9.5.3.4 RESET: Reset Registers to Default Values

The RESET command resets the digital filter cycle and returns all register settings to default values. See the Reset (RESET) subsection of the SPI Interface section for more details. There are no SCLK rate restrictions for this command and can be issued at any time. 18 tCLK cycles are required to execute the RESET command. Avoid sending any commands during this time.

9.5.3.5 START: Start Conversions

The START command starts data conversions. Tie the START pin low to control conversions by command. If conversions are in progress, this command has no effect. The STOP command stops conversions. If the START command is immediately followed by a STOP command, then there must be a 4-tCLK cycle delay between them. When the START command is sent to the device, keep the START pin low until the STOP command is issued. (See the Start subsection of the SPI Interface section for more details.) There are no SCLK rate restrictions for this command and can be issued at any time.

9.5.3.6 STOP: Stop Conversions

The STOP command stops conversions. Tie the START pin low to control conversions by command. When the STOP command is sent, the conversion in progress completes and further conversions are stopped. If conversions are already stopped, this command has no effect. There are no SCLK rate restrictions for this command and can be issued at any time.

9.5.3.7 RDATAC: Read Data Continuous

The RDATAC command enables conversion data output on each DRDY without the need to issue subsequent read data commands. This mode places the conversion data in the output register and may be shifted out directly. The read data continuous mode is the device default mode; the device defaults to this mode on power-up.

RDATAC mode is cancelled by the Stop Read Data Continuous command. If the device is in RDATAC mode, a SDATAC command must be issued before any other commands can be sent to the device. There are no SCLK rate restrictions for this command. However, subsequent data retrieval SCLKs or the SDATAC command should wait at least 4 tCLK cycles before completion (see the Sending Multi-Byte Commands section). RDATAC timing is illustrated in Figure 46. As depicted in Figure 46, there is a keep out zone of 4 tCLK cycles around the DRDY pulse where this command cannot be issued in. If no data are retrieved from the device, DOUT and DRDY behave similarly in this mode. To retrieve data from the device after the RDATAC command is issued, make sure either the START pin is high or the START command is issued. Figure 46 shows the recommended way to use the RDATAC command. RDATAC is ideally-suited for applications such as data loggers or recorders, where registers are set one time and do not need to be reconfigured.

9.5.3.8 SDATAC: Stop Read Data Continuous

The SDATAC command cancels the Read Data Continuous mode. There are no SCLK rate restrictions for this command, but the next command must wait for 4 tCLK cycles before completion.

9.5.3.9 RDATA: Read Data

The RDATA command loads the output shift register with the latest data when not in Read Data Continuous mode. Issue this command after DRDY goes low to read the conversion result. There are no SCLK rate restrictions for this command, and there is no wait time needed for the subsequent commands or data retrieval SCLKs. To retrieve data from the device after the RDATA command is issued, make sure either the START pin is high or the START command is issued. When reading data with the RDATA command, the read operation can overlap the next DRDY occurrence without data corruption. Figure 47 shows the recommended way to use the RDATA command. RDATA is best suited for ECG- and EEG-type systems, where register settings must be read or changed often between conversion cycles.

9.5.3.10 RREG: Read From Register

This command reads register data. The Register Read command is a two-byte command followed by the register data output. The first byte contains the command and register address. The second command byte specifies the number of registers to read – 1.

First command byte: 001r rrrr, where r rrrr is the starting register address.

Second command byte: 000n nnnn, where n nnnn is the number of registers to read – 1.

The 17th SCLK rising edge of the operation clocks out the MSB of the first register, as shown in Figure 48. When the device is in read data continuous mode, an SDATAC command must be issued before the RREG command can be issued. The RREG command can be issued any time. However, because this command is a multi-byte command, there are SCLK rate restrictions depending on how the SCLKs are issued to meet the tSDECODE timing. See the Serial Clock (SCLK) subsection of the SPI Interface section for more details. Note that CS must be low for the entire command.

Figure 48. RREG Command Example: Read Two Registers Starting from Register 00h (ID Register)

Figure 48. RREG Command Example: Read Two Registers Starting from Register 00h (ID Register)(BYTE 1 = 0010 0000, BYTE 2 = 0000 0001)

9.5.3.11 WREG: Write to Register

This command writes register data. The Register Write command is a two-byte command followed by the register data input. The first byte contains the command and register address. The second command byte specifies the number of registers to write – 1.

First command byte: 010r rrrr, where r rrrr is the starting register address.

Second command byte: 000n nnnn, where n nnnn is the number of registers to write – 1.

After the command bytes, the register data follows (in MSB-first format), as shown in Figure 49. The WREG command can be issued any time. However, because this command is a multi-byte command, there are SCLK rate restrictions depending on how the SCLKs are issued to meet the tSDECODE timing. See the Serial Clock (SCLK) subsection of the SPI Interface section for more details. Note that CS must be low for the entire command.

9.6 Register Maps

Table 11 describes the various ADS1299-x registers.

Table 11. Register Assignments

| ADDRESS | REGISTER | DEFAULT SETTING | REGISTER BITS | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

| Read Only ID Registers | ||||||||||

| 00h | ID | xxh | REV_ID[2:0] | 1 | DEV_ID[1:0] | NU_CH[1:0] | ||||

| Global Settings Across Channels | ||||||||||

| 01h | CONFIG1 | 96h | 1 | DAISY_EN | CLK_EN | 1 | 0 | DR[2:0] | ||

| 02h | CONFIG2 | C0h | 1 | 1 | 0 | INT_CAL | 0 | CAL_AMP0 | CAL_FREQ[1:0] | |

| 03h | CONFIG3 | 60h | PD_REFBUF | 1 | 1 | BIAS_MEAS | BIASREF_INT | PD_BIAS | BIAS_LOFF_ SENS |

BIAS_STAT |

| 04h | LOFF | 00h | COMP_TH[2:0] | 0 | ILEAD_OFF[1:0] | FLEAD_OFF[1:0] | ||||

| Channel-Specific Settings | ||||||||||

| 05h | CH1SET | 61h | PD1 | GAIN1[2:0] | SRB2 | MUX1[2:0] | ||||

| 06h | CH2SET | 61h | PD2 | GAIN2[2:0] | SRB2 | MUX2[2:0] | ||||

| 07h | CH3SET | 61h | PD3 | GAIN3[2:0] | SRB2 | MUX3[2:0] | ||||

| 08h | CH4SET | 61h | PD4 | GAIN4[2:0] | SRB2 | MUX4[2:0] | ||||

| 09h | CH5SET (1) | 61h | PD5 | GAIN5[2:0] | SRB2 | MUX5[2:0] | ||||

| 0Ah | CH6SET (1) | 61h | PD6 | GAIN6[2:0] | SRB2 | MUX6[2:0] | ||||

| 0Bh | CH7SET (2) | 61h | PD7 | GAIN7[2:0] | SRB2 | MUX7[2:0] | ||||

| 0Ch | CH8SET (2) | 61h | PD8 | GAIN8[2:0] | SRB2 | MUX8[2:0] | ||||

| 0Dh | BIAS_SENSP | 00h | BIASP8(2) | BIASP7(2) | BIASP6(1) | BIASP5(1) | BIASP4 | BIASP3 | BIASP2 | BIASP1 |

| 0Eh | BIAS_SENSN | 00h | BIASN8(2) | BIASN7(2) | BIASN6(1) | BIASN5(1) | BIASN4 | BIASN3 | BIASN2 | BIASN1 |

| 0Fh | LOFF_SENSP | 00h | LOFFP8(2) | LOFFP7(2) | LOFFP6(1) | LOFFP5(1) | LOFFP4 | LOFFP3 | LOFFP2 | LOFFP1 |

| 10h | LOFF_SENSN | 00h | LOFFM8(2) | LOFFM7(2) | LOFFM6(1) | LOFFM5(1) | LOFFM4 | LOFFM3 | LOFFM2 | LOFFM1 |

| 11h | LOFF_FLIP | 00h | LOFF_FLIP8(2) | LOFF_FLIP7(2) | LOFF_FLIP6(1) | LOFF_FLIP5(1) | LOFF_FLIP4 | LOFF_FLIP3 | LOFF_FLIP2 | LOFF_FLIP1 |

| Lead-Off Status Registers (Read-Only Registers) | ||||||||||

| 12h | LOFF_STATP | 00h | IN8P_OFF | IN7P_OFF | IN6P_OFF | IN5P_OFF | IN4P_OFF | IN3P_OFF | IN2P_OFF | IN1P_OFF |

| 13h | LOFF_STATN | 00h | IN8M_OFF | IN7M_OFF | IN6M_OFF | IN5M_OFF | IN4M_OFF | IN3M_OFF | IN2M_OFF | IN1M_OFF |

| GPIO and OTHER Registers | ||||||||||

| 14h | GPIO | 0Fh | GPIOD[4:1] | GPIOC[4:1] | ||||||

| 15h | MISC1 | 00h | 0 | 0 | SRB1 | 0 | 0 | 0 | 0 | 0 |

| 16h | MISC2 | 00h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 17h | CONFIG4 | 00h | 0 | 0 | 0 | 0 | SINGLE_ SHOT |

0 | PD_LOFF_

COMP |

0 |

9.6.1 User Register Description

The read-only ID control register is programmed during device manufacture to indicate device characteristics.

9.6.1.1 ID: ID Control Register (address = 00h) (reset = xxh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| REV_ID[2:0] | 1 | DEV_ID[1:0] | NU_CH[1:0] | ||||

| R-xh | R-1h | R-3h | R-xh | ||||

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 12. ID Control Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7:5 | REV_ID[2:0] | R | xh | Reserved.

These bits indicate the revision of the device and are subject to change without notice. |

| 4 | Reserved | R | 1h | Reserved.

Always read 1. |

| 3:2 | DEV_ID[1:0] | R | 3h | Device Identification.

These bits indicates the device. 11 : ADS1299-x |

| 1:0 | NU_CH[1:0] | R | xh | Number of Channels.

These bits indicates number of channels. 00 : 4-channel ADS1299-4 01 : 6-channel ADS1299-6 10 : 8-channel ADS1299 |

9.6.1.2 CONFIG1: Configuration Register 1 (address = 01h) (reset = 96h)

This register configures the DAISY_EN bit, clock, and data rate.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | DAISY_EN | CLK_EN | 1 | 0 | DR[2:0] | ||

| R/W-1h | R/W-0h | R/W-0h | R/W-1h | R/W-0h | R/W-6h | ||

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 13. Configuration Register 1 Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | Reserved | R/W | 1h | Reserved

Always write 1h |

| 6 | DAISY_EN | R/W | 0h | Daisy-chain or multiple readback mode

This bit determines which mode is enabled. 0 : Daisy-chain mode 1 : Multiple readback mode |

| 5 | CLK_EN | R/W | 0h | CLK connection(1)

This bit determines if the internal oscillator signal is connected to the CLK pin when the CLKSEL pin = 1. 0 : Oscillator clock output disabled 1 : Oscillator clock output enabled |

| 4:3 | Reserved | R/W | 2h | Reserved

Always write 2h |

| 2:0 | DR[2:0] | R/W | 6h | Output data rate

These bits determine the output data rate of the device. fMOD = fCLK / 2. 000 : fMOD / 64 (16 kSPS) 001 : fMOD / 128 (8 kSPS) 010 : fMOD / 256 (4 kSPS) 011 : fMOD / 512 (2 kSPS) 100 : fMOD / 1024 (1 kSPS) 101 : fMOD / 2048 (500 SPS) 110 : fMOD / 4096 (250 SPS) 111 : Reserved (do not use) |

9.6.1.3 CONFIG2: Configuration Register 2 (address = 02h) (reset = C0h)

This register configures the test signal generation. See the Input Multiplexer section for more details.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | 1 | 0 | INT_CAL | 0 | CAL_AMP | CAL_FREQ[1:0] | |

| R/W-1h | R/W-1h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 14. Configuration Register 2 Field Descriptions

9.6.1.4 CONFIG3: Configuration Register 3 (address = 03h) (reset = 60h)

Configuration register 3 configures either an internal or exteral reference and BIAS operation.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PD_REFBUF | 1 | 1 | BIAS_MEAS | BIASREF_INT | PD_BIAS | BIAS_LOFF_ SENS |

BIAS_STAT |

| R/W-0h | R/W-1h | R/W-1h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 15. Configuration Register 3 Field Descriptions

9.6.1.5 LOFF: Lead-Off Control Register (address = 04h) (reset = 00h)

The lead-off control register configures the lead-off detection operation.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| COMP_TH2[2:0] | 0 | ILEAD_OFF[1:0] | FLEAD_OFF[1:0] | ||||

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | ||||

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 16. Lead-Off Control Register Field Descriptions

9.6.1.6 CHnSET: Individual Channel Settings (n = 1 to 8) (address = 05h to 0Ch) (reset = 61h)

The CH[1:8]SET control register configures the power mode, PGA gain, and multiplexer settings channels. See the Input Multiplexer section for details. CH[2:8]SET are similar to CH1SET, corresponding to the respective channels.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PDn | GAINn[2:0] | SRB2 | MUXn[2:0] | ||||

| R/W-0h | R/W-6h | R/W-0h | R/W-0h | ||||

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 17. Individual Channel Settings (n = 1 to 8) Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | PDn | R/W | 0h |

Power-down This bit determines the channel power mode for the corresponding channel. 0 : Normal operation 1 : Channel power-down. When powering down a channel, TI recommends that the channel be set to input short by setting the appropriate MUXn[2:0] = 001 of the CHnSET register. |

| 6:4 | GAINn[2:0] | R/W | 6h | PGA gain

These bits determine the PGA gain setting. 000 : 1 001 : 2 010 : 4 011 : 6 100 : 8 101 : 12 110 : 24 111 : Do not use |

| 3 | SRB2 | R/W | 0h | SRB2 connection

This bit determines the SRB2 connection for the corresponding channel. 0 : Open 1 : Closed |

| 2:0 | MUXn[2:0] | R/W | 1h | Channel input

These bits determine the channel input selection. 000 : Normal electrode input 001 : Input shorted (for offset or noise measurements) 010 : Used in conjunction with BIAS_MEAS bit for BIAS measurements. 011 : MVDD for supply measurement 100 : Temperature sensor 101 : Test signal 110 : BIAS_DRP (positive electrode is the driver) 111 : BIAS_DRN (negative electrode is the driver) |

9.6.1.7 BIAS_SENSP: Bias Drive Positive Derivation Register (address = 0Dh) (reset = 00h)

This register controls the selection of the positive signals from each channel for bias voltage (BIAS) derivation. See the Bias Drive (DC Bias Circuit) section for details.

Registers bits[5:4] are not available for the ADS1299-4. Register bits[7:6] are not available for the ADS1299-4, or ADS1299-6. Set unavailable bits for the associated device to 0 when writing to the register.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BIASP8 | BIASP7 | BIASP6 | BIASP5 | BIASP4 | BIASP3 | BIASP2 | BIASP1 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 18. BIAS Positive Signal Derivation Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | BIASP8 | R/W | 0h | IN8P to BIAS

Route channel 8 positive signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 6 | BIASP7 | R/W | 0h | IN7P to BIAS

Route channel 7 positive signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 5 | BIASP6 | R/W | 0h | IN6P to BIAS

Route channel 6 positive signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 4 | BIASP5 | R/W | 0h | IN5P to BIAS

Route channel 5 positive signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 3 | BIASP4 | R/W | 0h | IN4P to BIAS

Route channel 4 positive signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 2 | BIASP3 | R/W | 0h | IN3P to BIAS

Route channel 3 positive signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 1 | BIASP2 | R/W | 0h | IN2P to BIAS

Route channel 2 positive signal into BIAS channel 0 : Disabled 1 : Enabled |

| 0 | BIASP1 | R/W | 0h | IN1P to BIAS

Route channel 1 positive signal into BIAS channel 0 : Disabled 1 : Enabled |

9.6.1.8 BIAS_SENSN: Bias Drive Negative Derivation Register (address = 0Eh) (reset = 00h)

This register controls the selection of the negative signals from each channel for bias voltage (BIAS) derivation. See the Bias Drive (DC Bias Circuit) section for details.

Registers bits[5:4] are not available for the ADS1299-4. Register bits[7:6] are not available for the ADS1299-4, or ADS1299-6. Set unavailable bits for the associated device to 0 when writing to the register.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BIASN8 | BIASN7 | BIASN6 | BIASN5 | BIASN4 | BIASN3 | BIASN2 | BIASN1 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 19. BIAS Negative Signal Derivation Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | BIASN8 | R/W | 0h | IN8N to BIAS

Route channel 8 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 6 | BIASN7 | R/W | 0h | IN7N to BIAS

Route channel 7 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 5 | BIASN6 | R/W | 0h | IN6N to BIAS

Route channel 6 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 4 | BIASN5 | R/W | 0h | IN5N to BIAS

Route channel 5 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 3 | BIASN4 | R/W | 0h | IN4N to BIAS

Route channel 4 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 2 | BIASN3 | R/W | 0h | IN3N to BIAS

Route channel 3 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 1 | BIASN2 | R/W | 0h | IN2N to BIAS

Route channel 2 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

| 0 | BIASN1 | R/W | 0h | IN1N to BIAS

Route channel 1 negative signal into BIAS derivation 0 : Disabled 1 : Enabled |

9.6.1.9 LOFF_SENSP: Positive Signal Lead-Off Detection Register (address = 0Fh) (reset = 00h)

This register selects the positive side from each channel for lead-off detection. See the Lead-Off Detection section for details. The LOFF_STATP register bits are only valid if the corresponding LOFF_SENSP bits are set to 1.

Registers bits[5:4] are not available for the ADS1299-4. Register bits[7:6] are not available for the ADS1299-4, or ADS1299-6. Set unavailable bits for the associated device to 0 when writing to the register.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LOFFP8 | LOFFP7 | LOFFP6 | LOFFP5 | LOFFP4 | LOFFP3 | LOFFP2 | LOFFP1 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 20. Positive Signal Lead-Off Detection Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | LOFFP8 | R/W | 0h | IN8P lead off

Enable lead-off detection on IN8P 0 : Disabled 1 : Enabled |

| 6 | LOFFP7 | R/W | 0h | IN7P lead off

Enable lead-off detection on IN7P 0 : Disabled 1 : Enabled |

| 5 | LOFFP6 | R/W | 0h | IN6P lead off

Enable lead-off detection on IN6P 0 : Disabled 1 : Enabled |

| 4 | LOFFP5 | R/W | 0h | IN5P lead off

Enable lead-off detection on IN5P 0 : Disabled 1 : Enabled |

| 3 | LOFFP4 | R/W | 0h | IN4P lead off

Enable lead-off detection on IN4P 0 : Disabled 1 : Enabled |

| 2 | LOFFP3 | R/W | 0h | IN3P lead off

Enable lead-off detection on IN3P 0 : Disabled 1 : Enabled |

| 1 | LOFFP2 | R/W | 0h | IN2P lead off

Enable lead-off detection on IN2P 0 : Disabled 1 : Enabled |

| 0 | LOFFP1 | R/W | 0h | IN1P lead off

Enable lead-off detection on IN1P 0 : Disabled 1 : Enabled |

9.6.1.10 LOFF_SENSN: Negative Signal Lead-Off Detection Register (address = 10h) (reset = 00h)

This register selects the negative side from each channel for lead-off detection. See the Lead-Off Detection section for details. The LOFF_STATN register bits are only valid if the corresponding LOFF_SENSN bits are set to 1.

Registers bits[5:4] are not available for the ADS1299-4. Register bits[7:6] are not available for the ADS1299-4, or ADS1299-6. Set unavailable bits for the associated device to 0 when writing to the register.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LOFFM8 | LOFFM7 | LOFFM6 | LOFFM5 | LOFFM4 | LOFFM3 | LOFFM2 | LOFFM1 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 21. Negative Signal Lead-Off Detection Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | LOFFM8 | R/W | 0h | IN8N lead off

Enable lead-off detection on IN8N 0 : Disabled 1 : Enabled |

| 6 | LOFFM7 | R/W | 0h | IN7N lead off

Enable lead-off detection on IN7N 0 : Disabled 1 : Enabled |

| 5 | LOFFM6 | R/W | 0h | IN6N lead off

Enable lead-off detection on IN6N 0 : Disabled 1 : Enabled |

| 4 | LOFFM5 | R/W | 0h | IN5N lead off

Enable lead-off detection on IN5N 0 : Disabled 1 : Enabled |

| 3 | LOFFM4 | R/W | 0h | IN4N lead off

Enable lead-off detectionn on IN4N 0 : Disabled 1 : Enabled |

| 2 | LOFFM3 | R/W | 0h | IN3N lead off

Enable lead-off detectionion on IN3N 0 : Disabled 1 : Enabled |

| 1 | LOFFM2 | R/W | 0h | IN2N lead off

Enable lead-off detectionction on IN2N 0 : Disabled 1 : Enabled |

| 0 | LOFFM1 | R/W | 0h | IN1N lead off

Enable lead-off detectionction on IN1N 0 : Disabled 1 : Enabled |

9.6.1.11 LOFF_FLIP: Lead-Off Flip Register (address = 11h) (reset = 00h)

This register controls the direction of the current used for lead-off derivation. See the Lead-Off Detection section for details.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LOFF_FLIP8 | LOFF_FLIP7 | LOFF_FLIP6 | LOFF_FLIP5 | LOFF_FLIP4 | LOFF_FLIP3 | LOFF_FLIP2 | LOFF_FLIP1 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 22. Lead-Off Flip Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | LOFF_FLIP8 | R/W | 0h | Channel 8 LOFF polarity flip

Flip the pull-up or pull-down polarity of the current source on channel 8 for lead-off detection. 0 : No flip = IN8P is pulled to AVDD and IN8N pulled to AVSS 1 : Flipped = IN8P is pulled to AVSS and IN8N pulled to AVDD |

| 6 | LOFF_FLIP7 | R/W | 0h | Channel 7 LOFF polarity flip

Flip the pull-up or pull-down polarity of the current source on channel 7 for lead-off detection. 0 : No flip = IN7P is pulled to AVDD and IN7N pulled to AVSS 1 : Flipped = IN7P is pulled to AVSS and IN7N pulled to AVDD |

| 5 | LOFF_FLIP6 | R/W | 0h | Channel 6 LOFF polarity flip

Flip the pull-up or pull-down polarity of the current source on channel 6 for lead-off detection. 0 : No flip = IN6P is pulled to AVDD and IN6N pulled to AVSS 1 : Flipped = IN6P is pulled to AVSS and IN6N pulled to AVDD |

| 4 | LOFF_FLIP5 | R/W | 0h | Channel 5 LOFF polarity flip

Flip the pull-up or pull-down polarity of the current source on channel 5 for lead-off detection. 0 : No flip = IN5P is pulled to AVDD and IN5N pulled to AVSS 1 : Flipped = IN5P is pulled to AVSS and IN5N pulled to AVDD |

| 3 | LOFF_FLIP4 | R/W | 0h | Channel 4 LOFF polarity flip

Flip the pull-up or pull-down polarity of the current source on channel 4 for lead-off detection. 0 : No flip = IN4P is pulled to AVDD and IN4N pulled to AVSS 1 : Flipped = IN4P is pulled to AVSS and IN4N pulled to AVDD |

| 2 | LOFF_FLIP3 | R/W | 0h | Channel 3 LOFF polarity flip

Flip the pull-up or pull-down polarity of the current source on channel 3 for lead-off detection. 0 : No flip = IN3P is pulled to AVDD and IN3N pulled to AVSS 1 : Flipped = IN3P is pulled to AVSS and IN3N pulled to AVDD |

| 1 | LOFF_FLIP2 | R/W | 0h | Channel 2 LOFF Polarity Flip

Flip the pull-up or pull-down polarity of the current source on channel 2 for lead-off detection. 0 : No flip = IN2P is pulled to AVDD and IN2N pulled to AVSS 1 : Flipped = IN2P is pulled to AVSS and IN2N pulled to AVDD |

| 0 | LOFF_FLIP1 | R/W | 0h | Channel 1 LOFF Polarity Flip

Flip the pull-up or pull-down polarity of the current source on channel 1 for lead-off detection. 0 : No flip = IN1P is pulled to AVDD and IN1N pulled to AVSS 1 : Flipped = IN1P is pulled to AVSS and IN1N pulled to AVDD |

9.6.1.12 LOFF_STATP: Lead-Off Positive Signal Status Register (address = 12h) (reset = 00h)

This register stores the status of whether the positive electrode on each channel is on or off. See the Lead-Off Detection section for details. Ignore the LOFF_STATP values if the corresponding LOFF_SENSP bits are not set to 1.

When the LOFF_SENSEP bits are 0, the LOFF_STATP bits should be ignored.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| IN8P_OFF | IN7P_OFF | IN6P_OFF | IN5P_OFF | IN4P_OFF | IN3P_OFF | IN2P_OFF | IN1P_OFF |

| R-0h | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 23. Lead-Off Positive Signal Status Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | IN8P_OFF | R | 0h | Channel 8 positive channel lead-off status

Status of whether IN8P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 6 | IN7P_OFF | R | 0h | Channel 7 positive channel lead-off status

Status of whether IN7P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 5 | IN6P_OFF | R | 0h | Channel 6 positive channel lead-off status

Status of whether IN6P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 4 | IN5P_OFF | R | 0h | Channel 5 positive channel lead-off status

Status of whether IN5P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 3 | IN4P_OFF | R | 0h | Channel 4 positive channel lead-off status

Status of whether IN4P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 2 | IN3P_OFF | R | 0h | Channel 3 positive channel lead-off status

Status of whether IN3P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 1 | IN2P_OFF | R | 0h | Channel 2 positive channel lead-off status

Status of whether IN2P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 0 | IN1P_OFF | R | 0h | Channel 1 positive channel lead-off status

Status of whether IN1P electrode is on or off 0 : Electrode is on 1 : Electrode is off |

9.6.1.13 LOFF_STATN: Lead-Off Negative Signal Status Register (address = 13h) (reset = 00h)

This register stores the status of whether the negative electrode on each channel is on or off. See the Lead-Off Detection section for details. Ignore the LOFF_STATN values if the corresponding LOFF_SENSN bits are not set to 1.

When the LOFF_SENSEN bits are 0, the LOFF_STATP bits should be ignored.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| IN8N_OFF | IN7N_OFF | IN6N_OFF | IN5N_OFF | IN4N_OFF | IN3N_OFF | IN2N_OFF | IN1N_OFF |

| R-0h | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 24. Lead-Off Negative Signal Status Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7 | IN8N_OFF | R | 0h | Channel 8 negative channel lead-off status

Status of whether IN8N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 6 | IN7N_OFF | R | 0h | Channel 7 negative channel lead-off status

Status of whether IN7N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 5 | IN6N_OFF | R | 0h | Channel 6 negative channel lead-off status

Status of whether IN6N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 4 | IN5N_OFF | R | 0h | Channel 5 negative channel lead-off status

Status of whether IN5N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 3 | IN4N_OFF | R | 0h | Channel 4 negative channel lead-off status

Status of whether IN4N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 2 | IN3N_OFF | R | 0h | Channel 3 negative channel lead-off status

Status of whether IN3N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 1 | IN2N_OFF | R | 0h | Channel 2 negative channel lead-off status

Status of whether IN2N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

| 0 | IN1N_OFF | R | 0h | Channel 1 negative channel lead-off status

Status of whether IN1N electrode is on or off 0 : Electrode is on 1 : Electrode is off |

9.6.1.14 GPIO: General-Purpose I/O Register (address = 14h) (reset = 0Fh)

The general-purpose I/O register controls the action of the three GPIO pins. When RESP_CTRL[1:0] is in mode 01 and 11, the GPIO2, GPIO3, and GPIO4 pins are not available for use.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| GPIOD[4:1] | GPIOC[4:1] | ||||||

| R/W-0h | R/W-Fh | ||||||

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 25. General-Purpose I/O Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7:4 | GPIOD[4:1] | R/W | 0h | GPIO data

These bits are used to read and write data to the GPIO ports. When reading the register, the data returned correspond to the state of the GPIO external pins, whether they are programmed as inputs or as outputs. As outputs, a write to the GPIOD sets the output value. As inputs, a write to the GPIOD has no effect. GPIO is not available in certain respiration modes. |

| 3:0 | GPIOC[4:1] | R/W | Fh | GPIO control (corresponding GPIOD)

These bits determine if the corresponding GPIOD pin is an input or output. 0 : Output 1 : Input |

9.6.1.15 MISC1: Miscellaneous 1 Register (address = 15h) (reset = 00h)

This register provides the control to route the SRB1 pin to all inverting inputs of the four, six, or eight channels (ADS1299-4, ADS1299-6, or ADS1299).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | SRB1 | 0 | 0 | 0 | 0 | 0 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 26. Miscellaneous 1 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7:6 | Reserved | R/W | 0h | Reserved

Always write 0h |

| 5 | SRB1 | R/W | 0h | Stimulus, reference, and bias 1

This bit connects the SRB1 to all 4, 6, or 8 channels inverting inputs 0 : Switches open 1 : Switches closed |

| 4:0 | Reserved | R/W | 0h | Reserved

Always write 0h |

9.6.1.16 MISC2: Miscellaneous 2 (address = 16h) (reset = 00h)

This register is reserved for future use.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 27. Miscellaneous 1 Register Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7:0 | Reserved | R/W | 0h | Reserved

Always write 0h |

9.6.1.17 CONFIG4: Configuration Register 4 (address = 17h) (reset = 00h)

This register configures the conversion mode and enables the lead-off comparators.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0 | 0 | 0 | SINGLE_SHOT | 0 | PD_LOFF_ COMP | 0 |

| R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 28. Configuration Register 4 Field Descriptions

| Bit | Field | Type | Reset | Description |

|---|---|---|---|---|

| 7:4 | Reserved | R/W | 0h | Reserved

Always write 0h |

| 3 | SINGLE_SHOT | R/W | 0h | Single-shot conversion

This bit sets the conversion mode. 0 : Continuous conversion mode 1 : Single-shot mode |

| 2 | Reserved | R/W | 0h | Reserved

Always write 0h |

| 1 | PD_LOFF_COMP | R/W | 0h | Lead-off comparator power-down

This bit powers down the lead-off comparators. 0 : Lead-off comparators disabled 1 : Lead-off comparators enabled |

| 0 | Reserved | R/W | 0h | Reserved

Always write 0h |