SBASB81 December 2024 AFE5401-EP

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Electrical Characteristics

- 5.6 Digital Characteristics

- 5.7 Timing Requirements: Output Interface

- 5.8 Timing Requirements: RESET

- 5.9 Timing Requirements: Serial Interface Operation

- 5.10 Typical Characteristics

- 6 Parameter Measurement Information

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Revision History

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGC|64

Thermal pad, mechanical data (Package|Pins)

- RGC|64

Orderable Information

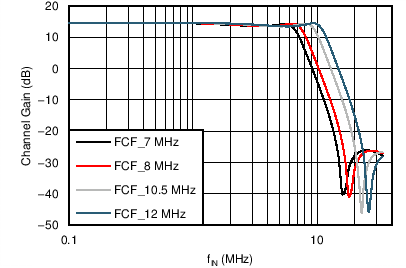

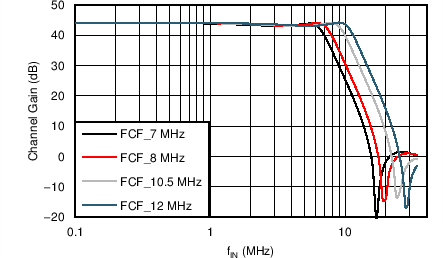

7.3.3 Antialiasing Filter

The device introduces a third-order, elliptic, active, antialias, low-pass filter (LPF) in the analog signal path. The filter –3-dB corner frequency can be configured using the FILTER_BW register, as shown in Table 7-3. The corresponding frequency response plots are shown in Figure 7-2 and Figure 7-3.

Table 7-3 FILTER_BW Register

| FILTER_BW | CORNER FREQUENCY (MHz) |

|---|---|

| 0 | 8 |

| 1 | 7 |

| 2 | 10.5 |

| 3 | 12 |