SBASB81 December 2024 AFE5401-EP

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Electrical Characteristics

- 5.6 Digital Characteristics

- 5.7 Timing Requirements: Output Interface

- 5.8 Timing Requirements: RESET

- 5.9 Timing Requirements: Serial Interface Operation

- 5.10 Typical Characteristics

- 6 Parameter Measurement Information

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Revision History

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGC|64

Thermal pad, mechanical data (Package|Pins)

- RGC|64

Orderable Information

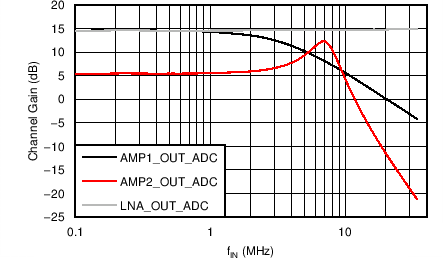

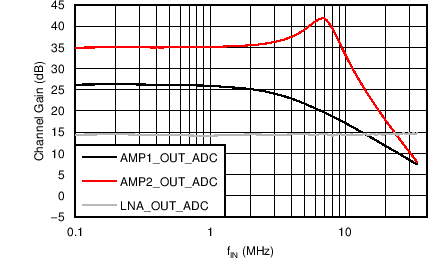

7.4.7 Signal Chain Probe

To enhance system-level debug capabilities, the device offers a mode where the output of each block in the signal chain can be connected to the ADC input. With this mode, internal signals can be easily monitored to ensure that each block output is not saturated. Figure 7-17 shows the device signal chain block diagram. Figure 7-18 and Figure 7-19 show typical frequency response plots at the output of each stage.

Figure 7-17 Signal Chain Block Diagram

Figure 7-17 Signal Chain Block Diagram Figure 7-18 Frequency Response for VOUT_ON_ADC Settings (PGA Gain = 0 dB)

Figure 7-18 Frequency Response for VOUT_ON_ADC Settings (PGA Gain = 0 dB) Figure 7-19 Frequency Response for VOUT_ON_ADC Settings (PGA Gain = 30 dB)

Figure 7-19 Frequency Response for VOUT_ON_ADC Settings (PGA Gain = 30 dB)