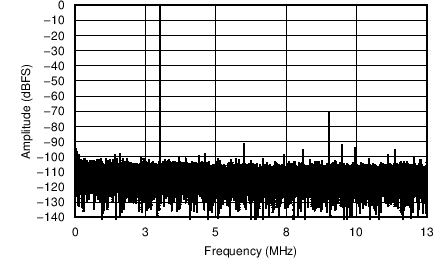

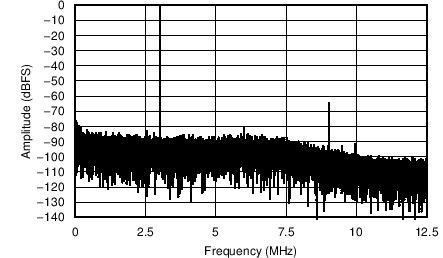

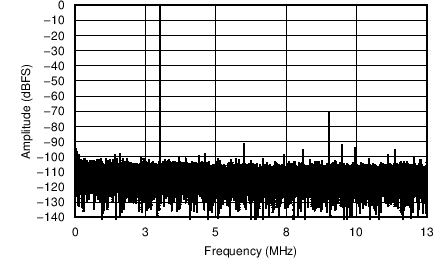

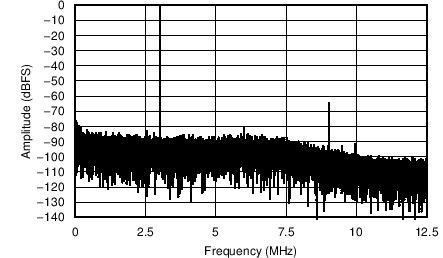

Typical values are at TA = +25°C, AVDD18 = DVDD18 = 1.8 V, AVDD3 = DRVDD = 3.3 V, –1-dBFS analog input ac-coupled with a 0.1-μF capacitor, AFE_CLK = 25 MHz, LNA gain = 15 dB, PGA gain = 0 dB, default mode, antialiasing filter corner frequency = 8 MHz, and differential input sine wave clock with 50% duty cycle, unless otherwise noted.

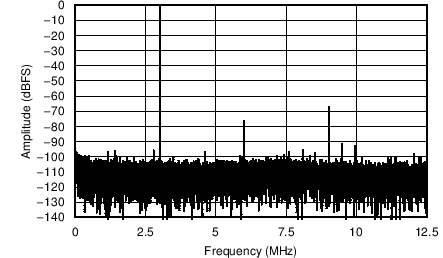

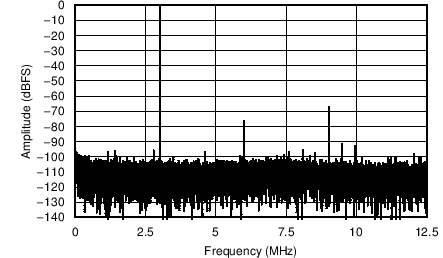

| SNR = 67.7 dBFS | SFDR = 65.7 dBc | THD = 65.2 dBc |

| fIN1 = 1.5 MHz | Each Tone at –7-dBFS Amplitude |

| fIN2 = 2 MHz | Two-Tone IMD = –83 dBFS |

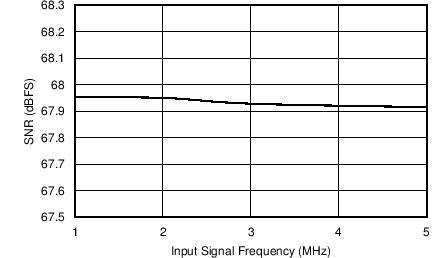

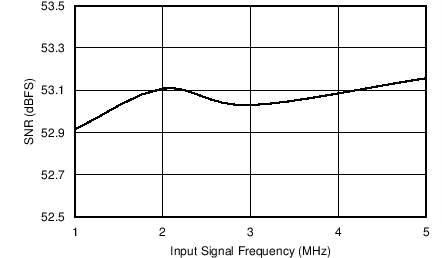

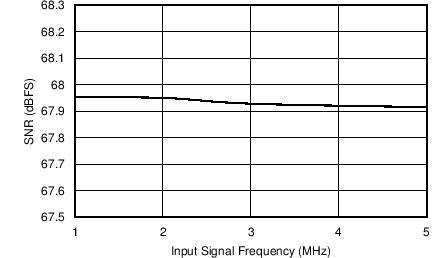

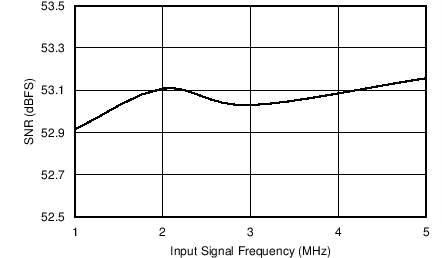

Figure 5-9 Signal-to-Noise Ratio vs Input Signal Frequency (PGA Gain = 0 dB)

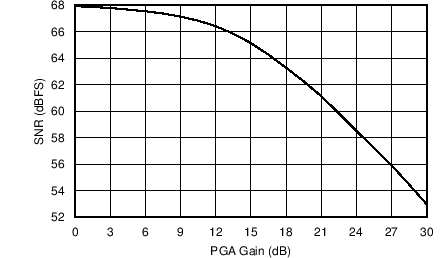

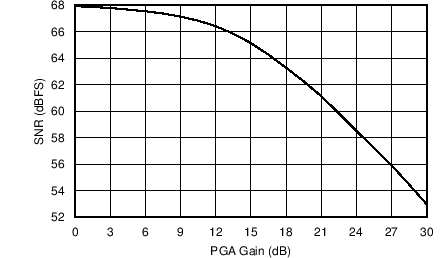

Figure 5-9 Signal-to-Noise Ratio vs Input Signal Frequency (PGA Gain = 0 dB) Figure 5-11 Signal-to-Noise Ratio vs PGA Gain

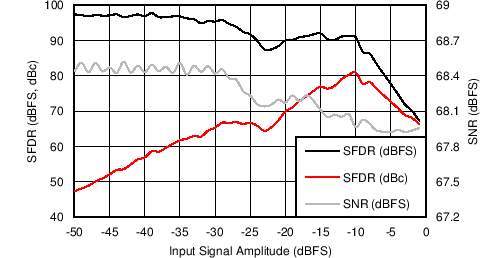

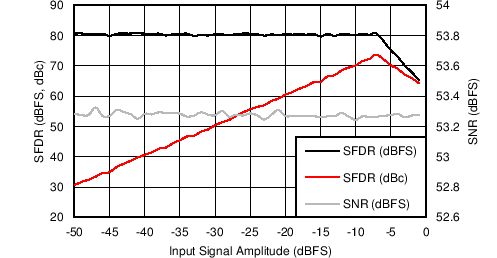

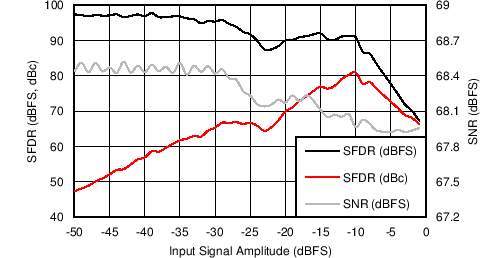

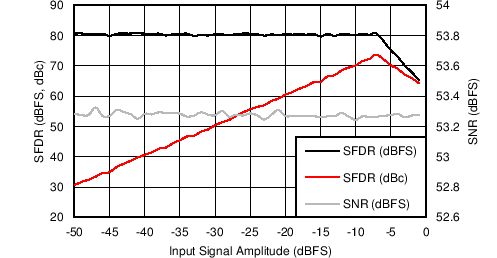

Figure 5-11 Signal-to-Noise Ratio vs PGA Gain Figure 5-13 Signal-to-Noise Ratio, Spurious-Free Dynamic Range vs Input Signal Amplitude (PGA Gain = 0 dB)

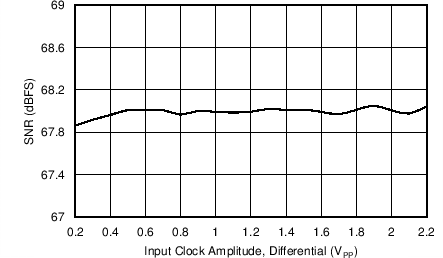

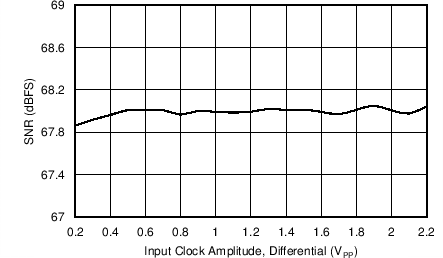

Figure 5-13 Signal-to-Noise Ratio, Spurious-Free Dynamic Range vs Input Signal Amplitude (PGA Gain = 0 dB) Figure 5-15 Signal-to-Noise Ratio vs Input Clock Amplitude (PGA Gain = 0 dB)

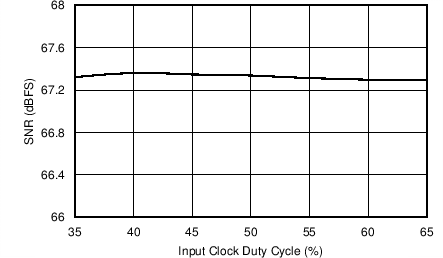

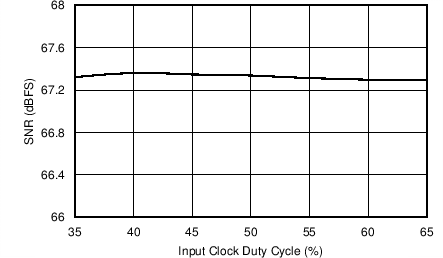

Figure 5-15 Signal-to-Noise Ratio vs Input Clock Amplitude (PGA Gain = 0 dB) Figure 5-17 Signal-to-Noise Ratio vs Input Clock Duty Cycle (PGA Gain = 0 dB)

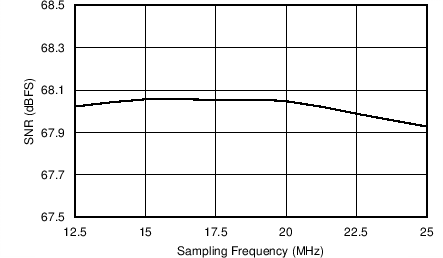

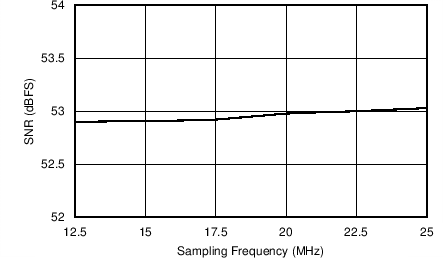

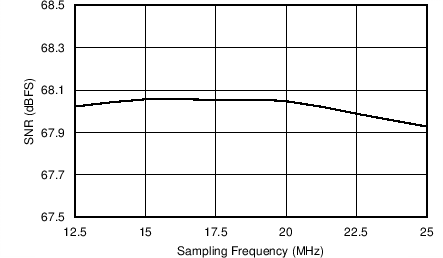

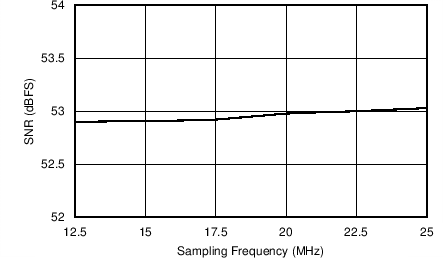

Figure 5-17 Signal-to-Noise Ratio vs Input Clock Duty Cycle (PGA Gain = 0 dB) Figure 5-19 Signal-to-Noise Ratio vs Sampling Frequency (PGA Gain = 0 dB)

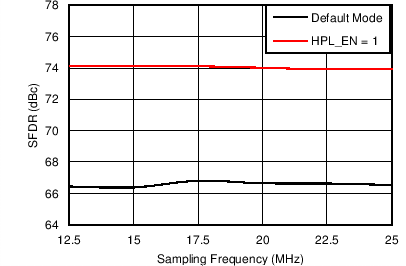

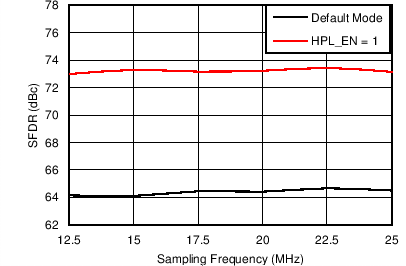

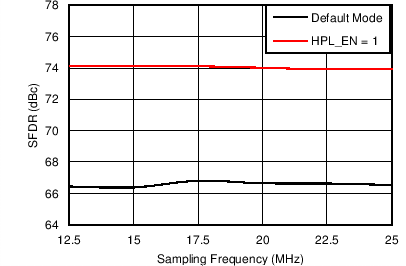

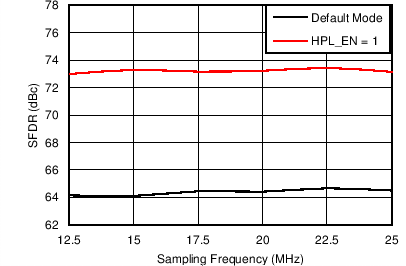

Figure 5-19 Signal-to-Noise Ratio vs Sampling Frequency (PGA Gain = 0 dB) Figure 5-21 Spurious-Free Dynamic Range vs Sampling Frequency (PGA Gain = 0 dB)

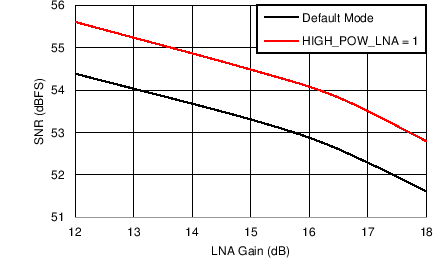

Figure 5-21 Spurious-Free Dynamic Range vs Sampling Frequency (PGA Gain = 0 dB) Figure 5-23 Signal-to-Noise Ratio vs LNA Gain (PGA Gain = 30 dB)

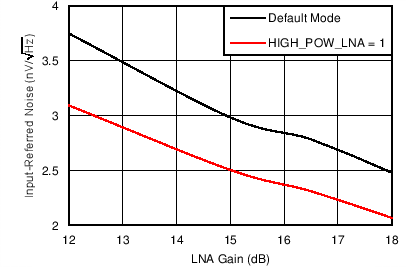

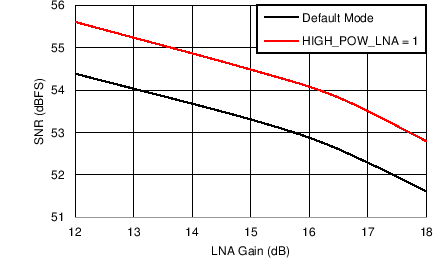

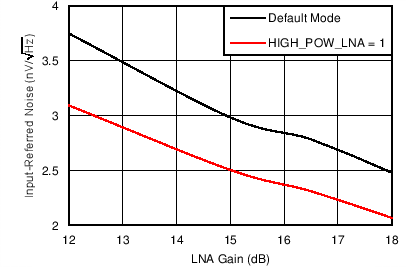

Figure 5-23 Signal-to-Noise Ratio vs LNA Gain (PGA Gain = 30 dB) Figure 5-25 Input-Referred Noise vs LNA Gain (PGA Gain = 30 dB)

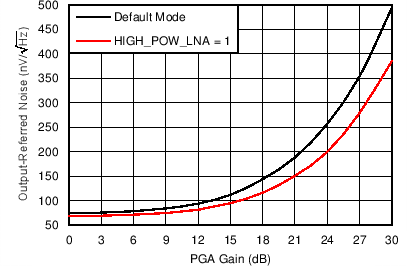

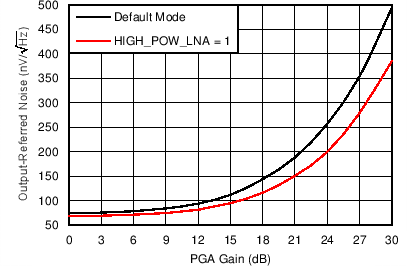

Figure 5-25 Input-Referred Noise vs LNA Gain (PGA Gain = 30 dB) Figure 5-27 Output-Referred Noise vs PGA Gain

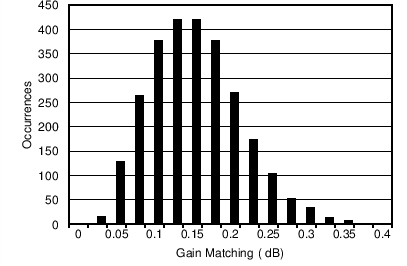

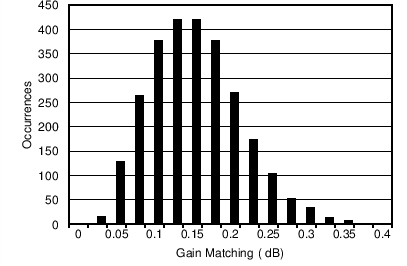

Figure 5-27 Output-Referred Noise vs PGA Gain Figure 5-29 Gain Matching Histogram (Maximum Gain Difference Among the Four Channels within a Device)

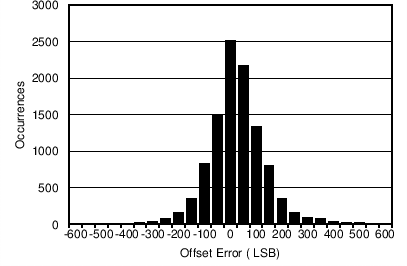

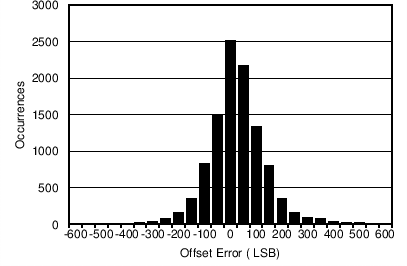

Figure 5-29 Gain Matching Histogram (Maximum Gain Difference Among the Four Channels within a Device) Figure 5-31 Offset Error Histogram at PGA Gain = 30 dB

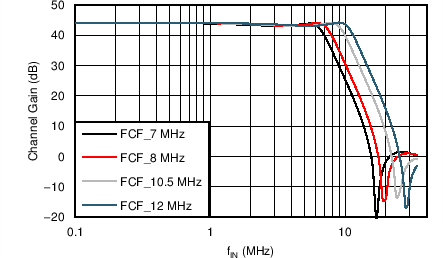

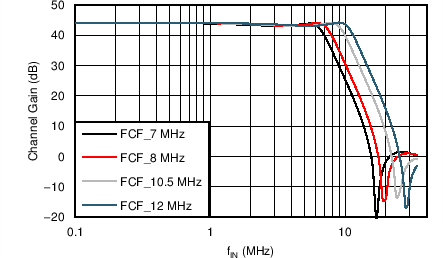

Figure 5-31 Offset Error Histogram at PGA Gain = 30 dB Figure 5-33 Antialias Filter Response vs FILTER_BW Settings (PGA Gain = 30 dB)

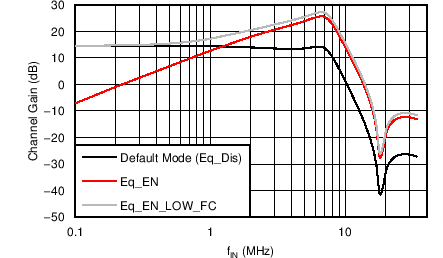

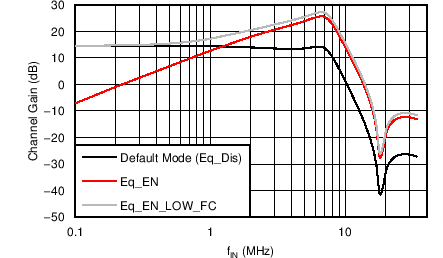

Figure 5-33 Antialias Filter Response vs FILTER_BW Settings (PGA Gain = 30 dB) Figure 5-35 Antialias Filter Response for Equalizer Modes (PGA Gain = 0 dB)

Figure 5-35 Antialias Filter Response for Equalizer Modes (PGA Gain = 0 dB)

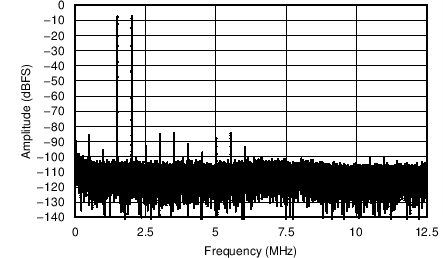

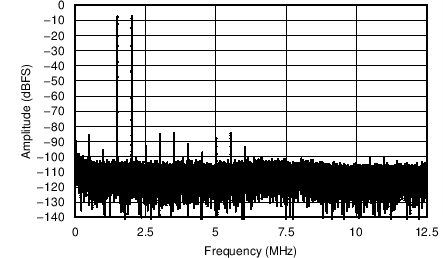

| SNR = 69.2 dBFS | SFDR = 69.8 dBc | THD = 69.7 dBc |

| | |

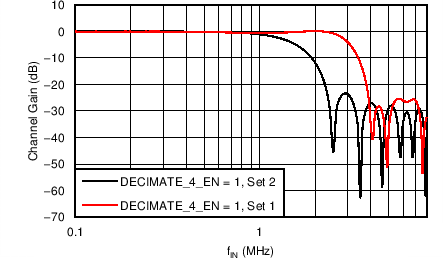

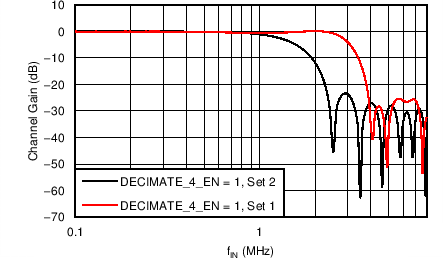

Figure 5-39 Decimate-by-4 Filter Response (Sampling Frequency = 12.5 MHz)

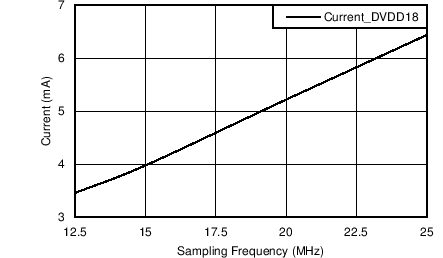

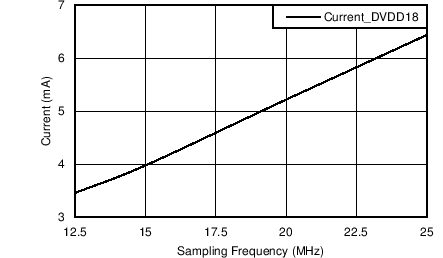

Figure 5-39 Decimate-by-4 Filter Response (Sampling Frequency = 12.5 MHz) Figure 5-41 DVDD18 Supply Current vs Sampling Frequency

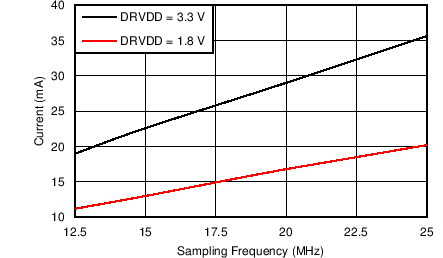

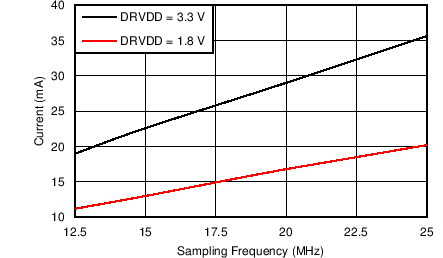

Figure 5-41 DVDD18 Supply Current vs Sampling Frequency Figure 5-43 DRVDD Supply Current vs Sampling Frequency (15-pF Load with Toggle Test Mode)

Figure 5-43 DRVDD Supply Current vs Sampling Frequency (15-pF Load with Toggle Test Mode)

| SNR = 53.3 dBFS | SFDR = 63.7 dBc | THD = 63.6 dBc |

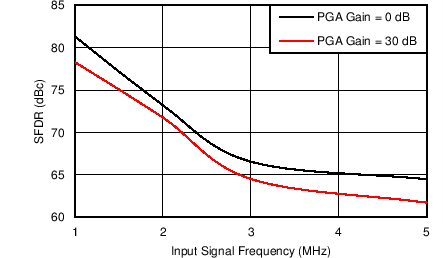

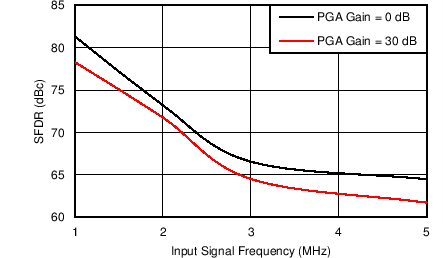

Figure 5-8 Spurious-Free Dynamic Range vs Input Signal Frequency

Figure 5-8 Spurious-Free Dynamic Range vs Input Signal Frequency Figure 5-10 Signal-To-Noise Ratio vs Input Signal Frequency (PGA Gain = 30 dB)

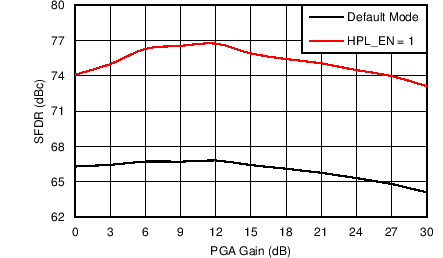

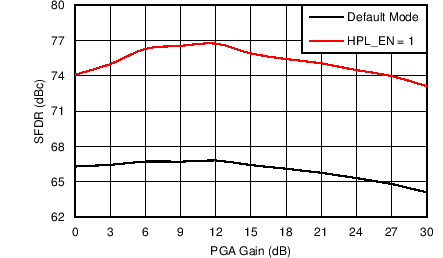

Figure 5-10 Signal-To-Noise Ratio vs Input Signal Frequency (PGA Gain = 30 dB) Figure 5-12 Spurious-Free Dynamic Range vs PGA Gain

Figure 5-12 Spurious-Free Dynamic Range vs PGA Gain Figure 5-14 Signal-to-Noise Ratio, Spurious-Free Dynamic Range vs Input Signal Amplitude (PGA Gain = 30 dB)

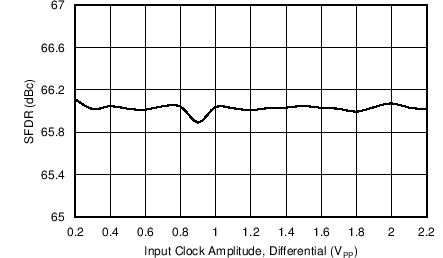

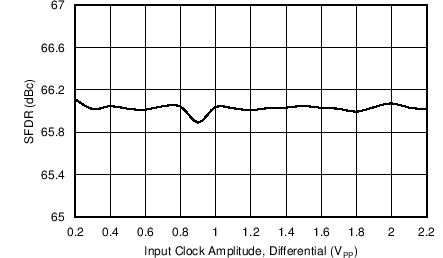

Figure 5-14 Signal-to-Noise Ratio, Spurious-Free Dynamic Range vs Input Signal Amplitude (PGA Gain = 30 dB) Figure 5-16 Spurious-Free Dynamic Range vs Input Clock Amplitude (PGA Gain = 0 dB)

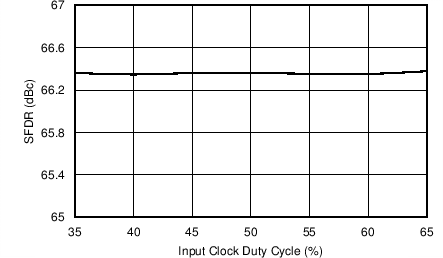

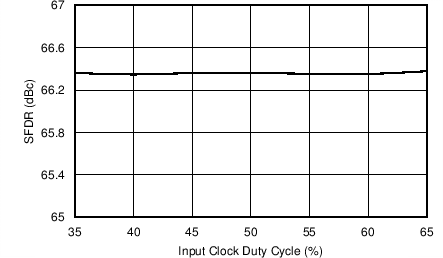

Figure 5-16 Spurious-Free Dynamic Range vs Input Clock Amplitude (PGA Gain = 0 dB) Figure 5-18 Spurious-Free Dynamic Range vs Input Clock Amplitude (PGA Gain = 0 dB)

Figure 5-18 Spurious-Free Dynamic Range vs Input Clock Amplitude (PGA Gain = 0 dB) Figure 5-20 Signal-to-Noise Ratio vs Sampling Frequency (PGA Gain = 30 dB)

Figure 5-20 Signal-to-Noise Ratio vs Sampling Frequency (PGA Gain = 30 dB) Figure 5-22 Spurious-Free Dynamic Range vs Sampling Frequency (PGA Gain = 30 dB)

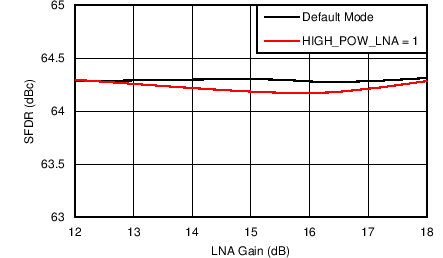

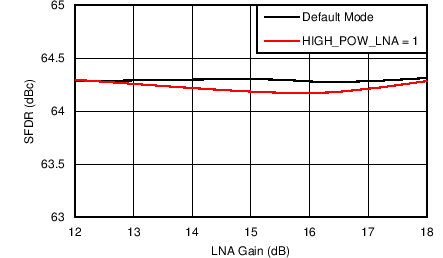

Figure 5-22 Spurious-Free Dynamic Range vs Sampling Frequency (PGA Gain = 30 dB) Figure 5-24 Spurious-Free Dynamic Range vs LNA Gain (PGA Gain = 30 dB)

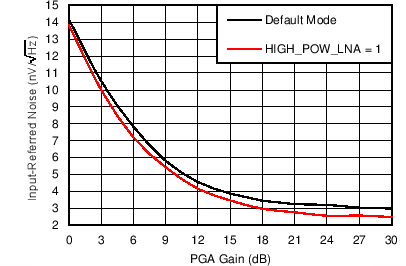

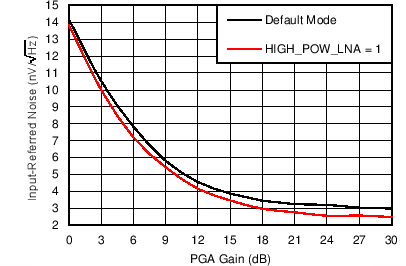

Figure 5-24 Spurious-Free Dynamic Range vs LNA Gain (PGA Gain = 30 dB) Figure 5-26 Input-Referred Noise vs PGA Gain

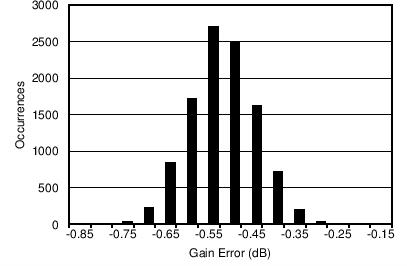

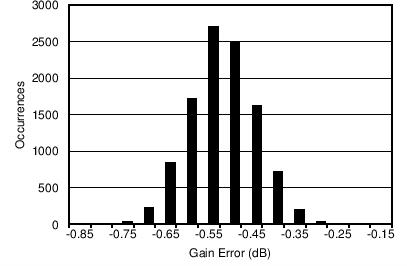

Figure 5-26 Input-Referred Noise vs PGA Gain Figure 5-28 Gain Error Histogram for PGA Gain = 30 dB

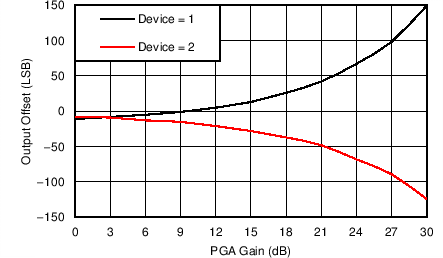

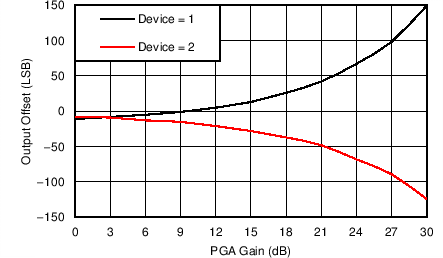

Figure 5-28 Gain Error Histogram for PGA Gain = 30 dB Figure 5-30 Channel Offset vs PGA Gain for Two Typical Devices

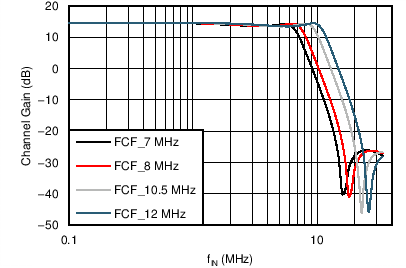

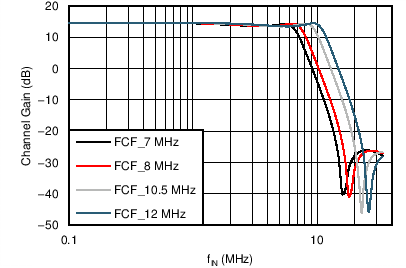

Figure 5-30 Channel Offset vs PGA Gain for Two Typical Devices Figure 5-32 Antialias Filter Response vs FILTER_BW Settings (PGA Gain = 0 dB)

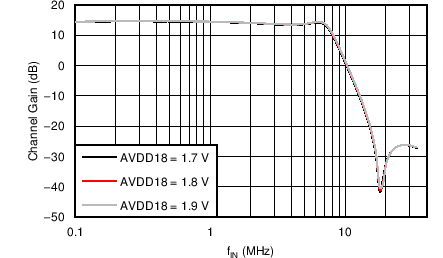

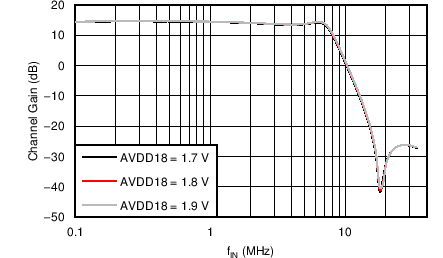

Figure 5-32 Antialias Filter Response vs FILTER_BW Settings (PGA Gain = 0 dB) Figure 5-34 Antialias Filter Response vs AVDD18 (PGA Gain = 0 dB, FILTER_BW = 8 MHz)

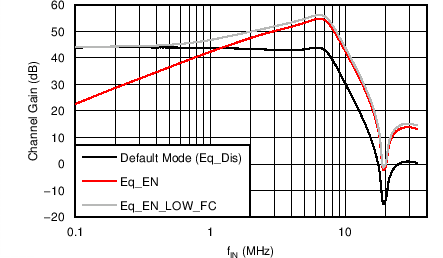

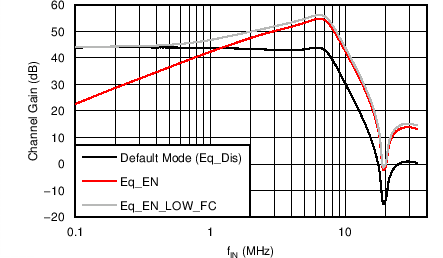

Figure 5-34 Antialias Filter Response vs AVDD18 (PGA Gain = 0 dB, FILTER_BW = 8 MHz) Figure 5-36 Antialias Filter Response for Equalizer Modes (PGA Gain = 30 dB)

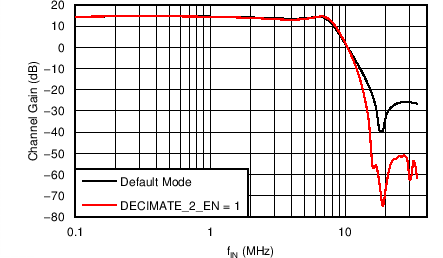

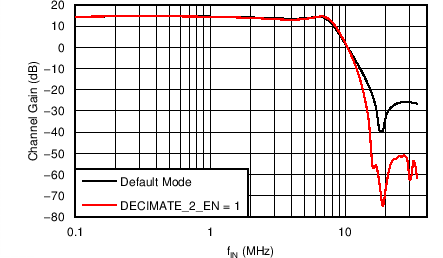

Figure 5-36 Antialias Filter Response for Equalizer Modes (PGA Gain = 30 dB) Figure 5-38 Decimate-by-2 Filter Response (Sampling Frequency = 50 MHz)

Figure 5-38 Decimate-by-2 Filter Response (Sampling Frequency = 50 MHz) Figure 5-40 AVDD18 Supply Current vs Sampling Frequency

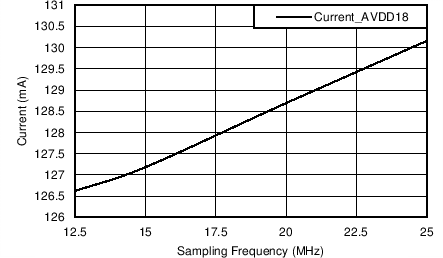

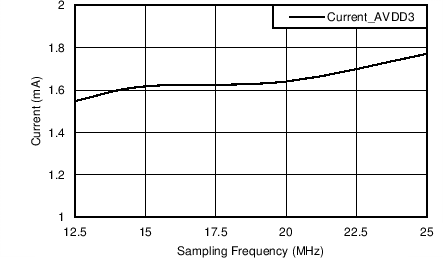

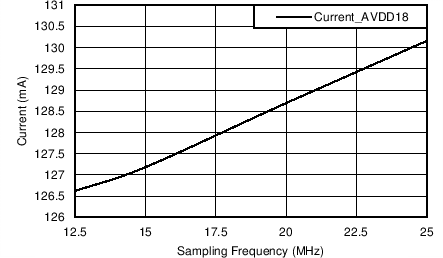

Figure 5-40 AVDD18 Supply Current vs Sampling Frequency Figure 5-42 AVDD3 Supply Current vs Sampling Frequency

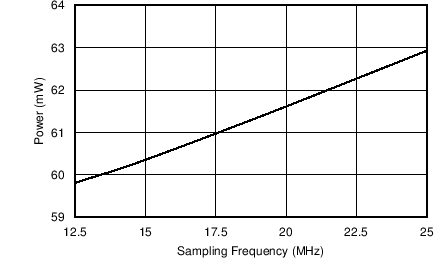

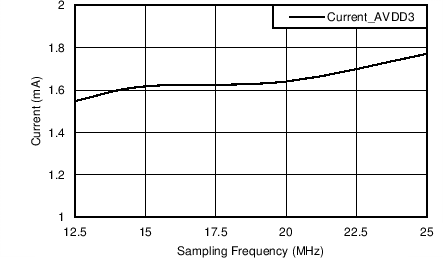

Figure 5-42 AVDD3 Supply Current vs Sampling Frequency Figure 5-44 AFE Core Power, Channel Excluding DRVDD

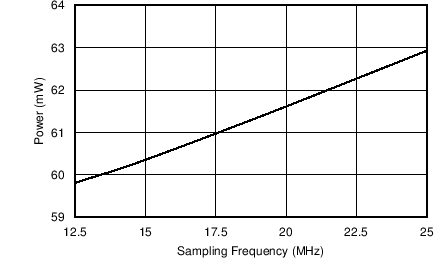

Figure 5-44 AFE Core Power, Channel Excluding DRVDD