SLUSAK9B September 2011 – April 2015

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Adapter Detect and ACOK Output

- 9.3.2 Adapter Overvoltage (ACOVP)

- 9.3.3 System Power Selection

- 9.3.4 Automatic Internal Soft-Start Charger Current

- 9.3.5 Converter Operation

- 9.3.6 Input Overcurrent Protection (ACOC)

- 9.3.7 Charge Overcurrent Protection (CHGOCP)

- 9.3.8 Battery Overvoltage Protection (BATOVP)

- 9.3.9 Battery Shorted to Ground (BATLOWV)

- 9.3.10 Thermal Shutdown Protection (TSHUT)

- 9.3.11 Inductor Short, MOSFET Short Protection

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6 Register Maps

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Design Requirements

- 10.2.2

Detailed Design Procedure

- 10.2.2.1 Negative Output Voltage Protection

- 10.2.2.2 Reverse Input Voltage Protection

- 10.2.2.3 Reduce Battery Quiescent Current

- 10.2.2.4 Inductor Selection

- 10.2.2.5 Input Capacitor

- 10.2.2.6 Output Capacitor

- 10.2.2.7 Power MOSFETs Selection

- 10.2.2.8 Input Filter Design

- 10.2.2.9 bq24735 Design Guideline

- 10.2.3 Application Curves

- 10.3 System Examples

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGR|20

Thermal pad, mechanical data (Package|Pins)

- RGR|20

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| Voltage | SRN, SRP, ACN, ACP, CMSRC, VCC | 0 | 24 | V | |

| PHASE | –2 | 24 | |||

| ACDET, SDA, SCL, LODRV, REGN, IOUT, ILIM, ACOK | 0 | 6.5 | |||

| BTST, HIDRV, ACDRV, BATDRV | 0 | 30 | |||

| Maximum difference voltage | SRP–SRN, ACP–ACN | –0.2 | 0.2 | V | |

| Junction temperature, TJ | 0 | 125 | °C | ||

7.4 Thermal Information

| THERMAL METRIC(1) | bq24735 | UNIT | |

|---|---|---|---|

| RGR [VQFN] | |||

| 20 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 46.8 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 56.9 | °C/W |

| RθJB | Junction-to-board thermal resistance | 46.6 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.6 | °C/W |

| ψJB | Junction-to-board characterization parameter | 15.3 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 4.4 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics

4.5 V ≤ VVCC ≤ 24 V, 0°C ≤ TJ ≤ 125°C, typical values are at TA = 25°C, with respect to GND (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| OPERATING CONDITIONS | ||||||

| VVCC_OP | VCC Input voltage operating range | 4.5 | 24 | V | ||

| CHARGE VOLTAGE REGULATION | ||||||

| VBAT_REG_RNG | Battery voltage range | 1.024 | 19.2 | V | ||

| VBAT_REG_ACC | Charge voltage regulation accuracy | ChargeVoltage() = 0x41A0H | 16.716 | 16.8 | 16.884 | V |

| –0.5% | 0.5% | |||||

| ChargeVoltage() = 0x3130H | 12.529 | 12.592 | 12.655 | V | ||

| –0.5% | 0.5% | |||||

| ChargeVoltage() = 0x20D0H | 8.35 | 8.4 | 8.45 | V | ||

| –0.6% | 0.6% | |||||

| ChargeVoltage() = 0x1060H | 4.163 | 4.192 | 4.221 | V | ||

| –0.7% | 0.7% | |||||

| CHARGE CURRENT REGULATION | ||||||

| VIREG_CHG_RNG | Charge current regulation differential voltage range | VIREG_CHG = VSRP - VSRN | 0 | 81.28 | mV | |

| ICHRG_REG_ACC | Charge current regulation accuracy 10-mΩ current-sensing resistor | ChargeCurrent() = 0x1000H | 3973 | 4096 | 4219 | mA |

| –3% | 3% | |||||

| ChargeCurrent() = 0x0800H | 1946 | 2048 | 2150 | mA | ||

| –5% | 5% | |||||

| ChargeCurrent() = 0x0200H | 410 | 512 | 614 | mA | ||

| –20% | 20% | |||||

| ChargeCurrent() = 0x0100H | 172 | 256 | 340 | mA | ||

| –33% | 33% | |||||

| ChargeCurrent() = 0x0080H | 64 | 128 | 192 | mA | ||

| –50% | 50% | |||||

| INPUT CURRENT REGULATION | ||||||

| VIREG_DPM_RNG | Input current regulation differential voltage range | VIREG_DPM = VACP – VACN | 0 | 80.64 | mV | |

| IDPM_REG_ACC | Input current regulation accuracy 10-mΩ current-sensing resistor | InputCurrent() = 0x1000H | 3973 | 4096 | 4219 | mA |

| –3% | 3% | |||||

| InputCurrent() = 0x0800H | 1946 | 2048 | 2150 | mA | ||

| –5% | 5% | |||||

| InputCurrent() = 0x0400H | 870 | 1024 | 1178 | mA | ||

| –15% | 15% | |||||

| InputCurrent() = 0x0200H | 384 | 512 | 640 | mA | ||

| –25% | 25% | |||||

| INPUT CURRENT OR CHARGE CURRENT-SENSE AMPLIFIER | ||||||

| VACP/N_OP | Input common-mode range | Voltage on ACP/ACN | 4.5 | 24 | V | |

| VSRP/N_OP | Output common-mode range | Voltage on SRP/SRN | 0 | 19.2 | V | |

| VIOUT | IOUT output voltage range | 0 | 3.3 | V | ||

| IIOUT | IOUT output current | 0 | 1 | mA | ||

| AIOUT | Current-sense amplifier gain | V(ICOUT)/V(SRP-SRN) or V(ACP-ACN) | 20 | V/V | ||

| VIOUT_ACC | Current-sense output accuracy | V(SRP-SRN) or V(ACP-ACN) = 40.96 mV | –2% | 2% | ||

| V(SRP-SRN) or V(ACP-ACN) = 20.48 mV | –4% | 4% | ||||

| V(SRP-SRN) or V(ACP-ACN) = 10.24 mV | –15% | 15% | ||||

| V(SRP-SRN) or V(ACP-ACN) = 5.12 mV | –20% | 20% | ||||

| V(SRP-SRN) or V(ACP-ACN) = 2.56 mV | –33% | 33% | ||||

| V(SRP-SRN) or V(ACP-ACN) = 1.28 mV | –50% | 50% | ||||

| CIOUT_MAX | Maximum output load capacitance | For stability with 0- to 1-mA load | 100 | pF | ||

| REGN REGULATOR | ||||||

| VREGN_REG | REGN regulator voltage | VVCC > 6.5 V, VACDET > 0.6 V (0-45 mA load) | 5.5 | 6 | 6.5 | V |

| IREGN_LIM | REGN current limit | VREGN = 0 V, VVCC > UVLO charge enabled and not in TSHUT | 50 | 75 | mA | |

| VREGN = 0 V, VVCC > UVLO charge disabled or in TSHUT | 7 | 14 | mA | |||

| CREGN | REGN output capacitor required for stability | ILOAD = 100 µA to 50 mA | 1 | µF | ||

| INPUT UNDERVOLTAGE LOCKOUT COMPARATOR (UVLO) | ||||||

| UVLO | Undervoltage rising threshold | VVCC rising | 3.5 | 3.75 | 4 | V |

| Undervoltage hysteresis, falling | VVCC falling | 340 | mV | |||

| FAST DPM COMPARATOR (FAST_DPM) | ||||||

| VFAST_DPM | Fast DPM comparator stop charging rising threshold with respect to input current limit, voltage across input sense resistor rising edge | 103% | 107% | 111% | ||

| QUIESCENT CURRENT | ||||||

| IBAT_BATFET_OFF | Battery BATFET OFF STATE Current, BATFET off, ISRP + ISRN + IPHASE + IACP + IACN |

VVBAT = 16.8 V, VCC disconnect from battery, BATFET charge pump off, BATFET turns off, TJ = 0 to 85°C | 5 | µA | ||

| IBAT_BATFET_ON | Battery BATFET ON STATE Current, BATFET on, ISRP + ISRN + IPHASE + IVCC + IACP + IACN |

VVBAT = 16.8 V, VCC connect from battery, BATFET charge pump on, BATFET turns on, TJ = 0 to 85°C | 25 | µA | ||

| ISTANDBY | Standby quiescent current, IVCC + IACP + IACN | VVCC > UVLO, VACDET > 0.6 V, charge disabled, TJ = 0 to 85°C |

0.65 | 0.8 | mA | |

| IAC_NOSW | Adapter bias current during charge, IVCC + IACP + IACN |

VVCC > UVLO, 2.4 V < VACDET < 3.15 V, charge enabled, no switching, TJ = 0 to 85°C |

1.5 | 3 | mA | |

| IAC_SW | Adapter bias current during charge, IVCC + IACP + IACN |

VVCC > UVLO, 2.4 V < VACDET < 3.15 V, charge enabled, switching, MOSFET Sis412DN |

10 | mA | ||

| ACOK COMPARATOR | ||||||

| VACOK_RISE | ACOK rising threshold | VVCC > UVLO, VACDET rising | 2.376 | 2.4 | 2.424 | V |

| VACOK_FALL_HYS | ACOK falling hysteresis | VVCC> UVLO, VACDET falling | 35 | 55 | 75 | mV |

| VWAKEUP_RISE | WAKEUP detect rising threshold | VVCC> UVLO, VACDET rising | 0.57 | 0.8 | V | |

| VWAKEUP_FALL | WAKEUP detect falling threshold | VVCC> UVLO, VACDET falling | 0.3 | 0.51 | V | |

| VCC to SRN COMPARATOR (VCC_SRN) | ||||||

| VVCC-SRN_FALL | VCC-SRN falling threshold | VVCC falling toward VSRN | 70 | 125 | 200 | mV |

| VVCC-SRN _RHYS | VCC-SRN rising hysteresis | VVCC rising above VSRN | 100 | 150 | 200 | mV |

| ACN to SRN COMPARATOR (ACN_SRN) | ||||||

| VACN-SRN_FALL | ACN to BAT falling threshold | VACN falling toward VSRN | 120 | 200 | 280 | mV |

| VACN-SRN_RHYS | ACN to BAT rising hysteresis | VACN rising above VSRN | 40 | 80 | 120 | mV |

| HIGH-SIDE IFAULT COMPARATOR (IFAULT_HI)(1) | ||||||

| VIFAULT_HI_RISE | ACP to PHASE rising threshold | ChargeOption() bit [8] = 1 (Default) | 450 | 750 | 1200 | mV |

| ChargeOption() bit [8] = 0 Disable function | ||||||

| LOW-SIDE IFAULT COMPARATOR (IFAULT_LOW)(1) | ||||||

| VIFAULT_LOW_RISE | PHASE to GND rising threshold | ChargeOption() bit [7] = 0 (Default) | 70 | 135 | 220 | mV |

| ChargeOption() bit [7] = 1 | 140 | 230 | 340 | |||

| INPUT OVERVOLTAGE COMPARATOR (ACOV) | ||||||

| VACOV | ACDET overvoltage rising threshold | VACDET rising | 3.05 | 3.15 | 3.25 | V |

| VACOV_HYS | ACDET overvoltage falling hysteresis | VACDET falling | 50 | 75 | 100 | mV |

| INPUT OVERCURRENT COMPARATOR (ACOC)(1) | ||||||

| VACOC | Adapter overcurrent rising threshold with respect to input current limit, voltage across input sense resistor rising edge | ChargeOption() bit [1] = 1 (Default) | 300% | 333% | 366% | |

| ChargeOption() bit [1] = 0 Disable function | ||||||

| VACOC_min | Min ACOC threshold clamp voltage | ChargeOption() bit [1] = 1 (333%), InputCurrent () = 0x0400H (10.24 mV) |

40 | 45 | 50 | mV |

| VACOC_max | Max ACOC threshold clamp voltage | ChargeOption() bit [1] = 1 (333%), InputCurrent () = 0x1F80H (80.64 mV) |

135 | 150 | 165 | mV |

| BAT OVERVOLTAGE COMPARATOR (BAT_OVP) | ||||||

| VOVP_RISE | Overvoltage rising threshold as percentage of VBAT_REG | VSRN rising | 103% | 104% | 106% | |

| VOVP_FALL | Overvoltage falling threshold as percentage of VBAT_REG | VSRN falling | 102% | |||

| CHARGE OVERCURRENT COMPARATOR (CHG_OCP) | ||||||

| VOCP_RISE | Charge overcurrent rising threshold, measure voltage drop across current-sensing resistor | ChargeCurrent() = 0x0xxxH | 54 | 60 | 66 | mV |

| ChargeCurrent() = 0x1000H – 0x17C0H | 80 | 90 | 100 | |||

| ChargeCurrent() = 0x1800 H– 0x1FC0H | 110 | 120 | 130 | |||

| CHARGE UNDERCURRENT COMPARATOR (CHG_UCP) | ||||||

| VUCP_FALL | Charge undercurrent falling threshold | VSRP falling toward VSRN | 1 | 5 | 9 | mV |

| LIGHT LOAD COMPARATOR (LIGHT_LOAD) | ||||||

| VLL_FALL | Light load falling threshold | Measure the voltage drop across current-sensing resistor | 1.25 | mV | ||

| VLL_RISE_HYST | Light load rising hysteresis | 1.25 | mV | |||

| BATTERY DEPLETION COMPARATOR (BAT_DEPL) [1] | ||||||

| VBATDEPL_FALL | Battery depletion falling threshold, percentage of voltage regulation limit, VSRN falling | ChargeOption() bit [12:11] = 00 | 55.53% | 59.19% | 63.5% | |

| ChargeOption() bit [12:11] = 01 | 58.68% | 62.65% | 67.5% | |||

| ChargeOption() bit [12:11] = 10 | 62.17% | 66.55% | 71.5% | |||

| ChargeOption() bit [12:11] = 11 (Default) | 66.06% | 70.97% | 77% | |||

| VBATDEPL_RHYST | Battery depletion rising hysteresis, VSRN rising | ChargeOption() bit [12:11] = 00 | 225 | 305 | 400 | mV |

| ChargeOption() bit [12:11] = 01 | 240 | 325 | 430 | |||

| ChargeOption() bit [12:11] = 10 | 255 | 345 | 450 | |||

| ChargeOption() bit [12:11] = 11 (Default) | 280 | 370 | 490 | |||

| tBATDEPL_RDEG | Battery depletion rising deglitch (specified by design) | Delay to turn off ACFET and turn on BATFET during LEARN cycle | 600 | ms | ||

| BATTERY LOWV COMPARATOR (BAT_LOWV) | ||||||

| VBATLV_FALL | Battery LOWV falling threshold | VSRN falling | 2.4 | 2.5 | 2.6 | V |

| VBATLV_RHYST | Battery LOWV rising hysteresis | VSRN rising | 200 | mV | ||

| IBATLV | Battery LOWV charge current limit | 10-mΩ current-sensing resistor | 0.5 | A | ||

| THERMAL SHUTDOWN COMPARATOR (TSHUT) | ||||||

| TSHUT | Thermal shutdown rising temperature | Temperature rising | 155 | °C | ||

| TSHUT_HYS | Thermal shutdown hysteresis, falling | Temperature falling | 20 | °C | ||

| ILIM COMPARATOR | ||||||

| VILIM_FALL | ILIM as CE falling threshold | VILIM falling | 60 | 75 | 90 | mV |

| VILIM_RISE | ILIM as CE rising threshold | VILIM rising | 90 | 105 | 120 | mV |

| LOGIC INPUT (SDA, SCL) | ||||||

| VIN_ LO | Input low threshold | 0.8 | V | |||

| VIN_ HI | Input high threshold | 2.1 | V | |||

| IIN_ LEAK | Input bias current | V = 7 V | –1 | 1 | μA | |

| LOGIC OUTPUT OPEN DRAIN (ACOK, SDA) | ||||||

| VOUT_ LO | Output saturation voltage | 5-mA drain current | 500 | mV | ||

| IOUT_ LEAK | Leakage current | V = 7 V | –1 | 1 | μA | |

| ANALOG INPUT (ACDET, ILIM) | ||||||

| IIN_ LEAK | Input bias current | V = 7 V | –1 | 1 | μA | |

| PWM OSCILLATOR | ||||||

| FSW | PWM switching frequency | ChargeOption() bit [9] = 0 (Default) | 600 | 750 | 900 | kHz |

| FSW+ | PWM increase frequency | ChargeOption() bit [10:9] = 11 | 665 | 885 | 1100 | kHz |

| FSW– | PWM decrease frequency | ChargeOption() bit [10:9] = 01 | 465 | 615 | 765 | kHz |

| BATFET GATE DRIVER (BATDRV) | ||||||

| IBATFET | BATDRV charge pump current limit | 40 | 60 | µA | ||

| VBATFET | Gate drive voltage on BATFET | VBATDRV – VSRN when VSRN > UVLO | 5.5 | 6.1 | 6.5 | V |

| RBATDRV_LOAD | Minimum load resistance between BATDRV and SRN | 500 | kΩ | |||

| RBATDRV_OFF | BATDRV turnoff resistance | I = 30 µA | 5 | 6.2 | 7.4 | kΩ |

| ACFET GATE DRIVER (ACDRV) | ||||||

| IACFET | ACDRV charge pump current limit | 40 | 60 | μA | ||

| VACFET | Gate drive voltage on ACFET | VACDRV – VCMSRC when VVCC > UVLO | 5.5 | 6.1 | 6.5 | V |

| RACDRV_LOAD | Minimum load resistance between ACDRV and CMSRC | 500 | kΩ | |||

| RACDRV_OFF | ACDRV turnoff resistance | I = 30 µA | 5 | 6.2 | 7.4 | kΩ |

| VACFET_LOW | ACDRV turnoff when Vgs voltage is low (specified by design) | 5.9 | V | |||

| PWM HIGH-SIDE DRIVER (HIDRV) | ||||||

| RDS_HI_ON | High-side driver turnon resistance | VBTST – VPH = 5.5 V, I = 10 mA | 6 | 10 | Ω | |

| RDS_HI_OFF | High-side driver turnoff resistance | VBTST – VPH = 5.5 V, I = 10 mA | 0.65 | 1.3 | Ω | |

| VBTST_REFRESH | Bootstrap refresh comparator threshold voltage | VBTST – VPH when low-side refresh pulse is requested | 3.85 | 4.3 | 4.7 | V |

| PWM LOW-SIDE DRIVER (LODRV) | ||||||

| RDS_LO_ON | Low-side driver turnon resistance | VREGN = 6 V, I = 10 mA | 7.5 | 12 | Ω | |

| RDS_LO_OFF | Low-side driver turnoff resistance | VREGN = 6 V, I = 10 mA | 0.9 | 1.4 | Ω | |

| INTERNAL SOFT START | ||||||

| ISTEP | Soft start current step | In CCM mode 10-mΩ current-sensing resistor | 64 | mA | ||

(1) User can adjust threshold through SMBus ChargeOption() REG0x12.

7.6 Timing Requirements

| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| ACOK COMPARATOR | ||||||

| VACOK_RISE_DEG | ACOK rising deglitch (specified by design) | VVCC > UVLO, VACDET rising above 2.4 V, First time OR ChargeOption() bit [15] = 0 |

100 | 150 | 200 | ms |

| VVCC > UVLO, VACDET rising above 2.4 V, (NOT First time) AND ChargeOption() bit [15] = 1 (Default) |

0.9 | 1.3 | 1.7 | s | ||

| INPUT OVERCURRENT COMPARATOR (ACOC)(1) | ||||||

| tACOC_DEG | ACOC deglitch time (specified by design) | Voltage across input sense resistor rising to disable charge | 2.3 | 4.2 | 6.6 | ms |

| BATTERY DEPLETION COMPARATOR (BAT_DEPL) [1] | ||||||

| tBATDEPL_RDEG | Battery depletion rising deglitch (specified by design) | Delay to turn off ACFET and turn on BATFET during LEARN cycle | 600 | ms | ||

| PWM DRIVER TIMING | ||||||

| tLOW_HIGH | Driver dead time from low side to high side | 20 | ns | |||

| tHIGH_LOW | Driver dead time from high side to low side | 20 | ns | |||

| INTERNAL SOFT START | ||||||

| tSTEP | Soft start current step time | 240 | μs | |||

| SMBus TIMING CHARACTERISTICS | ||||||

| tR | SCLK/SDATA rise time | 1 | μs | |||

| tF | SCLK/SDATA fall time | 300 | ns | |||

| tW(H) | SCLK pulse width high | 4 | 50 | μs | ||

| tW(L) | SCLK Pulse Width Low | 4.7 | μs | |||

| tSU(STA) | Setup time for START condition | 4.7 | μs | |||

| tH(STA) | START condition hold time after which first clock pulse is generated | 4 | μs | |||

| tSU(DAT) | Data setup time | 250 | ns | |||

| tH(DAT) | Data hold time | 300 | ns | |||

| tSU(STOP) | Setup time for STOP condition | 4 | µs | |||

| t(BUF) | Bus free time between START and STOP condition | 4.7 | μs | |||

| FS(CL) | Clock Frequency | 10 | 100 | kHz | ||

| HOST COMMUNICATION FAILURE | ||||||

| ttimeout | SMBus bus release time-out(2) | 25 | 35 | ms | ||

| tBOOT | Deglitch for watchdog reset signal | 10 | ms | |||

| tWDI | Watchdog time-out period, ChargeOption() bit [14:13] = 01(3) | 35 | 44 | 53 | s | |

| Watchdog time-out period, ChargeOption() bit [14:13] = 10(3) | 70 | 88 | 105 | s | ||

| Watchdog time-out period, ChargeOption() bit [14:13] = 11(3) (Default) | 140 | 175 | 210 | s | ||

(1) User can adjust threshold through SMBus ChargeOption() REG0x12.

(2) Devices participating in a transfer will time out when any clock low exceeds the 25-ms minimum time-out period. Devices that have detected a time-out condition must reset the communication no later than the 35-ms maximum time-out period. Both a master and a slave must adhere to the maximum value specified, as it incorporates the cumulative stretch limit for both a master (10 ms) and a slave (25 ms).

(3) User can adjust threshold through SMBus ChargeOption() REG0x12.

7.7 Typical Characteristics

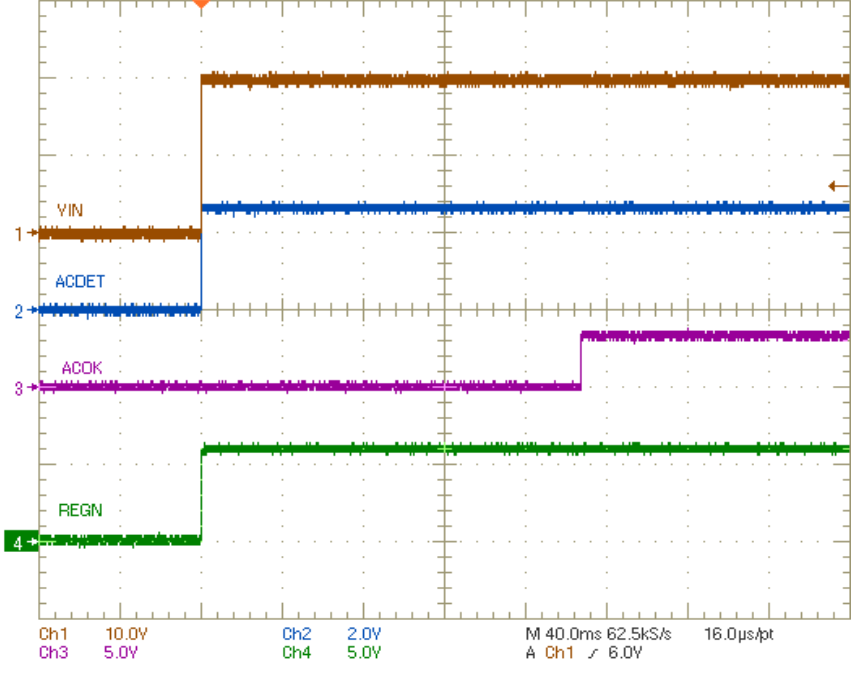

| CH1: VCC, 10 V/div, CH2: ACDET, 2 V/div, CH3: ACOK, 5 V/div, | ||

| CH4: REGN, 5 V/div, 40 ms/div | ||

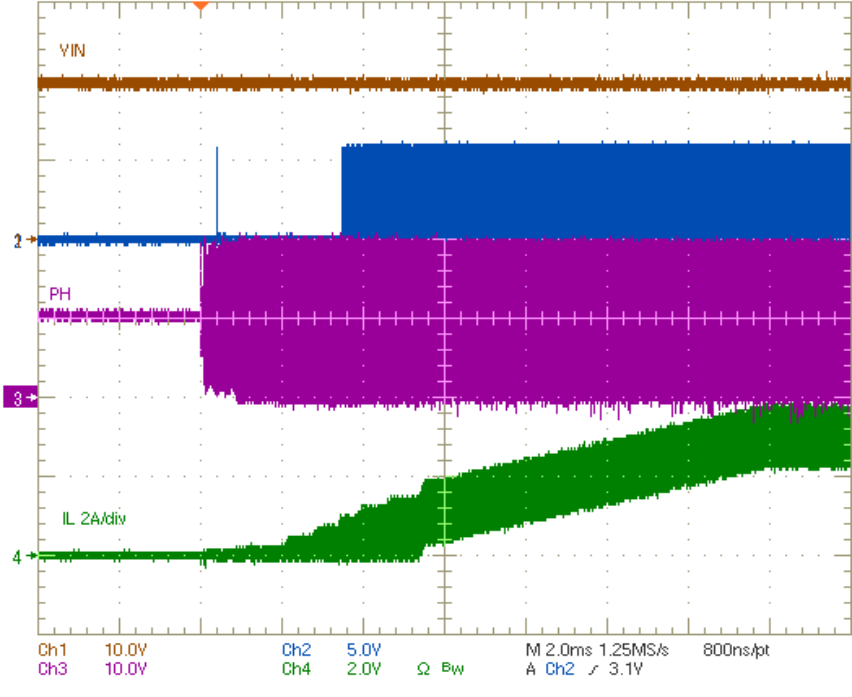

| CH1: Vin, 10 V/div, | CH2: LODRV, 5 V/div, | |

| CH3: PHASE, 10 V/div, | ||

| CH4: inductor current, 2 A/div, 2 ms/div | ||

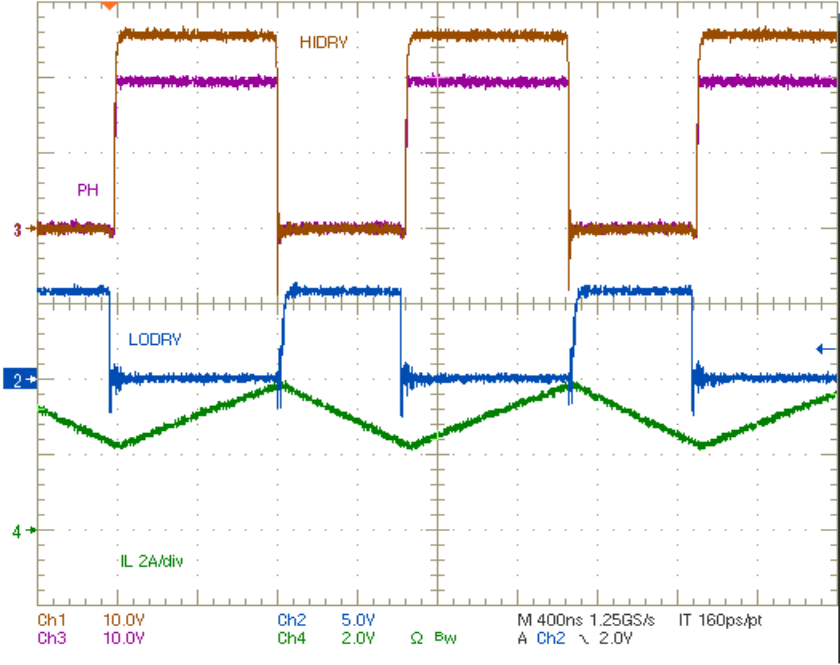

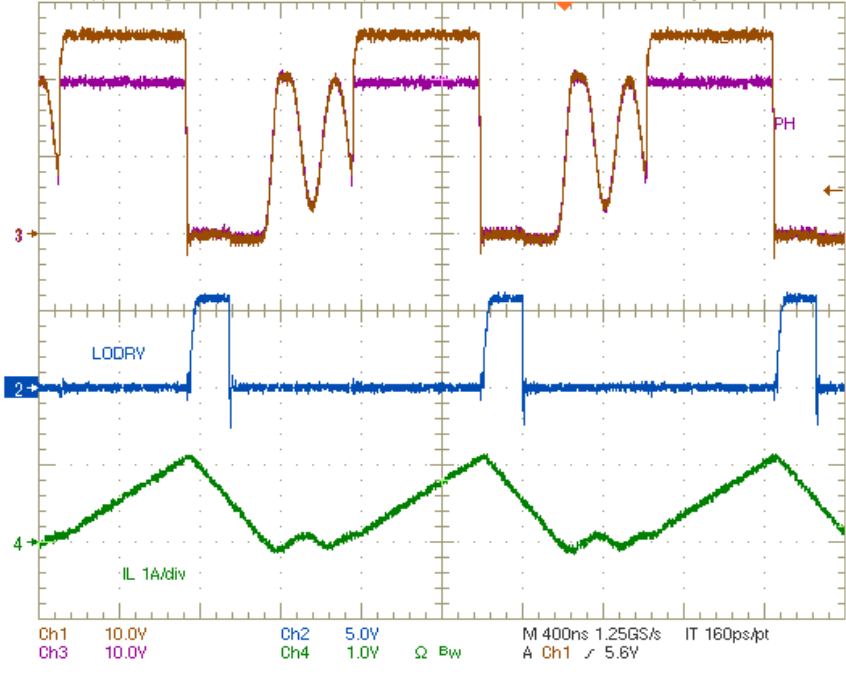

| CH1: PHASE, 10 V/div, | CH2: LODRV, 5 V/div, | |

| CH3: HIDRV, 10 V/div | ||

| CH4: inductor current, 2 A/div, 400 ns/div | ||

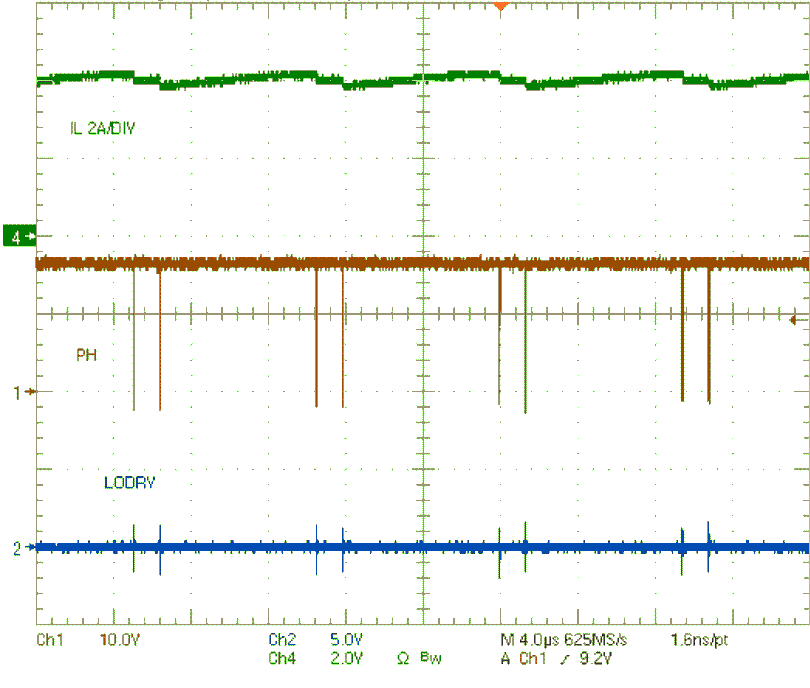

| CH1: PHASE, 10 V/div, | CH2: LODRV, 5 V/div, | |

| CH4: inductor current, 2 A/div, 4 µs/div | ||

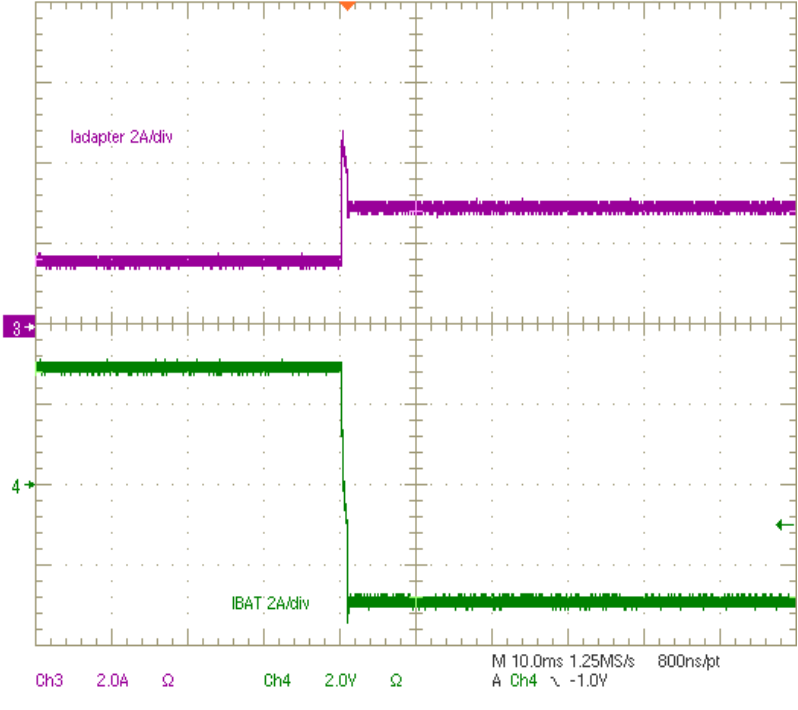

| CH3: adapter current, 2 A/div, | ||

| CH4: battery current, 2 A/div, 10 ms/div |

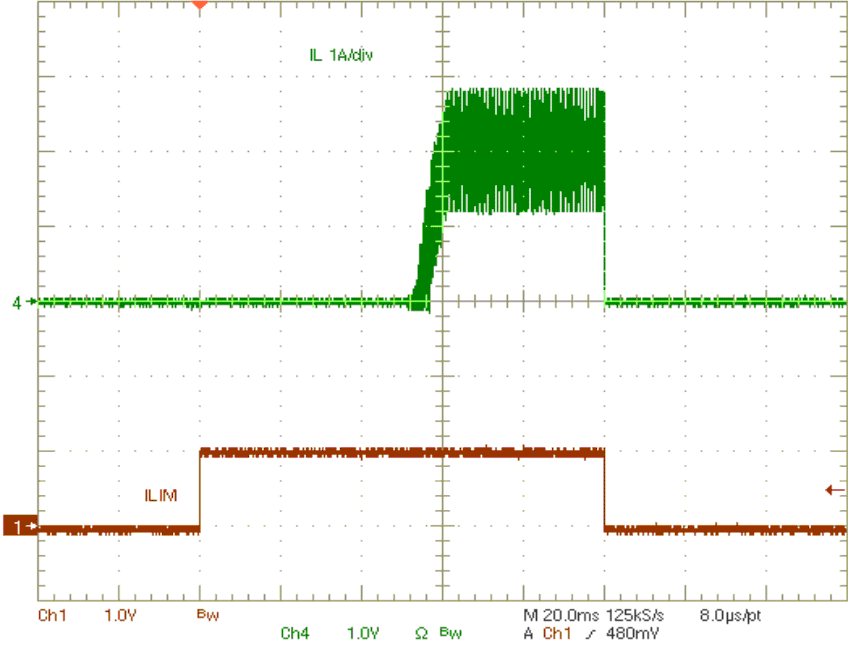

| CH1: ILIM, 1 V/div, | CH4: inductor current, 1 A/div, 20 ms/div | |

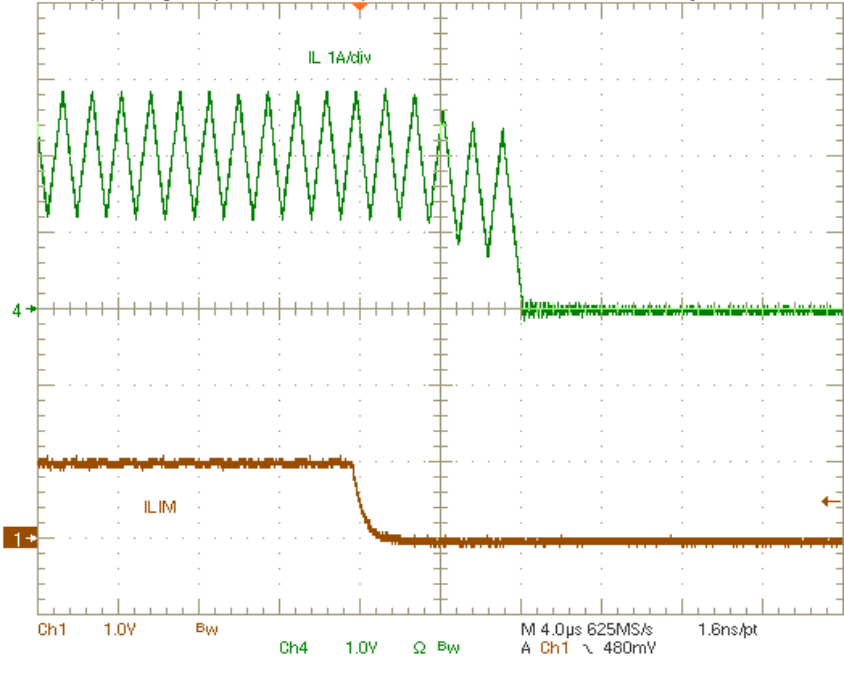

| CH1: ILIM, 1 V/div, | CH4: inductor current, 1 A/div, 4 µs/div | |

| CH1: PHASE, 10 V/div, | CH2: LODRV, 5 V/div, | |

| CH3: HIDRV, 10 V/div, | ||

| CH4: inductor current, 1 A/div, 400 ns/div | ||

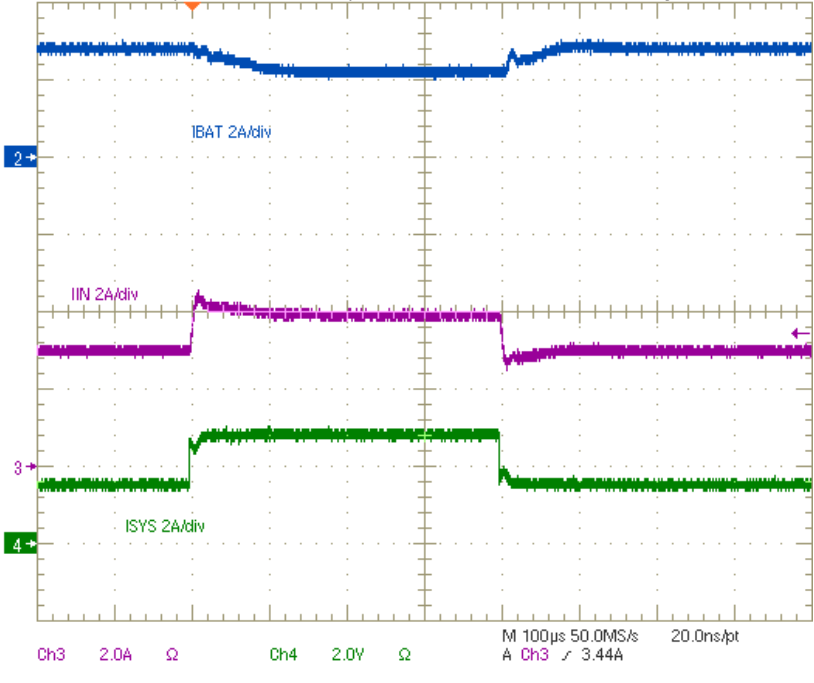

| CH2: battery current, 2 A/div, | CH3: adapter current, 2 A/div, | |

| CH4: system load current, 2 A/div, 100 µs/div | ||

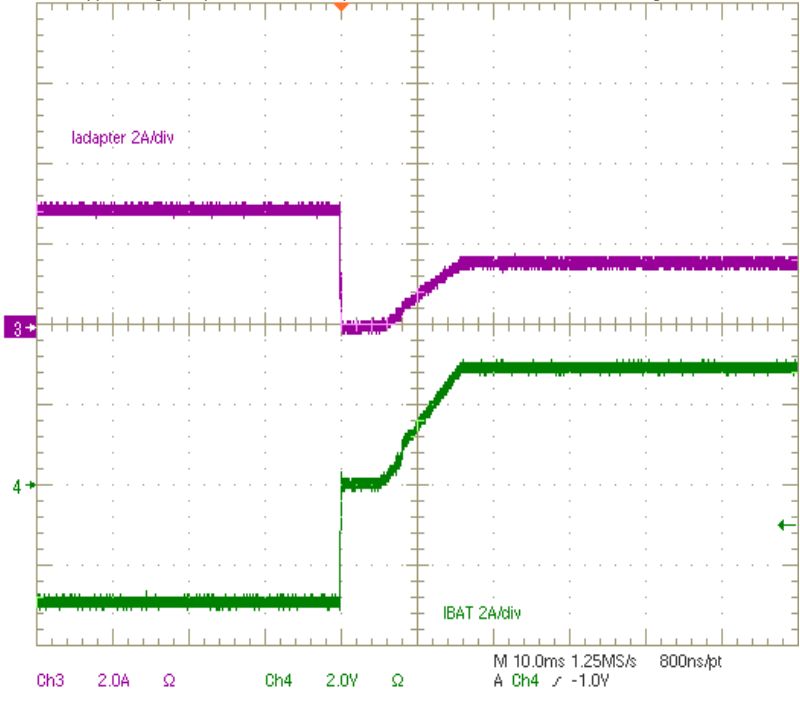

| CH3: adapter current, 2 A/div, | ||

| CH4: battery current, 2 A/div, 10 ms/div |