SCHS051J November 1998 – August 2024 CD4066B

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- J|14

Thermal pad, mechanical data (Package|Pins)

Orderable Information

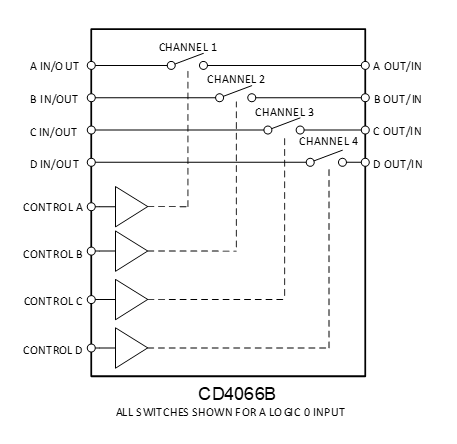

7.2 Functional Block Diagram

A. All control inputs are protected by the CMOS protection network.

B. All p substrates are connected to VDD.

C. Normal operation control-line biasing: switch on (logic 1), VC = VDD; switch off (logic 0), VC = VSS.

D. Signal-level range: VSS ≤ Vis ≤ VDD.

Figure 7-1 Schematic Diagram of One-of-Four Identical Switches and Associated Control Circuitry