SCLS552B December 2003 – April 2024 CD74HC4051-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- PW|16

- D|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

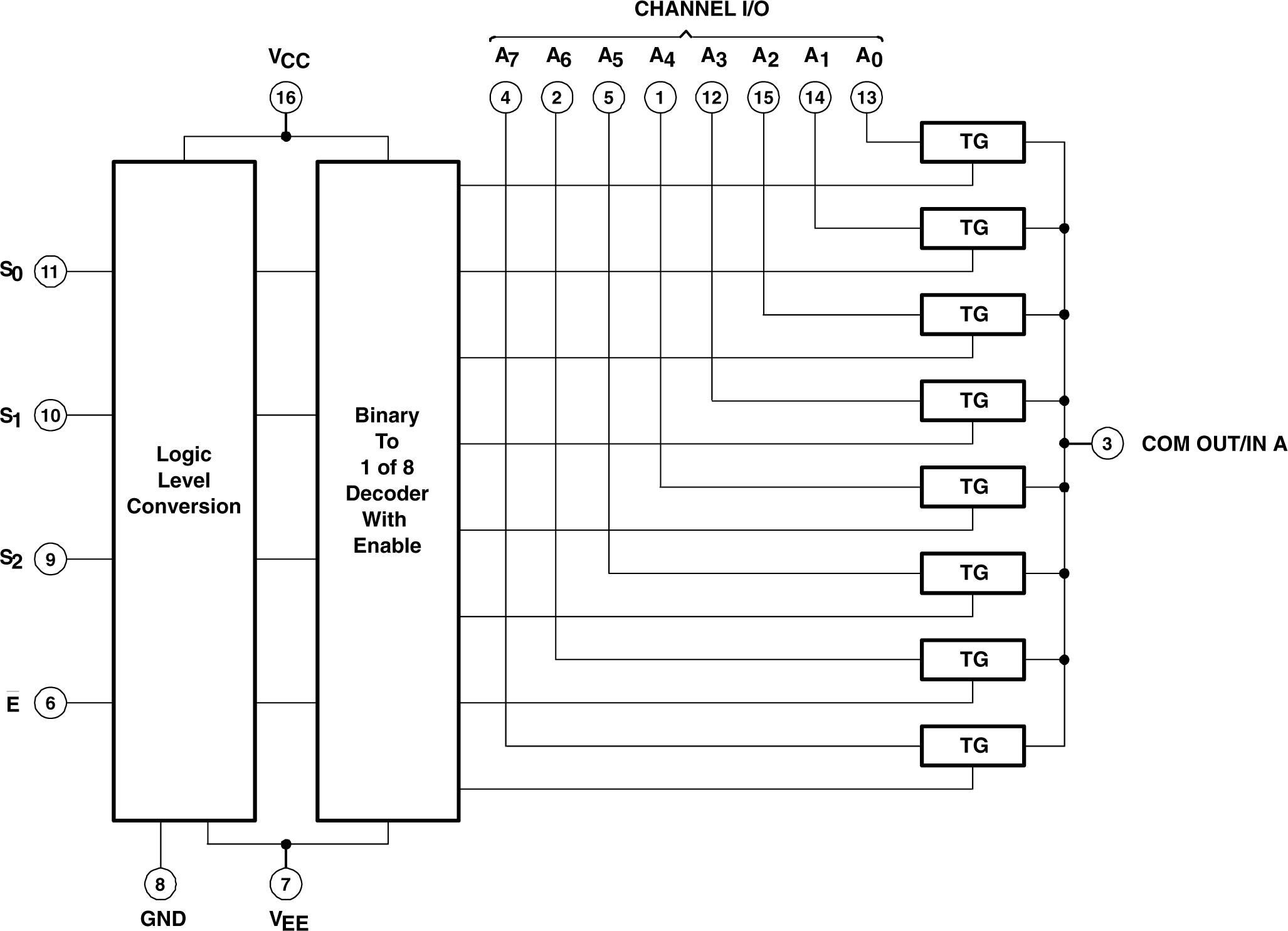

3 Description

This device is a digitally controlled analog switch that utilizes silicon-gate CMOS technology to achieve operating speeds similar to LSTTL, with the low power consumption of standard CMOS integrated circuits.

This analog multiplexer/demultiplexer controls analog voltages that may vary across the voltage supply range (for example, VCC to VEE). These bidirectional switches allow any analog input to be used as an output and vice versa. The switches have low ON resistance and low OFF leakages. In addition, the device has an enable control (E) that, when high, disables all switches to their OFF state.

| PART NUMBER | PACKAGE(1) | PACKAGE SIZE(2) |

|---|---|---|

| CD74HC4051-Q1 | PW (TSSOP, 16) | 5mm × 6.4mm |

| D (SOIC, 16) | 9.9mm × 3.9mm |

Logic

Diagram (Positive Logic)

Logic

Diagram (Positive Logic)