SCLS581C April 2004 – July 2024 CD74HCT4066-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|14

- PW|14

Thermal pad, mechanical data (Package|Pins)

Orderable Information

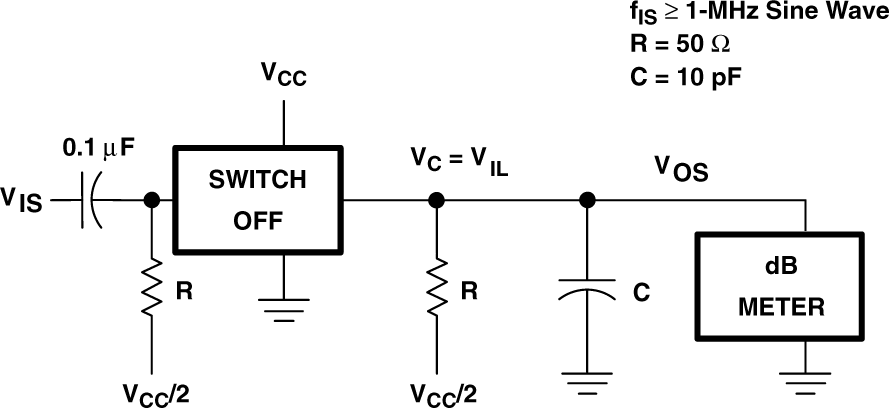

6 Parameter Measurement Information

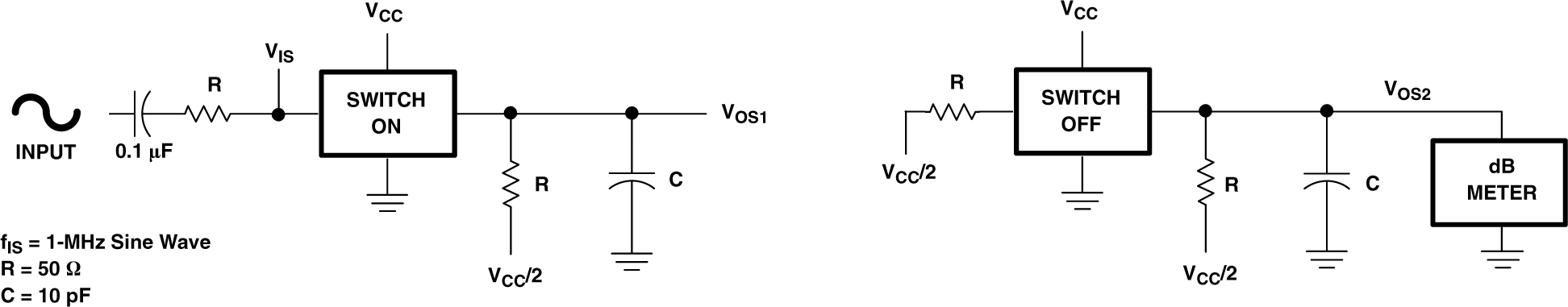

Figure 6-1 Crosstalk between Two Switches Test Circuit

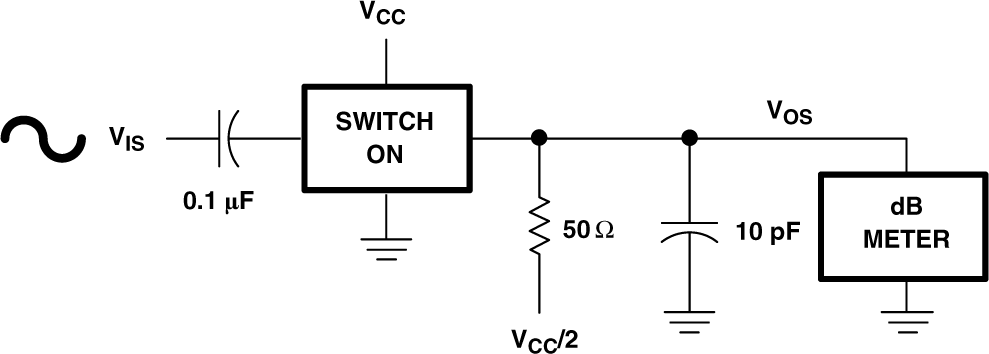

Figure 6-1 Crosstalk between Two Switches Test Circuit Figure 6-2 Frequency-Response Test Circuit

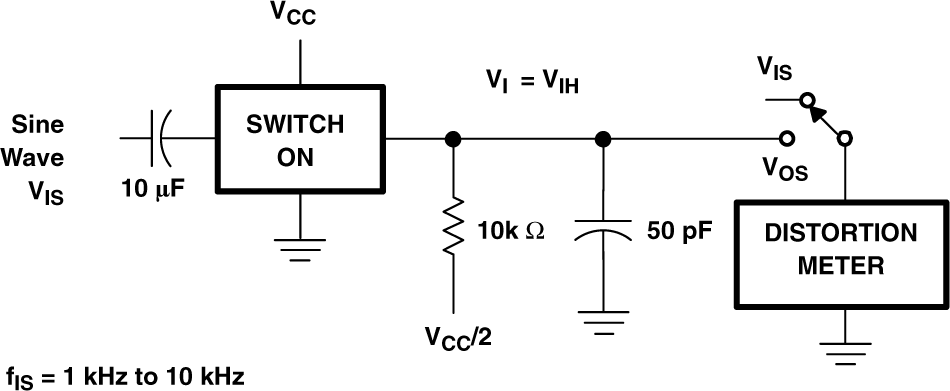

Figure 6-2 Frequency-Response Test Circuit Figure 6-3 Total Harmonic Distortion Test Circuit

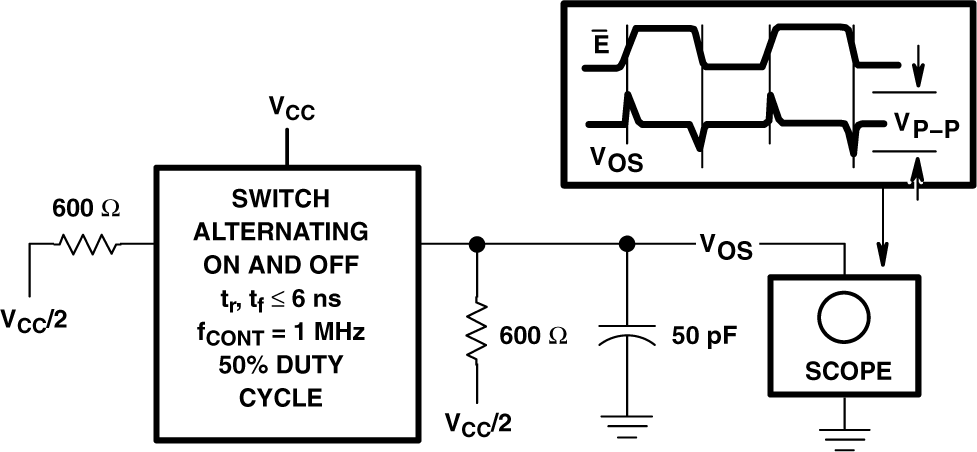

Figure 6-3 Total Harmonic Distortion Test Circuit Figure 6-4 Control-to-Switch Feedthrough Noise Test Circuit

Figure 6-4 Control-to-Switch Feedthrough Noise Test Circuit Figure 6-5 Switch off Signal Feedthrough Test Circuit

Figure 6-5 Switch off Signal Feedthrough Test Circuit

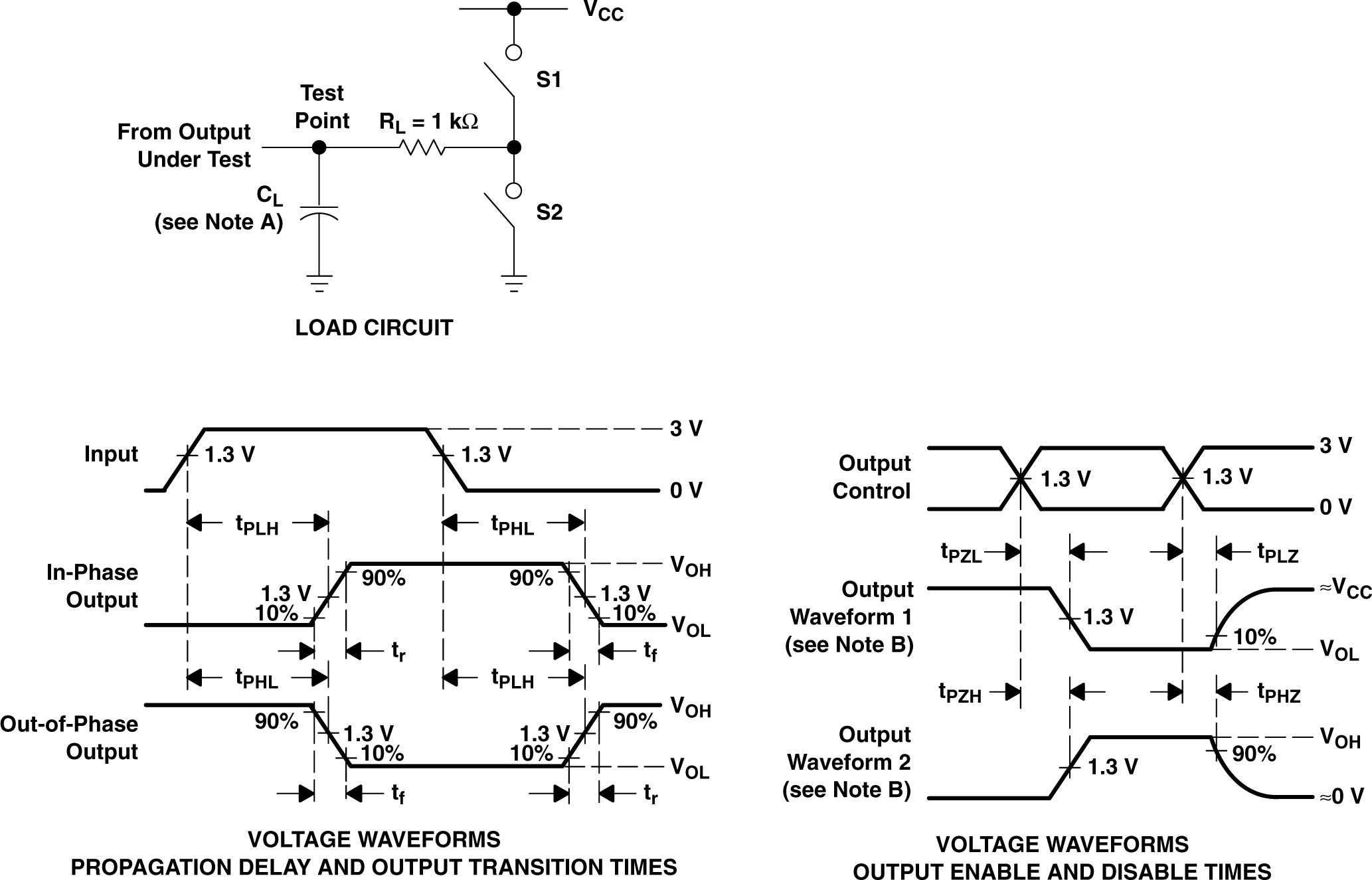

A. CL includes probe and test-fixture capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

C. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR ≤ 1MHz, ZO = 50Ω, tr = 6ns, tf = 6ns.

D. For clock inputs, fmax is measured with the input duty cycle at 50%.

E. The outputs are measured one at a time, with one input transition per measurement.

F. tPLZ and tPHZ are the same as tdis.

G. tPZL and tPZH are the same as ten.

H. tPLH and tPHL are the same as tpd.

Figure 6-6 Load Circuit and Voltage Waveforms| PARAMETER | S1 | S2 | |

|---|---|---|---|

| ten | tPZH | Open | Closed |

| tPZL | Closed | Open | |

| tdis | tPHZ | Open | Closed |

| tPLZ | Closed | Open | |

| tpd | Open | Open | |