SLLS781D February 2007 – November 2014 CDCL1810

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Functional Block Diagram

- 5 Revision History

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGZ|48

Thermal pad, mechanical data (Package|Pins)

- RGZ|48

Orderable Information

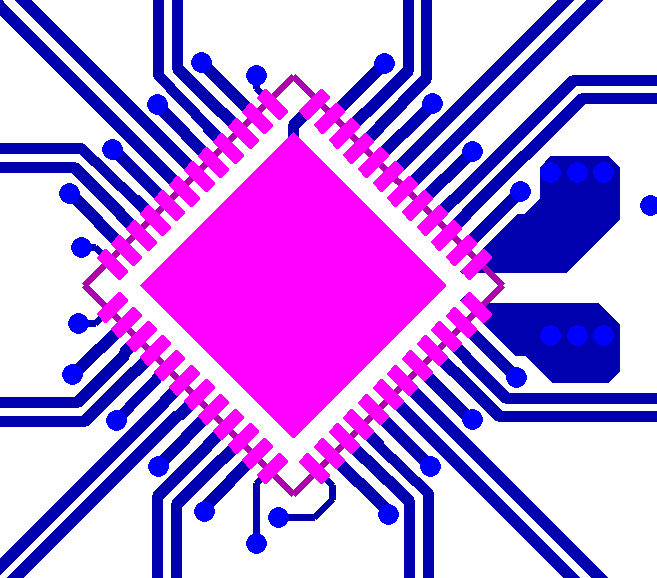

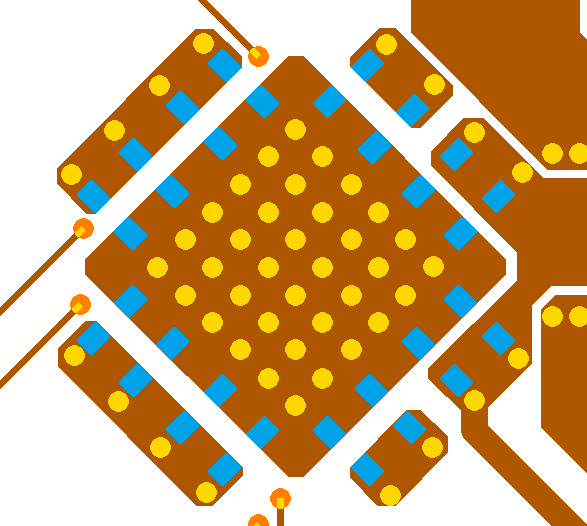

12 Layout

12.1 Layout Guidelines

- Keep the connections between the bypass capacitors and the power supply on the device as short as possible.

- Ground the other side of the capacitor using a low impedance connection to the ground plane.

- If the capacitors are mounted on the back side, 0402 components can be employed; however, soldering to the Thermal Dissipation Pad can be difficult.

- For component side mounting, use 0201 body size capacitors to facilitate signal routing.

NOTE

The device must be soldered to ground (VSS) using as many ground vias as possible. The device performance will be severely impacted if the exposed thermal pad is not grounded appropriately.

12.2 Layout Example

Figure 11. Layout Example: Signal Layer (TOP)

Figure 11. Layout Example: Signal Layer (TOP)

Figure 12. Layout Example: Bottom Layer with Decoupling Capacitors

Figure 12. Layout Example: Bottom Layer with Decoupling Capacitors