SLPS393A October 2013 – January 2015 CSD17571Q2

PRODUCTION DATA.

- 1Features

- 2Applications

- 3Description

- 4Revision History

- 5 Specifications

- 6Device and Documentation Support

- 7Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- DQK|6

Thermal pad, mechanical data (Package|Pins)

Orderable Information

5 Specifications

5.1 Electrical Characteristics

TA = 25°C| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| STATIC CHARACTERISTICS | |||||||

| BVDSS | Drain-to-Source Voltage | VGS = 0 V, ID = 250 μA | 30 | V | |||

| IDSS | Drain-to-Source Leakage Current | VGS = 0 V, VDS = 24 V | 1 | μA | |||

| IGSS | Gate-to-Source Leakage Current | VDS = 0 V, VGS = 20 V | 100 | nA | |||

| VGS(th) | Gate-to-Source Threshold Voltage | VDS = VGS, IDS = 250 μA | 1.3 | 1.6 | 2 | V | |

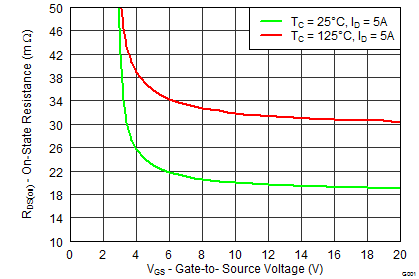

| RDS(on) | Drain-to-Source On-Resistance | VGS = 4.5 V, IDS = 5 A | 24 | 29 | mΩ | ||

| VGS = 10 V, IDS = 5 A | 20 | 24 | mΩ | ||||

| gƒs | Transconductance | VDS = 15 V, IDS = 5 A | 43 | S | |||

| DYNAMIC CHARACTERISTICS | |||||||

| CISS | Input Capacitance | VGS = 0 V, VDS = 15 V, ƒ = 1 MHz | 360 | 468 | pF | ||

| COSS | Output Capacitance | 101 | 131 | pF | |||

| CRSS | Reverse Transfer Capacitance | 9 | 12 | pF | |||

| Rg | Series Gate Resistance | 3.8 | 7.6 | Ω | |||

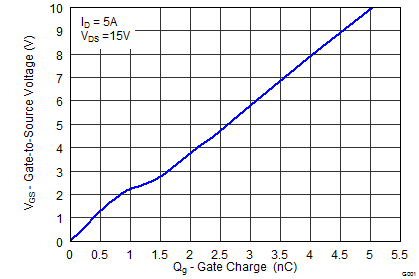

| Qg | Gate Charge Total (4.5 V) | VDS = 15 V, IDS = 5 A | 2.4 | 3.1 | nC | ||

| Qgd | Gate Charge – Gate-to-Drain | 0.6 | nC | ||||

| Qgs | Gate Charge Gate-to-Source | 0.9 | nC | ||||

| Qg(th) | Gate Charge at Vth | 0.6 | nC | ||||

| QOSS | Output Charge | VDS = 15 V, VGS = 0 V | 3.4 | nC | |||

| td(on) | Turn On Delay Time | VDS = 15 V, VGS = 4.5 V, IDS = 5 A RG = 2 Ω |

5.3 | ns | |||

| tr | Rise Time | 19 | ns | ||||

| td(off) | Turn Off Delay Time | 8 | ns | ||||

| tƒ | Fall Time | 2.6 | ns | ||||

| DIODE CHARACTERISTICS | |||||||

| VSD | Diode Forward Voltage | IDS = 5 A, VGS = 0 V | 0.8 | 1 | V | ||

| Qrr | Reverse Recovery Charge | VDD = 15 V, IF = 5 A, di/dt = 300 A/μs | 2.3 | nC | |||

| trr | Reverse Recovery Time | 11 | ns | ||||

5.2 Thermal Information

TA = 25°C unless otherwise specified| THERMAL METRIC | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|

| RθJC | Junction-to-Case Thermal Resistance(1) | 6.2 | °C/W | ||

| RθJA | Junction-to-Ambient Thermal Resistance(1)(2) | 65 | |||

(1) RθJC is determined with the device mounted on a 1 inch2 (6.45 cm2), 2 oz. (0.071 mm thick) Cu pad on a 1.5 inches × 1.5 inches

(3.81 cm × 3.81 cm), 0.06 inch (1.52 mm) thick FR4 PCB. RθJC is specified by design, whereas RθJA is determined by the user’s board design.

(3.81 cm × 3.81 cm), 0.06 inch (1.52 mm) thick FR4 PCB. RθJC is specified by design, whereas RθJA is determined by the user’s board design.

(2) Device mounted on FR4 material with 1 inch2 (6.45 cm2), 2 oz. (0.071 mm thick) Cu.

|

Max RθJA = 65 when mounted on 1 inch2 (6.45 cm2) of 2 oz. (0.071 mm thick) Cu. |

|

Max RθJA = 235 when mounted on minimum pad area of 2 oz. (0.071 mm thick) Cu. |

5.3 Typical MOSFET Characteristics

TA = 25°C unless otherwise specified