SLPS327B September 2012 – April 2018 CSD86360Q5D

PRODUCTION DATA.

- 1Features

- 2Applications

- 3Description

- 4Revision History

- 5Specifications

- 6Application and Implementation

- 7Layout

- 8Device and Documentation Support

- 9Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DQY|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

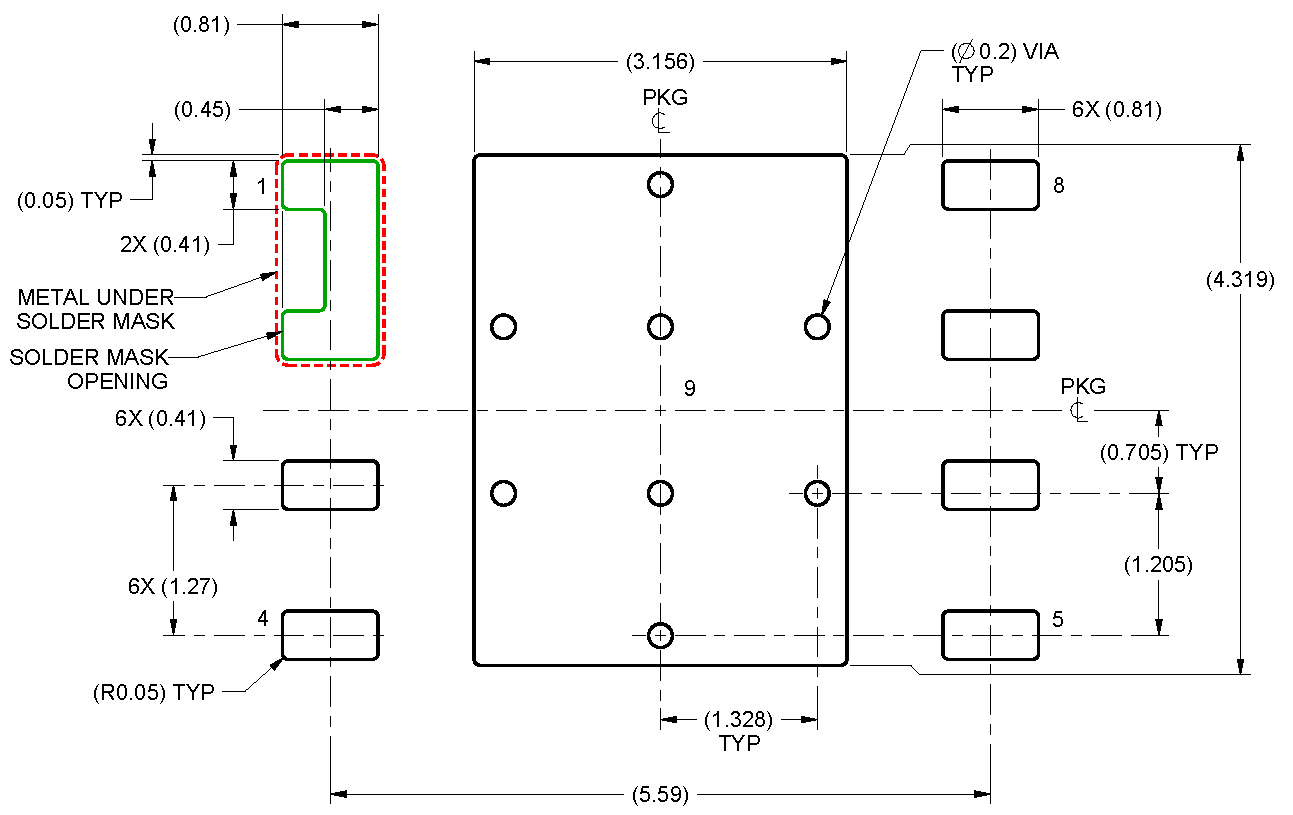

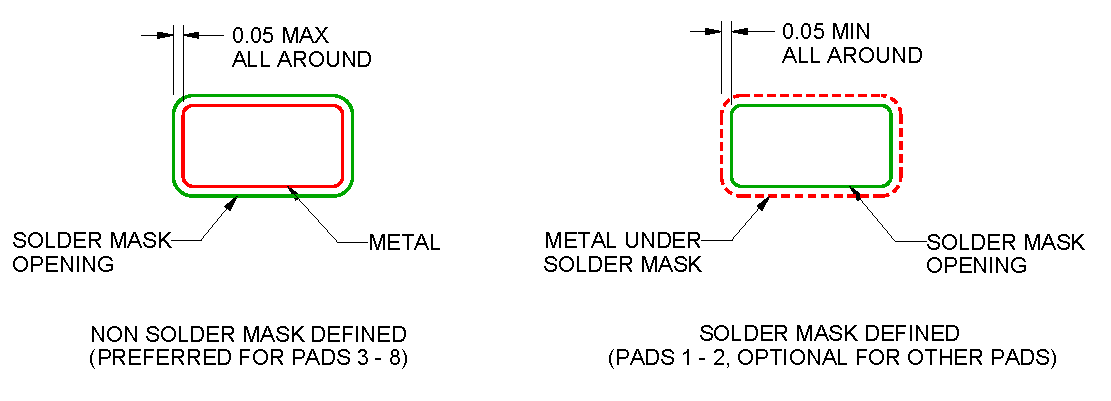

9.2 Land Pattern Recommendation

- This package is designed to be soldered to a thermal pad on the board. For more information, see QFN/SON PCB Attachment (SLUA271).

- Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.