SLASEH4A November 2023 – December 2024 DAC61401 , DAC81401

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Electrical Characteristics

- 5.6 Timing Requirements - Write, IOVDD = 1.7V to 2.7V

- 5.7 Timing Requirements - Write, IOVDD = 2.7V to 5.5V

- 5.8 Timing Requirements - Read and Daisy Chain, FSDO = 0, IOVDD = 1.7V to 2.7V

- 5.9 Timing Requirements - Read and Daisy Chain, FSDO = 1, IOVDD = 1.7V to 2.7V

- 5.10 Timing Requirements - Read and Daisy Chain, FSDO = 0, IOVDD = 2.7V to 5.5V

- 5.11 Timing Requirements - Read and Daisy Chain, FSDO = 1, IOVDD = 2.7V to 5.5V

- 5.12 Timing Diagrams

- 5.13 Typical Characteristics

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4 Device Functional Modes

- 6.5 Programming

- 7 Register Map

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- PW|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

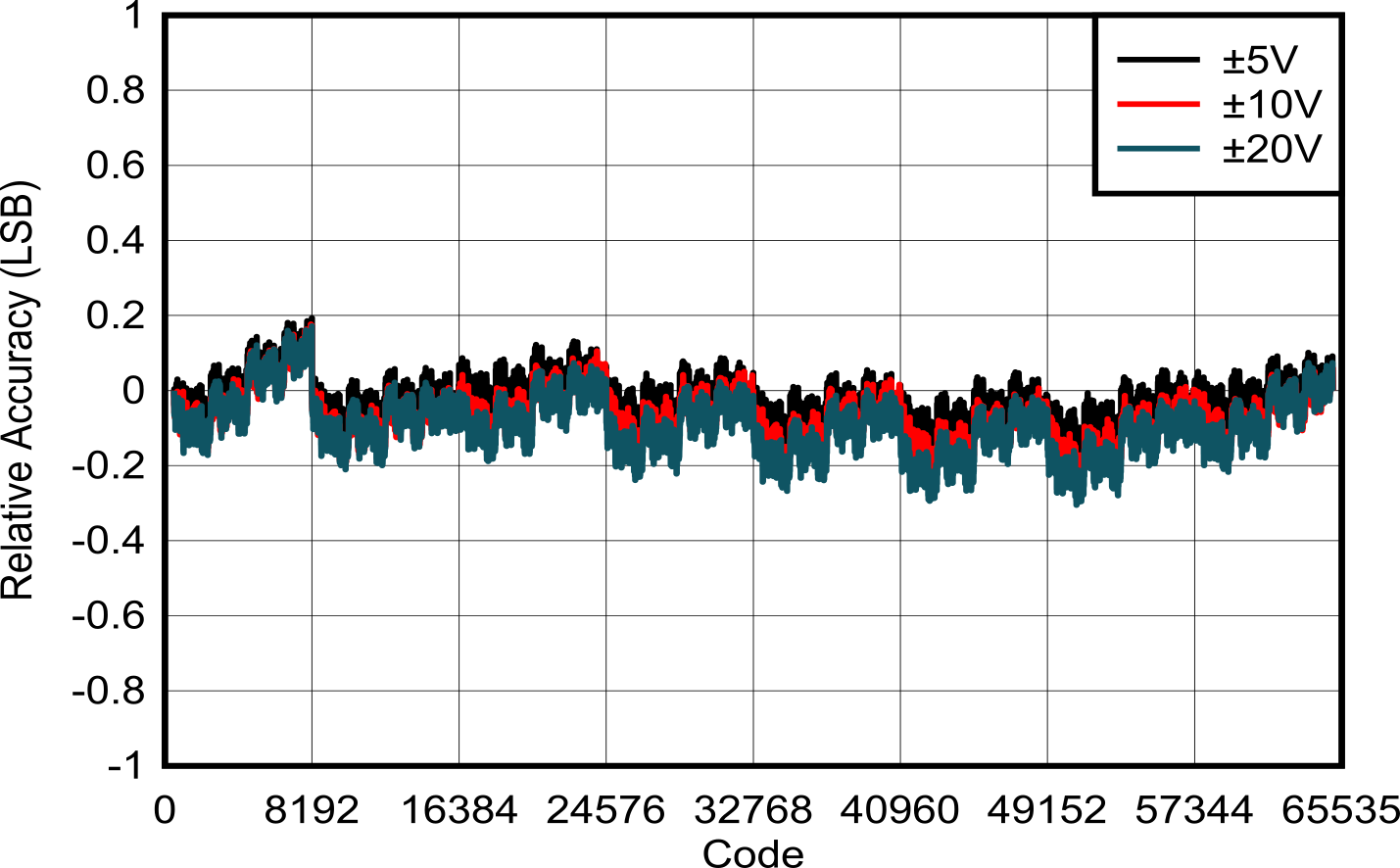

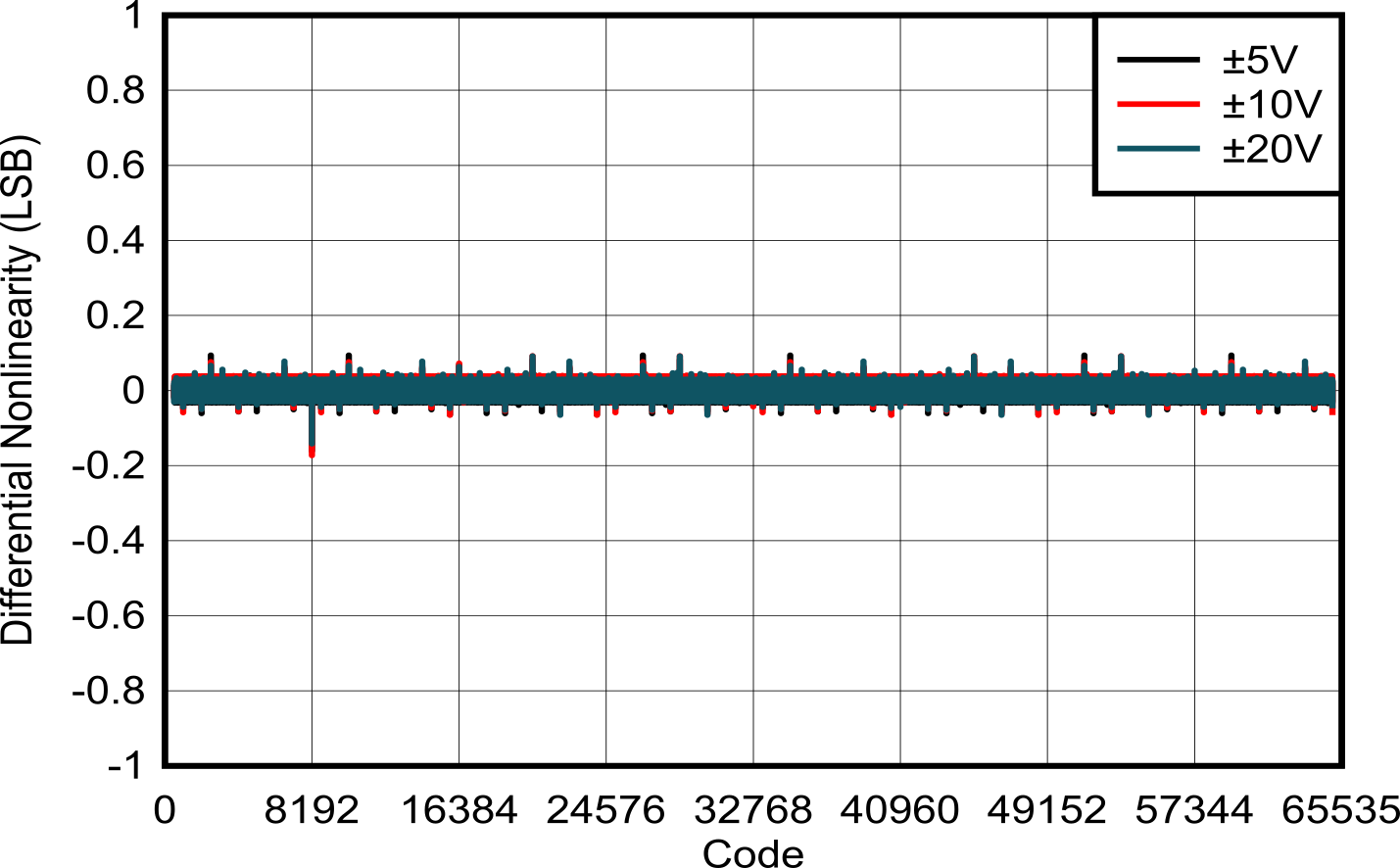

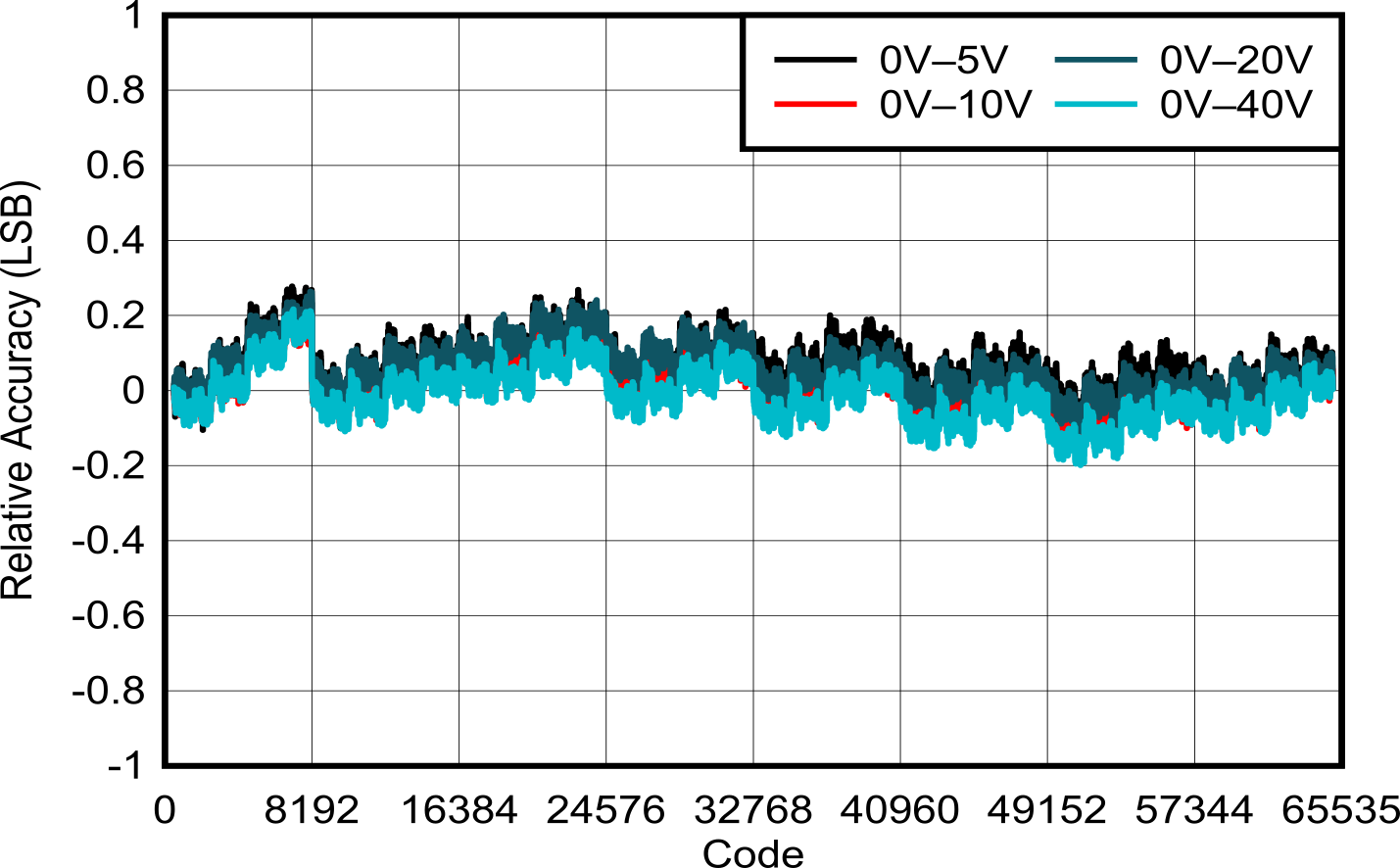

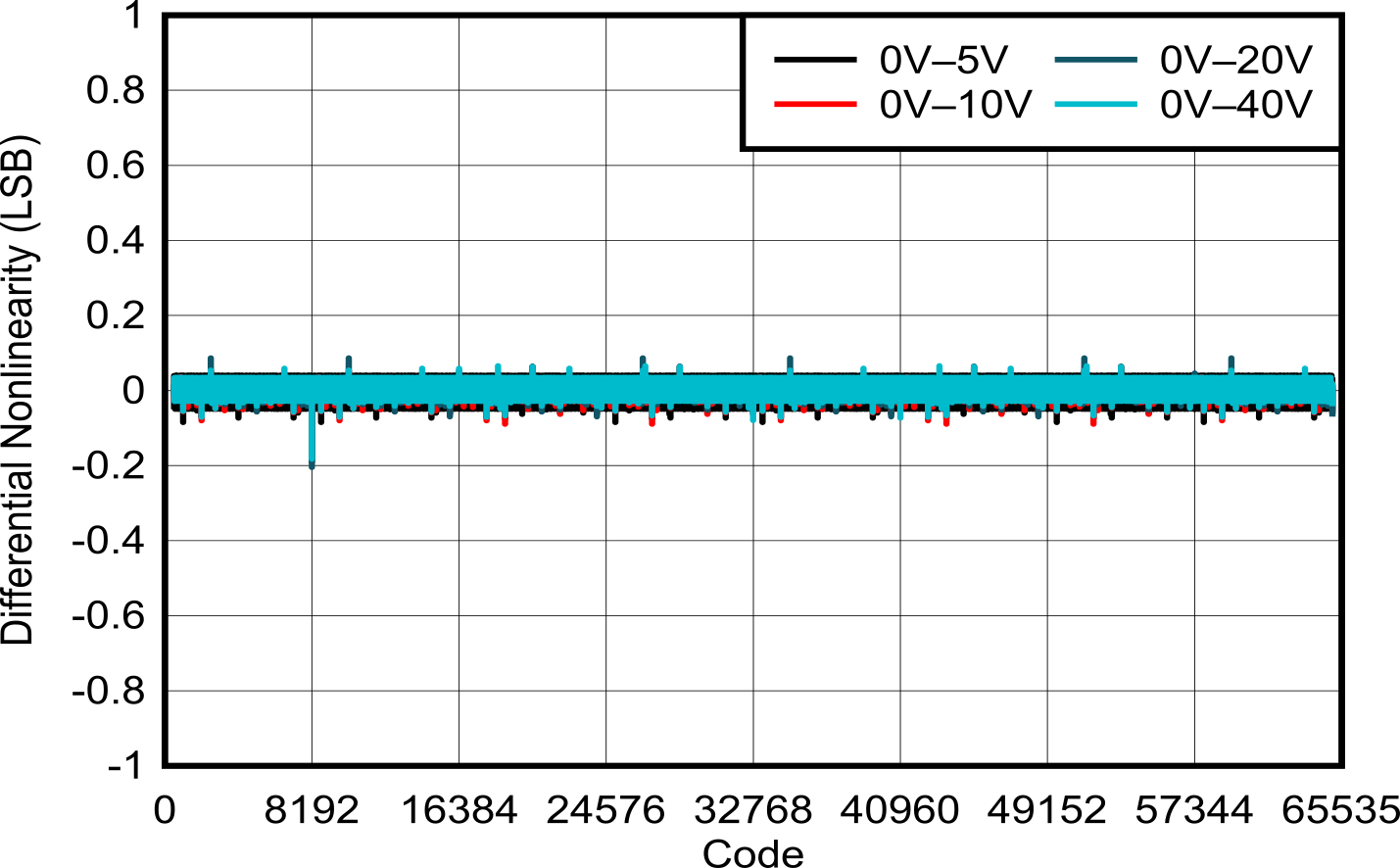

5.13 Typical Characteristics

at TA = 25°C, VDD = 5.0V, IOVDD = 1.8V, external reference, unipolar ranges: AVSS = 0V and AVDD ≥ VMAX + 1.5V for the DAC range, bipolar ranges: AVSS ≤ VMIN − 1.5V and AVDD ≥ VMAX + 1.5V for the DAC range, and DAC output unloaded (unless otherwise noted)

(Bipolar Outputs)

(Bipolar Outputs)

(Bipolar Outputs)

(Bipolar Outputs)

(Bipolar Outputs)

(Bipolar Outputs)

vs Digital Input Code

| DAC range = ±20V |

vs Output Current

| DAC range = ±10V |

| DAC range = ±20V |

| DAC range = ±10V |

Falling Edge

| DAC range= 0V to 5V | midscale code | |

(Unipolar Outputs)

(Unipolar Outputs)

(Unipolar Outputs)

(Unipolar Outputs)

(Unipolar Outputs)

(Unipolar Outputs)

vs Digital Input Code

vs Supply Voltage

| DAC range = ±20V |

| DAC range = ±10V |

| DAC range = ±10V |

Rising Edge

| DAC range= 0V to 5V | midscale code | |

vs Supply Voltage

| VOUT = 0V (DAC code at midscale), output unloaded, | ||

| AVDD = 10V, AVSS = –10V, VDD = 5V, | ||

| supply noise VPP = 0.2V |