SLVSH58 August 2024 DRV81004-Q1

ADVANCE INFORMATION

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3

Feature Description

- 6.3.1 Control Pins

- 6.3.2 Power Supply

- 6.3.3 Power Stage

- 6.3.4 Protection and Diagnostics

- 6.3.5

SPI Communication

- 6.3.5.1 SPI Signal Description

- 6.3.5.2 Daisy Chain Capability

- 6.3.5.3 SPI Protocol

- 6.3.5.4

SPI Registers

- 6.3.5.4.1 Standard Diagnosis Register

- 6.3.5.4.2 Output control register

- 6.3.5.4.3 Input 0 Mapping Register

- 6.3.5.4.4 Input 1 Mapping Register

- 6.3.5.4.5 Input Status Monitor Register

- 6.3.5.4.6 Open Load Current Control Register

- 6.3.5.4.7 Output Status Monitor Register

- 6.3.5.4.8 Configuration Register

- 6.3.5.4.9 Output Clear Latch Register

- 6.3.5.4.10 Configuration Register 2

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PWP|14

Thermal pad, mechanical data (Package|Pins)

- PWP|14

Orderable Information

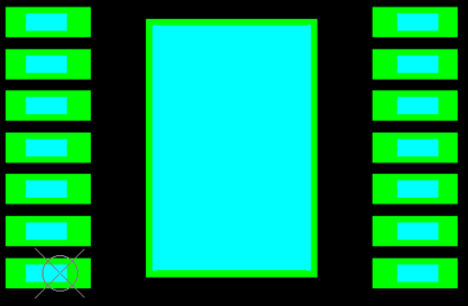

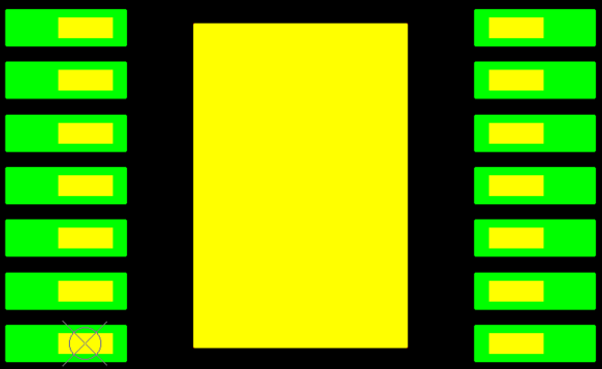

7.2.2 Package Footprint Compatibility

The PWP0014L package of the DRV81004-Q1 is footprint compatible with other SO-14 packages used in the industry, as shown in Figure 7-2 and Figure 7-3.

Figure 7-2 PWP0014L on another SO-14 PCB Pad, Light blue: TI PWP0014L leads, Green: Other SO-14 PCB Pad

Figure 7-2 PWP0014L on another SO-14 PCB Pad, Light blue: TI PWP0014L leads, Green: Other SO-14 PCB Pad Figure 7-3 SO-14 on PWP0014L PCB Pad, Yellow: Other SO-14 leads, Green: TI PWP0014L PCB Pad

Figure 7-3 SO-14 on PWP0014L PCB Pad, Yellow: Other SO-14 leads, Green: TI PWP0014L PCB Pad