SLOSE50A April 2020 – June 2021

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- RGE|24

Orderable Information

3 Description

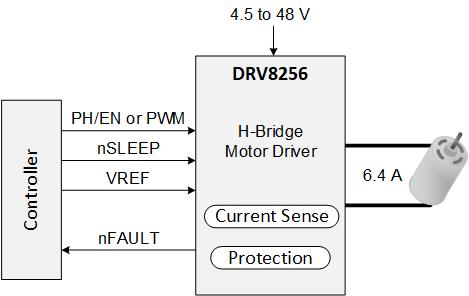

The DRV8256E/P devices are single H-bridge motor drivers for a wide variety of industrial applications. The devices integrate an N-channel H-bridge, charge pump regulator, current sensing and regulation, and protection circuitry.

Integrated current sensing allows the driver to regulate the motor inrush current during start up and high load events. A current limit can be set with an adjustable external voltage reference. The integrated current sensing uses an internal current mirror architecture, removing the need for a large power shunt resistor, saving board area and reducing system cost. A low-power sleep mode is provided to achieve ultra-low quiescent current draw by shutting down most of the internal circuitry.

Internal protection features are provided for supply undervoltage lockout (UVLO), charge pump undervoltage (CPUV), output overcurrent (OCP), and device overtemperature (TSD). Fault conditions are indicated on nFAULT.

| PART NUMBER (1) | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| DRV8256EPWPR | HTSSOP (28) | 9.7mm x 4.4mm |

| DRV8256ERGER | VQFN (24) | 4.0mm x 4.0mm |

| DRV8256PPWPR | HTSSOP (28) | 9.7mm x 4.4mm |

| DRV8256PRGER | VQFN (24) | 4.0mm x 4.0mm |

DRV8256 Simplified Schematic

DRV8256 Simplified Schematic