SNLS683 june 2023 DS320PR1601

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Programming

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZDG|354

Thermal pad, mechanical data (Package|Pins)

Orderable Information

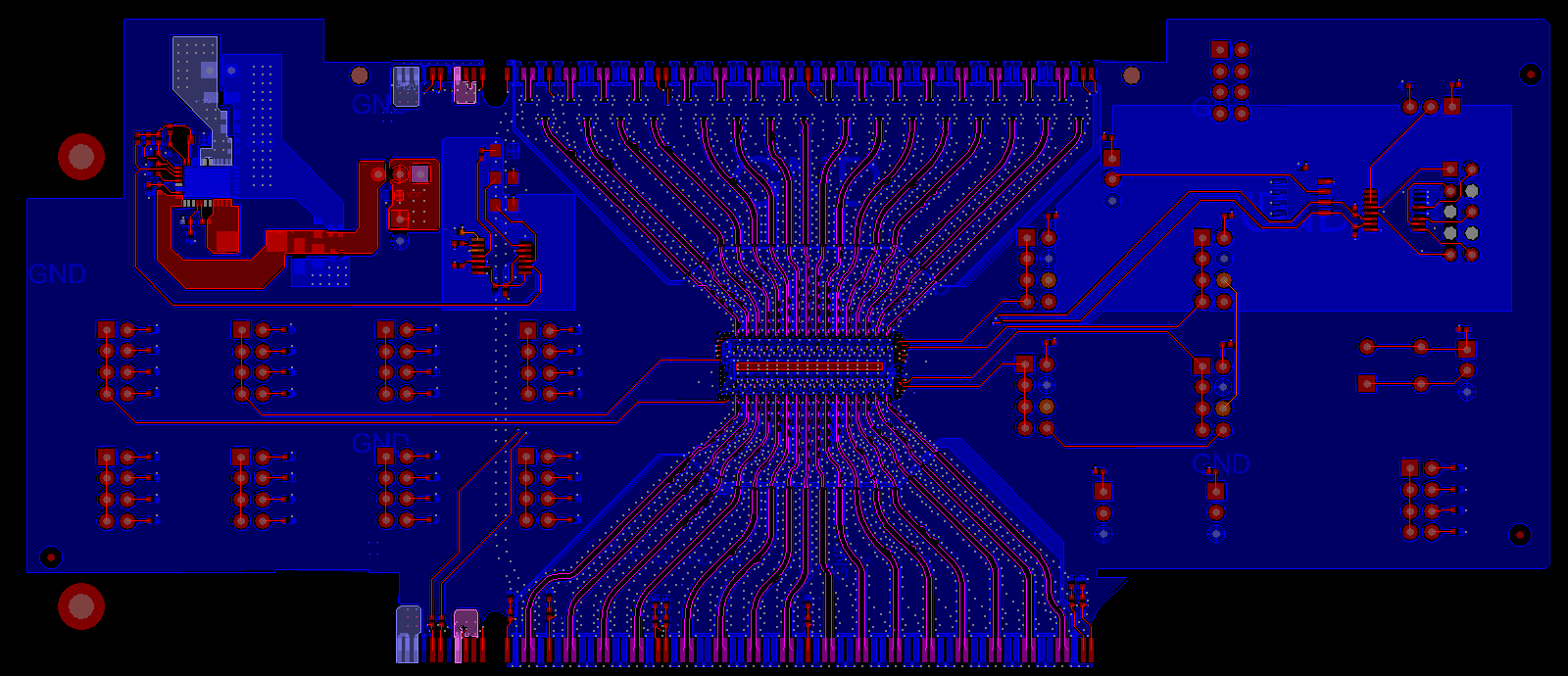

9.4.2 Layout Example

Figure 9-7 Top Layer View of

TI PCIe Riser Card Using DS320PR1601 with CEM

Connectors

Figure 9-7 Top Layer View of

TI PCIe Riser Card Using DS320PR1601 with CEM

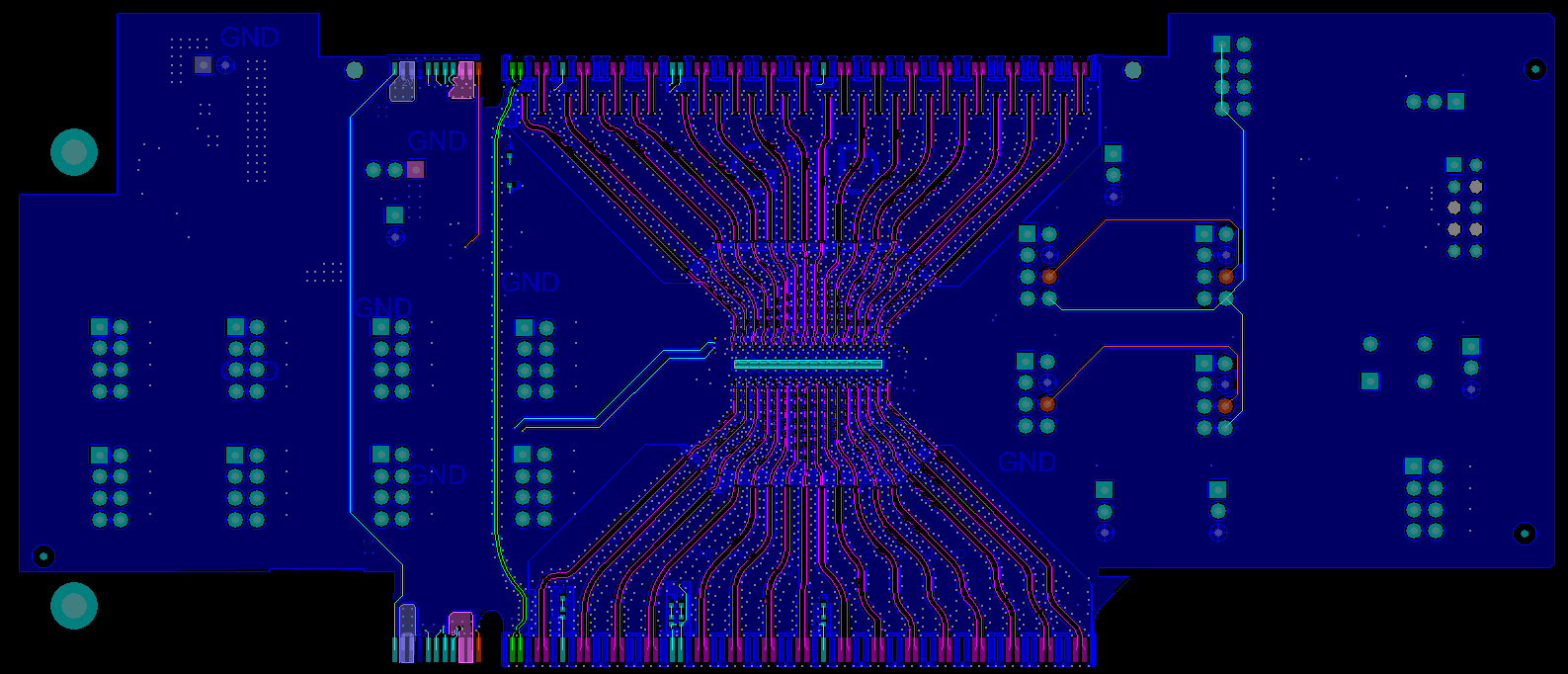

Connectors Figure 9-8 Bottom Layer View of TI PCIe Riser

Card Using DS320PR1601 with CEM Connectors

Figure 9-8 Bottom Layer View of TI PCIe Riser

Card Using DS320PR1601 with CEM Connectors