SNVS739F December 2011 – October 2016 LM10504

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - General

- 6.6 Electrical Characteristics - Buck 1

- 6.7 Electrical Characteristics - Buck 2

- 6.8 Electrical Characteristics - Buck 3

- 6.9 Electrical Characteristics - LDO

- 6.10 Electrical Characteristics - Comparators

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4

Device Functional Modes

- 7.4.1 Start-Up Sequence

- 7.4.2 Power-On Default and Device Enable

- 7.4.3 Reset Pin Function

- 7.4.4 DevSLP Function

- 7.4.5 Vselect_B2, Vselect_B3 Function

- 7.4.6 Undervoltage Lockout (UVLO)

- 7.4.7 Overvoltage Lockout (OVLO)

- 7.4.8 Device Status, Interrupt Enable

- 7.4.9 Thermal Shutdown (TSD)

- 7.4.10 Comparator

- 7.5 Programming

- 7.6 Register Maps

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2 Detailed Design Procedure

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YFR|34

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Layout

10.1 Layout Guidelines

PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss in the traces. These can send erroneous signals to the DC-DC converter resulting in poor regulation or instability. Good layout can be implemented by following a few simple design rules.

- Minimize area of switched current loops. In a buck regulator there are two loops where currents are switched rapidly. The first loop starts from the CIN input capacitor, to the regulator SWx_VIN pin, to the regulator SW pin, to the inductor then out to the output capacitor COUTand load. The second loop starts from the output capacitor ground, to the regulator SWx_GND pins, to the inductor and then out to COUT and the load (see Figure 31). To minimize both loop areas, the input capacitor must be placed as close as possible to the VIN pin. Grounding for both the input and output capacitors must consist of a small localized top-side plane that connects to PGND. The inductor must be placed as close as possible to the SW pin and output capacitor.

- Minimize the copper area of the switch node. The SW pins must be directly connected with a trace that runs on top-side directly to the inductor. To minimize IR losses this trace must be as short as possible and with a sufficient width. However, a trace that is wider than 100 mils increases the copper area and cause too much capacitive loading on the SW pin. The inductors must be placed as close as possible to the SW pins to further minimize the copper area of the switch node.

- Have a single point ground for all device analog grounds. The ground connections for the feedback components must be connected together then routed to the GND pin of the device. This prevents any switched or load currents from flowing in the analog ground plane. If not properly handled, poor grounding can result in degraded load regulation or erratic switching behavior.

- Minimize trace length to the FB pin. The feedback trace must be routed away from the SW pin and inductor to avoid contaminating the feedback signal with switch noise.

- Make input and output bus connections as wide as possible. This reduces any voltage drops on the input or output of the converter and can improve efficiency. If voltage accuracy at the load is important make sure feedback voltage sense is made at the load. Doing so corrects for voltage drops at the load and provide the best output accuracy.

10.1.1 PCB Layout Thermal Dissipation For DSGBA Package

- Position ground layer as close as possible to DSBGA package. Second PCB layer is usually good option. LM10504 evaluation board is a good example.

- Draw power traces as wide as possible. Bumps which carry high currents must be connected to wide traces. This helps the silicon to cool down.

10.2 Layout Example

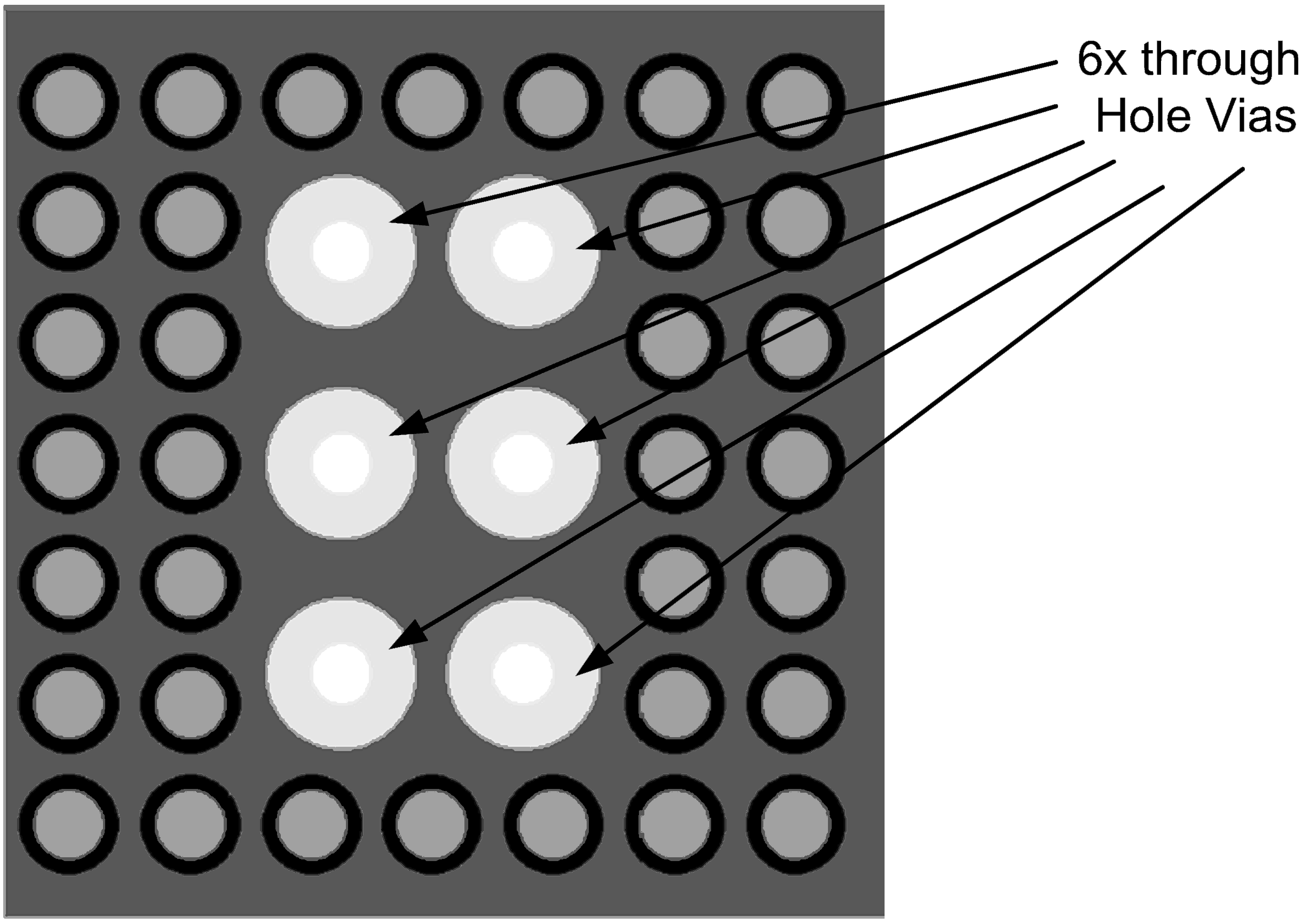

Outside 7×7 array, 0.4-mm DSBGA 34-bump with 24 peripheral and 6 inner vias = 30 individual signals

Figure 30. Possible PCB Layout Configuration

Figure 31. Schematic of LM10504 Highlighting Layout Sensitive Nodes

Figure 31. Schematic of LM10504 Highlighting Layout Sensitive Nodes