SNVS782C October 2010 – August 2015 LM3243

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YFQ|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Layout

10.1 Layout Guidelines

PC board layout is critical to successfully designing a DC-DC converter into a product. A properly planned board layout optimizes the performance of a DC-DC converter and minimizes effects on surrounding circuitry while also addressing manufacturing issues that can have adverse impacts on board quality and final product yield.

10.1.1 PCB Considerations

Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss in the traces. Erroneous signals could be sent to the DC-DC converter device, resulting in poor regulation or instability. Poor layout can also result in re-flow problems leading to poor solder joints between the DSBGA package and board pads. Poor solder joints can result in erratic or degraded performance of the converter.

10.1.1.1 Energy Efficiency

Minimize resistive losses by using wide traces between the power components and doubling up traces on multiple layers when possible

10.1.1.2 EMI

By its very nature, any switching converter generates electrical noise. The circuit board designer’s challenge is to minimize, contain, or attenuate such switcher-generated noise. A high-frequency switching converter, such as the LM3243, switches Ampere level currents within nanoseconds, and the traces interconnecting the associated components can act as radiating antennas. The following guidelines are offered to help to ensure that EMI is maintained within tolerable levels.

To help minimize radiated noise:

- Place the LM3243 switcher, its input capacitor, and output filter inductor and capacitor close together, and make the interconnecting traces as short as possible.

- Arrange the components so that the switching current loops curl in the same direction. During the first half of each cycle, current flows from the input filter capacitor, through the internal PFET of the LM3243 and the inductor, to the output filter capacitor, then back through ground, forming a current loop. In the second half of each cycle, current is pulled up from ground, through the internal synchronous NFET of the LM3243 by the inductor, to the output filter capacitor and then back through ground, forming a second current loop. Routing these loops so the current curls in the same direction prevents magnetic field reversal between the two half-cycles and reduces radiated noise.

- Make the current loop area(s) as small as possible. Interleave doubled traces with ground planes or return paths, where possible, to further minimize trace inductances.

To help minimize conducted noise in the ground-plane:

- Reduce the amount of switching current that circulates through the ground plane: Connect the ground bumps of the LM3243 and its input filter capacitor together using generous component-side copper fill as a pseudo-ground plane. Then connect this copper fill to the system ground-plane (if one is used) by multiple vias located at the input filter capacitor ground terminal. The multiple vias help to minimize ground bounce at the LM3243 by giving it a low-impedance ground connection.

To help minimize coupling to the DC-DC converter voltage feedback trace:

- Route noise sensitive traces, such as the voltage feedback path (FB), as directly as possible from the switcher FB pad to the VOUT pad of the output capacitor, but keep it away from noisy traces between the power components.

To help minimize noise coupled back into power supplies:

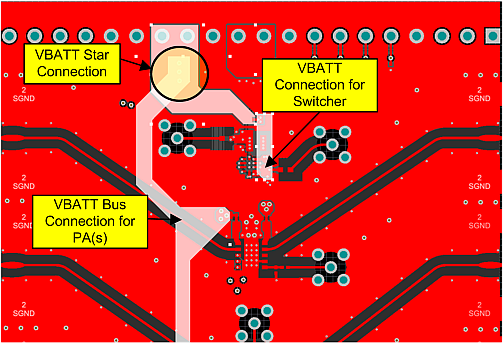

- Use a star connection to route from the VBATT power input to Switcher PVIN and to VBATT_PA.

- Route traces for minimum inductance between supply pins and bypass capacitor(s).

- Route traces to minimize inductance between bypass capacitors and the ground plane.

- Maximize power supply trace inductance(s) to reduce coupling among function blocks.

- Inserting a ferrite bead in-line with power supply traces can offer a favorable tradeoff in terms of board area, by attenuating noise that might otherwise propagate through the supply connections, allowing the use of fewer bypass capacitors.

VBATT Star Connection: It is critically important to use a ‘Star’ connection from VBATT supply to LM3243 PVIN and from VBATT to PA modules as implementing a ‘daisy chain’ supply connection may add noise to the PA output.

Figure 26. VBATT Star Connection on VIN And VBATT_PA

Figure 26. VBATT Star Connection on VIN And VBATT_PA

10.1.2 Manufacturing Considerations

The LM3243 package employs a 16-pin (4 × 4) array of 0.24-mm solder balls, with a 0.4-mm pad pitch. A few simple design rules will go a long way to ensuring a good layout.

- Pad size should be 0.225 ± 0.02 mm. Solder mask opening should be 0.325 ± 0.02 mm.

- As a thermal relief, connect to each pad with 9 mil wide, 6 mil long traces and incrementally increase each trace to its optimal width. Symmetry is important to ensure the solder bumps re-flow evenly. Refer to TI Application Note AN-1112 DSBGA Wafer Level Chip Scale Package (SNVA009).

10.2 Layout Example

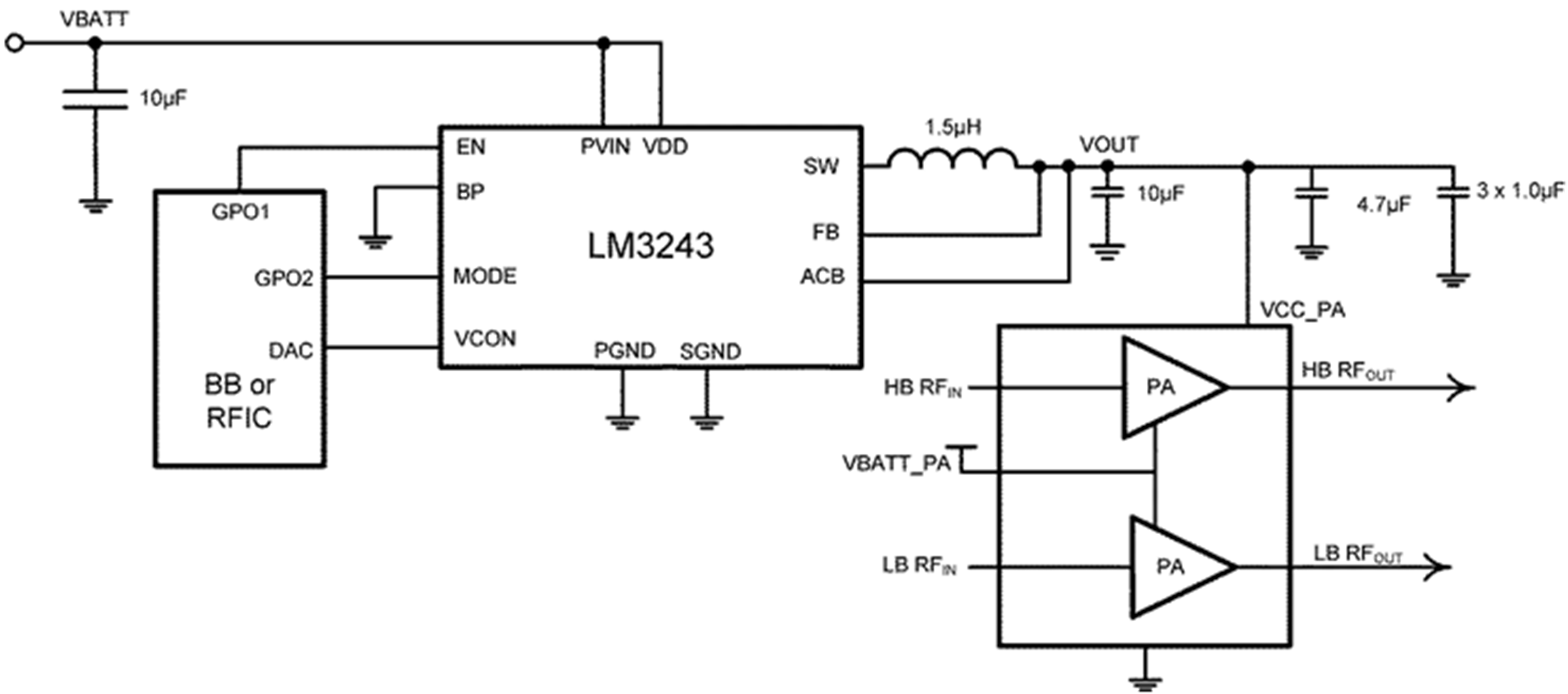

Figure 27. Simplified LM3243 RF Evaluation Board Schematic

Figure 27. Simplified LM3243 RF Evaluation Board Schematic

10.2.1 LM3243 RF Evaluation Board

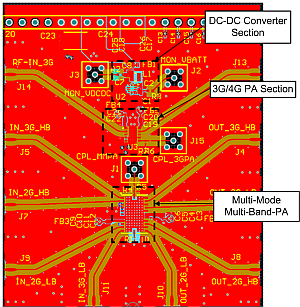

Figure 28. Top View of RF Evaluation Board With PAs

Figure 28. Top View of RF Evaluation Board With PAs

10.2.2 DC-DC Converter Section

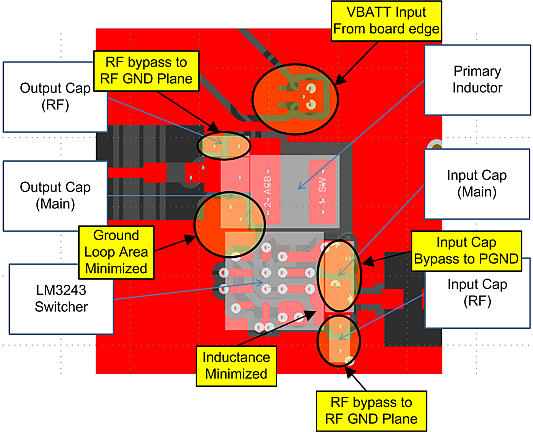

Figure 29. Top Layer

Figure 29. Top Layer

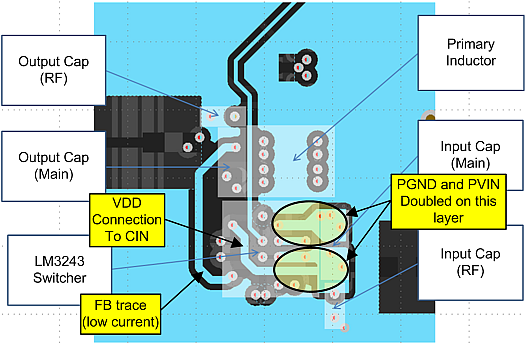

Figure 30. Board Layer 2 - FB, VDD, Additional Routing For PGND, PVIN

Figure 30. Board Layer 2 - FB, VDD, Additional Routing For PGND, PVIN

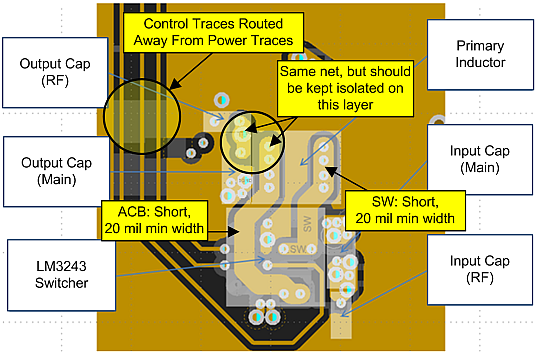

Figure 31. Board Layer 2 - Switcher Detail

Figure 31. Board Layer 2 - Switcher Detail

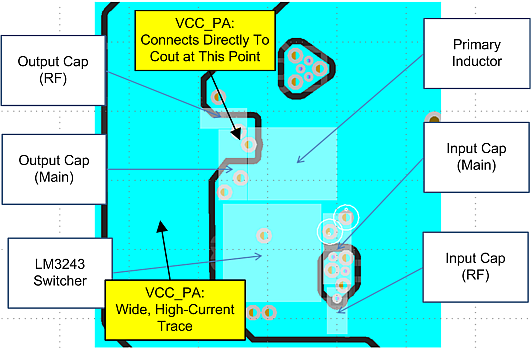

Figure 32. Board Layer 4 - GND Plane VCC_PA

Figure 32. Board Layer 4 - GND Plane VCC_PA

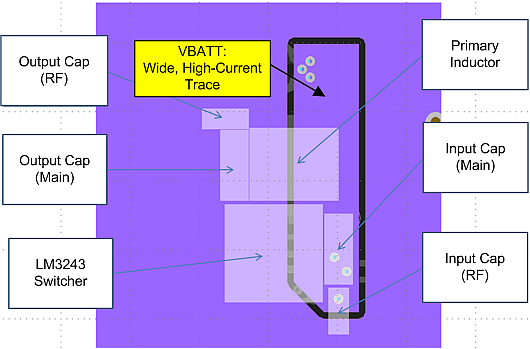

Figure 33. Board Layer 5 - VBATT_SW Connection

Figure 33. Board Layer 5 - VBATT_SW Connection

10.2.3 VBATT Star Supply Connection

Figure 34. Multiple Board Layers - VBATT Supply Star Connection

Figure 34. Multiple Board Layers - VBATT Supply Star Connection

10.3 DSBGA Package Assembly and Use

Use of the DSBGA package requires specialized board layout, precision mounting and careful re-flow techniques, as detailed in TI Application Note AN-1112 DSBGA Wafer Level Chip Scale Package (SNVA009). Please refer to the section Surface Mount Assembly Considerations. For best results in assembly, local alignment fiducials on the PC board should be used to facilitate placement of the device.

The pad style used with DSBGA package must be the NSMD (non-solder mask defined) type. This means that the solder-mask opening is larger than the pad size. This prevents a lip that would otherwise form if the solder-mask and pad overlap, which would hold the device off the surface of the board and interfere with mounting. See SNVA009 for specific instructions how to do this.

The 16-pin package used for LM3243 has 265 micron solder balls and requires 0.225-mm pads for mounting the circuit board. The trace to each pad should enter the pad with a 90°entry angle to prevent debris from being caught in deep corners. Initially, the trace to each pad should be 5.6 mil wide, for a section approximately 5 mil long, as a thermal relief. Then each trace should neck up or down to its optimal width. An important criterion is symmetry to insure the solder bumps on the LM3243 re-flow evenly and that the device solders level to the board. In particular, special attention must be paid to the pads for bumps A1, A3, B1, and B3 since PGND and PVIN are typically connected to large copper planes, inadequate thermal reliefs can result in inadequate re-flow of these bumps.

The DSBGA package is optimized for the smallest possible size in applications with red-opaque or infrared-opaque cases. Because the DSBGA package lacks the plastic encapsulation characteristic of larger devices, it is vulnerable to light. Backside metallization and/or epoxy coating, along with front-side shading by the printed circuit board, reduce this sensitivity. However, the package has exposed die edges that are sensitive to light in the read and infrared range shining on the package’s exposed die edges.