SNVS598B August 2010 – March 2018 LM3535

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2 Detailed Design Procedure

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YFQ|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6.5 Electrical Characteristics

Typical limits are TA = 25°C, and minimum and maximum limits in apply over the full operating temperature range (–30°C to +85°C). Unless otherwise specified: VIN = 3.6 V; VHWEN = VIN; VPWM = 0 V; VDxA = VDxB = VDxC = 0.4 V; GroupA = GroupB = GroupC = full-scale current; ENxA, ENxB, ENxC bits = 1; 53A, 62A bits = 0; C1 = C2 = CIN = COUT= 1 µF.(1)(2)(3)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| IDxx | Output current regulation GroupA |

2.7 V ≤ VIN ≤ 5.5 V EN1A to EN4A = 1, 53A = 62A = 0, EN53 = EN62 = ENxB = ENxC = 0 4 LEDs in GroupA |

23.6 (–5.6%) |

25 | 26.3 (5.2%) |

mA (%) |

|

| 2.7 V ≤ VIN ≤ 5.5 V EN1A to EN4A = EN53 = EN62 = 1, 53A = 62A = 1, ENxB = ENxC = 0 6 LEDs in GroupA |

23.2 (–7.2%) |

25 | 26.3 5.2% |

mA (%) |

|||

| Output current regulation GroupB |

2.7 V ≤ VIN ≤ 5.5 V EN1B = EN53 = EN62 = 1, 53A = 62A = 0, ENxA = ENC = 0 3 LEDs in GroupB |

23.3 (–6.8%) |

25 | (+4%) | mA (%) |

||

| Output current regulation IDC |

2.7 V ≤ VIN ≤ 5.5 V ENC = 1, ENxA = ENxB = 0 |

23.8 (–4.8%) |

25 | 26.8 (7.2%) |

mA (%) |

||

| Output current regulation GroupA, GroupB, and GroupC enabled |

3.2 V ≤ VIN ≤ 5.5V VLED = 3.6 V |

25 DxA |

mA | ||||

| 25 DxB |

|||||||

| 25 DxC |

|||||||

| IDxx-MATCH | LED current matching(4) | 2.7 V ≤ VIN ≤ 5.5 V | GroupA (4 LEDs) | 0.25% | 2.4% | ||

| GroupA (6 LEDs) | 0.55% | 2.78 | |||||

| GroupB (3 LEDs) | 0.25% | 2.41% | |||||

| VDxTH | VDxx 1x to 3/2x gain transition threshold | VDxA and/or VDxB falling | 130 | mV | |||

| VHR | Current sink headroom voltage requirement(5) | IDxx = 95% ×IDxx (nominal) (IDxx (nominal) = 25 mA) |

100 | mV | |||

| ROUT | Open-loop charge pump output resistance | Gain = 3/2 | 2.4 | Ω | |||

| Gain = 1 | 0.5 | ||||||

| IQ | Quiescent supply current | Gain = 3/2, no load | 2.86 | 4.38 | mA | ||

| Gain = 1, no load | 1.09 | 2.31 | |||||

| ISB | Standby supply current | 2.7 V ≤ VIN ≤ 5.5 V HWEN = VIN, all ENx bits = 0 |

1.7 | 4 | µA | ||

| ISD | Shutdown supply current | 2.7 V ≤ VIN ≤ 5.5 V HWEN = 0 V, All ENx bits = 0 |

1.7 | 4 | µA | ||

| fSW | Switching frequency | 1.1 | 1.33 | 1.56 | MHz | ||

| tSTART | Start-up time | VOUT = 90% steady state | 250 | µs | |||

| VALS | ALS reference voltage accuracy | 0.95 (–5%) |

1 | 1.05 5% |

V | ||

| RALS | ALS resistor accuracy | RALS = 9.08 kΩ | –9% | 9% | |||

| RALS = 5.46 kΩ | –9% | 9% | |||||

| VHWEN | HWEN voltage thresholds | 2.7 V ≤ VIN ≤ 5.5 V | Reset | 0 | 0.45 | V | |

| Normal operation | 1.2 | VIN | |||||

| VPWM | PWM voltage thresholds | 2.7 V ≤ VIN ≤ 5.5 V | Diodes off | 0 | 0.45 | V | |

| Diodes on | 1.2 | VIN | |||||

| VOL-INT | Interrupt output logic low 0 | ILOAD = 3 mA | 400 | mV | |||

| I2C-COMPATIBLE INTERFACE VOLTAGE SPECIFICATIONS (SCL, SDIO) | |||||||

| VIL | Input logic low 0 | 2.7 V ≤ VIN ≤ 5.5 V | 0 | 0.45 | V | ||

| VIH | Input logic high 1 | 2.7 V ≤ VIN ≤ 5.5 V | 1.2 | VIN | V | ||

| VOL | SDIO output logic low 0 | ILOAD = 3 mA | 400 | mV | |||

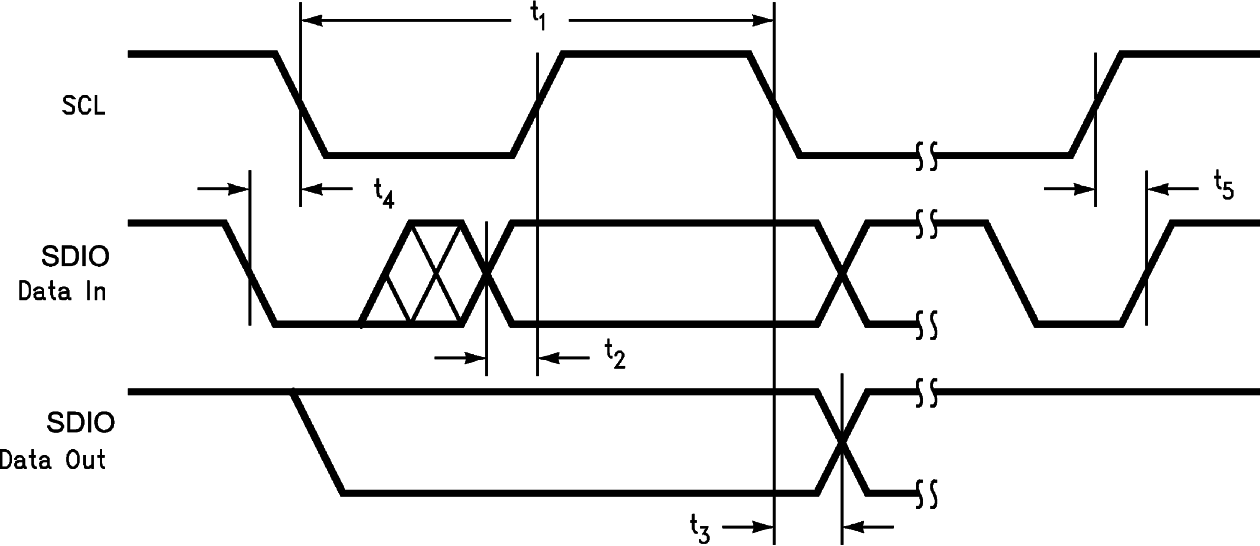

| I2C-COMPATIBLE INTERFACE TIMING SPECIFICATIONS (SCL, SDIO) | |||||||

| t1 | SCL (clock period) | See(6) | 2.5 | µs | |||

| t2 | Data in setup time to SCL high | 100 | ns | ||||

| t3 | Data out stable after SCL low | 0 | ns | ||||

| t4 | SDIO low setup time to SCL low (start) | 100 | ns | ||||

| t5 | SDIO high hold time after SCL high (stop) | 100 | ns | ||||

(1) All voltages are with respect to the potential at the GND pins.

(2) Minimum and maximum limits are ensured by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

(3) CIN, CVOUT, C1, and C2 : Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics

(4) For the two groups of current sinks on a part (GroupA and GroupB), the following are determined: the maximum sink current in the group (MAX), the minimum sink current in the group (MIN), and the average sink current of the group (AVG). For each group, two matching numbers are calculated: (MAX-AVG)/AVG and (AVG-MIN)/AVG. The largest number of the two (worst case) is considered the matching figure for the Group. The matching figure for a given part is considered to be the highest matching figure of the two Groups. The typical specification provided is the most likely norm of the matching figure for all parts.

(5) For each Dxxpin, headroom voltage is the voltage across the internal current sink connected to that pin. For Group A, B, and C current sinks, VHRx = VOUT – VLED. If headroom voltage requirement is not met, LED current regulation will be compromised.

(6) SCL is tested with a 50% duty-cycle clock.

Figure 1. I2C Timing Diagram

Figure 1. I2C Timing Diagram