SNVS449O June 2007 – April 2015 LM3668

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DQB|12

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | |

|---|---|---|---|

| PVIN, VDD, SW1, SW2 & VOUT pins: voltage to SGND & PGND | –0.2 | 6 | V |

| FB, EN, and MODE/SYNC pins | (PGND and SGND-0.2) | (PVIN + 0.2) | V |

| PGND to SGND | –0.2 | 0.2 | V |

| Continuous power dissipation(3) | Internally Limited | ||

| Maximum junction temperature (TJ-MAX) | 125 | °C | |

| Maximum lead temperature (soldering, 10 sec) | 260 | °C | |

| Storage temperature , Tstg | –65 | 150 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP = 125ºC), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the part/package in the application (RθJA), as given by the following equation: TA-MAX = TJ-MAX-OP – (RθJA × PD-MAX).

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2500 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±1250 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

| MIN | MAX | UNIT | |

|---|---|---|---|

| Input voltage | 2.5 | 5.5 | V |

| Recommended load current | 0 | 1 | A |

| Junction temperature (TJ) | −40 | 125 | °C |

| Ambient temperature (TA) (1) | −40 | 85 | °C |

(1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP = 125ºC), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the part/package in the application (RθJA), as given by the following equation: TA-MAX = TJ-MAX-OP – (RθJA × PD-MAX).

7.4 Thermal Information

| THERMAL METRIC(1) | LM3668 | UNIT | |

|---|---|---|---|

| DQB (WSON) | |||

| 12 PINS | |||

| RθJA | Junction-to-ambient thermal resistance, WSON package(2) | 47.3 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 43..4 | |

| RθJB | Junction-to-board thermal resistance | 21.6 | |

| ψJT | Junction-to-top characterization parameter | 0.4 | |

| ψJB | Junction-to-board characterization parameter | 21.7 | |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 3.5 | |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) Junction-to-ambient thermal resistance (RθJA) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 101.6 mm x 76.2 mm x 1.6 mm. Thickness of the copper layers are 2oz/1oz/1oz/2oz. The middle layer of the board is 60 mm x 60 mm. Ambient temperature in simulation is 22°C, still air. Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

7.5 Electrical Characteristics

Unless otherwise noted, specifications apply to the LM3668. VIN = 3.6 V = EN, VOUT = 3.3 V. For VOUT = 4.5V-5 V, VIN = 4 V.(1)(2)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VFB | Feedback voltage | −40°C ≤ TA ≤ 85°C, see(2) | –3% | 3% | ||

| ILIM | Switch peak current limit | Open loop(3) | 1.85 | A | ||

| Switch peak current limit | Open loop(3), −40°C ≤ TA ≤ 85°C | 1.6 | 2.05 | |||

| ISHDN | Shutdown supply current | EN = 0 V | 0.01 | µA | ||

| Shutdown supply current | EN = 0 V, −40°C ≤ TA ≤ 85°C | 1 | ||||

| IQ_PFM | DC bias current in PFM | No load, device is not switching (FB forced higher than programmed output voltage) | 45 | µA | ||

| DC bias current in PFM | No load, device is not switching (FB forced higher than programmed output voltage) −40°C ≤ TA ≤ 85°C |

60 | ||||

| IQ_PWM | DC bias current in PWM | PWM mode, no switching | 600 | µA | ||

| DC bias current in PWM | PWM mode, no switching −40°C ≤ TA ≤ 85°C |

750 | ||||

| RDSON(P) | Pin-pin resistance for PFET | Switches P1 and P2 | 130 | 180 | mΩ | |

| RDSON(N) | Pin-pin resistance for NFET | Switches N1 and N2 | 100 | 150 | mΩ | |

| FOSC | Internal oscillator frequency | PWM mode | 2.2 | MHz | ||

| PWM mode, −40°C ≤ TA ≤ 85°C | 1.9 | 2.5 | ||||

| FSYNC | Sync frequency range | VIN = 3.6 V | 1.6 | 2.7 | MHz | |

| VIH | Logic high input for EN, MODE/SYNC pins | −40°C ≤ TA ≤ 85°C | 1.1 | V | ||

| VIL | Logic low input for EN, MODE/SYNC pins | −40°C ≤ TA ≤ 85°C | 0.4 | V | ||

| IEN, MODE, SYNC | EN, MODE/SYNC pins input current | 0.3 | µA | |||

| −40°C ≤ TA ≤ 85°C | 1 | |||||

(1) All voltages with respect to SGND.

(2) Minimum and Maximum limits are specified by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

(3) Electrical Characteristics table reflects open loop data (FB = 0 V and current drawn from SW pin ramped up until cycle-by-cycle current limits is activated). Closed loop current limit is the peak inductor current measured in the application circuit by increasing output current until output voltage drops by 10%.

(4) CIN and COUT: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics. COUT_MIN should not exceed −40% of suggested value. The preferable choice would be a type and make MLCC that issues –30% over the operating temperature and voltage range.

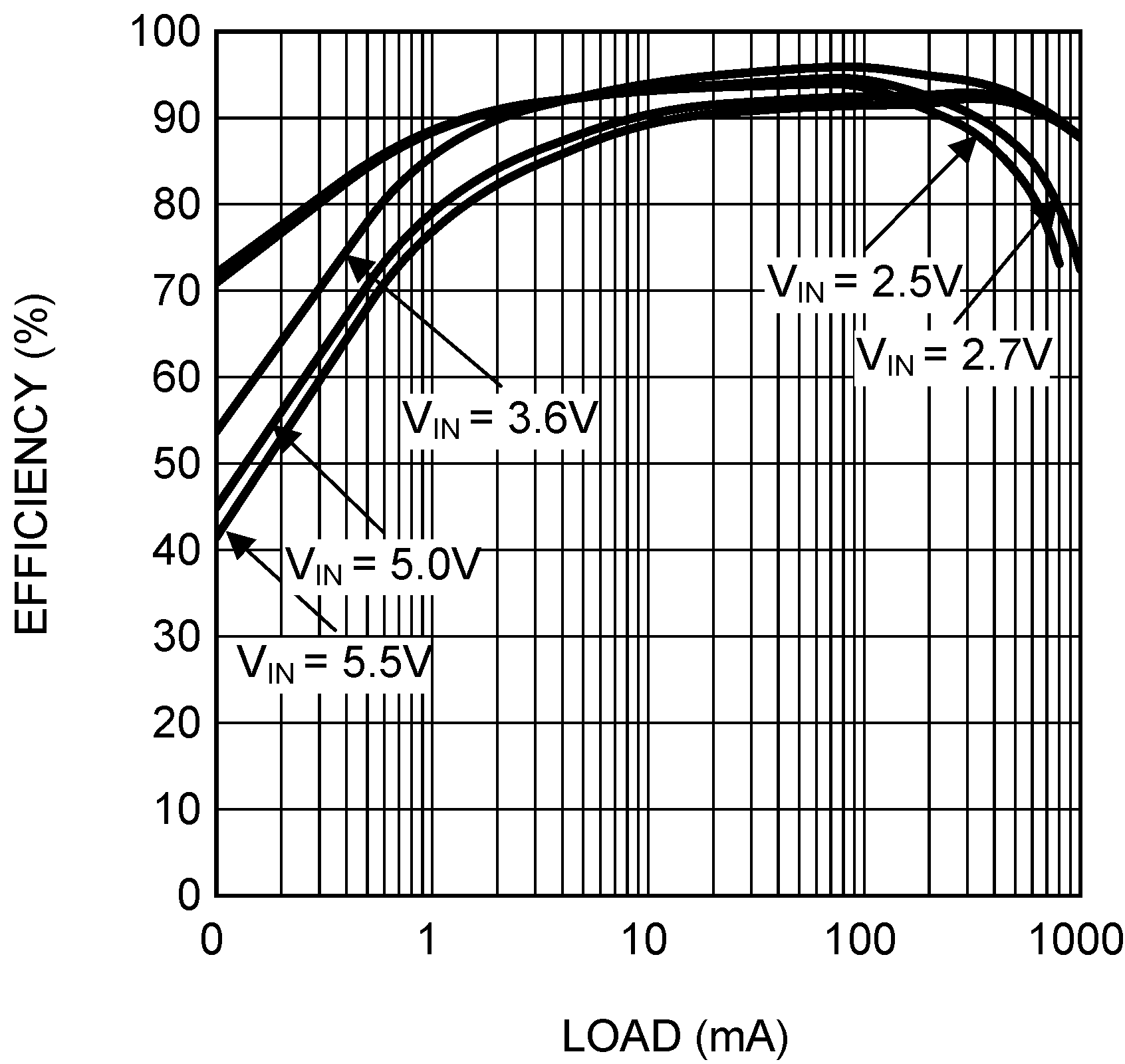

7.6 Typical Characteristics

Typical Application Circuit (see Figure 46): VIN = 3.6 V, L = 2.2 µH, CIN = 10 µF, COUT = 22 µF(4), TA = 25°C , unless otherwise stated. Figure 1. Supply Current vs Temperature (Not Switching)

Figure 1. Supply Current vs Temperature (Not Switching) (VOUT = 3.4 V)

Figure 3. NFET_RDS (on) vs. Temperature (VOUT = 3.4 V)

Figure 3. NFET_RDS (on) vs. Temperature (VOUT = 3.4 V)

Figure 5. ILIMIT vs. Temperature (VOUT = 3.4 V)

Figure 5. ILIMIT vs. Temperature (VOUT = 3.4 V)

Figure 7. Efficiency at VOUT = 2.8 V (Auto Mode)

Figure 7. Efficiency at VOUT = 2.8 V (Auto Mode)

Figure 9. Efficiency at VOUT = 3 V (Auto Mode)

Figure 9. Efficiency at VOUT = 3 V (Auto Mode)

Figure 11. Efficiency at VOUT = 3.3 V (Auto Mode)

Figure 11. Efficiency at VOUT = 3.3 V (Auto Mode)

Figure 13. Efficiency at VOUT = 3.4 V (Auto Mode)

Figure 13. Efficiency at VOUT = 3.4 V (Auto Mode)

Figure 15. Efficiency at VOUT = 4.5 V (Auto Mode)

Figure 15. Efficiency at VOUT = 4.5 V (Auto Mode)

Figure 17. Efficiency at VOUT = 5 V (Auto Mode)

Figure 17. Efficiency at VOUT = 5 V (Auto Mode)

Figure 19. Line Transient in Boost Mode (VOUT = 3.4 V, Load = 500 mA)

Figure 19. Line Transient in Boost Mode (VOUT = 3.4 V, Load = 500 mA)

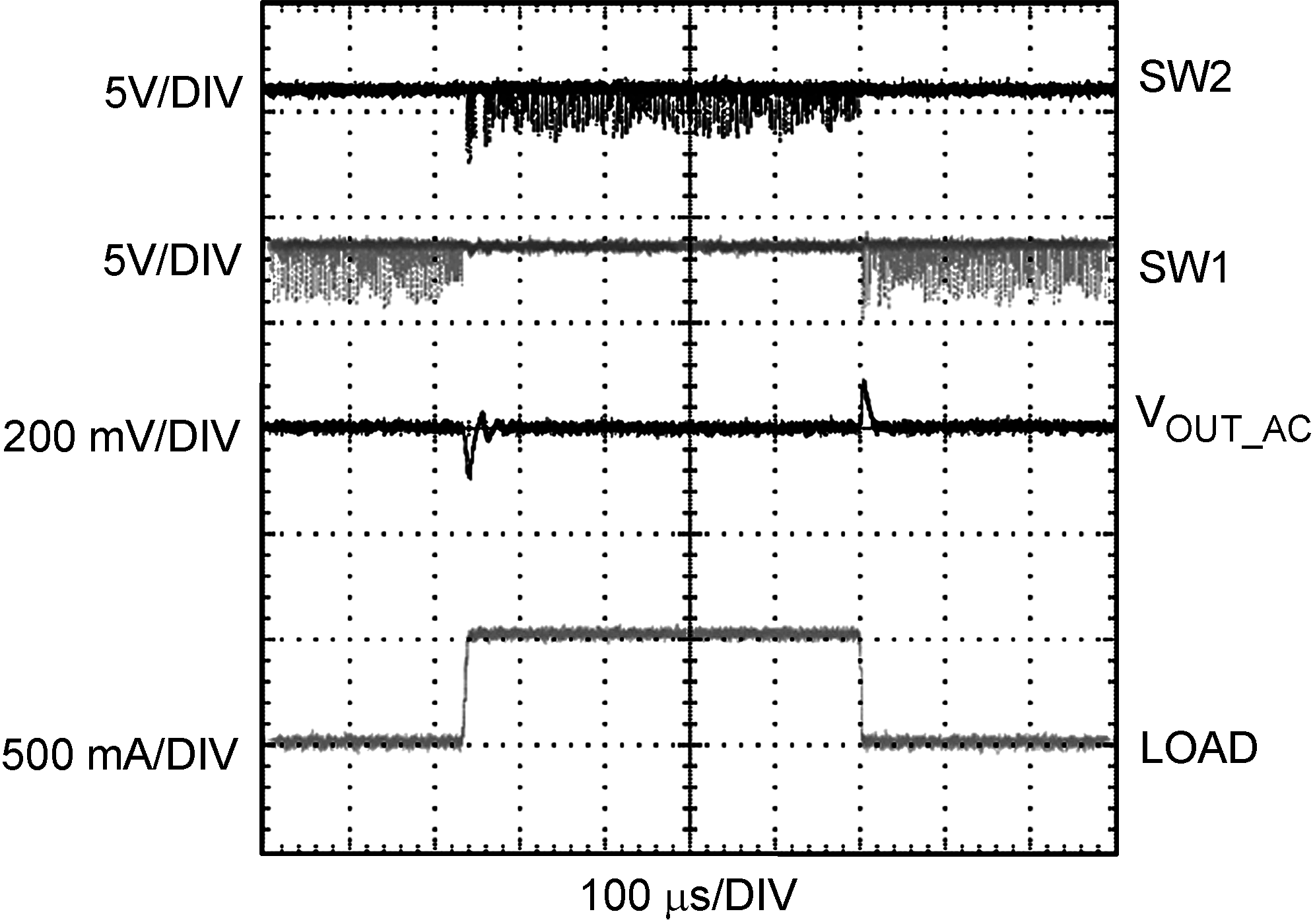

Figure 21. Load Transient in Buck Mode (Forced PWM Mode) VIN = 4.2 V, VOUT = 3.4 V, Load = 0 to 500 mA

Figure 21. Load Transient in Buck Mode (Forced PWM Mode) VIN = 4.2 V, VOUT = 3.4 V, Load = 0 to 500 mA

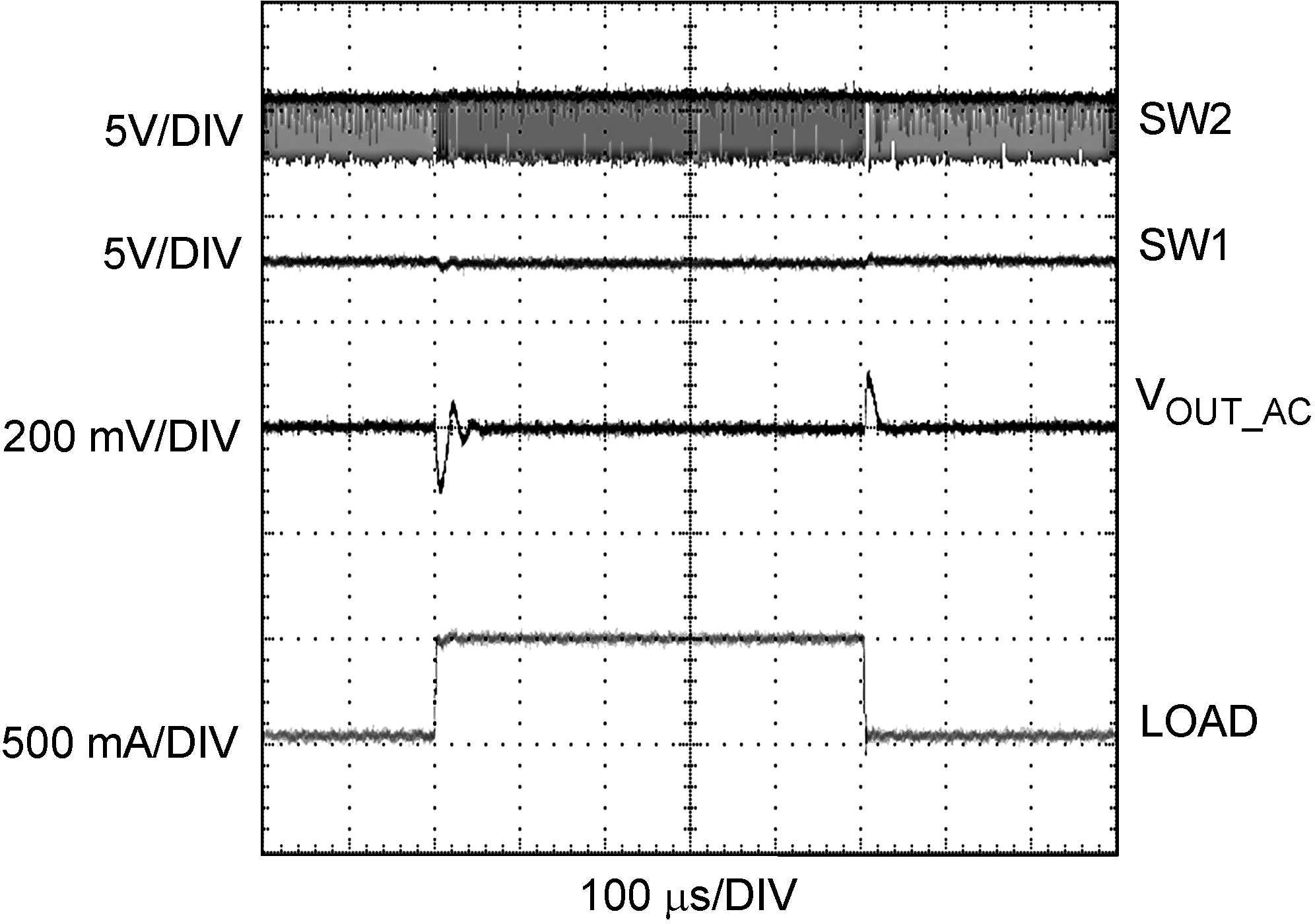

Figure 23. Load Transient in Buck-Boost Operation (Forced PWM Mode) VIN = 3.44 V, VOUT = 3.4 V, Load = 0 to 500 mA

Figure 23. Load Transient in Buck-Boost Operation (Forced PWM Mode) VIN = 3.44 V, VOUT = 3.4 V, Load = 0 to 500 mA

Figure 25. Load Transient in Boost Mode (Forced PWM Mode) VIN = 2.7 V, VOUT = 3 V, Load = 0 to 500 mA

Figure 25. Load Transient in Boost Mode (Forced PWM Mode) VIN = 2.7 V, VOUT = 3 V, Load = 0 to 500 mA

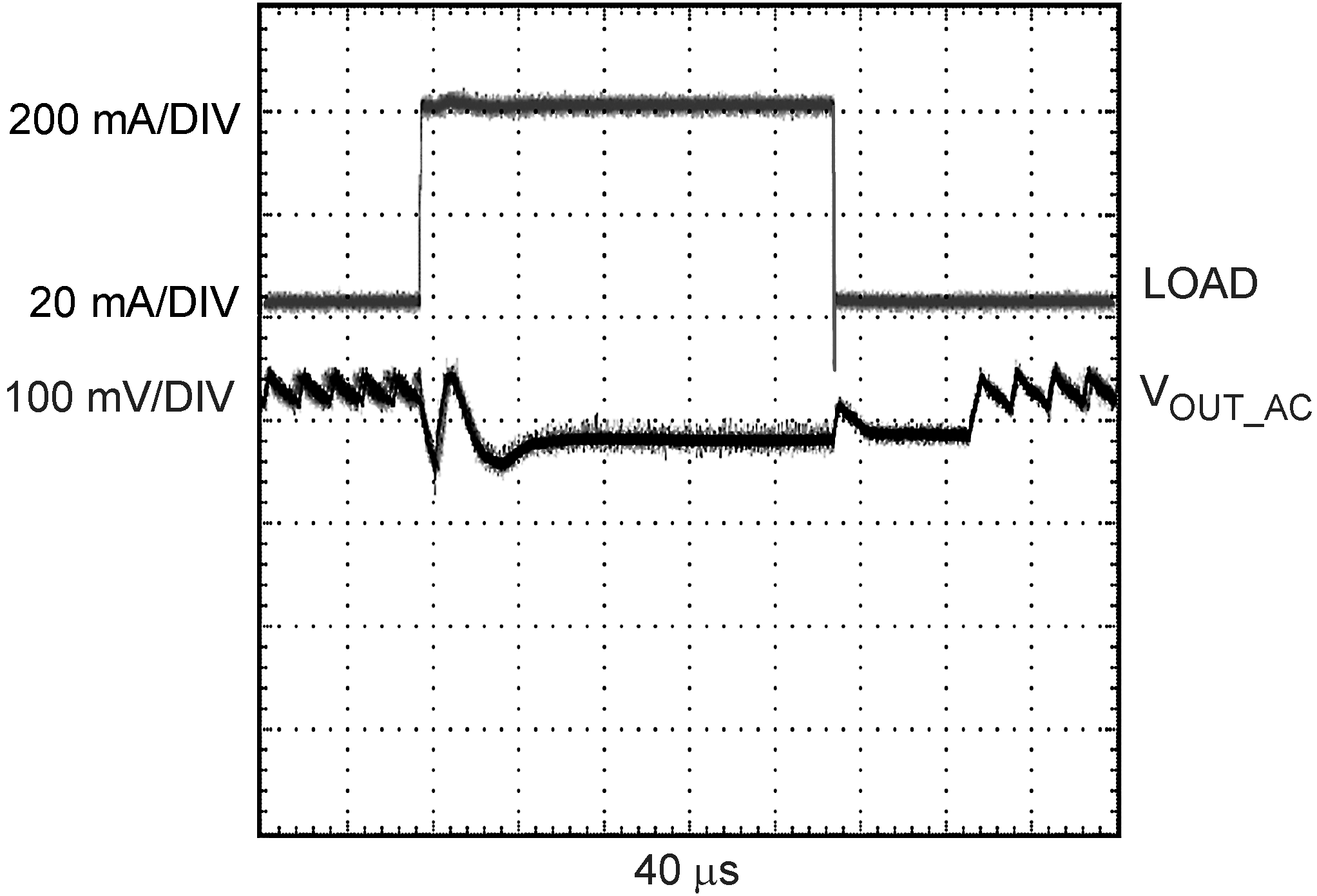

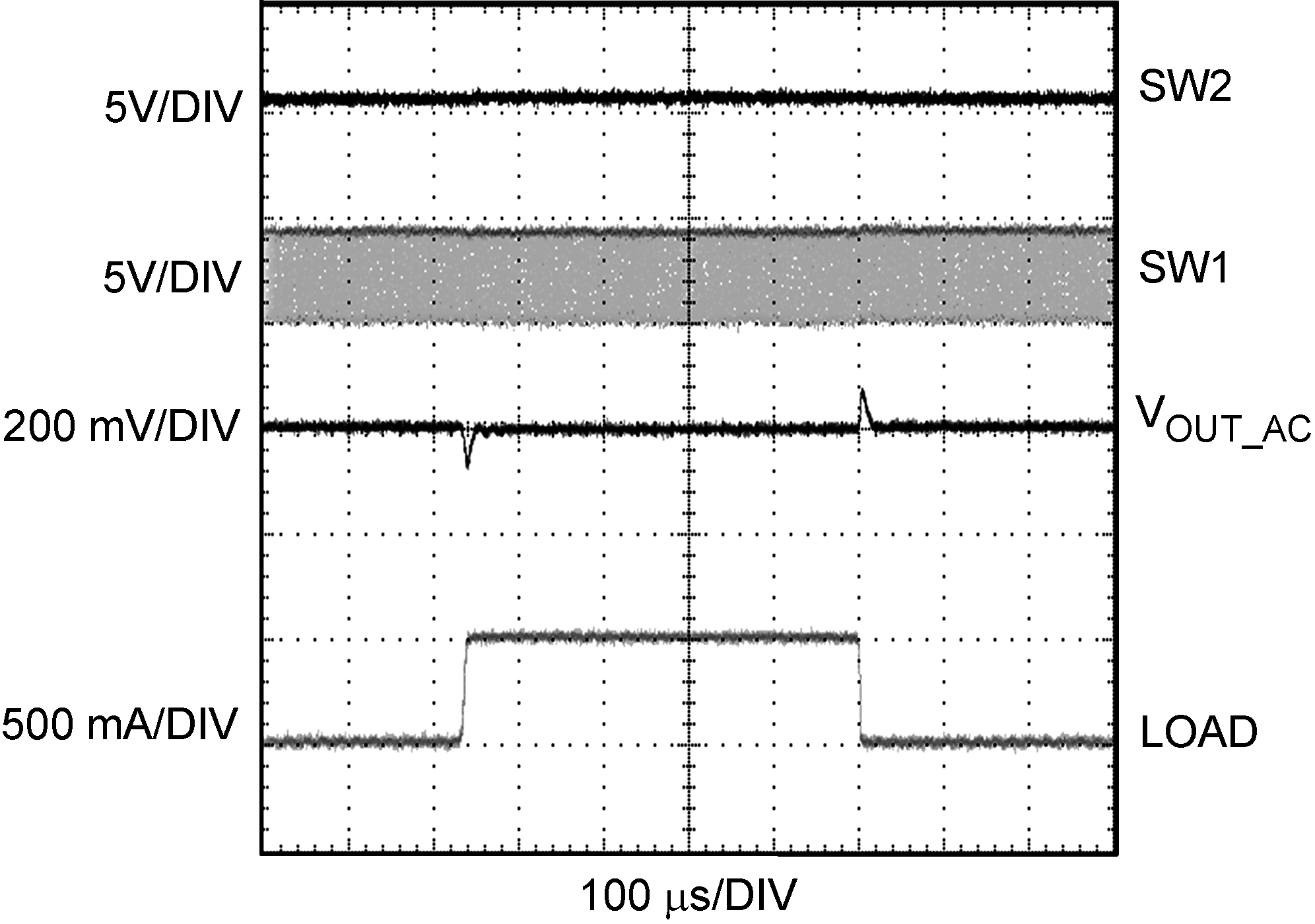

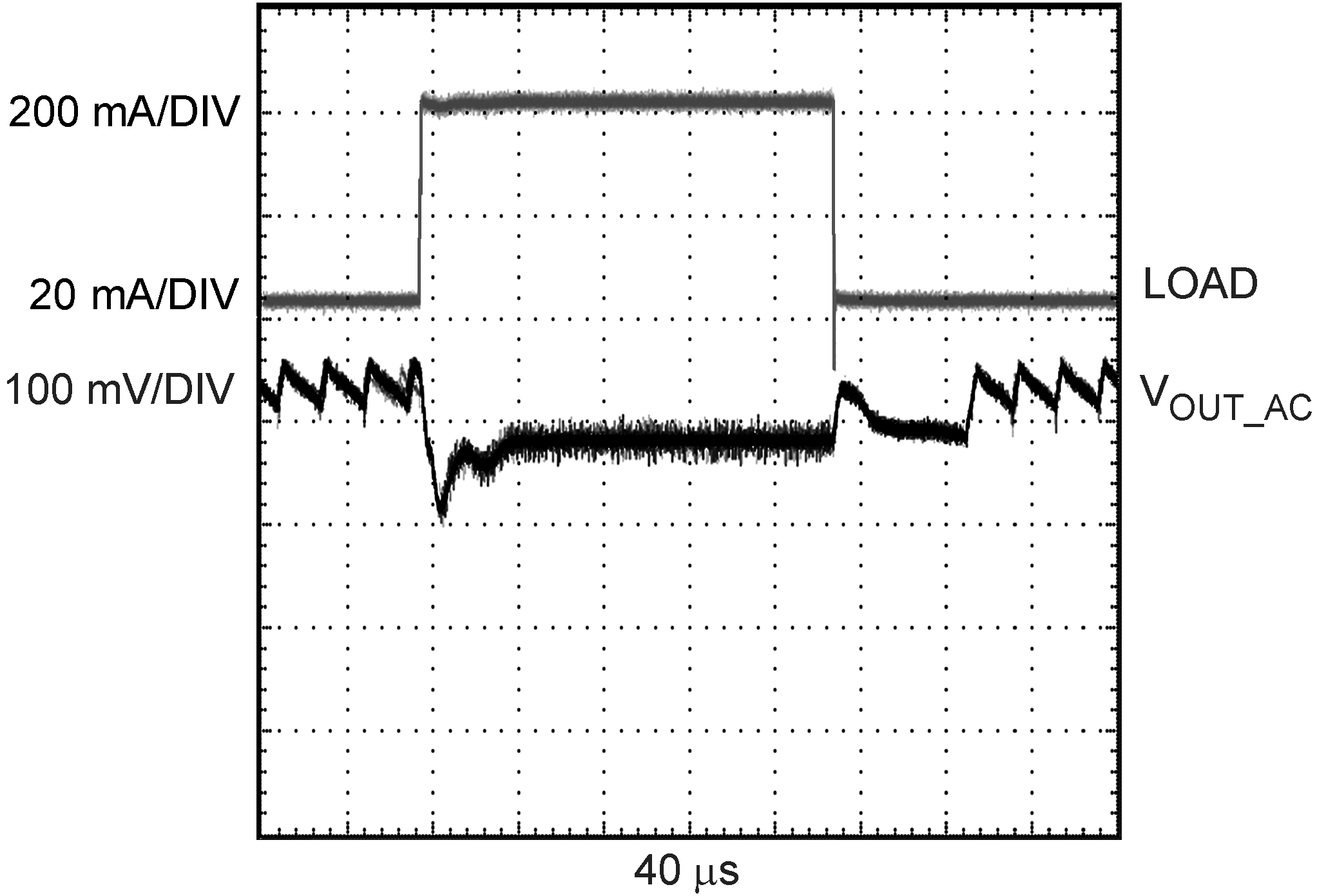

Figure 27. Load Transient in Buck Mode (Auto Mode) VIN = 4.2 V, VOUT = 3.3 V, Load = 50 to 150 mA

Figure 27. Load Transient in Buck Mode (Auto Mode) VIN = 4.2 V, VOUT = 3.3 V, Load = 50 to 150 mA

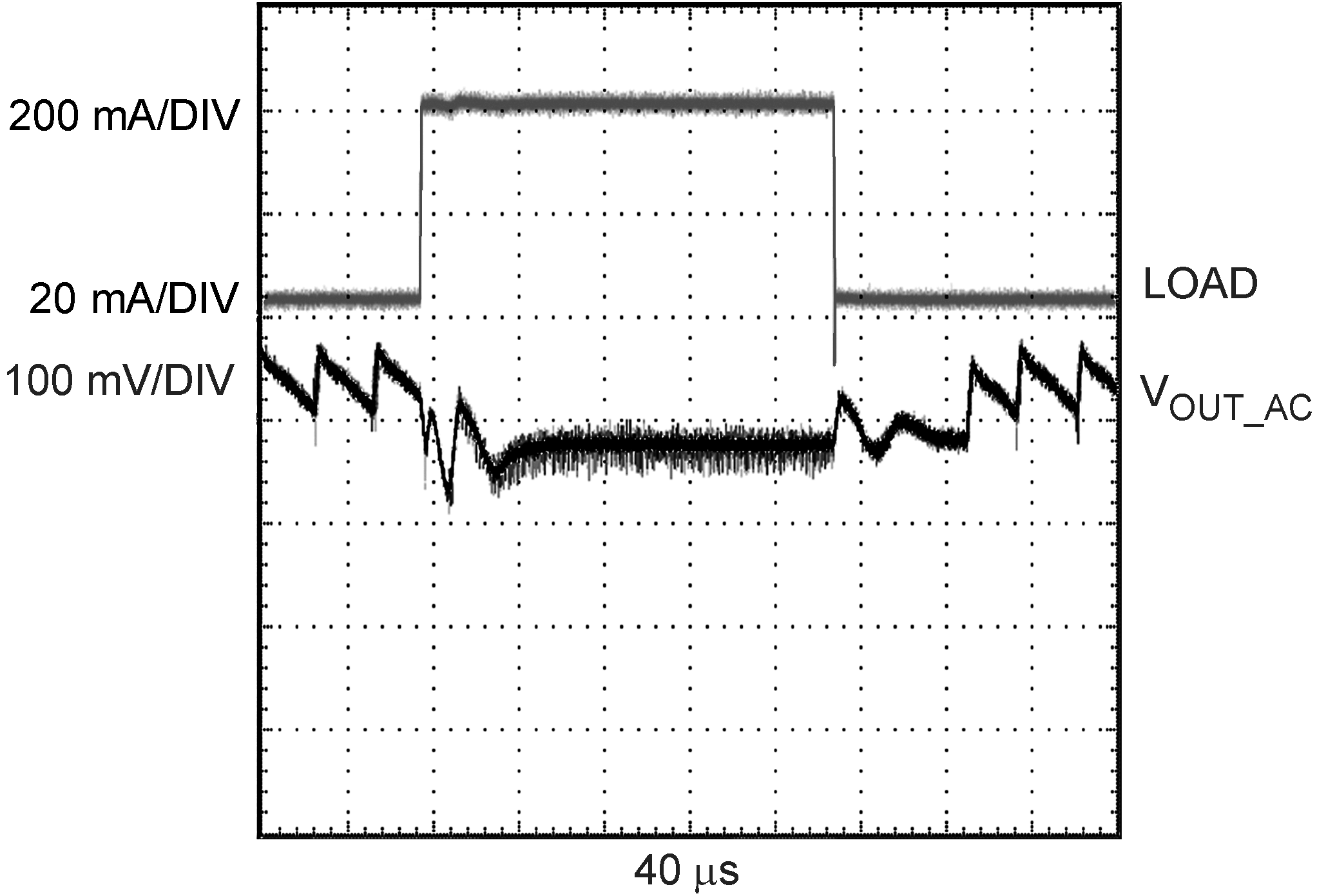

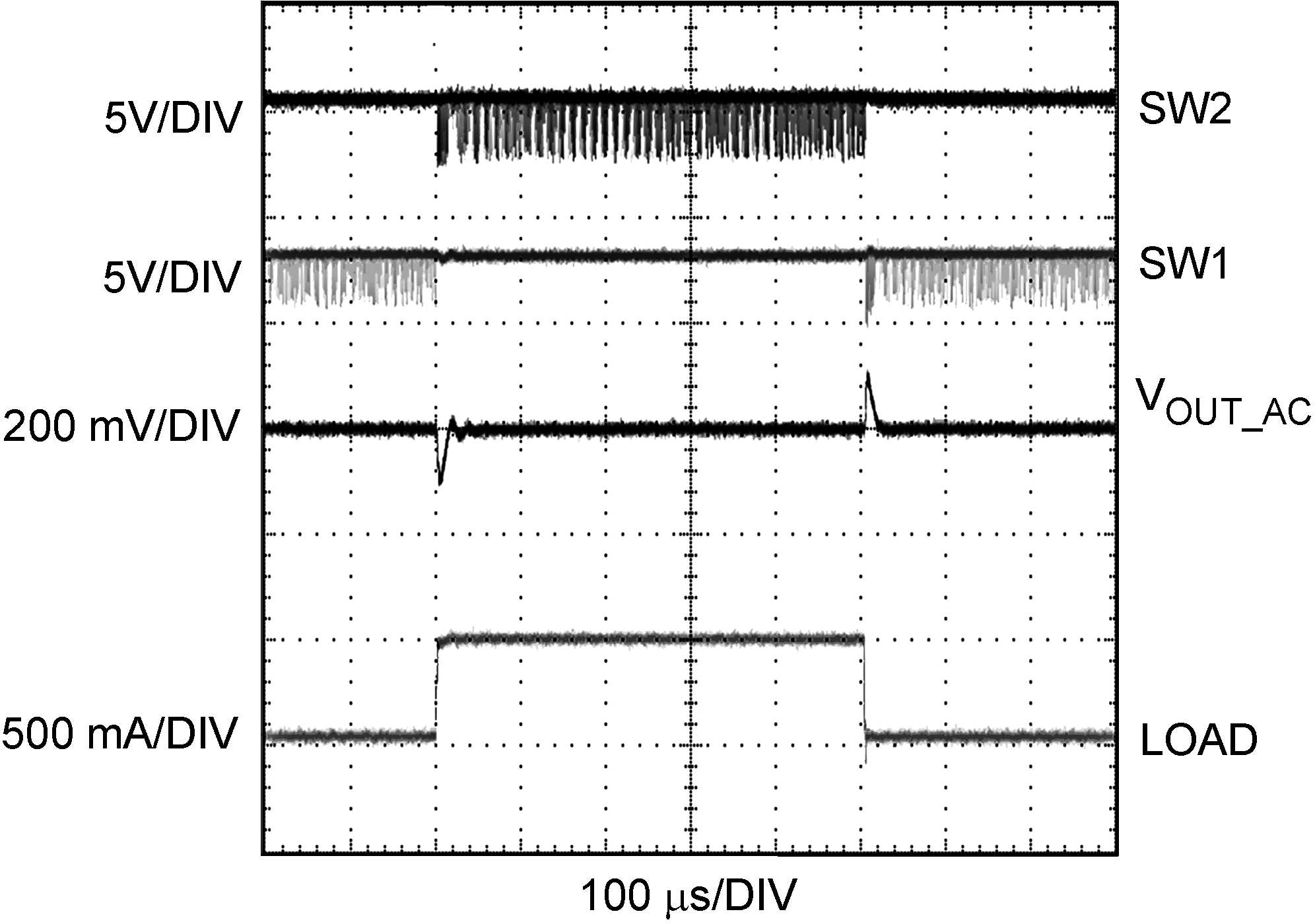

Figure 29. Load Transient in Buck-Boost Mode (Auto Mode) VIN = 3.6 V, VOUT = 3.3 V, Load = 50-150 mA

Figure 29. Load Transient in Buck-Boost Mode (Auto Mode) VIN = 3.6 V, VOUT = 3.3 V, Load = 50-150 mA

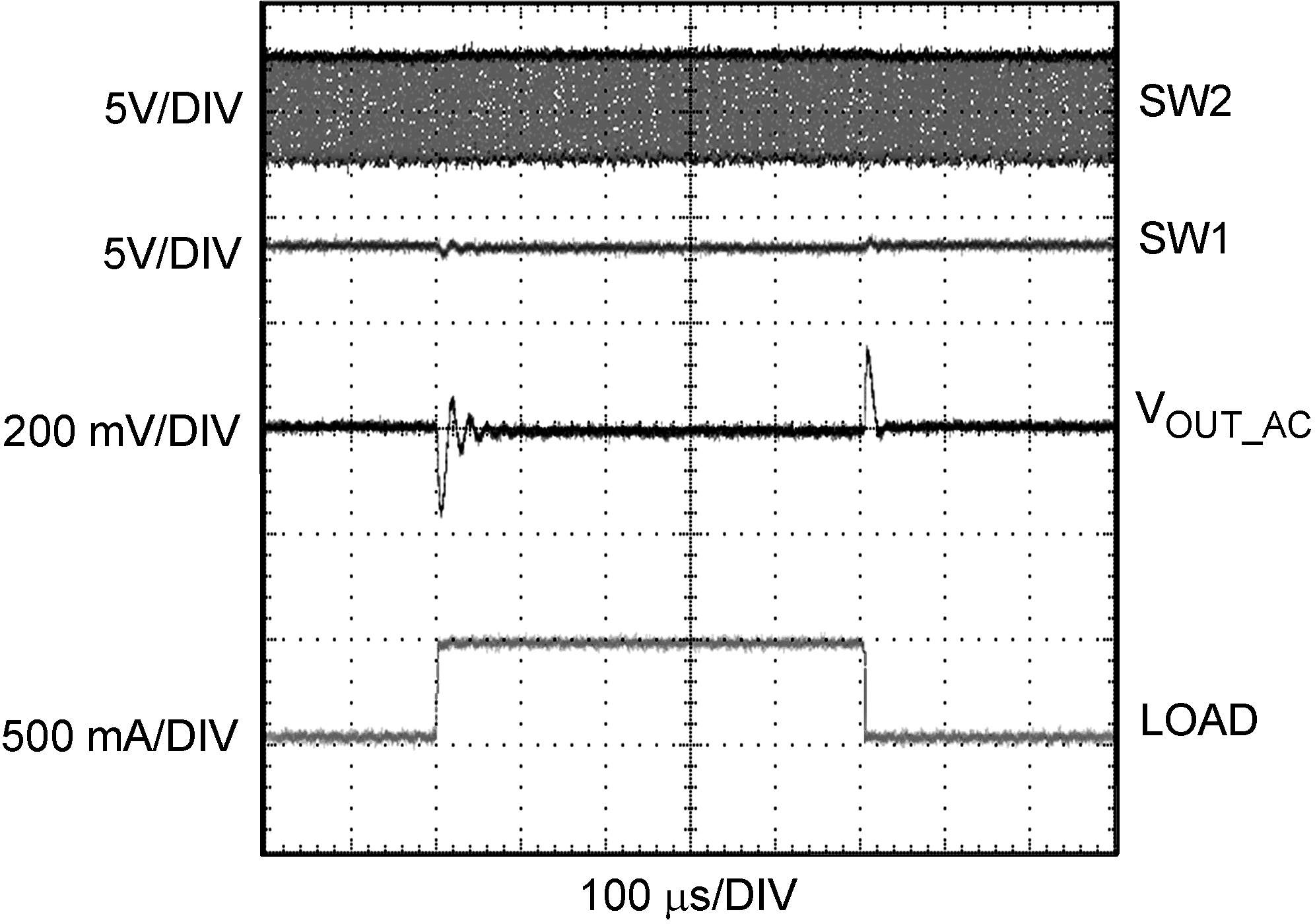

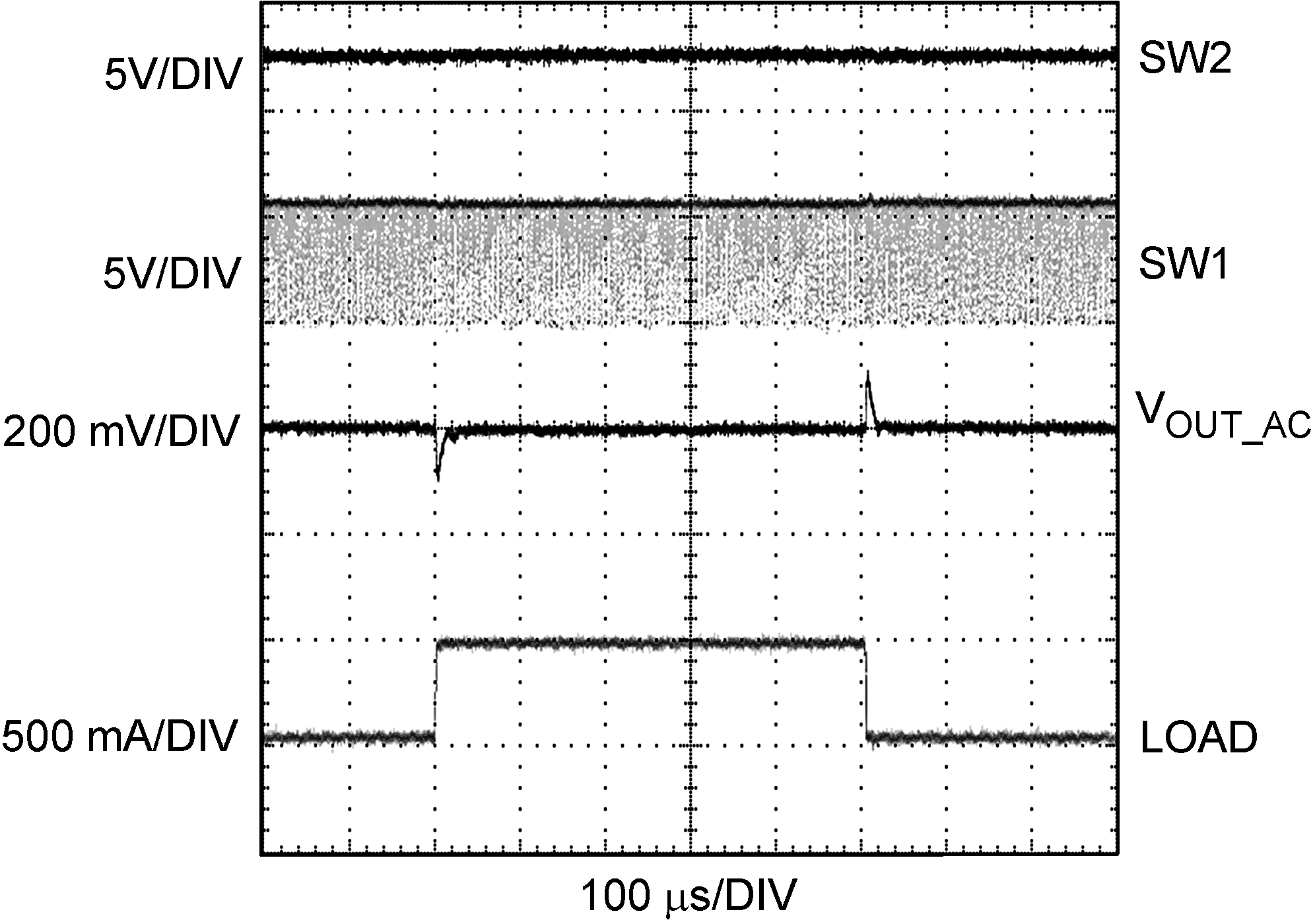

Figure 31. Load Transient in Boost Mode (Forced PWM Mode) VIN = 3.5 V, VOUT = 5 V, Load = 0 to 500 mA

Figure 31. Load Transient in Boost Mode (Forced PWM Mode) VIN = 3.5 V, VOUT = 5 V, Load = 0 to 500 mA

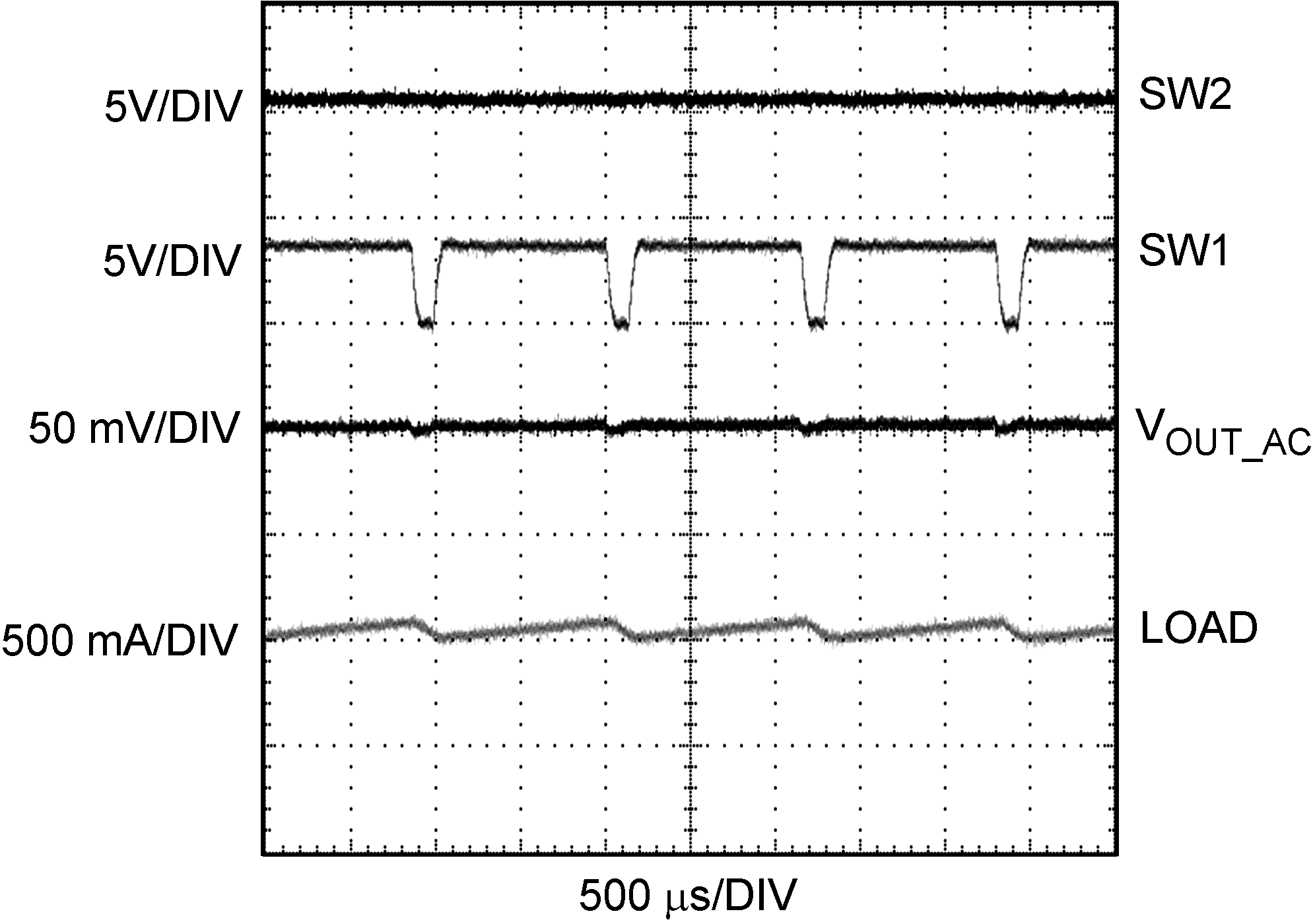

Figure 33. Typical Switching Waveform in Buck Mode (PWM Mode) VIN = 3.6 V, VOUT = 3 V, Load = 500 mA

Figure 33. Typical Switching Waveform in Buck Mode (PWM Mode) VIN = 3.6 V, VOUT = 3 V, Load = 500 mA

Figure 35. Typical Switching Waveform in Buck Mode (PFM Mode) VIN = 3.6 V, VOUT = 3 V, Load = 50mA

Figure 35. Typical Switching Waveform in Buck Mode (PFM Mode) VIN = 3.6 V, VOUT = 3 V, Load = 50mA

Figure 37. Typical Switching Waveform in Buck Mode (PWM Mode) VIN = 4 V, VOUT = 3.4 V, Load = 500 mA

Figure 37. Typical Switching Waveform in Buck Mode (PWM Mode) VIN = 4 V, VOUT = 3.4 V, Load = 500 mA

Figure 39. Typical Switching Waveform in Buck Mode (PFM Mode) VIN = 4 V, VOUT = 3.4 V, Load = 50 mA

Figure 39. Typical Switching Waveform in Buck Mode (PFM Mode) VIN = 4 V, VOUT = 3.4 V, Load = 50 mA

Figure 2. Switching Frequency vs. Temperature

Figure 2. Switching Frequency vs. Temperature (VOUT = 3.4 V)

Figure 4. PFET_RDS (on) vs. Temperature (VOUT = 3.4 V)

Figure 4. PFET_RDS (on) vs. Temperature (VOUT = 3.4 V)

Figure 6. Efficiency at VOUT = 2.8 V (Forced PWM Mode)

Figure 6. Efficiency at VOUT = 2.8 V (Forced PWM Mode)

Figure 8. Efficiency at VOUT = 3 V (Forced PWM Mode)

Figure 8. Efficiency at VOUT = 3 V (Forced PWM Mode)

Figure 10. Efficiency at VOUT = 3.3 V (Forced PWM Mode)

Figure 10. Efficiency at VOUT = 3.3 V (Forced PWM Mode)

Figure 12. Efficiency at VOUT = 3.4 V (Forced PWM Mode)

Figure 12. Efficiency at VOUT = 3.4 V (Forced PWM Mode)

Figure 14. Efficiency at VOUT = 4.5 V (Forced PWM Mode)

Figure 14. Efficiency at VOUT = 4.5 V (Forced PWM Mode)

Figure 16. Efficiency at VOUT = 5 V (Forced PWM Mode)

Figure 16. Efficiency at VOUT = 5 V (Forced PWM Mode)

Figure 18. Line Transient in Buck Mode (VOUT = 3.4 V, Load = 500 mA)

Figure 18. Line Transient in Buck Mode (VOUT = 3.4 V, Load = 500 mA)

Figure 20. Line Transient in Buck-Boost Mode (VOUT = 3.4 V, Load = 500 mA)

Figure 20. Line Transient in Buck-Boost Mode (VOUT = 3.4 V, Load = 500 mA)

Figure 22. Load Transient in Boost Operation (Forced PWM Mode) VIN = 2.7 V, VOUT = 3.4 V, Load = 0 to 500 mA

Figure 22. Load Transient in Boost Operation (Forced PWM Mode) VIN = 2.7 V, VOUT = 3.4 V, Load = 0 to 500 mA

Figure 24. Load Transient in Buck Mode (Forced PWM Mode) VIN = 4.2 V, VOUT = 3 V, Load = 0 to 500 mA

Figure 24. Load Transient in Buck Mode (Forced PWM Mode) VIN = 4.2 V, VOUT = 3 V, Load = 0 to 500 mA

Figure 26. Load Transient in Buck-Boost Mode (Forced PWM Mode) VIN = 3.05 V, VOUT = 3 V, Load = 0 to 500 mA

Figure 26. Load Transient in Buck-Boost Mode (Forced PWM Mode) VIN = 3.05 V, VOUT = 3 V, Load = 0 to 500 mA

Figure 28. Load Transient in Boost Mode (Auto Mode) VIN = 2.7 V, VOUT = 3.3 V, Load = 50 to 150 mA

Figure 28. Load Transient in Boost Mode (Auto Mode) VIN = 2.7 V, VOUT = 3.3 V, Load = 50 to 150 mA

Figure 30. Load Transient in Buck Mode (Forced PWM Mode) VIN = 5.5 V, VOUT = 5 V, Load = 0 to 500 mA

Figure 30. Load Transient in Buck Mode (Forced PWM Mode) VIN = 5.5 V, VOUT = 5 V, Load = 0 to 500 mA

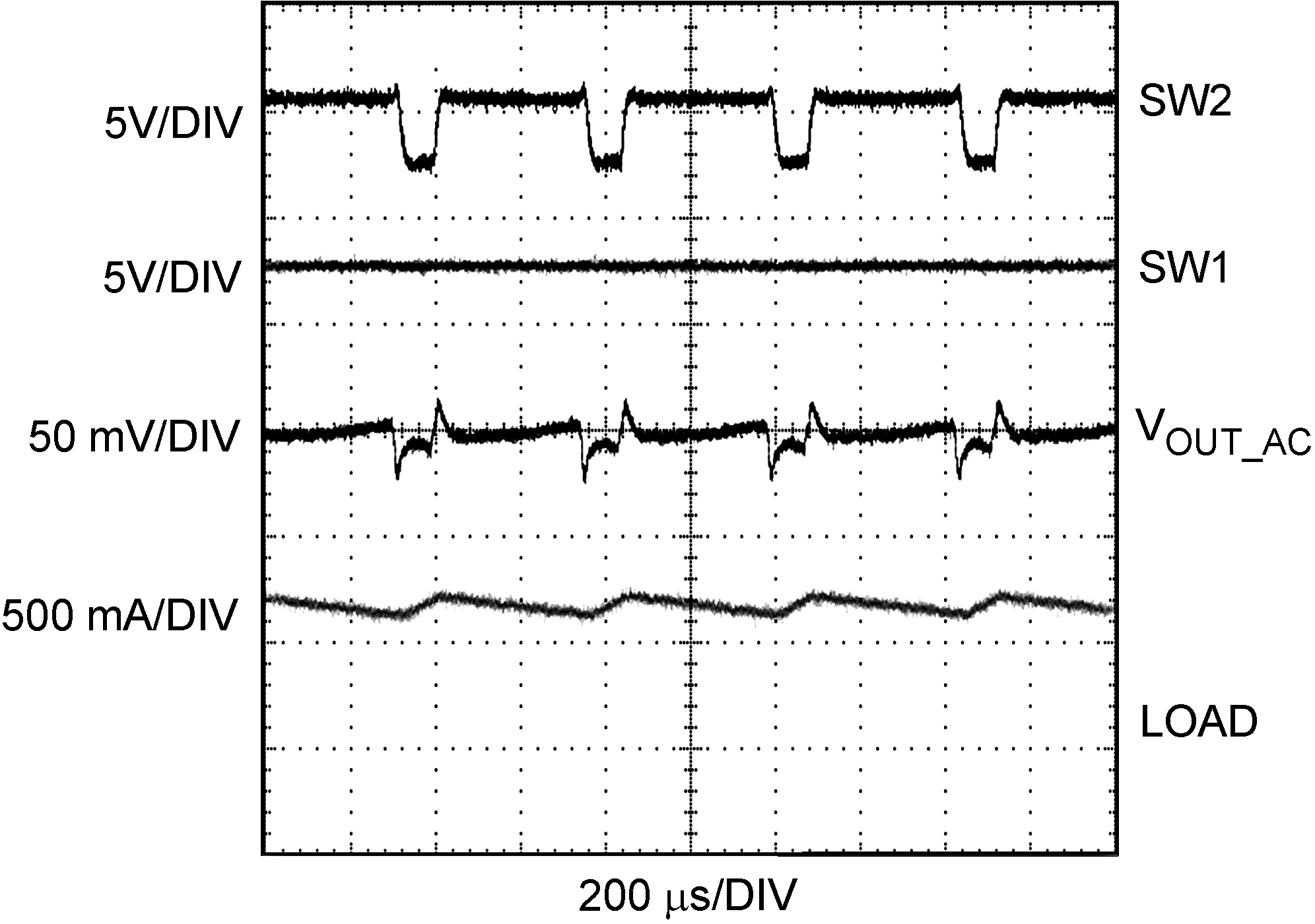

Figure 32. Typical Switching Waveform in Boost Mode (PWM Mode) VIN = 2.7 V, VOUT = 3 V, Load = 500 mA

Figure 32. Typical Switching Waveform in Boost Mode (PWM Mode) VIN = 2.7 V, VOUT = 3 V, Load = 500 mA

Figure 34. Typical Switching Waveformt in Boost Mode (PFM Mode) VIN = 2.7 V, VOUT = 3 V, Load = 50 mA

Figure 34. Typical Switching Waveformt in Boost Mode (PFM Mode) VIN = 2.7 V, VOUT = 3 V, Load = 50 mA

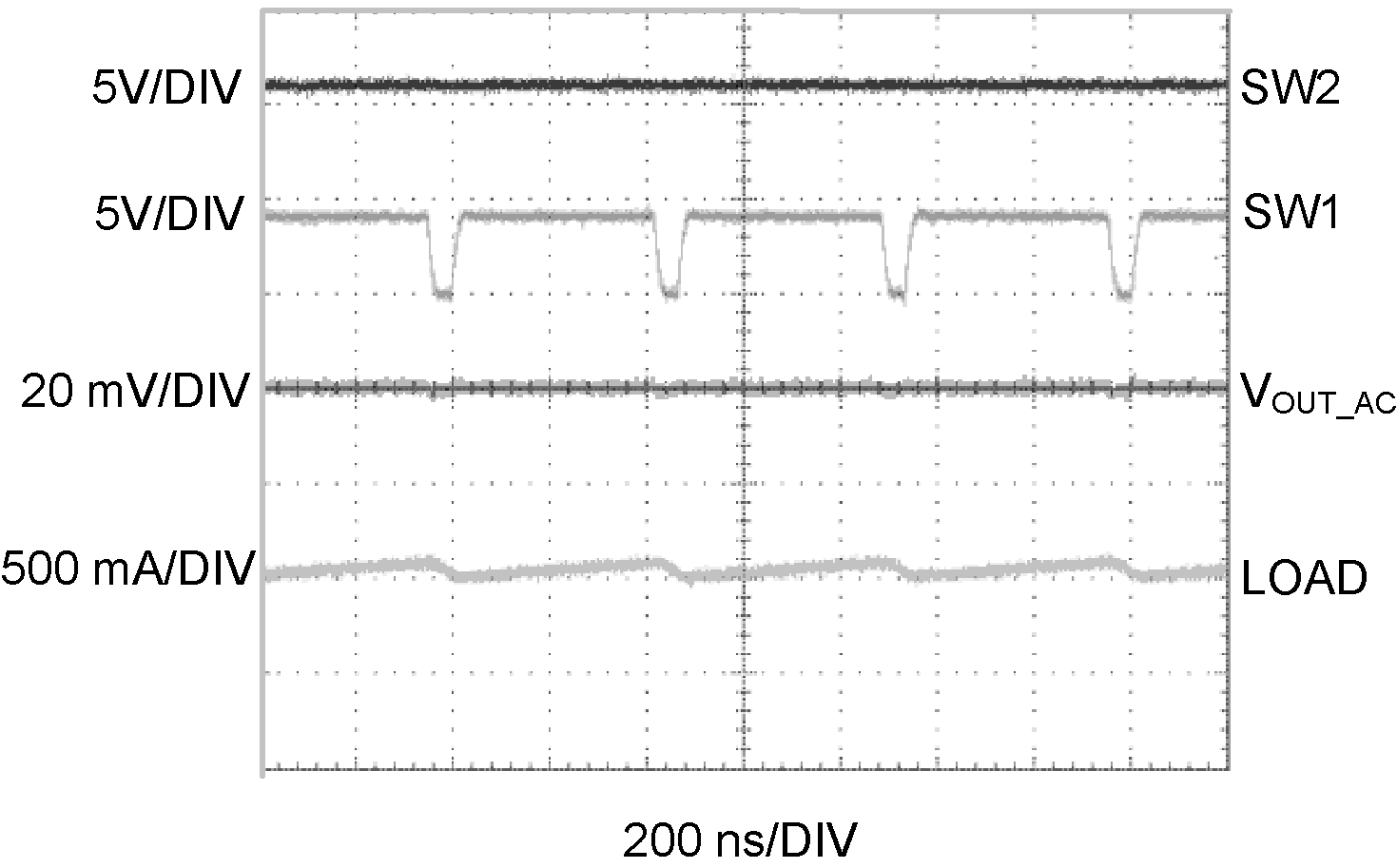

Figure 36. Typical Switching Waveform in Boost Mode (PWM Mode) VIN = 3 V, VOUT = 3.4 V, Load = 500 mA

Figure 36. Typical Switching Waveform in Boost Mode (PWM Mode) VIN = 3 V, VOUT = 3.4 V, Load = 500 mA

Figure 38. Typical Switching Waveform in Boost Mode (PFM Mode) VIN = 3 V, VOUT = 3.4 V, Load = 50 mA

Figure 38. Typical Switching Waveform in Boost Mode (PFM Mode) VIN = 3 V, VOUT = 3.4 V, Load = 50 mA