SNVS520F August 2008 – November 2016 LM3686

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (Continued)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: Linear Regulator - LILO

- 7.6 Electrical Characteristics: Linear Regulator - LDO

- 7.7 Electrical Characteristics: DC-DC Converter

- 7.8 Electrical Characteristics: Global Parameters (DCDC, LILO, and LDO)

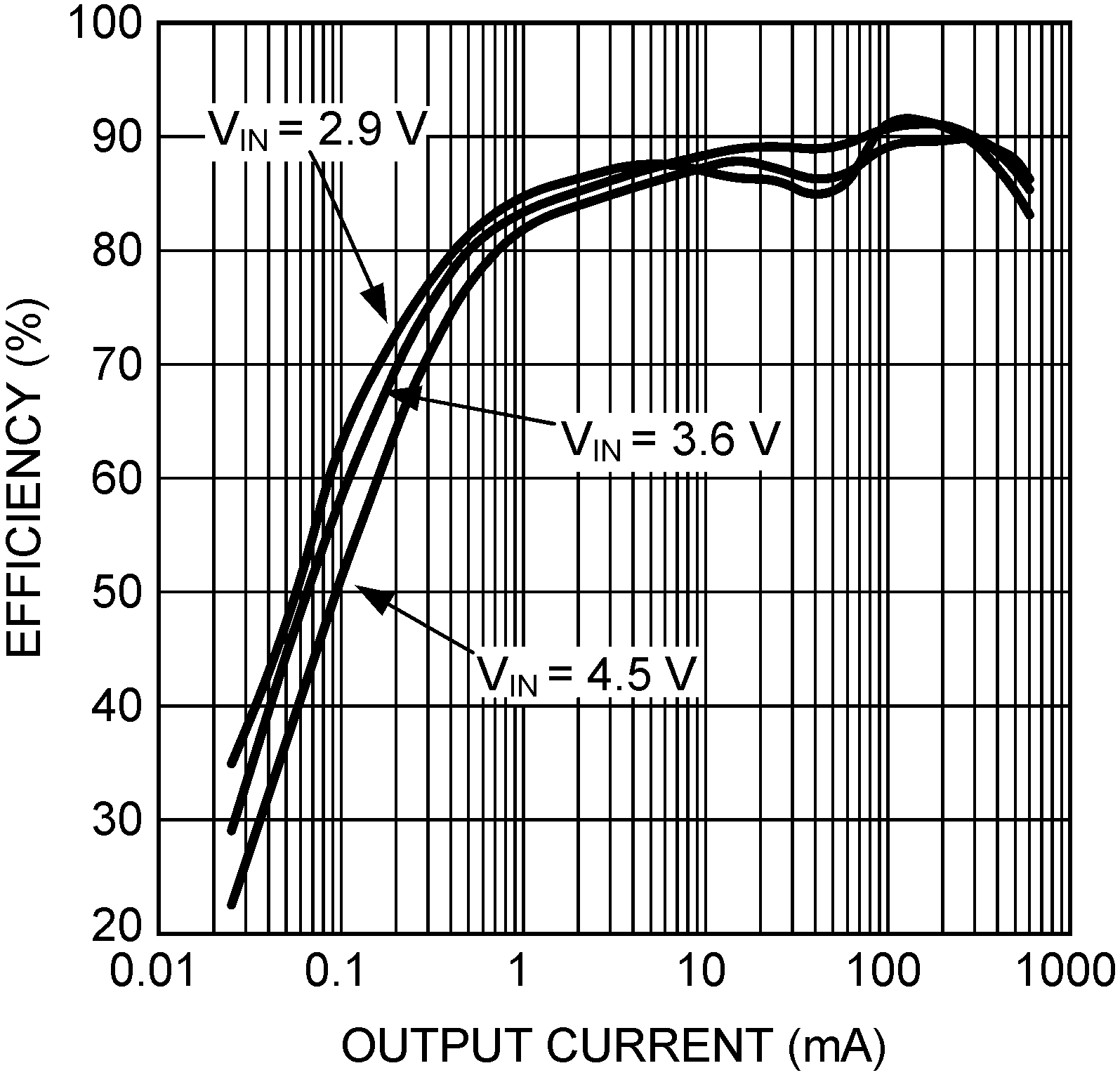

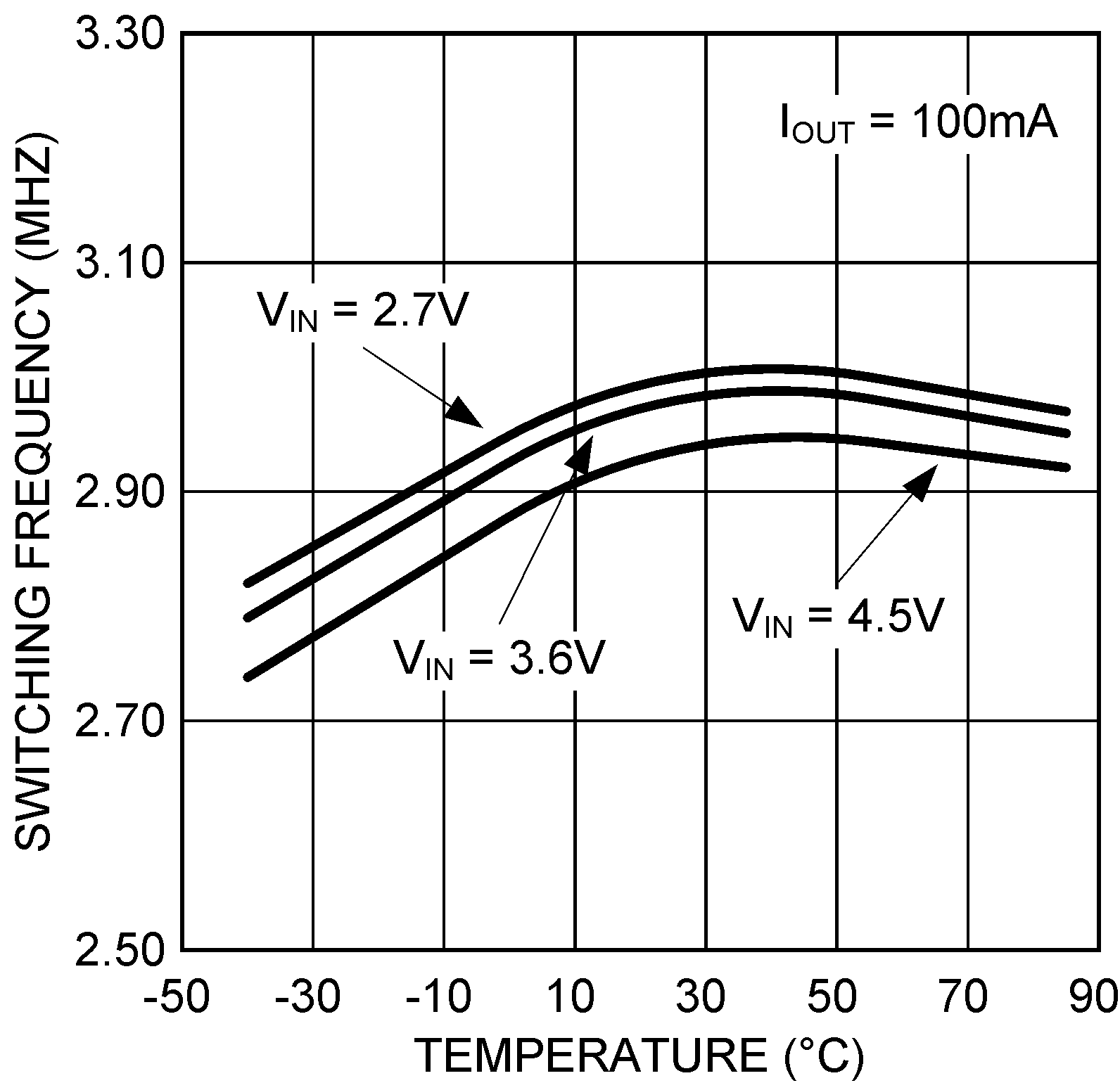

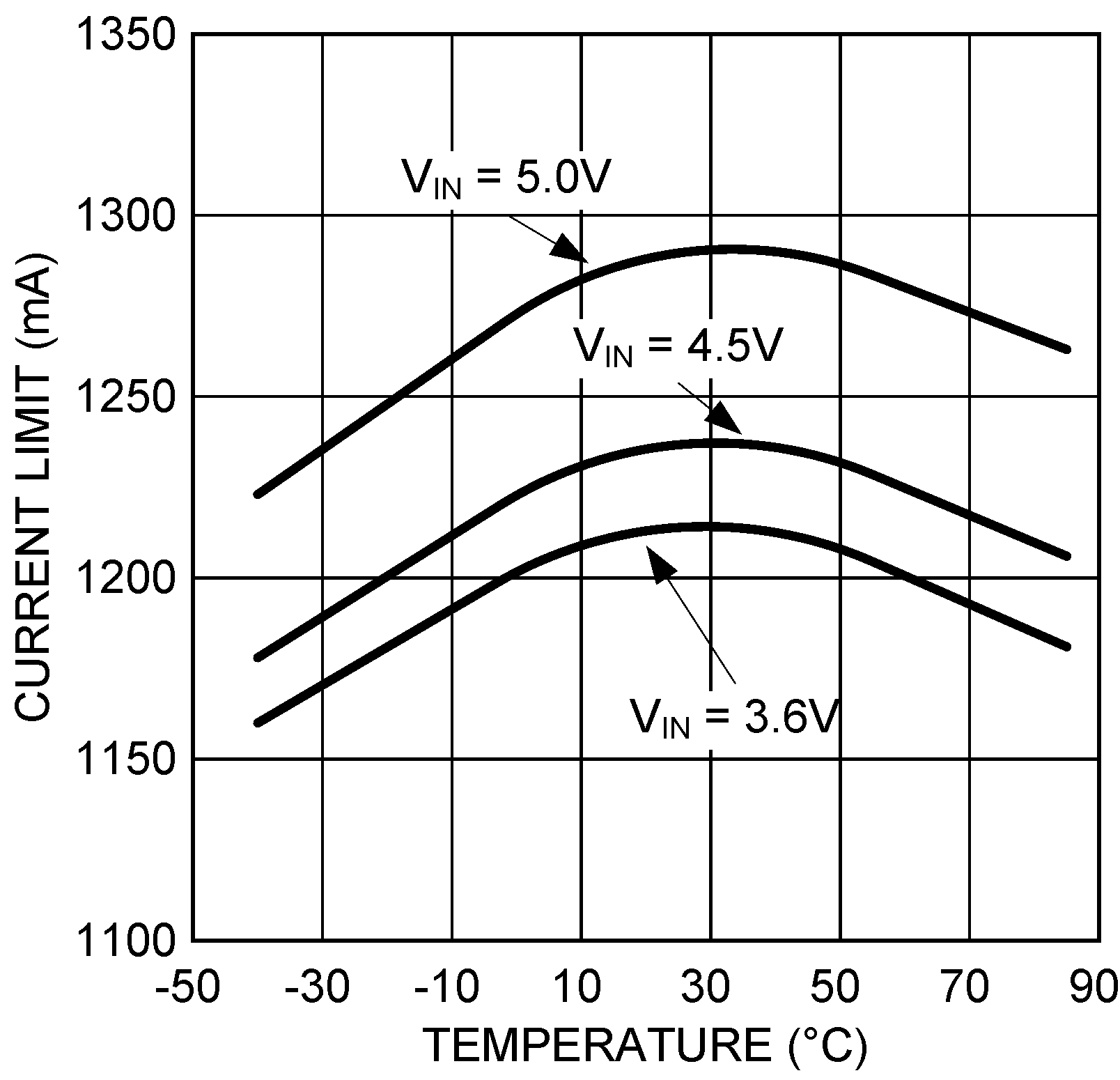

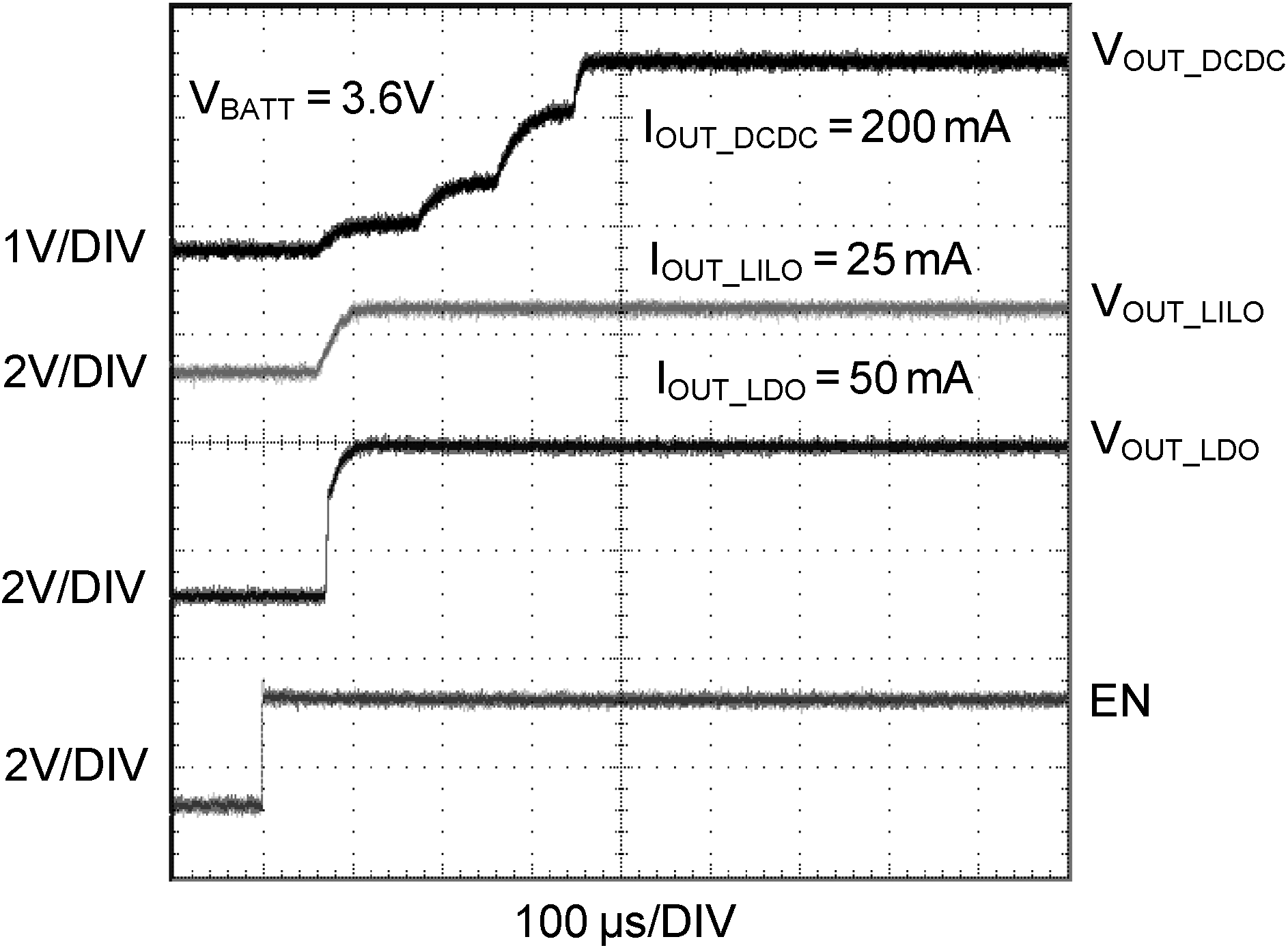

- 7.9 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YZR|12

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)(3)(5)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VBATT pin to GND and QGND | –0.2 | 6 | V | |

| EN_x pins, FB_DC-DC pin, SW pin | (GND – 0.2 V) to (VBATT+0.2 V) with 6 V maximum | |||

| Continuous power dissipation(4) | Internally limited | |||

| Junction temperature, TJ-MAX | 150 | °C | ||

| Storage temperature, Tstg | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pin.

(3) If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(4) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at TJ = 150°C (typical) and disengages at TJ = 130°C (typical).

(5) For detailed soldering specifications and information, see AN-1112 DSBGA Wafer Level Chip Scale Package.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±200 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Input voltage, VBATT (DC-DC and LDO) | 2.7 | 5.5 | V | |

| Junction temperature, TJ | –40 | 125 | °C | |

| Ambient temperature, TA(1) | –40 | 85 | °C | |

(1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP = 125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the part/package in the application (RθJA), as given by the following equation: TA-MAX = TJ-MAX-OP – (RθJA × PD-MAX).

7.4 Thermal Information

| THERMAL METRIC(1) | LM3686 | UNIT | |

|---|---|---|---|

| YZR (DSBGA) | |||

| 12 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 80.9 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 0.4 | °C/W |

| RθJB | Junction-to-board thermal resistance | 16.8 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.2 | °C/W |

| ψJB | Junction-to-board characterization parameter | 16.9 | °C/W |

(1) For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

7.5 Electrical Characteristics: Linear Regulator - LILO

Unless otherwise noted, limits apply for TA = 25°C, specifications apply to the closed-loop typical application circuits (linear regulator) with VIN_LDO = VBATT = 3.6 V(1) , VIN_LILO = VOUT_DCDC(NOM), VEN (All) = VBATT, CIN_DC = 4.7 μF, COUT_LILO = 2.2 μF, CIN_LDO = 1 μF , COUT_LDO = 1 μF, COUT_DC = CIN_LILO = 10 μF.(2)(3)(4)(5)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| EN_DC-DC = EN_LILO = ON – LARGE NMOS | ||||||

| ΔVOUT_LILO, VOUT_LILO | Output voltage accuracy, VOUT-LILO |

IOUT_LILO = 1 mA to 350 mA, VIN_LILO = VOUT_DCDC VBATT = 3.6 V |

1.2 | V | ||

| IOUT_LILO = 1 mA to 350 mA, VIN_LILO = VOUT_DCDC VBATT = 3.6 V, –40°C ≤ TA = TJ ≤ 85°C |

1.176 | 1.224 | ||||

| ΔVOUT_LILO / ΔmA | Load regulation(6) | IOUT_LILO = 1 mA to 350 mA, VIN_LILO = VOUT_DCDC VBATT = 3.6 V |

4 | μV/mA | ||

| IOUT_LILO = 1 mA to 350 mA, VIN_LILO = VOUT_DCDC VBATT = 3.6 V, –40°C ≤ TA = TJ ≤ 85°C |

12 | |||||

| VDROP | Dropout voltage(7) | VBATT = VOUT_LILO + 1.5 V (VIN_LILO disconnected from VOUT_DCDC) IOUT = 350 mA |

50 | mV | ||

| VBATT = VOUT_LILO + 1.5 V (VIN_LILO disconnected from VOUT_DCDC) IOUT = 350 mA, –40°C ≤ TA = TJ ≤ 85°C |

80 | |||||

| IQ_VIN_LILO | Quiescent current | VBATT = VIN_LILO = 3.6 V | 70 | µA | ||

| VBATT = VIN_LILO = 3.6 V –40°C ≤ TA = TJ ≤ 85°C |

90 | |||||

| ISC_LILO | Short-circuit current limit | VOUT = GND (VOUT_LILO = 0) –40°C ≤ TA = TJ ≤ 85°C |

400 | mA | ||

| EN_DC-DC = OFF, EN_LILO = ON – SMALL NMOS | ||||||

| ΔVOUT_LILO, VOUT_LILO | Output voltage accuracy VOUT_LILO |

IOUT = 1 mA to 50 mA –40°C ≤ TA = TJ ≤ 85°C |

1.176 | 1.224 | V | |

| ΔVOUT_LILO, ΔVBATT | Line regulation (small NMOS)(8) | VIN_LILO = (VOUT_LILO + 0.3 V) to 5.5 V | 0.4 | mV/V | ||

| VIN_LILO = (VOUT_LILO + 0.3 V) to 5.5 V –40°C ≤ TA = TJ ≤ 85°C |

1.5 | |||||

| ISC_LILO | Short-circuit current | VOUT_LILO = GND, –40°C ≤ TA = TJ ≤ 85°C | 70 | |||

| TSTARTUP | Start-up time | EN to 0.95 VOUT | 70 | µs | ||

| SYSTEM CHARACTERISTICS(9) | ||||||

| PSRR | Power supply rejection ratio | Signal to VBATT = 3.6 V, VIN_LILO = 1.8 V, IOUT = 200 mA, ƒ = 100 Hz |

68 | dB | ||

| Signal to VIN_LILO = 1.8 V, IOUT = 200 mA, ƒ = 100 kHz |

60 | |||||

| eN_LILO | Output noise voltage | BW = 10 Hz to 100 kHz, VIN_LILO = 1.8 V, IOUT = 200 mA, VIN_LDO = 3.6 V |

166 | µVRMS | ||

| ΔVOUT_LILO | Dynamic load transient response | Pulsed load 1 mA to 350 mA di/dt = 350 mA / 1 µs |

±30(10) | mV | ||

| ΔVIN_LILO | Dynamic load transient response on VBATT | VBATT = 3.1 V to 3.7 V VIN_LILO = VOUT_DCDC tr, tf = 10 µs, IOUT = 200 mA |

±15(10) | mV | ||

(1) VIN_LDO must be ON at all time for biasing internal reference circuits.

(2) All voltages are with respect to the potential at the GND pin.

(3) Minimum (MIN) and maximum (MAX) limits are specified by design, test, or statistical analysis. Typical (TYP) numbers represent the most likely norm. Unless otherwise specified, conditions for typical specifications are: VBATT = 3.6 V and TA = 25°C.

(4) The parameters in the electrical characteristic table are tested at VBATT = 3.6 V unless otherwise specified. For performance over the input voltage range refer to Typical Characteristics.

(5) The input voltage ranges recommended for ideal application performance for the specified output voltages are:

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V.

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V.

(6) To calculate the output voltage from the load regulation specified, use the following equation:

ΔVOUT = load regulation (%/mA) × nominal VOUT (V) × ΔIOUT (mA).

ΔVOUT = load regulation (%/mA) × nominal VOUT (V) × ΔIOUT (mA).

(7) Dropout voltage is defined as the input to output voltage differential at which the output voltage falls to 100 mV below the nominal output voltage.

(8) To calculate the output voltage from the line regulation specified, use the following equation:

ΔVOUT = line regulation (%/V) × nominal VOUT (V) × ΔVIN (V).

ΔVOUT = line regulation (%/V) × nominal VOUT (V) × ΔVIN (V).

(9) Specified by design. Not production tested.

(10) For line and load transient specifications, the + symbol represents an overshoot in the output voltage and the – symbol represents an undershoot in the output voltage. The first value signifies overshoot or undershoot at the rising edge and the second value signifies the overshoot or undershoot at the falling edge.

7.6 Electrical Characteristics: Linear Regulator - LDO

Unless otherwise noted, limits apply for TA = 25°C.(1)(2)(3)(4)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VIN_LDO | LDO input voltage range | 2.7 | 5.5 | V | ||

| ΔVOUT_LDO / VOUT_LDO | Output voltage accuracy, VOUT-LDO | VIN = 3.6 V, IOUT_LDO = 1 mA and 300 mA | 2.8 | V | ||

| VIN = 3.6 V, IOUT_LDO = 1 mA and 300 mA –40°C ≤ TA = TJ ≤ 85°C |

2.744 | 2.856 | ||||

| VIN = 3.6 V, IOUT_LDO = 1 mA and 300 mA | 3 | 3.06 | ||||

| VIN = 3.6 V, IOUT_LDO = 1 mA and 300 mA –40°C ≤ TA = TJ ≤ 85°C |

2.94 | |||||

| ΔVOUT_LDO / ΔmA | Load regulation(5) | IOUT_LDO = 1 mA and 300 mA | 8 | μV/mA | ||

| ΔVOUT_LDO / ΔVBATT | Line regulation(6) | VIN_LDO = (VOUT_LDO(NOM) + 0.3 V) to 5.5 V | 0.2 | mV/V | ||

| VDROP | Dropout voltage(7) | IOUT = 300 mA | 120 | mV | ||

| IOUT = 300 mA, –40°C ≤ TA = TJ ≤ 85°C | 200 | |||||

| IQ | Quiescent current | Ven = 0.95 V, IOUT = 0 mA | 50 | µA | ||

| Ven = 0.95 V, IOUT = 0 mA –40°C ≤ TA = TJ ≤ 85°C |

80 | |||||

| ISC_LDO | Short-circuit current limit | VOUT = GND, –40°C ≤ TA = TJ ≤ 85°C | 350 | mA | ||

| SYSTEM CHARACTERISTICS(8) | ||||||

| PSRR | Power supply rejection ratio | EN_DC = EN_LILO = GND IOUT = 200 mA, ƒ = 1 kHz |

85 | dB | ||

| Signal to VIN_LDO = 3.6 V, IOUT = 200 mA, ƒ = 10 kHz |

70 | |||||

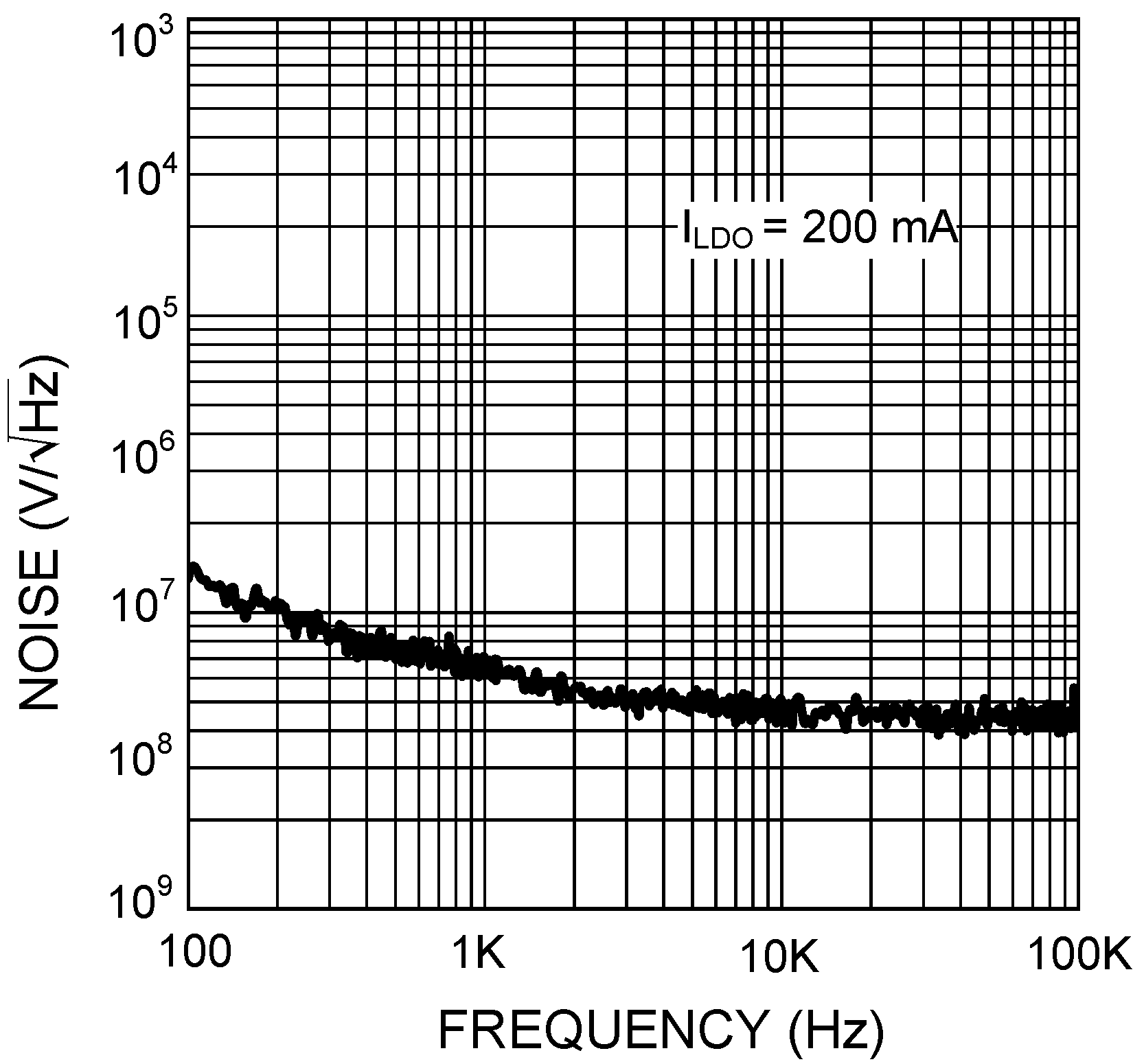

| eN_LDO | Output noise voltage | BW = 10 Hz to 100 kHz, VIN_LDO = 3.6 V, IOUT = 200 mA |

6.7 | µVRMS | ||

| ΔVIN_LDO | Dynamic line transient response | VIN_LDO = 3.8 V to 4.4 V tr, tf = 30 µs, IOUT = 1 mA |

±2(10) | mV | ||

| ΔVIN_LILO | Dynamic load transient response on VBATT | Pulsed load 1 mA and 300 mA tr, tf = 10 µs |

±30(10) | mV | ||

(1) All voltages are with respect to the potential at the GND pin.

(2) Minimum (MIN) and maximum (MAX) limits are specified by design, test, or statistical analysis. Typical (TYP) numbers represent the most likely norm. Unless otherwise specified, conditions for typical specifications are: VBATT = 3.6 V and TA = 25°C.

(3) The parameters in the Electrical Characteristics tables are tested at VBATT = 3.6 V unless otherwise specified. For performance over the input voltage range refer to Typical Characteristics.

(4) The input voltage ranges recommended for ideal application performance for the specified output voltages are

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V

(5) To calculate the output voltage from the load regulation specified, use the following equation:

ΔVOUT = load regulation (%/mA) × nominal VOUT (V) × ΔIOUT (mA)

ΔVOUT = load regulation (%/mA) × nominal VOUT (V) × ΔIOUT (mA)

(6) To calculate the output voltage from the line regulation specified, use the following equation:

ΔVOUT = line regulation (%/V) × nominal VOUT (V) × ΔVIN (V)

ΔVOUT = line regulation (%/V) × nominal VOUT (V) × ΔVIN (V)

(7) Dropout voltage is defined as the input to output voltage differential at which the output voltage falls to 100 mV below the nominal output voltage.

(8) Specified by design. Not production tested.

7.7 Electrical Characteristics: DC-DC Converter

Unless otherwise noted, limits apply for TA = 25°C.(2)(3)(4)(1)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VFB_DCDC | Feedback voltage accuracy | PWM mode(2) | 1.8 | V | ||

| PWM mode(2), –40°C ≤ TA = TJ ≤ 85°C | 1.746 | 1.836 | ||||

| VREF | Internal reference voltage | 0.5 | V | |||

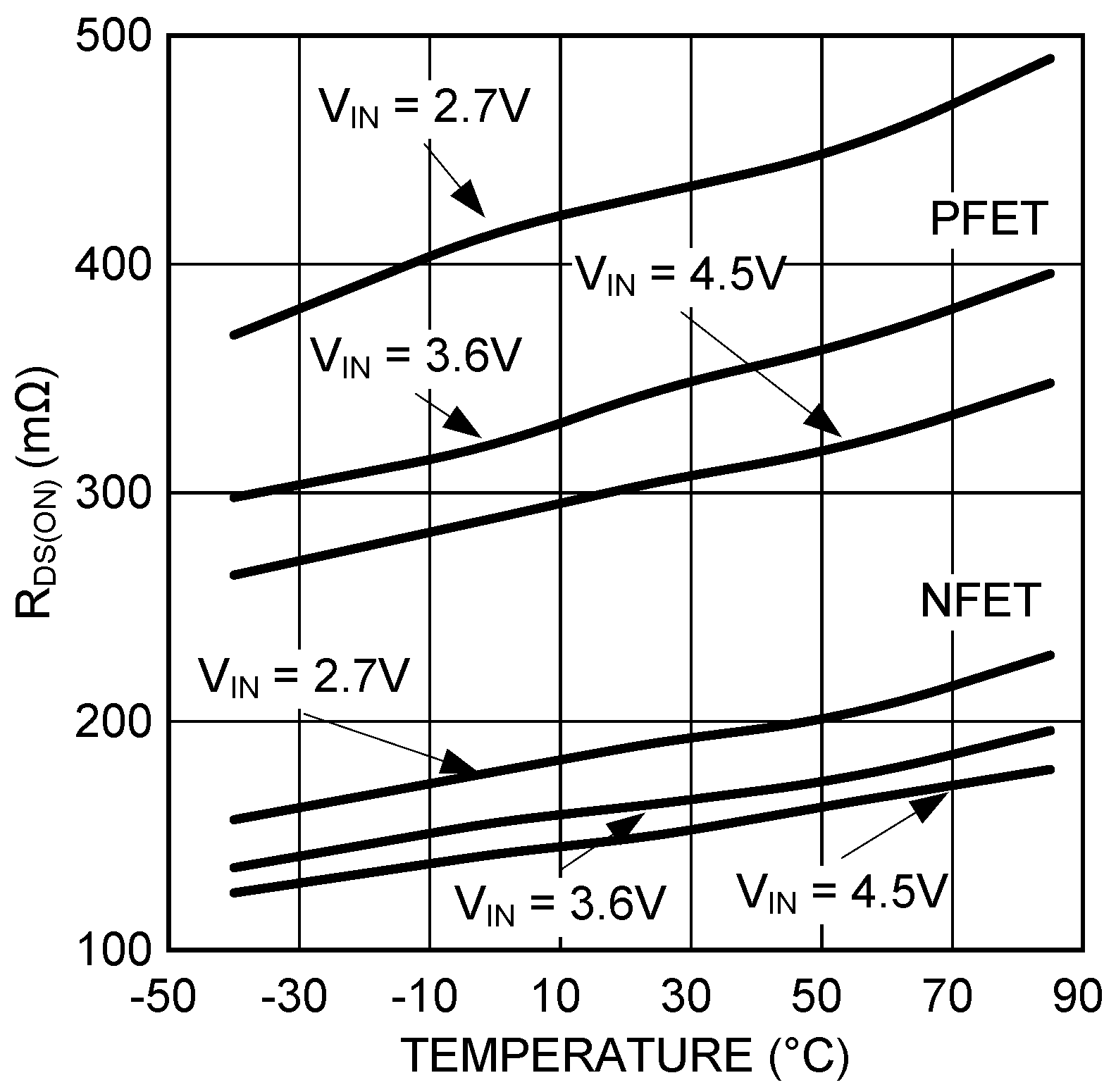

| RDSON(P) | Pin-pin resistance for PFET | VBATT = 3.6 V ISW = 100 mA |

350 | 450 | mΩ | |

| RDSON(N) | Pin-pin resistance for NFET | VBATT = 3.6 V ISW = 100 mA |

150 | 250 | mΩ | |

| IQ_AUTO | Quiescent current for auto mode | No load, device is not switching, FB = HIGH | 28 | µA | ||

| No load, device is not switching, FB = HIGH –40°C ≤ TA = TJ ≤ 85°C |

40 | |||||

| ILIM | Switch peak current limit | Open loop | 1.22 | A | ||

| Open loop, –40°C ≤ TA = TJ ≤ 85°C | 1.035 | 1.375 | ||||

| ƒOSC | Internal oscillator frequency | PWM mode | 3 | MHz | ||

| PWM mode, –40°C ≤ TA = TJ ≤ 85°C | 2.4 | 3.4 | ||||

(1) The input voltage ranges recommended for ideal application performance for the specified output voltages are:

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V

(2) Electrical Characteristics tables reflects open loop data (FB = 0 V and current drawn from SW pin ramped up until cycle by cycle current limit is activated). Closed loop current limit is the peak inductor current measured in the application circuit by increasing output current until output voltage drops by 10%.

7.8 Electrical Characteristics: Global Parameters (DCDC, LILO, and LDO)

Unless otherwise noted, limits apply for TA = 25°C.(1)(2)(3)(4)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| IQ_VBATT | Quiescent current into VBATT | Full power mode IOUT_DCDC = IOUT_LILO = IOUT_LDO = 0 mA, DC-DC is not switching (FB_DCDC forced higher than VOUT_DCDC) Ven = 1.1V, |

100 | µA | ||

| Full power mode IOUT_DCDC = IOUT_LILO = IOUT_LDO = 0 mA, DC-DC is not switching (FB_DCDC forced higher than VOUT_DCDC) Ven = 1.1V, –40°C ≤ TA = TJ ≤ 85°C |

130 | |||||

| IQ_GLOBAL | Shutdown current into VBATT | VEN_DCDC = VEN_LILO = VEN_LDO = 0 V | 2.5 | µA | ||

| VEN_DCDC = VEN_LILO = VEN_LDO = 0 –40°C ≤ TA = TJ ≤ 85°C |

4 | |||||

| ENABLE PINS (EN_DCDC, EN_LILO, EN_LDO) | ||||||

| IEN | Enable pin input current | All EN = 0 V | .01 | µA | ||

| All EN = 0 V, –40°C ≤ TA = TJ ≤ 85°C | 1 | |||||

| VIH | Logic high input | –40°C ≤ TA = TJ ≤ 85°C | 1.1 | V | ||

| VIL | Logic low input | –40°C ≤ TA = TJ ≤ 85°C | 0.4 | V | ||

(1) All voltages are with respect to the potential at the GND pin.

(2) Mininum (MIN) and maximum (MAX) limits are specified by design, test, or statistical analysis. Typical (TYP) numbers represent the most likely norm. Unless otherwise specified, conditions for typical specifications are: VBATT = 3.6 V and TA = 25°C.

(3) The parameters in the Electrical Characteristics tables are tested at VBATT = 3.6 V unless otherwise specified. For performance over the input voltage range refer to Typical Characteristics.

(4) The input voltage ranges recommended for ideal application performance for the specified output voltages are:

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V

VBATT = 2.7 V to 5.5 V for 1 V ≤ VOUT_DCDC < 1.8 V

VBATT = (VOUT_DCDC + 1 V) to 5.5 V for 1.8 V ≤ VOUT_DCDC < 3.6 V

7.9 Typical Characteristics

Unless otherwise specified, typical application (post regulation), VBATT = 3.6 V, TA = 25°C, enable pins tied to VBATT, VOUT_DCDC = 1.8 V, VOUT_LILO = 1.2 V, VOUT_LDO = 2.8 V.

| LDO – VIN_LDO = 3.6 V |

| LILO – VIN_LILO = 3.6 V |

| LDO – VIN_LDO = 3.6 V |

| Open Loop |

| All Three Enables Tied Together |