SNVSAA7B December 2015 – July 2021 LM53625-Q1 , LM53635-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 General Application

- 9.2.2 Fixed 5-V Output for USB-Type Applications

- 9.2.3 Fixed 3.3-V Output

- 9.2.4 Adjustable Output

- 9.3 What to Do and What Not to Do

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- RNL|22

Thermal pad, mechanical data (Package|Pins)

- RNL|22

Orderable Information

9.2.4.3 Application Curves

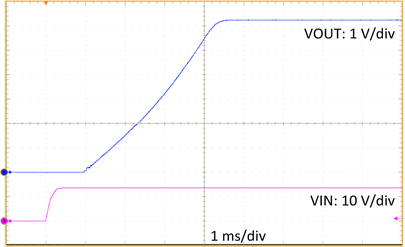

The following characteristics apply only to the circuit of Figure 9-34. These parameters are not tested and represent typical performance only. Unless otherwise stated, the following conditions apply: VIN = 12 V, TA = 25°C. For the purpose of offering meaningful information to the designer, information is included for the application with FPWM pin high (FPWM mode) and FPWM pin low (AUTO mode) although the schematic shows the application running specifically in AUTO mode. The mode is specified under each of the following graphs.

| VOUT = 6 V (ADJ part) | FPWM | IOUT = 0 A |

| VOUT = 6 V (ADJ part) | FPWM | IOUT = 0 A |

| VOUT = 6 V (ADJ part) | FPWM | IOUT = 0 A |

| VOUT = 6 V (ADJ part) | FPWM |