SLVSFD0 September 2019 LM74202-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Undervoltage Lockout (UVLO)

- 8.3.2 Overvoltage Protection (OVP)

- 8.3.3 Reverse Battery Protection

- 8.3.4 Hot Plug-In and In-Rush Current Control

- 8.3.5 Overload and Short Circuit Protection

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2 Detailed Design Procedure

- 9.2.3 Application Curves

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PWP|16

Thermal pad, mechanical data (Package|Pins)

- PWP|16

Orderable Information

8.3.4 Hot Plug-In and In-Rush Current Control

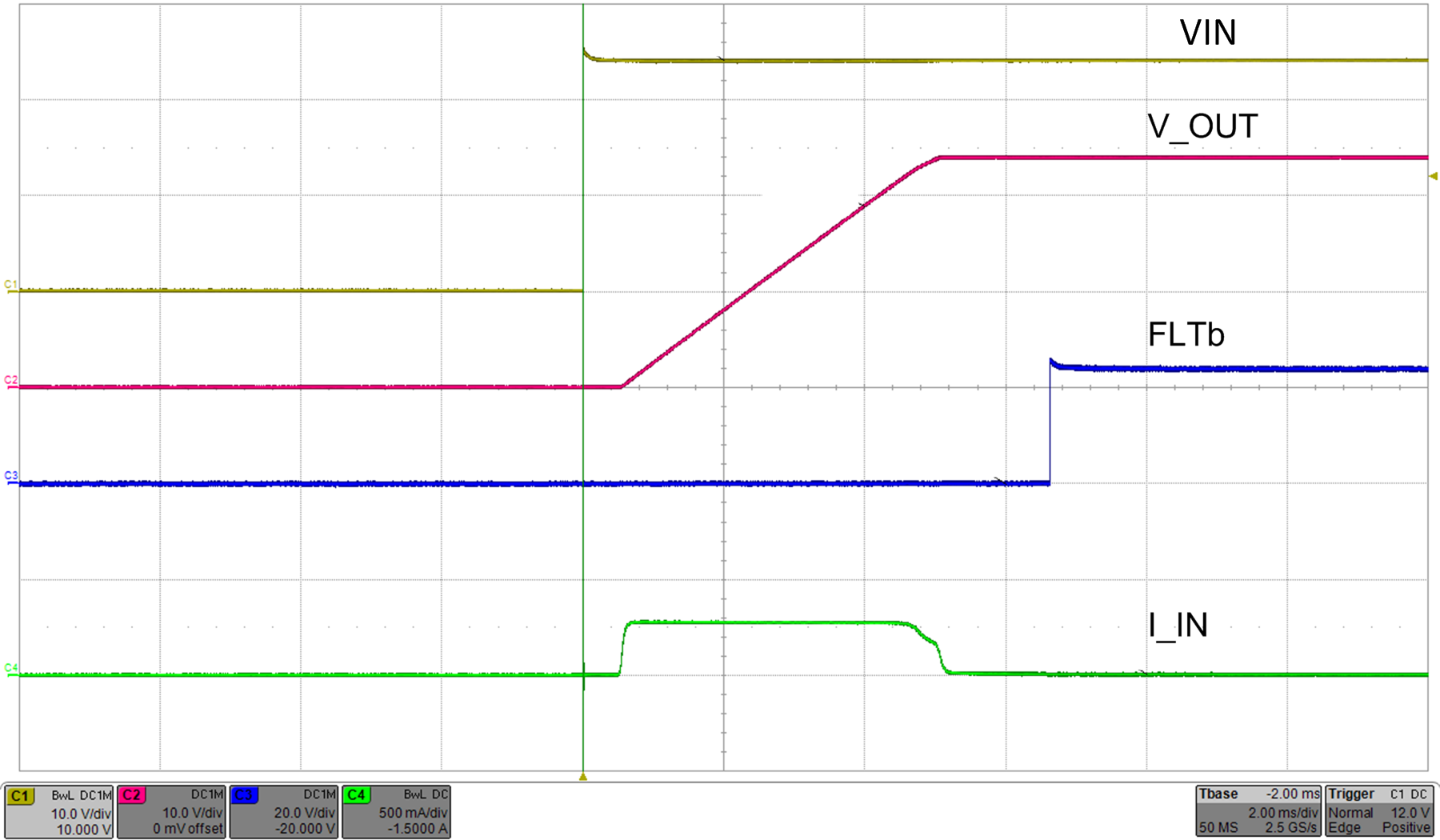

The device is designed to control the in-rush current upon insertion of a card into a live backplane or other "hot" power source. This limits the voltage sag on the supply voltage and prevents unintended resets of the system power. The controlled start-up also helps to eliminate conductive and radiative interferences. An external capacitor connected from the dVdT pin to RTN defines the slew rate of the output voltage at power-on as shown in Figure 27 and Figure 28.

Figure 27. Output Ramp Up Time tdVdT is Set by C(dVdT)

Figure 27. Output Ramp Up Time tdVdT is Set by C(dVdT) The dVdT pin can be left floating to obtain a predetermined slew rate (tdVdT) on the output. When the terminal is left floating, the devices set an internal output voltage ramp rate of 23.9 V / 1.6 ms. A capacitor can be connected from dVdT pin to RTN to program the output voltage slew rate slower than 23.9 V / 1.6 ms. Use Equation 1 and Equation 2 to calculate the external C(dVdT) capacitance.

Equation 1 governs slew rate at start-up.

where

- I(dVdT) = 4.7 µA (typical)

- Gain(dVdT) = dVdT to VOUT gain = 24.6

The total ramp time (tdVdT) of V(OUT) for 0 to V(IN) can be calculated using Equation 2.

The inrush current can be calculated by Equation 3

| CdVdT = 22 nF | COUT = 47 µF | RILIM = 5.36 kΩ |